Abstract

A new macro model of single electron transistor (SET) for SPICE based simulation of SET circuits is proposed. Two voltage controlled current sources and some scaling factors are incorporated in the existing model to derive our model. The V–I characteristics of the proposed SET is promising enough to be used as the basic element for designing circuits based on SETs. A comparison with the previous models establishes the fact that our model efficiently removes the drawbacks of the existing models. Our model also agrees well with the results obtained from popular SIMON simulator. To verify the accuracy, we have designed a SET inverter cell and investigated its characteristics. The work includes the effect of the parameters on the noise margin and voltage transfer characteristics of the inverter circuit. Further, to verify the applicability, a multi peak negative differential resistance circuit based on the proposed model is designed and simulated.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the rapid advancement of the nano-scale fabrication, the single electron transistor (SET) [1, 2] has become one of the most attractive and promising nano device due to its small size, low power consumption and sensitive charge measurement property [3–5]. SETs are being used and proposed as promising devices for quantum systems, including quantum computers and quantum dots and also as logic elements [6–9]. The main principles behind the operation of SETs are tunneling effect and Coulomb blockade oscillation [10, 11].

SETs show completely different electrical characteristics from MOS transistors and basically based on few electron transport. In recent times, maximum attention has been given in design and simulation of SET-based circuits [12–16]. To understand the characteristics of SET based circuits and to explore its applications, simulation and device modeling of this device has become very important. Mainly three different approaches are used for simulation of SET: Macro-modeling, Monte-Carlo method and analytical modeling. The Monte Carlo approach is based on probability calculation of the tunnel events for all the Coulomb islands. This is a tedious job to perform and takes lot of time [17]. SETs have some serious drawbacks which can be overcome by the co-design of MOSFET and SET. Several works have been reported in the literature on hybrid SET-MOS based circuit design [18–24]. SET-MOS hybrid circuits cannot be simulated in Monte Carlo based simulators like SIMON, but with macro model approach hybrid circuits can be easily simulated in SPICE.

Other than macro model, several other approaches have also been reported in literature, which are based on master equation method [25–27]. In the master equation method, a set of equations is solved to obtain the characteristics curves of single electron transistor. In this approach, to obtain an accurate result one needs to consider a large number of states. This increases the complexity of the process and also the computation time [11]. A macro model can be defined as an equivalent circuit of a particular device, designed using basic microelectronics components like voltage and current sources, diodes and resistors. In macro modeling approach, we solely concentrate on solving KCL and KVL equations rather than calculating the probability of tunnel events or solving a set of equations. Therefore, the computation time of this approach is much lesser compared to other approaches. For circuits with a small number of tunnel junctions, the master equation method is much faster compared to Monte Carlo method. In case of large circuits, the master equation method is not feasible and the macro model approach is faster compared to the other two approaches. Single electronic circuits based on macro model approach can be easily simulated using SPICE. In this approach, a SET is replaced by its equivalent electrical circuit called the macro model. For simulation of multiple SET-based circuits, we just have to call the corresponding macro model or the sub circuit. There are two main assumptions for macro modeling: (1) after determining the parameters of SET equivalent model, it can be used in a whole circuit, and (2) the I–V characteristic of the SET is influenced by neighbouring transistors only through the changes of terminal voltages [28]. The macro model proposed by Yu et al [29] is based on parameter based modeling and line fitting. In the V–I characteristic curves of Yu’s model, it is observed that the \(\hbox {I}_{\mathrm{ds}}\)–\(\hbox {V}_{\mathrm{{ds}}}\) curves are not parallel to each other. Wu and Lin later modified the model to make the current flowing from gate to source negligibly small [29]. Karimian et al further modified it to calculate the timing of electron tunneling through the barrier by employing a switch capacitor circuit in the model [30]. Recently we proposed a macro model [31], which removes the drawbacks of the existing models and works as an ideal single electron transistor. However, none of the models reported above have yielded the expected characteristics of practical SETs, since there are still some drawbacks with these models. Therefore, in this work, we have modified our previous model to make it more accurate and practical, by employing two voltage controlled current sources in Yu’s model. Also, to reduce the complexity the number of design parameters has been reduced compared to our previous model. The V–I characteristics of the proposed SET is thoroughly studied to verify its applicability for designing single electronics circuits. The simulation results are compared with previously reported models. To confirm the validity of the model, different benchmarked circuits have been designed using the proposed model and their characteristics are thoroughly investigated.

2 Design and analysis of the proposed model

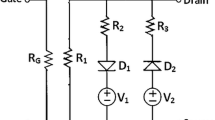

The proposed macro model of SET is shown in Fig. 1. The V–I characteristics of SETs can be divided into two parts; the Coulomb blockade and non-Coulomb blockade parts. The non-Coulomb blockade part of the characteristics which shows symmetric nature of the drain current as a function of \(\hbox {V}_{\mathrm{ds}}\) has been incorporated in our model by using two branches of circuit elements consisting of diodes (D1,D2), resistors (R2,R3) and voltage source \(\hbox {V}_{\mathrm{p}}\). Here, D2, R3, \(-\hbox {V}_{\mathrm{p}}\) and D1, R2, \(+\hbox {V}_{\mathrm{p}}\) are responsible for the positive and negative parts of the characteristics curve, respectively. When the value of the critical voltage is greater than \(\hbox {V}_{\mathrm{p}}\), diode D1 is ON and current flows through R2. If the critical voltage is less than the \(-\hbox {V}_{\mathrm{p}}\), diode D2 is ON and current flows through the resistor R3. Two more branches consisting of R1, D3, g1 and R5, D4, g2 have been used to generate the Coulomb blockade part of the characteristics. In the positive part of the Coulomb blockade characteristics, current flows through R5 and g2 bypassing D4, and a very small current also flows through R1 and D3. In the negative part of the Coulomb blockade characteristics, current flows through R1 and g1 bypassing D3 and a very small current also flows through R5 and D4. RG is used in the circuit to isolate the gate terminal from the source terminal by restricting the current flowing through it. Also the value of RG has been chosen much higher compared to other resistor values so that it acts like an open circuit. From designer point of view, R6 has no significance, it only helps in plotting the overall drain current. We have used two voltage controlled current sources (g1 and g2) which are functions of gate to source voltage. The voltage source \(\hbox {V}_{\mathrm{p}}\) has been used for defining the range of Coulomb blockade region. The values of resistors R1, R5, R2 and R3 (written as RR1, RR5, RR2 and RR3) can be expressed as [28]

The parameters CF1, \(\hbox {C}\hbox {V}_{\mathrm{p}}\), CI2, CR1 and CR2 are used to fit the I–V characteristics curve at various gate biases. CF1, which determines the frequency of Coulomb oscillation in \(\hbox {I}_{\mathrm{ds}}\)–\(\hbox {V}_{\mathrm{gs}}\) characteristics curve, can be expressed as [28]

In a SET, the gate to source voltage is responsible for shifting the Id-Vds curve vertically, keeping the nature of the curve intact. Taking this factor into account, the novel components, g1 and g2, are expressed as

Initially the basic structure of the equation is obtained using curve fitting technique. Though the values of other parameters cannot be calculated directly, we can get an approximate range through the nomenclature of these parameters. CVp, as the name implies is a peak voltage value which represents the maximum range of the Coulomb blockade region. CI2 is related to the current in nano range. CR1 and CR2 are related to the tunnel junction resistance which should be in mega range. Initially, the values for these parameters are taken from Ref. [28] and thereafter different parameter values are obtained using parametric analysis of the designed model. According to the orthodox theory of single electron tunneling, the Coulomb energy or the charging energy must be bigger than the thermal energy [20], and it can be expressed as

where, \(\hbox {E}_{\mathrm{C}}\) is the Coulomb energy, \(\hbox {K}_{\mathrm{B}}\) is the Boltzmann constant and T is the operating temperature in Kelvin. C is the total capacitance of the island and is calculated as

Here \(\hbox {C}_{\mathrm{g}}\) and \(\hbox {C}_{\mathrm{j}}\) are the gate capacitance and junction capacitance respectively. If the thermal energy becomes greater than the charging energy, electron tunneling occurs due to thermal fluctuations in energy thereby causing instability of the circuit. From (5), it can be observed that the charging energy is totally dependent on the overall capacitance of the respective island, and the maximum operating temperature is inversely proportional to the total capacitance of the island. The sub circuit code for the proposed macro model circuit, which also includes the parameter declaration of the model, is given in Fig. 2.

In the code, CF1, CI2, CR1, CR2, CR3, CR4, and CVp are macro model parameters; \(\hbox {K}_{1}\) and \(\hbox {K}_{2}\) are scaling factors. The components g1 and g2 represent two voltage control current sources which are the main design component of the design. Assuming the value of CF1 as 40 [28], the value of \(\hbox {C}_{\mathrm{g}}\) is calculated as 3.2 aF. Again from (4), it is seen that \(\hbox {C}_{\mathrm{g}}\) directly controls the operating temperature of the SET. So, a temperature controlling parameter is incorporated in the proposed sub circuit code, by including CF1. The code shows the dependency of the two current sources, g1 and g2, on the gate to source voltage. k1 and k2 are scaling factors for adjusting the slope of the I–V graphs .

3 Simulation results

The code is executed in Tanner SPICE environment using the following parameters: Cg\(\,=\,\)3.2 aF, Cj\(\,=\,\)1.6 aF, T\(\,=\,\)30 K [28]. The values for the fitting parameters are chosen as CF1\(\,=\,\)40, CVp\(\,=\,\)0.02, \(\hbox {CI}2=0.2 \times 10^{-9}, \hbox {CR}1=300\times 10^{+6}\) and \(\hbox {CR}2=220\times 10^{+6}\). The variation of drain current (\(\hbox {I}_{\mathrm{ds}})\) with \(\hbox {V}_{\mathrm{gs,}}\), considering \(\hbox {V}_{\mathrm{ds}}\) as a parameter is shown in Fig. 3. It can be observed that drain current oscillates periodically for a constant value of \(\hbox {V}_{\mathrm{ds}}\). This characteristic is known as the Coulomb blockade oscillation or single electron current oscillation which is considered as one of the most important property of SET.

The \(\hbox {I}_{\mathrm{ds}}\)–\(\hbox {V}_{\mathrm{ds}}\) characteristics plotted using our proposed modified macro-model is shown in Fig. 4. From the characteristics curve, the Coulomb blockade region can be identified for drain to source voltage range of \(-\)20 to 20 mV. The drain to source voltage on both side of the Coulomb blockade region represents the non-Coulomb blockade features. Ideally, the drain current is zero in the Coulomb blockade region but in reality, a very small amount of current flows due to tunneling of thermally activated carriers at small finite temperatures.

This justifies the small variation of the drain current in the Coulomb blockade region as visible in Fig. 4. With increase in Vgs the graph shifts along the Y-axis. This shift is also observed in case of Yu’s model, but the nature of the shift was not fixed there. If we go on increasing \(\hbox {V}_{\mathrm{ds}}\) beyond Coulomb blockade region, the number of electrons charging the island increases one-by-one. Since we have considered the junction to be symmetric, the current increases linearly outside the Coulomb blockade region.

Comparison of the \(\hbox {I}_{\mathrm{ds}}\)–\(\hbox {V}_{\mathrm{ds}}\) characteristics of the proposed model, for both Coulomb blockade and non-Coulomb blockade regions, with Yu’s model, Wu and Lin’s model, SIMON, MIB model and our previous model. The parameters for other models are \(\hbox {R}_{\mathrm{D}}= \hbox {R}_{\mathrm{S}} =100\hbox {M}\Omega \), \(\hbox {C}_{\mathrm{TD}}= \hbox {C}_{\mathrm{TS}}=1.6\) aF, and T\(\,=\,\)30 K. The parameters for our macro model are CF1\(\,=\,\)40, \(\hbox {C}_{\mathrm{VP}} = 0.02, \hbox {CI}2 = 0.5*10^{-9}, \hbox {CR}1 = 300*10^{+6}, \hbox {CR}2 = 10*10^{+6}\). The value of RG is taken as 100*10\(^{9}\,\Omega \)

The \(\hbox {I}_{\mathrm{ds}}\)–\(\hbox {V}_{\mathrm{ds}}\) characteristics of the proposed model, for both Coulomb blockade and non-Coulomb blockade regions, are compared with other models in Fig. 5. It can be observed that the simulation result of our model closely matches with that of popular simulation software SIMON. The values of the parameter taken as Rj\(\,=\,\)100 M\(\Omega \), Cj\(\,=\,\)3.2 aF and T\(\,=\,\)30 K. CF1\(\,=\,\)40, \(\hbox {C}\hbox {V}_{\mathrm{P}} = 0.02, \hbox {CI}2 = 0.2*10^{-9}, \hbox {CR}1 = 300*10^{+6}, \hbox {CR}2 = 220*10^{+6}\) and \(\hbox {V}_{\mathrm{gs}} = 0\) V. It is also observed that the proposed model covers the maximum range of the drain current.

4 Single electron inverter

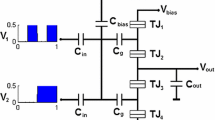

To check the validity of the proposed model, an inverter is designed using the proposed model as shown in Fig. 6. The transient response of the single electron inverter has been tested by applying an input pulse to its input. The output wave form is found to be an exact opposite replica of the input and it is shown in Fig. 7.

The variation of voltage transfer characteristics of the designed SET inverter for different values of RG is depicted in Fig. 8. The output voltage is found to increase with increasing value of RG. No significant changes are observed in the characteristic curve for RG above 100 \(\hbox {G}\Omega \), therefore we have restricted the value of RG to 100 \(\hbox {G}\Omega \). The voltage transfer characteristics with \(\hbox {RG}=100\,\hbox {G}\Omega \) and \(\hbox {V}_{\mathrm{dd}}=0.03\,\hbox {V}\) is shown separately in Fig. 9 to calculate the corresponding noise margins [high noise margin \((\hbox {NM}_{\mathrm{H}})\) and low noise margin \((\hbox {NM}_{\mathrm{L}})]\) [32]. We have further investigated the effect of parameter RG on the noise margin of the inverter cell as it has the maximum effect on the SET logic robustness compare to other parameters.

Transient characteristic of the SET inverter circuit. Here solid line and dashed line represents input waveform and output waveform respectively. The parameters for the macro model is CF1\(\,=\,\)40, \(\hbox {C}\hbox {V}_{\mathrm{P}} = 0.02, \hbox {CI}2 = 0.2*10^{-9}, \hbox {CR}1 = 340*10^{+6}, \hbox {CR}2 = 100*10^{+6}\). The value of RG is taken as 100*10\(^{9}\,\Omega \)

The variation of high/low noise margin with different values of RG can be obtained from Fig. 10. It can be seen from the plot that high/low noise margin improves with increasing values of RG up to \(100\,\hbox {G}\Omega \) after which it gets saturated. By evaluating the overall performance, it can be said that the designed inverter shows sufficient accuracy in both static and dynamic regimes. The gain of the inverter cell for different input voltage has been given in Fig. 11. It is observed that, in the transition region the gain decreases rapidly in both side of the transition point, otherwise the gain remains almost constant.

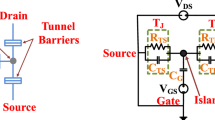

Schematic diagram of the multi peak NDR circuit with two cross coupled single electron transistors and one current source used for biasing the transistor T1. The parameter values used are CF1\(\,=\,\)40, \(\hbox {C}\hbox {V}_{\mathrm{P}} = 0.02, \hbox {CI}2 = 0.2*10^{-9}, \hbox {CR}1 = 270*10^{+6}, \hbox {CR}2 = 70*10^{+6}\) (for T1) and CR1\(\,=\,\)280*10\(^{+6}\), CR2\(\,=\,\)280*10\(^{+6}\) (for T2). The value of RG is taken as 10*10\(^{8}\,\Omega \)

Characteristics of the designed multi peak NDR circuit for different bias current simulated in SPICE environment. The parameter values used are CF1\(\,=\,\)40, \(\hbox {C}\hbox {V}_{\mathrm{P}} = 0.02\), CI2\(\,=\,\)0.5*10\(^{-9}\), CR1\(\,=\,\)270*10\(^{+6}\), CR2\(\,=\,\)70*10\(^{+6}\) (for T1) and CR1\(\,=\,\)280*10\(^{+6}\), CR2\(\,=\,\)280*10\(^{+6}\) (for T2). The value of RG is taken as 10*10\(^{8}\,\Omega \)

5 Multiple peak NDR circuit

Ultra high speed and reducing circuit complexity are the two important properties of multi peak NDR circuits [33–35], which makes it suitable for designing multiple values memory circuits, frequency multiplier and multiple valued logic circuits. We have designed a multi peak NDR circuit based on single electron transistor [7]. The designed circuit is consisting of two cross coupled SETs as shown in Fig. 12. The transistor T1 controls the current flowing through T2 by creating a feedback loop. Clear peaks are observed in the I–V characteristics of the designed circuit as depicted in Fig. 13. It can be noticed that the height of the peaks increases with increase in bias current. The further investigation is laid upon the effect of RG on the I–V characteristics of the designed multi peak NDR circuit as shown in Fig. 14. with increase in RG the height of the peaks are increasing and it has been observed that beyond \(1\,\hbox {G}\Omega \), the effect of RG starts diminishing and after \(50\,\hbox {G}\Omega \) there is no effect at all.

Effect of Rg on the characteristics of the multi peak NDR circuit. The parameter values used are CF1\(\,=\,\)40, \(\hbox {C}\hbox {V}_{\mathrm{P}} = 0.02\), CI2\(\,=\,\)0.5*10\(^{-9}\), CR1\(\,=\,\)270*10\(^{+6}\), CR2\(\,=\,\)70*10\(^{+6}\) (for T1) and CR1\(\,=\,\)280*10\(^{+6}\), CR2\(\,=\,\)280*10\(^{+6}\) (for T2). The value of the bias current is 14 nA

6 Conclusion

An improved version of our previous macro model of SET suitable for SPICE based simulation of single electron circuits is proposed by incorporating two voltage controlled current sources and some scaling factors. The proposed model was simulated in SPICE environment. The simulation results clearly demonstrate the Coulomb blockade and Coulomb oscillation characteristic of the SET. It was found that our model overcomes the drawbacks of all existing models. Our model also agrees well with the results obtained from monte carlo based simulator SIMON. The proposed SET model is used to design an inverter cell. Simulation results of the inverter are promising enough to justify the validity of the proposed model for designing SET based circuits. The investigation about the effect of the parameters reveals that RG has maximum effect on the noise margin of the inverter cell and the noise margin gets affected by the values of the RG up to \(100\,\hbox {G}\Omega \). The corresponding voltage transfer characteristic and noise margin plots are also shown to validate our proposal. Prominent peaks are observed in the simulation results of the designed multi peak NDR circuit. It is observed that with increase in bias current and RG the height of the peaks increases.

References

Grabert, H., Devoret, M.H. (eds.): Single Charge Tunneling Coulomb Blockade Phenomena in Nanostructures. Plenum press, New York and London (1992)

Gordon, D.G., Montemerlo, M.S., Love, J.C., Opiteck, G.J., Ellenborgen, J.C.: Overview of nanoelectronic devices. Proc. IEEE 85, 521 (1997)

Ionescu, A.M., Declercq, M.J., Mahapatra, S., Banerjee, K., Gautier, J.: Few Electron devices: towards hybrid CMOS-SET integrated circuits. In: Proceedings \(39^{{\rm th}}\)Design Automation Conference. New Orleans (2002)

Jain, A., Singh, N.B., Sarkar, S.K.: A new compact analytical model of single electron transistor for hybrid SET-MOS circuits. Solid State Electron. 104, 90 (2015)

Jana, B., Jana, A., Sing, J.K., Sarkar, S.K.: Performance of multigate single electron transistor in wide temperature range and 22 nm hybrid technology. J. Nanoelectron. Optoelectron. 9, 357 (2014)

Chen, R.H., Korotkov, A.N., Likharev, K.K.: Single-electron transistor logic. Appl. Phys. Lett. 68, 1954 (1996)

Boubaker, A., Sghaier, Na, Trodi, M., Kalbossi, A., Boboux, N., Souifi, A.: A new SIMPLORER model for single-electron transistors. Microelectron. J. 38, 894 (2007)

Mahapatra, S., Banerjee, K., Pegeon, F., Ionescu, A.M.: A CAD framework for co-design and analysis of CMOS-SET hybrid integrated circuits. In: Proceedings of ICCAD. SanJose (2003)

Mahapatra, S., Vaish, V., Wasshuber, C., Banerjee, K., Ionescu, A.M.: Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design. IEEE Trans. Electron. Devices 51, 1772 (2004)

Durrani, Z.A.K.: Single Electron Devices and Circuits in Silicon. Imperial College Press, London (2010)

Wasshuber, C.: Computational Single-Electronics. Springer, New York (2001)

Chaohong, H., Cotofana, S.D., Jianfei, J., Qiyu, C.: Analog-to-digital converter based on single-electron tunneling transistors. IEEE Trans. VLSI Syst. 12, 1209 (2004)

Gerousis, C., Grepiotis, A.: Reconfigurable gate array architecture for logic functions in tunneling transistor technology. Microelectron. J. 44, 706 (2011)

Chen, Y.C., Wang, C.Y., Huang, C.Y.: Verification of reconfigurable binary decision diagram-based single-electron transistor arrays. IEEE Trans. Comput. Aided Des. Integr. Circuit. Syst. 32, 1473 (2013)

Sahafi, A., Moaiyeri, M.H., Navi, K., Hashemipour, O.: Efficient single-electron transistor inverter-based logic circuits and memory elements. J. Comput. Theor. Nanosci. 10, 1171 (2013)

agarwal, P.B., Kumar, A.: Design and simulation of octal-to-bi nary encoder using capacitive single-electron transistors (C-SETs). Microelectron. J. 42, 96 (2011)

Wasshuber, C.: Single-electronics-how it works: how it’s used—how it’s simulated. In: Proceedings of the International Symposium on Quality Electronic Design. San Jose (2002)

Samanta, D., Ghosh, A., Sarkar, S., Sarkar, S.K.: Design and simulation of a sequence generator using single electron devices and hybrid architecture. J. Nanoelectron. Optoelectron. 5, 1 (2010)

Abutaleb, M.M.: A new static differential design style for hybrid SET-CMOS logic circuits. J. Comput. Electron. 14, 329 (2015)

Jana, A., Basanta Singh, N., Sing, J.K., Sarkar, S.K.: Design and simulation of hybrid CMOS-SET circuits. Microelectron. Reliab. 53, 592 (2012)

Sui, B., Fang, L., Chi, Y., Zhang, C.: Nano-reconfigurable cells with hybrid circuits of single-electron transistors and MOSFETs. IEEE Trans. Electron. Devices 57, 2251 (2010)

Koppimen, P.J., Stewart, M.D., Zimmerman, M.J.: Fabrication and electrical characterization of fully CMOS-compatible Si single-electron devices. IEEE Trans. Electron. Device. 60, 78 (2013)

Jain, A., Singh, N.B., Ghosh, A., Sarkar, S.K.: Stability and reliability analysis of hybrid CMOS-SET circuits: a new approach. J. Comput. Theor. Nanosci. 11, 2519 (2014)

Wei, W., Han, J., Lombardi, F.: Design and evaluation of a hybrid memory cell by single-electron transfer. IEEE Trans. Nanotechnol. 12, 57 (2013)

Yu, Y.S., Hwang, S.W., Ahn, D.: Transient modelling of single-electron transistors for efficient circuit simulation by SPICE. IEE Proc. Circuit Device. Syst. 152, 691 (2005)

Boubaker, A., Troudib, M., Sghaierb, N., Souifia, A., Babouxa, N., Kalboussib, A.: A spice model for single electron transistor applications at low temperatures: inverter and ring oscillator. Proceedings of International Conference on Design & Technology of Integrated Systems in Nanoscale Era. Tozeur (2008)

Wei, W., Han, J., Lombardi, F.: Robust HSPICE modeling of a single electron turnstile. Microelectron. J. 45, 394 (2014)

Yu, Y.S., Hwang, S.W., Ahn, D.: Macromodeling of single-electron transistors for efficient circuit simulation. IEEE Trans. Electron. Device. 46, 1667 (1999)

Wu, Y.L., Lin, S.T.: An improved single electron transistor model for SPICE application. Nanotechnology 3, 321 (2003)

Karimian, M.R., Dousti, M.: A new SPICE macro-model for the simulation of single electron circuits. J. Korean Phys. Soc. 56, 1202 (2001)

Jain, A., Ghosh, A., Singh, N.B., Sarkar, S.K.: A new SPICE macro model of single electron transistor for efficient simulation of single-electronics circuits. Analog Integr. Circuit Signal Process. 82, 653 (2015)

Rabey, J., Chandrakasan, A., Nikolic, B.: Digital Integrated Circuits a Design Perspective. Prentice Hall, Englewood Cliffs (2003)

Gan, K.J.: Novel four-peak or five-peak current-voltage characteristics for three negative differential resistance devices in series. Solid-State Electron. 44(9), 1597–1602 (2000)

Gan, K.J.: The low-high-low I V characteristics of five to seven peaks based on four NDR devices. IEEE Trans. Electron. Device. 48(8), 1683–1687 (2001)

Shin, S., Kim, K.R.: Novel design of multiple negative-differential resistance (NDR) device in a 32 nm CMOS technology using TCAD. Proceeding of International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 316–319 (2013)

Acknowledgments

Subir Kumar Sarkar thankfully acknowledges the financial support obtained from UGC UPE-Phase II project, Jadavpur University.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghosh, A., Jain, A., Singh, N.B. et al. A modified macro model approach for SPICE based simulation of single electron transistor. J Comput Electron 15, 400–406 (2016). https://doi.org/10.1007/s10825-015-0790-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0790-1