Abstract

This paper presents a 120-GHz wideband phase-compensated variable gain amplifier (VGA) with a p-type metal–oxide–semiconductor (PMOS) switch using a 40-nm CMOS process. By applying a PMOS switch to the common source (CS) amplifier, the gain of the CS amplifier can be controlled by as much as 6.1 dB with 2° phase variations in 15.1-GHz bandwidth ranging from 100.9 to 115 GHz. The measured gain and 3-dB bandwidth of the VGA are 19.1 dB and 33.8 GHz for high-gain state, and 13 dB and 44.2 GHz for low gain state, respectively. Meanwhile, the DC power consumption in the high-gain state is 45 mW, and the OP1dB is −2.7 dBm.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Recently, wireless systems that use millimeter wave and sub-terahertz spectrum have rapidly evolved [1,2,3]. For these applications, a variable gain amplifier (VGA) is needed to improve the dynamic range. A VGA is also used as a main component of the vector-summing phase shifter [4, 5]. In addition, when a VGA is applied to a phased array for a beam-tapering function, the multi-path effect caused by the side lobe level (SLL) can be improved by reducing the SLL [6]. Moreover, controlling the polarization of an antenna by installing a VGA on each port of a dual-polarized antenna can improve the signal-to-noise ratio of the receiver [7, 8]. In particular, in the case of a phase shifter, tapered beam former, and polarization control unit for high-speed communication, minimizing the phase variation is important to prevent distorted radiation pattern or poor cross-polarization.

For these applications, a VGA is typically realized using a cascode topology. For instance, gain-control mechanisms are implemented using a PMOS switch [9], current-splitting technique [10], a variable-transistor transconductance [11], and a current-steering technique [12,13,14,15,16]. The varactor control technique [17] is also applied to a cascode amplifier to achieve a variable-gain function. However, the cascode amplifier suffers from several drawbacks compared with a CS topology, including the following: (1) narrow bandwidth owing to the rapidly changing input/output impedance with frequency and (2) low linearity by assuming that the VDD voltage is constant. Therefore, the CS topology is advantageous in this respect. However, CS VGAs, which exhibit wideband characteristics with minimized phase variation, have not been reported so far.

In this study, we demonstrate a wideband and compact 120-GHz phase-compensated VGA with a p-type metal–oxide–semiconductor (PMOS) switch. In sect. 2, analysis of the gain-control mechanism using the PMOS switch is presented. In sect. 3, the measurement results are provided, and the conclusion of this work is presented in sect. 4.

2 Phase-Compensated VGA with PMOS Switch

The 120-GHz VGA is designed for wireless chip-to-chip communication, and the detailed scenario is described in [18,19,20]. In the current work, the phase-compensated technique has been recently applied to CS VGA to obtain a flat gain in high gain (HG) and low gain (LG) modes and low phase variation.

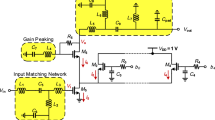

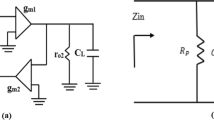

Figure 1 shows the schematic of the 120-GHz VGA with a PMOS switch. The inter-stage matching network is designed with a single parallel inductor for low insertion loss. For the variable-gain function, the PMOS switch is installed parallel to the inductor from the 4th to the 8th stages. To prevent degradation of the noise figure of the overall amplifier, the PMOS switch is not connected from the 1st to the 3rd stages. The PMOS switches are connected in parallel to the inter-stage matching inductor. Meanwhile, the source is connected to the VDD, and the drain is connected to the drain of the NMOS amplifier. By turning the PMOS switch on and off, the overall gain of the amplifier is controlled by adjusting the parallel resistance of the PMOS. The variables of the VGA are listed in Table 1. Figure 2 shows the schematic and equivalent circuit of the PMOS switch when the latter is turned on and off. The equivalent circuit can be modeled as a parallel resistor and parallel capacitor. When the switch is turned off, the switch operates as an open circuit. When the switch is turned on, the turn-on resistance (Ron) is considerably smaller than the turn-off resistance (Roff). The parallel resistance contributes to the reduction in the unit stage gain of the amplifier due to increment of the damping factor of the amplifier (ζ).

Table 2 lists the simulated real and imaginary impedances and calculated resistance and capacitance when the PMOS transistor is on and off at 120-GHz. Ron, Roff, Con, and Coff are calculated as 186 Ω, 535 Ω, 3.5 fF, and 2.7 fF, respectively, where Ron is approximately three times smaller than Roff.

Generally, the gain of the nth-stage amplifier (Gn(s)) is expressed as follows:

where s = jω, An = gmLn, \( {\omega}_n\left(=\sqrt{\frac{1}{L_n\left({C}_{n,n+1}+{C}_{\mathrm{PMOS}}\right)}}\right) \) is the resonant frequency, and ζn is the damping factor. Ln and CPMOS are inductance of the nth stage of the amplifier and parasitic capacitance of the PMOS switch, respectively. The damping factors in the HG and LG modes are given by

where Coff and Con is parasitic capacitance of the high-gain mode and low gain mode of the PMOS transistor, respectively. Rn, n + 1 is equivalent resistance of the nth stage of the amplifier.

From Eqs. (1) to (3), the relative gain (\( \frac{G_{n, LG}(s)}{G_{n, HG}(s)}\Big) \) of the nth stage is expressed as follows:

In the LG mode, the gain is dominantly reduced because ζn, LG is higher than ζn, HG due to the additional parallel resistance from the PMOS switch. Figure 3 shows the simulated relative gain and phase variation in the LG and HG modes in the 4th, 5th, 6th, 7th, and 8th stages. The relative gain and phase variation represent the gain and phase variation between the HG and LG modes, respectively. From Eq. (4), the relative gain at the nth stage at frequency ωn is ζn, LG/ζn, HG (= 10log(ζn, LG/ζn, HG) dB). At ωn ≪ ω and ωn ≫ ω, the relative gain converges to one (= 0 dB). Therefore, the relative gain at the nth stage monotonically decreases from the DC frequency and monotonically increases after ωn. The VGA is designed to have a flat gain in the LG and HG modes by setting the gain-variation stage at low and high frequencies. From Eq. (4), when ω is substituted to ωn + ∆ωn, the phase variation in the nth stage (∆θn) is given as

Equation (5) shows that, if ∆ωn is negative, ∆θn is positive. In contrast, if ∆ωn is positive, ∆θn is negative. In the 7th and 8th stages, because the center frequency of 120 GHz is larger than the resonating frequency in the seventh stage, ∆ω7 and ∆ω8 are positive, and ∆θ7 and ∆θ8 are negative. On the other hand, ∆θ4, ∆θ5, and ∆θ6 are positive. In this manner, the VGA is designed by applying the phase-compensated technique so that the phase variation approaches zero near the center frequency.

Figure 4 shows gain frequency response with continuous bias tuning. It is shown that gain is continuously controlled by tuning the control bias voltage. In this work, only two states (Vctrl = 1 and Vctrl = 0) are measured to be applied for polarization control unit.

3 Measurement Results

Figure 5 shows the fabricated 120-GHz VGA. The amplifier is fabricated using the 40-nm CMOS process. The addition of the PMOS switches does not affect the total chip area, and the total chip area is 450 μm × 500 μm. The total DC power consumption of the amplifier is 45 mW. Figure 6 shows the S11, S22, and gain of the amplifier. The measured S11 is less than −9 dB from 104.9 to 136.2 GHz, whereas the measured S22 is less than −9 dB from 93.3 to 141.4 GHz. Furthermore, the measured peak gains are 19.1 dB in the HG state and 13 dB in the LG state. The 3-dB gain bandwidths are 33.8 GHz in the HG state and 40.2 GHz in the LG state. The discontinuity at 110 GHz occurs because the S-parameter from 90 to 150 GHz is measured by a W-band (from 90 to 110 GHz) and D-band (from 110 to 150 GHz) vector network analyzer (VNA). Figure 7 shows the simulated and measured P1dB for the HG and LG states of the VGA. For the HG and LG states, the OP1dB values are −2.7 and −2.6 dBm, respectively. Figure 8 shows the simulated and measured phase difference of the VGA. The phase variation of the amplifier is 15.5° within the 3-dB-gain bandwidth (102.9–136.7 GHz). If the VGA is applied to polarization control unit [9], the cross-polarization could be lower than at least −11.46 dB with 15.5° phase variation. Moreover, the measured phase variation is less than 2° in the 15.1-GHz frequency band that ranges from 100.9 to 115 GHz by implementing the phase-compensated technique. Figure 9 shows the simulated and measured group delay in the HG and LG states. The similar group delay characteristics are revealed compared to [21], and measured group delay is lower than 50 ps. Figure 10 shows the simulated and measured noise figures in the HG and LG states. The measured average noise figures are 8.5 and 8.9 dB in the HG and LG modes, respectively. Figure 11 shows the simulated IIP3 values of the HG and LG states. The simulated IIP3 values are −17.5 and dB −13.9 dB in the HG and LG modes, respectively. Table 3 lists the performance of the CMOS VGAs in the millimeter-wave frequencies. The CS amplifier with a PMOS switch exhibits the widest bandwidth than the other reported VGAs owing to the application of the CS topology. The presented VGA is advantageous for system integration because it uses a relatively small area compared with the number of stages.

4 Conclusion

A wideband 120-GHz phase-compensated VGA with a PMOS switch is presented. The measured gain and 3-dB bandwidth of the VGA are 19.1 dB and 33.8 GHz, respectively, while consuming DC power of 45 mW in the HG state. The OP1dB is −2.7 dBm, and the phase variation between the HG and LG states are 15.5° and 2° in the 3-dB gain bandwidth and 15.1-GHz frequency band, respectively.

References

R. Wu, et. al., A 42Gb/s 60GHz CMOS transceiver for IEEE802.11ay in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 248–250, Feb. 2016

K. K. Tokgoz1, et. al., A 56Gb/s W-band CMOS wireless transceiver in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 242–244, Feb. 2016

K. Okada, et. al., A 64-QAM 60GHz CMOS transceiver with 4-channel bonding, in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 346–348, Feb. 2014

D. Pepe and D. Zito, Two mm-wave vector modulator active phase shifters with novel IQ generator in 28nm FDSOI CMOS, IEEE J. Solid-State Circuits, vol. 52, no. 2, pp.344-356, Feb. 2017.

S. Zihir, O. Gurbuz, A. Kar-Roy, S. Raman and G. Rebeiz, 60-GHz 64- and 256-elements wafer-scale phased-array transmitters using ull-reticle and subreticle stitching techniques, IEEE Trans. Microwave Theory and Tech, vol. 64, no. 12, pp. 4701-4719, Dec. 2016.

J. Lee, T. Jang, G. Park, H. Lee, C. Byeon and C. Park, A 60-GHz four-element beam-tapering phased-array transmitter with a phase-compensated VGA in 65-nm CMOS, IEEE Trans. Microwave Theory and Tech, vol. 67, no. 7, pp. 2998-3009, July 2019.

S. Bowers, A. Safaripour, and A. Hajimiri, Dynamic polarization control, IEEE Journal of Solid-State Circuits, vol. 50, no. 5, pp. 1224-1235, May. 2015.

T. Jang, K. Hwang, G. Park, H. Kim, H. Bae, C. Byeon and C. Park, A 60-GHz wideband, low-power, active receiving antenna with adjustable polarization for SNR improvement, Trans. Antenna and Propag., vol.67, iss.12, pp.2796-7303, Dec.2019.

Y. Cheng, Y. Chen and H. Lu, 38GHz low power variable gain LNA using PMOS current-steering device and Gm-boost technique, Proceedings of 2018 Asia-Pacific Microwave Conference(APMC2018).

K. L. Fong, Dual-band high-linearity variable-gain low-noise amplifiers for wireless applications, in IEEE Int. Solid-State Circuits Tech. Dig., pp. 224–225, Feb. 1999.

C. H. Wu, C. S. Liu, and S. L. Liu, A 2-GHz CMOS variable-gain amplifier with 50-dB linear-in-magnitude controlled gain range for 10 GBase-LX4 ethernet, in IEEE Int. Solid-State Circuits Tech.Dig., pp. 484–541, Feb. 2004.

F. Padovan, M. Tiebout, A. Neviani and A. Bevilacqua, A 15.5-39GHz BiCMOS VGA with phase shift compensation for 5G mobile communication transceivers, ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference. pp. 363–366, Sep. 2016

J. Xiao, I. Mehr, and J. Silva-Martinez, A high gain control range CMOS variable gain amplifier for mobile DTV tuner, IEEE J. Solid-State Circuit, vol. 42, no. 2, pp. 292–301, Feb. 2007.

C.-C. Kuo, Z.-M. Tsai, J.-H. Tsai, and H.Wang, A 71–76 GHz CMOS variable gain amplifier using current steering technique, in IEEE RFIC Symp. Dig., pp. 609–612, Jun. 2008.

Y. Wang, C. Chen, Y. Wu and H. Wang, An E-band variable gain low noise amplifier in 90-nm CMOS process using body-floating and noise reduction techniques in Proceedings of the 13th European Microwave Integrated Circuit Conference (EuMIC), Sep. 2018.

H. Yeh, S. Aloui, C. Chiong and H. Wang, A wide gain control range V-band CMOS variable-gain amplifier with built-in linearizer, IEEE Trans. Microwave Theory and Tech, vol. 61, no. 2, pp. 902-913, Feb. 2013.

Y. Kim and Y. Kwon, A 60 GHz Cascode variable-gain low-noise amplifier with phase compensation in a 0.13 CMOS technology, IEEE Microw. and Wireless Components Lett., vol. 22, no. 7, pp. 372-374, July 2012.

T. Jang, D. Kang, S. Kim, C. Lee, S. Jun, H. Park, J. Kim, and C. Park, Wideband 120-GHz I/Q receiver with baseband equalizer, IEEE Journal of Solid State Circuit, accepted

C. Lee, S. Kim, H. Son, D. Kang, J. Kim, C. Byeon, and C. Park, A 120 GHz I/Q transmitter front-end in a 40 nm CMOS for wireless chip to chip communication, 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), pp. 192-195, June 2018.

T. Jang, H. Kim, S. Kim, D. Kang and C. Park, 120 GHz on-board wireless link using Y-shaped open-ended micro-strip antenna, IEEE Antenna and Wireless Propagation Letters, vol. 18, no. 10, pp. 2165-2169, Oct. 2019.

T. Jang, K. Jung, J. Kang, C. Byeon, and C. Park, 120-GHz 8-Stage Broadband Amplifier With Quantitative Stagger Tuning Technique, IEEE Transaction on Circuit and System I : Regular Papers, vol. 67, no.3, pp.785-796, Mar. 2020.

Funding

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (Ministry of Science, ICT and Future Planning) (No. 2017R1A2B3009294), and the National Research Foundation of Korea (NRF) through the Korea Government, Ministry of Science, Information and Communications Technology (ICT) and Future Planning (MSIP), under Grant 2019R1C1C1003918.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jang, T.H., Kim, S.H., Byeon, C.W. et al. Wideband Phase-Compensated VGA with PMOS Switch in 40-nm CMOS for 120-GHz Band. J Infrared Milli Terahz Waves 42, 514–524 (2021). https://doi.org/10.1007/s10762-021-00794-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10762-021-00794-7