Abstract

In this paper, the design challenges of the injection-locked oscillator (ILO)-based phase shifter are reviewed and analyzed. The key design considerations such as the operating frequency, locking range, and linearity of the phase shifters are analysed in detail. It is possible to optimize the phase shifter in certain parameters such as ultra-low power while meeting the requirements of a certain system. As a design example, a K-band phase shifter is implemented using a commercial 0.13 μm CMOS technology, where a conventional LC tank based topology is implemented but optimised with a good balance among power consumption, working range, sensitivity, and silicon area, etc. Measurement results show that the proposed phase shift is able to work at 22–23.4 GHz with a range of 180∘ while consuming 3.14 mW from a 1.2 V supply voltage.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The continuously increasing demands for higher data rate have increased attentions to phased arrays for nowadays communication systems. At the expense of hardware complexity, a higher signal-to-noise ratio is achievable in such a system where a high-performance phase shifter is a key building block to combine multi-phase signals effectively [21, 25, 31]. As for circuit implementation, with the rapid progress of silicon based radio-frequency integrated circuits (RFICs), it is possible to implement a fully-integrated phase-array system with low power consumption by taking the advantage of the highest level of integration using the CMOS technology [21, 25, 31]. Phase shifters with different topologies such as passive reciprocal networks type using transmission lines [21, 25, 31] , lumped elements networks [2, 17], vector modulated type [3, 29, 30], and other topologies [18, 24], have been extensively reported. And recently, many work implemented in advanced CMOS technology, with lower power or high-frequency operations has been reported in [1, 15, 27]. Unfortunately, a phase shifter with high frequency, accurate phase control, small silicon area, low power consumption, low loss variation within the entire working frequency range, etc., remains a great challenge. The design strategy of a phase shifter should be determined based on different applications. For example, an active vector modulator phase shifter exhibits high gain at the cost of high DC power and complexity with additional digital control circuits. By contrast, passive phase shifters usually exhibit better linearity without DC power consuming but with a certain insert loss which requires additional link budget in a communication system. In addition, the passive components in the passive phase shifter, such as transmission lines occupy a considerably large silicon area, making it less attractive in CMOS fully-integrated system. The tuning mechanism of the phase shift is another key consideration, vector summer can only provide certain phase shifts with several-bit of resolution, e.g., a 4-bit 360∘ phase shifter in 22.5∘ steps, using digital switches [27] (e.g., 22.5∘ for 3-bit operation, using digital switches). The alternative solution, a continuously varying phase shifter is able to work at a limited range only. It is therefore not possible to conclude an uniform solution to a communication system. But considering the rapid progress of millimetre wave range phase array mobile system with a high level of integration, it is of a great interest if the phase shifter can be implemented with acceptable phase accuracy, small silicon area and low power consumption. In this paper, a K-band phase shifter is presented to meet these requirements. The theoretical analysis of the phase shift in a LC tank based oscillator is presented, followed by the optimisation of the performance matrix as well as the silicon verification of the prototype in a commercial 0.13 μ m CMOS technology.

2 Design Consideration

In a K-band fully-integrated mobile communication system, the silicon area and power consumption become the major design considerations once the accuracy of the phase shifter is secured. The passive design is less attractive due to large silicon areas occupied by the passive devices [21]. The large power consumption and limited resolutions in a vector summer based phase shifter are the major drawbacks. As a design example, a K-band vector-sum phase shifter with a resolution of 22.5∘ requires a total power consumption of 25.2 mW as reported in [23]. Phase shifts based on injection locked voltage controlled oscillators have been reported as a good candidate to solve these issues [11, 26]. They has been widely used in designing quadrature (fix phase of 90∘) oscillator [9, 10, 14] or phase shifters [1, 4, 11, 26, 27]. Unfortunately, the oscillator is sensitive to process, voltage, and temperature (PVT) variations. The total linear phase tuning range is thus very limited and unstable. It is therefore of a great importance to perform a detailed analysis of this topology and to perform optimizations accordingly.

2.1 Physical Model of the Injection Locked Oscillator

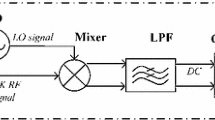

A simplified scheme of injection locked oscillator (ILO) can be modeled as an oscillator locked to an external signal source, as shown in Fig. 1.

The circuit works as a free running oscillator without an input signal. But the oscillator will tracks the input frequency at a certain frequency range close to its self-resonant frequency, which is called injection locking. For an oscillator with the free running frequency of ω 0, which is locked in with an input signal I inj (at the frequency of ω inj), as shown in Fig. 2, the working condition can be derived as follows.

As illustrated in Fig. 3,

The sum of the vectors of I inj and I osc is I out [22]

It is assumed that the angle between I inj and I osc is 𝜃 and the angle between I out and I osc is φ, the relationship between 𝜃 and φ can be written as.

According to Eq. 1,

When I inj ≪ I osc , then

Considering Z(ω) represents the impedance of the resonance circuit, then

Where R L is the loss of the tank and ω 0 = 1L C is the resonant frequency of the tank.

Since ω is close to ω 0, so

The phase shift φ of the tank is given as:

Considering \(Q_{\text {{ext}}}=\frac {L\omega _{\text {{0}}}}{R_{\text {{L}}}}\) to be the external quality factor, Eq. 9 can be re-written as

When I inj ≪ I osc, φ is small enough to make sinφ ≈tanφ,

The phase shift between injected signal and output, 𝜃 − φ ≈ 𝜃 (at the extreme case that φ is so small that can be ignored), can now be approximated as

Supposing the injection source is a stable oscillation source, function of 𝜃 is relevant to ω 0, Q ext and I osc.

The phase shift depends on at least three design parameters. It is possible to change ω 0, Q ext, or I osc to obtain the phase shift as suggested in Eq. 13. Given a constant Q ext and ω 0, e.g., Q ext = 10 and f = 24 GHz, the phase shift vs. I osc can be illustrated in Fig. 4. Moreover, Fig. 5 suggests that phase shift is strongly linear over I osc/I inj if Δω = ω − ω 0, the frequency shift, is small enough, which suggests that to adjust the phase shift by controlling I osc is a high linearity way.

Unfortunately, the range of phase shift is quite limited in this solution, as illustrated in Fig. 4. Likewise, the changing of Q ext(while I osc and ω 0 is locked) exhibits similar characteristic. Tuning ω 0 to change the phase induces the largest phase shift range, because

Δω reaches maximum value

when sin𝜃 = 1, or maximum absolute value

when sin𝜃 = −1. [ω + Δω -max,ω + Δω max] is the locking range. If ω 0 is able to reach both lower and upper bound, 180∘ phase shift can be achieved theoretically.

2.2 Voltage-Controlled Oscillator

2.2.1 General Design Considerations

Supposing the oscillator of the ILO mentioned above is designed as a voltage controlled oscillator(VCO), it is possible to obtain variable phase shifts by changing the free running frequency of the VCO, ω 0. Both ring oscillators [1, 7, 13, 28] and LC oscillators [9, 11, 19, 26, 27] can be possibly implemented as a phase shifter. Considering the working range of tens of GHz, only the LC tank based VCO as shown in Fig. 6a is analyzed in this work.

The working frequency of this ILO (Fig. 6b), ω 0 is given as Eq. 17

The major challenge in the frequency tuning of the VCO is the optimization of the varactor, which has been widely used to change the effective load capacitance in the LC tank. The strong desire of wide tuning range of capacitance is actually limited by the minimal required quality factor. The sizing of the varactor is thus one of the key trade-offs. As illustrated in Eq. 14 and [16], a tank with low quality factor, Q ext, is preferred if a larger locking range is desired. However, it is risky to design a low Q ext tank which results in a larger power consumption and poor phase noise performance.

2.2.2 Optimisation of the LC Tank

The key issue in this design will be the optimisation of the LC tank. The operating frequency and quality factor of the oscillator can be determined as follows.

Considering the tank as a parallel LC circuit, the relationship between the inductor, the capacitor and the quality factor of the tank, Q tank, can be addressed as (18)

where

At a relatively low frequency, the Q L is the dominator of the Q tank. But at K-Band, the quality factor of both the inductor and capacitor are important. To achieve a high resonant frequency, the L tank and the C tank of the tank circuit should be determined as:

Where L ≈ L tank and \(C \approx {} \frac {1}{\frac {1}{C_{\text {{tank}}}}+\frac {1}{C_{\text {{para.total}}}}}\)(C para.total refers to the total parasitic capacitance).

As mentioned in Eq. 14, low Q tank results in a larger locking range at the expenses of large device (C para.total) and total power consumption.

According to Eqs. 14, 15 and 16, if the minimum VCO working frequency is larger than the lower bound(or the maximum working frequency is smaller than the upper bound), the Δω is too small for the sin𝜃 to reach −1 (or 1), thus shrinking the phase shift range. Which also means that, to achieve full 180∘ phase shift, the locking range needs to be located within the VCO frequency tuning range. In this work, the term “full 180∘ range” refers to “the frequency range of the input which can be shifted 180∘ by the phase shifter” to address this issue. Figure 7a shows how the full 180∘ range almost covers the entire frequency range. If the locking range is much larger and not ignorable, full 180∘ range will shrink, as shown in Fig. 7b. Assuming a wide locking range which is even larger than the frequency range as shown in Fig. 7c, the phase shift generated by this ILO can never achieve 180∘. Meanwhile, it can be concluded that small locking range are more sensitive to tuning voltage (a small deviation on tuning voltage), which suggest that the large locking range topology exhibits a higher precision.

By taking the advantage of the unique characteristic of varactor capacitance curve, fine tuning of phase shift is now possible. Figure 8 shows the C-V curve of the varactor used in this work, which has a lower slope at around −0.4 V and higher slope at around 0 V. If the injection is just located at the frequency when varactor is biased at −0.4 V, the ΔC/ΔV is small so that the phase changes smoothly. When V tune is 0 V, phase tuning around this biasing condition is the best way to perform a coarse tuning. It should be noticed that the coarse tuning area exhibits better linearity than the fine tuning area [27], which suggests that the low ΔC/ΔV area may also affect the linearity or precision.

High-quality factor means higher power efficiency, but it narrows the locking range down and the phase shifts are more sensitive to control voltage(harmful to the precision of phase shift). Besides, to maintain a high-quality factor at a given frequency, lumped elements of the circuit should be balanced and properly sized as suggested in Eq. 21. For example, if MIM capacitors (MIMs) are sized to be smaller (both capacitance and size) to increase the quality factor, the inductors need to be larger (usually both inductance and size). If quality factor is lowered to increase the precision, the power consumption is increased when using larger transistors. The increased parasitic capacitance that grows with power consumption will also narrow the frequency range down. Although a narrow frequency range results in a better precision, the frequency shift generated by model mismatch and small working bandwidth are additional issues.

3 Circuit Design

A guideline is therefore summarized to design the ILO based phase shifter with a good balance among these design considerations.

-

Step 1.

Design a VCO circuit, which covers the desired working range. The quality factor of the LC tank can be determined subject to different applications. For example, to have a smaller silicon area, a small inductor without significant Q decrease is usually preferred.

-

Step 2.

Determine the locking range. One of the three kinds of schemes, which are shown in Fig. 7, can be selected to set a goal in future quality factor optimisation. Larger locking range needs lower Q in small signal condition while smaller one needs higher.

-

Step 3.

Tank optimization. Since the locking range has been determined, the tank should be adjusted to achieve the target quality factor. The sizing of both inductors and capacitors are possible solutions in tuning the tank quality factor. Higher quality factor usually means smaller inductors or MIMs but it may cause frequency up-shift. The width and length of each finger of MOS varactors can be reduced to have higher quality factor at the cost of narrow scaling range [6, 32]. Considering the large silicon area contributed by the inductor, a smaller inductor is always preferred, hence the change of inductors should be at the lowest priority.

-

Step 4.

Circuit optimization. The negative resistance path consumes most of the power and brings large amount of parasitic capacitance. Back to step 3 once the path changes and repeat this procedure until a satisfied result is achieved. Offsets of frequency can be set to re-locate the locking range at the desired frequency range in low ΔC/ΔV area at the cost of lower linearity, as shown in Fig. 7.

As a design example, an injection locked oscillator phase shifter(core of the circuit) is designed under this guideline. The K-band phase shifter is implemented in a commercial 0.13 μm RF CMOS technology. The schematic is based on the conventional topology shown in Fig. 6b. The input signal is injected at the tail transistor of the oscillator. Buffers are used to isolate the oscillator from output port, or power will be drained from the oscillation cycle and the circuit can hardly oscillate. Low power and small silicon area are the key considerations in this design. The LC tank is designed to have a mid-frequency range to solve frequency drift problems and with 180∘ frequency coverage. A high-quality factor is designed to achieve a low power operation.

3.1 Optimization

The inductor and capacitor should be properly sized to reach the target frequency at K-band. For example, 0.9 nH L tank need about 1.9 pF C tank to achieve around 24 GHz. Since the C tank can be adjust in future without much area consideration and it is desirable to have a certain margin of potential parasitics, a smaller capacitor is used in this design.

Equation 14 suggests that both lowering the Q ext and increasing the I inj are helpful to enlarge the locking range. However, both solutions increase the I osc and thus increasing power consumption [5, 12, 20]. The first and second schemes in Fig. 7 are preferred in this design. These schemes exhibit a slightly lower precision but a lower power (high Q) and full 180∘ phase shift are achieved compared with the third scheme in Fig. 7.

Further optimization can be performed as well. The varactors of the tank are shown in Fig. 9, where C 0 are used to keep varactors in zero voltage biasing. Since a mid-frequency range is chosen to improve the precision, small L varactors can be used to lower the scale ability. Ratios of C 0 and varactors also have related with the scale ability and quality factor, as illustrated in Fig. 10.

Supposing the capacitor circuit of the tank has a fix maximum capacitance, the capacitance of C 0 should be decreased when the fingers of MOS varactors increase (W and L remained) and vice versa. This will affect the scaling ratio and Q C of the capacitor circuit. It can be seen in Fig. 10 that ratios goes down as fingers grow while Q C has a maximum value at about 22 fingers. Since neither maximum Q nor maximum frequency range is the goal of optimisation, the number of fingers can be determined within [10,22].

Usually, the negative-resistance path consumes most of the power of the phase shifter. Reducing the biasing current of the path is an essential way to lower the power consumption. That means the width or the number of fingers of the transistors should be kept as small as possible. However, changing the size of the transistor will have a side-effect, changing the parasitic capacitance. The C tank has to be increased to maintain desired phase shifts within the same frequency range, since the parasitic capacitance has been lowered unconsciously. Besides, considering the efficiency of signal injection and redundancy of process variations, the path still need further adjustments.

Based on this design strategy, the parameters of instances of the tank can be determined as Table 1.

For simplicity, the input network is not perfectly matched to a perfect 50 Ohm match to save silicon area. In case there is a need of inject efficiency, the matching work can be added [8].

4 Simulation and Experiment Results

In this paper, the complete schematic of the proposed circuit is shown in Fig. 11. The V inj is the injection port(also the input port) while the RF + and RF − is both connected to the 50-Ohm port. V tune is used to change the VCO working frequency. Buffers are added to isolate the core from output port. Under proper DC condition, the input of the circuit is connected to an input frequency source, the output will locked in to the input and generate tunable output with certain phase shifts. The proposed circuit is simulated using Cadence Spectre RF with EM extraction of critical interconnections.

The circuit is first simulated as a VCO. It can be seen in Fig. 12 that the frequency increase along with the V tune and has a tuning range of about 1.5 GHz, from 23.5 to 25.0 GHz in periodic steady state (PSS) analysis.

To verify the stability of the phase tuning, post-layout transient simulations at different operating frequencies and tuning voltages are performed as well. In these simulations, the amplitude of the injected signal is set to be 550 mV. Figures 13 and 14 implies that with the increase of V tune, phase increases as well, which verifies the theoretical analysis above. The increase rate of the phase is about 1.3∘/mV. In this case, voltage steps around 8.65 mV can make 11.25∘ shifts. A polar plot, Fig. 15, also shows that the output amplitude variation is smaller than 0.5 dBV from 23.8 to 24.4 GHz. As shown in Fig. 13, the phase noise variation is smaller than 8 dB from 23.8 to 24.4 GHz at 100 kHz offset.

The circuit is fabricated using Grace Semiconductor Manufacturing Corporation(GSMC) 0.13 μm RF CMOS technology. Die photo of the circuit is shown in Fig. 16, which occupies an silicon area of about 540 μm × 620 μm (including I/O pads) or about 316 μm × 388 μm (excluding I/O pads). The on-wafer measurement is carried out using an Agilent MXA Signal Analyzer N9020A with a Cascade Probe Station. RF probes are attached to the GSGSG (output) pads on die. All measurement with a DC power consumption of ILO core of about 3.14 mW with a DC Voltage of 1.2 V. A spectrum measurement is performed at the very first stage. Figure 17 shows the ILO has a frequency range of 22 ∼ 23.4 GHz.

Compared Fig. 17 with Fig. 14, it is clear that the operating frequency and tuning range of the oscillator reduce considerably. This is due to insufficient EM extraction of interconnections and inaccurate device model at tens of GHz. The working frequency in measurement is about 22 to 23.4 GHz with a range of 1.4 GHz.

The S-parameter measurement is on an R&S ZVA67 network analyzer (VNA) with same Probe Station. RF probes calibrated through the on-wafer 12-term TOSM calibration are attached to the GSG(input) and GSGSG(output) pads on die. The measured S-parameters are shown in Figs. 18 and 19.

As can be seen in Fig. 19, with the increase of V tune, phase shift drops and the range of it is about 180∘, almost reach the theoretically maximum range. Compared with the simulation results, the locking range is smaller and the increase rate of the phase is even larger, about 4∘/mV. In this case, to be used as a phase shifter, the V tune should be precisely controlled to achieve desired phase shift, e.g., a high 10-bit DAC to provide 1 mV steps. Table 2 summarizes the proposed work with literatures, which suggests the successful implementation of a low power phase shifter with a small silicon area.

5 Conclusion

An ILO-based phase shifters in K-band with continuous phase tuning is proposed. Several key design considerations have been analyzed to reach a design strategy of a low cost and low power operation at K-band. The proposed phase shifter is implemented using a 0.13 μm CMOS technology. Measurement results show that the proposed design is able to provide about 180 degree phase shift continuously while consuming 3.14 mW from a 1.2 V supply voltage.

References

Aleksic, M.: A 3.2-GHz 1.3-mW ILO phase rotator for burst-mode mobile memory i/o in 28-nm low-leakage CMOS. In: European Solid State Circuits Conference (ESSCIRC), ESSCIRC 2014 - 40th, pp. 451–454 (2014). doi:10.1109/ESSCIRC.2014.6942119

Alsuraisry, H., Cheng, J.H., Wang, H.W., Zhong, J.Y., Tsai, J.H., Huang, T.W.: A x-band digitally controlled 5-bit phase shifter in 0.18- μ m CMOS technology. In: 2015 Asia-Pacific Microwave Conference (APMC), vol. 2, pp. 1–3 (2015). doi:10.1109/APMC.2015.7413072

Askari, M., Kaabi, H., Kavian, Y.S.: A 24 GHz reflective-type phase shifter with constant loss in 0.18 μ m CMOS technology. AEU - International Journal of Electronics and Communications 69(8), 1134–1142 (2015). doi:10.1016/j.aeue.2015.04.015. http://www.sciencedirect.com/science/article/pii/S1434841115001168

Barth, H.: A 94 GHz synchronized oscillator-chain for fast, continuous 360∘ phase modulation. In: Microwave Symposium Digest, 1987 IEEE MTT-S International, vol. 1, pp. 433–436 (1987). doi:10.1109/MWSYM.1987.1132424

Calandra, E.F., Sommariva, A.M.: Approach to the analysis of nonlinear feedback oscillators under large-signal injection. IEE Proceedings G - Electronic Circuits and Systems 133(5), 233–242 (1986). doi:10.1049/ip-g-1:19860038

Cao, C., O, K.K.: Millimeter-wave voltage-controlled oscillators in 0.13- μ m CMOS technology. IEEE Journal of Solid-State Circuits 41(6), 1297–1304 (2006). doi:10.1109/JSSC.2006.874321

Cho, H., Bae, J., Yoo, H.J.: A 37.5 μ w body channel communication wake-up receiver with injection-locking ring oscillator for wireless body area network. IEEE Transactions on Circuits and Systems I: Regular Papers 60(5), 1200–1208 (2013). doi:10.1109/TCSI.2013.2249173

Feng, C., Yu, X.P., Lu, Z.H., Lim, W.M., Sui, W.Q.: V-band injection-locked oscillator with 9 ghz locking range. Electronics Letters 49(8), 548–549 (2013). doi:10.1049/el.2013.0182

GHonoodi, H., Naimi, H.M.: A phase and amplitude tunable quadrature lc oscillator: Analysis and design. IEEE Transactions on Circuits and Systems I: Regular Papers 58(4), 677–689 (2011). doi:10.1109/TCSI.2010.2073910

Ghonoodi, H., Naimi, H.M.: Analysis and design of a phase-tunable source injection-coupled lc quadrature oscillator. Circuits, Systems, and Signal Processing 35(3), 731–752 (2016). doi:10.1007/s00034-015-0085-6

Grubinger, H., v. Buren, G., Barth, H., Vahldieck, R.: Continuous Tunable Phase Shifter Based on Injection Locked Local Oscillators at 30 GHz. In: 2006 IEEE MTT-S International Microwave Symposium Digest, pp. 1821–1824 (2006). doi:10.1109/MWSYM.2006.249749

Kurokawa, K.: Injection locking of microwave solid-state oscillators. Proceedings of the IEEE 61(10), 1386–1410 (1973). doi:10.1109/PROC.1973.9293

Liu, S., Zheng, Y., Lim, W.M., Yang, W.: Ring oscillator based injection locked frequency divider using dual injection paths. IEEE Microwave and Wireless Components Letters 25(5), 322–324 (2015). doi:10.1109/LMWC.2015.2409792

Liu, T.P.: A 6.5 GHz monolithic CMOS voltage-controlled oscillator. In: Solid-State Circuits Conference, 1999. Digest of Technical Papers. ISSCC. 1999 IEEE International, pp. 404–405 (1999). doi:10.1109/ISSCC.1999.759323

Lu, C., Matters-Kammerer, M.K., Mahmoudi, R., Baltus, P.G.M., Habekotté, E., van Hartingsveldt, K., van der Wilt, F.: A 48 GHz 6-bit lo-path phase shifter in 40-nm CMOS for 60 GHz applications. In: ESSCIRC (ESSCIRC), 2013 Proceedings of the, pp. 73–76 (2013). doi:10.1109/ESSCIRC.2013.6649075

Mansuri, M., O’Mahony, F., Balamurugan, G., Jaussi, J., Kennedy, J., Shekhar, S., Mooney, R., Casper, B.: Strong injection locking of low-Q LC oscillators. In: 2008 IEEE Custom Integrated Circuits Conference, pp. 699–702 (2008). doi:10.1109/CICC.2008.4672182

Meng, F., Ma, K., Yeo, K.S., Xu, S.: A 57-to-64-GHz 0.094-mm2 5-bit passive phase shifter in 65-nm CMOS. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 24(5), 1917–1925 (2016). doi:10.1109/TVLSI.2015.2469158

Minaei, S., Yuce, E.: High input impedance nmos-based phase shifter with minimum number of passive elements. Circuits, Systems, and Signal Processing 31(1), 51–60 (2012). doi:10.1007/s00034-011-9290-0

Mirzaei, A., Heidari, M.E., Abidi, A.A.: Analysis of oscillators locked by large injection signals: Generalized adler’s equation and geometrical interpretation. In: IEEE Custom Integrated Circuits Conference 2006, pp. 737–740 (2006). doi:10.1109/CICC.2006.320928

Paciorek, L.J.: Injection locking of oscillators. Proceedings of the IEEE 53(11), 1723–1727 (1965). doi:10.1109/PROC.1965.4345

Padilla, P., Muñoz-Acevedo, A., Sierra-Castañer, M.: Low loss 360∘ ku band electronically reconfigurable phase shifter. AEU - International Journal of Electronics and Communications 64(11), 1100–1104 (2010). doi:10.1016/j.aeue.2009.11.007. http://www.sciencedirect.com/science/article/pii/S1434841109003227

Razavi, B.: A study of injection locking and pulling in oscillators. IEEE Journal of Solid-State Circuits 39(9), 1415–1424 (2004). doi:10.1109/JSSC.2004.831608

Sah, S.P., Yu, X., Heo, D.: Design and analysis of a wideband 15-35GHz quadrature phase shifter with inductive loading. IEEE Transactions on Microwave Theory and Techniques 61(8), 3024–3033 (2013). doi:10.1109/TMTT.2013.2267749

Toker, A., Ozoguz, S.: Tunable allpass filter for low voltage operation. Electronics Letters 39(2), 175–176 (2003). doi:10.1049/el:20030179

Tousi, Y., Valdes-Garcia, A.: A ka-band digitally-controlled phase shifter with sub-degree phase precision. In: 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), pp. 356–359 (2016). doi:10.1109/RFIC.2016.7508326

Tseng, W.J., Tsai, Z.M., Lin, C.S., Wang, H.: Ku-band phase shifter based on injection locked voltage oscillator. In: Wireless Information Technology and Systems (ICWITS), 2010 IEEE International Conference on, pp. 1–4 (2010). doi:10.1109/ICWITS.2010.5612270

Wu, L., Li, A., Luong, H.C.: A 4-path 42.8-to-49.5 GHz lo generation with automatic phase tuning for 60 GHz phased-array receivers. IEEE Journal of Solid-State Circuits 48(10), 2309–2322 (2013). doi:10.1109/JSSC.2013.2269855

Yu, X.P., Liu, Z., Fan, D.Z., Yeo, K.S.: The investigation and optimisation of phase-induced amplitude attenuation in the injection-locked ring oscillators-based receiver. Circuits, Systems, and Signal Processing pp. 1–18 (2016). doi:10.1007/s00034-016-0405-5

Yu, Y., Baltus, P.G.M., de Graauw, A., van der Heijden, E., Vaucher, C.S., van Roermund, A.H.M.: A 60 GHz phase shifter integrated with lna and pa in 65 nm CMOS for phased array systems. IEEE Journal of Solid-State Circuits 45(9), 1697–1709 (2010). doi:10.1109/JSSC.2010.2051861

Yu, Y., Zheng, Q., Zhao, C., Kang, K.: A 60-GHz vector summing phase shifter with digital tunable current-splitting and current-reuse techniques in 90 nm CMOS. In: 2015 IEEE MTT-S International Microwave Symposium, pp. 1–3 (2015). doi:10.1109/MWSYM.2015.7166920

Zhang, M., Liu, M., Ling, S., Chen, P., Zhu, X., Yu, X.: K-band tunable phase shifter with microstrip line structure using bst technology. In: 2015 Asia-Pacific Microwave Conference (APMC), vol. 2, pp. 1–3 (2015). doi:10.1109/APMC.2015.7413118

Zhao, Y., Wang, Z.G.: 20-ghz differential colpitts vco in 0.35- μ m bicmos. Journal of Infrared, Millimeter, and Terahertz Waves 30(3), 250–258 (2009). doi:10.1007/s10762-008-9448-4

Acknowledgements

This work was supported by Zhejiang Provincial Natural Science Foundation of China (Grant No. LY16F040001), the ZJU-SUTD Joint research project under the Fundamental Research Funds for the Central Universities (no. 2015XZZX001-01) and Natural Science Foundation of China under grant number 61574125.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Qiu, QL., Yu, XP. & Sui, WQ. A K-Band Low-Power Phase Shifter Based on Injection Locked Oscillator in 0.13 μm CMOS Technology. J Infrared Milli Terahz Waves 38, 1368–1386 (2017). https://doi.org/10.1007/s10762-017-0424-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10762-017-0424-8