Abstract

A multi-stage amplifier is a frequency compensated via a single and small MOSFET based capacitor. The idea reduces die occupation considerably since removes any passive elements in the compensation network. Also, a normal differential pair and a MOSFET based capacitor form compensation network and boost DC gain simultaneously. The proposed approach is symbolically described via MATLAB and numerically simulated via HSPICE circuit simulator using standard TSMC 0.18µ CMOS technology. According to mathematical justifications and simulation results, the proposed amplifier shows operation excellency especially in terms of die occupation and frequency response parameters which make it appropriate choice to realize larger analog and mixed mode systems like modulators and data converters.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Amplifiers play an inevitable role in many electronics systems include modulators and data converters. Using an amplifier, almost any functional block can be realized, so the amplifier is considered as the most important block in analog and mixed mode electronics. Extensive researches are performed to design different configurations and improve basic techniques for more efficient amplifier design. Usually, to address advanced demands regarding DC gain and GBW requirements, two approaches are considered by circuit designers. Firstly, the tendency is to use Cascode structures, since appropriate DC gain and acceptable GBW are available. For instance, Akbari M et al. [1, 2] and Aghaee et al. [3] report improved folded Cascode (FC) amplifiers, reaching more than 70 dB as DC gain and more than 300 MHz as GBW while driving small load capacitors in a range of few pF. Cascode technique as depicted in Fig. 1 uses MOSFETs vertically which reduces output swing, depending on allocated drain-source voltage for each MOSFET. Considering the feature size and supply voltage reduction in advanced CMOS technologies, Cascode approach is not compatible with technology advancements. The reason is the fact that there is not enough voltage budget to allocate MOSFETs drain-source which have to work in the saturation region. In this region, the absolute value of drain-source voltage must be larger than VGS − Vth. Where VGS is gate-source voltage and Vth is threshold voltage value. So, satisfying MOSFETs to operate in the saturation region is a challenging and may impossible task to design Cascode structures in advanced CMOS technologies. This limitation becomes more rigid when demands are at a great level for high speed and high DC gain amplifiers. Therefore, the second approach as multi-stage amplifiers or Cascade configurations attracted designer attention. The cascade amplifies are able to provide very high DC gains (more than 100 dB for three-stage cases) and also can be realized via cascading simple gain stages like common source stage. But the main problem in dealing with the multi-stage amplifier is instability issues which are raised due to increasing nodes of the amplifier compared to Cascode structures. This problem is dominant since poles and zeros locations determine the amplifier response. The value of GBW and PM directly related to pole-zero map of the amplifier. In a simple view, poles and zeros positioning via circuit parameters (like gm, r, CC) is the subject of numerous multi-stage works. For instance, Grasso et al. [4] describes general methods for three stage cases manly based on NMC and RNMC approaches. Using differential current conveyor is investigated in Shahsavari et al. [5]. Also, Grasso et al. [6] presents details description of RNMC methods. As a complete new method, Largani et al. [7] is used differential block in compensation network and reduced size of compensation capacitor considerably. To boost bandwidth of the amplifier, Peng and Sansen [8] proposed a new scheme, exploiting direct injection via a separate feed forward path while Lee and Mok [9] tries to realize an active frequency compensation network using active transistor instead of passive elements like capacitors and resistors. As a high performance three stage amplifier, Biabanifard et al. [10] presents a novel scheme of compensation capacitor using a current subtractor. In addition, Grasso et al. [11] dedicated to improve RNMC using additional resistors and buffers. To reduce noise effects and its degenerations, Akbari et al. [12] introduces a simple design methodology via transistor sizing which is appropriate to consider in circuit design. Additionally, Aloisi et al. [13] investigates using buffers in RNMC configurations. To point out current mode operation, Shahsavari et al. [14] exploits current conveyors and benefits its high speed performance. As a control view, Leung et al. [15] discusses design via control theories while Largani et al. [16] attenuates feed forward paths to improve frequency response. Also, Akbari et al. [17] highlights noise performance for a multi stage amplifier and Biabanifard et al. [18] exploits a fully differential block to realize both output stage and frequency compensation network. In addition a comprehensive design using binary matrixes is proposed in Biabanifard et al. [19] which is appropriate for computer aided designs. At last, Chaharmahali et al. [20, 21] and Zaherfekr and Biabanifard [22] attenuate and amplify feed forward and feedback paths respectively which all improve frequency response compared to conventional NMC and RNMC approaches.

Recycling folded cascode amplifier [3]

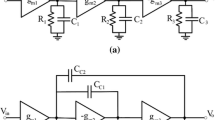

To specify the discussion atmosphere, Fig. 2 is presented. Nested Miller compensation [4] and revered nested Miller compensation [6] are considered as conventional approaches to design three-stage amplifiers. Both are simple while RNMC is more efficient than NMC. The nested loop in the RNMC structure is not loaded on the output node, leads to the smaller capacitor in the output node. Consequently, the possible dominant or first non-dominant pole is shifted to higher frequencies and more degree of freedom is provided compared to NMC. In addition, NMC and RNMC have to unlimber negative loop gains which guarantee proper Miller effect. So, the sign of stages is absolutely determined as depicted in Fig. 2.

Two general methods of three-stage frequency compensation [4] a nested miller compensation, b reversed nested miller compensation

Based on the previous state of the art [4, 6], these amplifiers are capable of driving capacitors as large as 100 pF while exhibiting 100 dB, 0.22 MHz, and 70° as DC gain, GBW, and PM, respectively. In addition, to driving a 100 pF load capacitor, NMC and RNMC need more than 100 pF as compensation capacitor (collecting both compensation capacitors). This is a very bad condition regarding die occupation. Usually, the load capacitor can be an off-chip one, so the compensation capacitor is the sole passive element in the circuit. The size of the compensation capacitor is determinative. Any effort to reduce the size of the compensation capacitor reduces die occupation proportionally. Also, lower capacitors lead to higher circuit dynamics (poles and zeros) which can improve frequency response parameters like GBW and PM.

In this content and mentioned environment, several works are reported to improve NMC and RNMC schemes. The improvements mean larger GBW, more stable circuits, less power consumption, more simple circuit design, and less die occupation.

Addition of nulling resistor to the Miller capacitor (compensation capacitor) provides more degree of freedom to control poles and zeros location. Even paved the way to pole-zero cancellation scenarios [11]. Using voltage and the current buffer is verified to increase GBW value since buffers are one-way blocks and can obstruct feedforward paths. This means that the Right Half Plan (RHP) zero shifts to very high frequencies and its effects are negligible [13].

At last, Largani et al. [7] is introduced to highlight the role of differential pair stage in the compensation network. Since the differential block can amplify and attenuate multiple paths simultaneously, it can be used as a multi-task block in the circuit. For instance, Largani et al. [7] uses a differential pair to form a compensation network, while it can be used to boost DC gain too. Also, by placing compensation capacitor in series with differential block, the capacitor value can be control via gain of differential stage [7], so smaller Miller capacitor can perform frequency compensation with the aim of virtual amplification. This is a great advantage to reduce die area. This type of amplifiers is used in many telecommunication systems such as Khalesi and Ghods [23].

Rest of this paper is organized as follows. Section 2 describes and discusses the proposed method which is based on RNMC scheme while compensation capacitors are replaced with a small MOSCAP. This reduces die occupation as low as possible and it can be said that there is no passive element to occupy die. So, die area is fully allocated to MOSFETs. Section 3 introduces circuit level implementation of the proposed device and reports simulation results which are extracted from MATLAB (symbolical and simplified TF) and HSPICE circuit simulator. Discussion around the proposed amplifier and its performance are brought in Sect. 4. Finally, the paper is concluded in Sect. 5 as the conclusion.

2 Proposed method

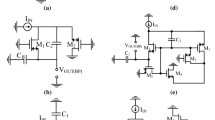

Using a fully differential block to form compensation network and boost DC gain besides realizing a small compensation capacitor via a MOSFET are suggested in this work. As depicted in Fig. 3, the proposed amplifier consists of two differential stages as the first and last stages. Also, the second and third stages are simple common-source gain stage. Also, just a single capacitor is shared in two loops include (gm2gfrf+CC) and (gm2gm3gfrf+CC) which could be small with the existence of (gfrf) in loop gains terms. According to current allocations, this factor can be set in a relatively large range from 10 to 500 which is the gain of the differential block. So, the compensation capacitor value can be select 10–500 times smaller while the loop gain value remains unchanged compared to conventional RNMC configuration. This reduces die area considerably while increase chances to implement compensation capacitors via an active MOSFET similar to Fig. 3 as a controlled gate-bulk capacitor.

The Kirchhoff Current Law (KCL) is applied to the presented linear model in Fig. 3. Five nodes as five outputs of stages are considered. It should be noted that the last stage has two outputs. So five equations are obtained which variables are nodes voltages. The transfer function is calculable as ration of the output voltage to input. We solved the set of equation symbolically with MATLAB advanced toolbox for symbolical calculations. The obtained TF is heavy and complicated to deal with paper and pencil. So, a simple simplification is performed via two basic assumptions. First of all, we consider that each stage has DC gain (gmiri) larger than unity and secondly we assume that CL > CC > CParasitics. These two assumptions help to find dominant terms and neglecting marginal terms. As a result, the simplified TF is described via (1). Where CL is load capacitor, CC is a compensation capacitor and gmi is ith stage transconductance. Also, ri represents ith stage output impedance while s denotes Laplace variable. From (1), two poles and a single RHP zero are calculated as (2), (3) and (4). It is obvious that both P2 and Z are really large values and the system behaves like single pole systems.

To more in-depth knowledge of poles and zero locations, numerical values are allocated to circuit parameters. The values are extracted from circuit simulation in the next stage. Table 1 reports numerical values for circuit parameters.

Based on the extracted values for circuit parameters, poles and zeros are settled which is shown in Fig. 4 as the system pole-zero map. According to this figure, the first pole is occurred in − 129 rad/s, the second pole occurs in − 2.29 G rad/s and the right side zero frequency is 255 G rad/s. The fact is that the second pole and the zero are in high frequencies and can be neglected without any error.

Additionally, GBW is defined as the product of DC gain and first pole. DC gain is described via (5) and GBW is calculated via (6).

Based on reported values in Table 1, the system behaves like a single pole system which means shows 90° as PM. Depends on the application, may lower PM be more desirable since the single pole system with PM equal to 90° is slow compared to systems satisfying Butterworth criteria (PM = 63°). So, the second pole is determinative. Considering the fact that each pole degenerates PM in a frequency range of one decade before and one decade after its occurrence, it can be concluded that to reach PM equal to 90°, the second pole must be at least ten times bigger than GBW frequency. While to obtain PM equal to 63°, the second pole has to be two times bigger than the GBW frequency. This condition is formulated via (7) and (8) respectively.

Replacing (3) and (6) in (7) and (8), the gf or CC can be developed further. For instance, the gf for each state can be described as below:

It should be noted that (7), (8), (9) and (10) specify borders for PM and gf values. Any other value between two borders is acceptable which results in PM in the range of 63° to 90°.

The next section reveals more details on simulation results and operational performance of the amplifier.

3 Simulation results

The proposed method is simulated using standard TSMC 0.18 µm CMOS technology and HSPICE circuit simulator. The circuit schematic is depicted in Fig. 5. All MOSFETs are set to operate in saturation region and the MOSCAP is designed to show 0.9 pF capacitance. MOSFETs dimensions and corresponding bias values are tabulated in Table 2.

The most important response for an amplifier is Bode diagram since reveals DC gain, GBW and PM values. It also can report a simple vision of poles and zerosfrequencies. TF described in (1) and frequency domain simulation of Fig. 5 is presented in Fig. 6 as the frequency response of the proposed circuit. According to this figure, both the theory and simulation are matched together in the operational frequency of the amplifier which is considered GBW. After this frequency mismatch exists which is ignorable. In addition according to this figure, DC gain, GBW, and PM are obtained equal to 120 dB, 18 MHz and 89°, respectively. The reported power consumption via simulator is 545 µW, which is needed to provide relatively large transconductances as reported in Table 1.

Considering circuit dependency to compensation capacitor, Figs. 7 and 8 are presented. These figures report GBW and PM versus compensation capacitor deviation. Since, MOSCAP is exploited and mismatches may exist in the fabrication process. According to these figures, the proposed circuit is appropriately robust against MOSCAP mismatches.

Also, Figs. 9 and 10 report GBW and PM against load capacitor variation. The load capacitor variation is ± 20%, while GBW deviates less than 1 MHz and PM deviation is less than 4°.

To investigate the transient response of the proposed circuit, Fig. 11 is presented as the step response. Both rising and falling edges are included. Based on the presented step response, the settling time is 23 ns. Also, the response is similar to single pole systems without any overshoot.

Circuit dependency on transconductances is always important since several errors and mismatches are inevitable such as noisy condition and fabrication errors. To investigate the proposed circuit dependency to stages transconductances, Figs. 12 and 13 report GBW and PM versus gmf variations. Figures 14 and 15 show circuit dependency versus gm1 variations while Figs. 16 and 17 illustrate GBW and PM deviations against gm2 changing. At last but not least Figs. 18 and 19 are presented to show GBW and PM deviations versus gm3 variation. According to this analysis, the proposed circuit could be considered as a robust amplifier against transconductances values.

In addition, Monte-Carlo simulation is performed and circuit parameters set to 30% variations on normal values under Gaussian distribution. The circuit is simulated using 100 iterations which results are shown in Fig. 20.

4 Discussion

To compare the proposed circuit with other existing works, tradeoffs have to be considered. Using defined figure of merits (FOM) in Biabanifard et al. [19], the comparison table reports amplifier parameters and FOM values of the proposed work along with another state of the art in Table 3. The defined FOMs are highlighting small and large signal behavior via (11) and (12). Also, the compensation capacitor is considered in (13) to magnify the effect of the compensation capacitor. Finally, PM is placed on the numerator of (14) to express stability merit.

According to Table 3, the proposed amplifier shows higher performance especially the compensation capacitor value is reduced notably while is realized via MOSCAP. Also, the defined FOMs values verify the efficiency of the simulated amplifier.

5 Conclusion

A MOSCAP based frequency compensation method is discussed. Exploiting differential block to realize compensation network, reduced size of compensation capacitor. Also, the differential block boosts DC gain of overall amplifier. The proposed approach modeled via symbolical TF and simulated via TSMC 0.18 µm CMOS technology while HSPICE circuit simulator is used. Based on theoretical and obtained simulation results, the circuit is capable of driving a 100-pF as a load capacitor just by a single 0.9 pF compensation capacitor. This reduces the die area considerably. Also, ample simulations are performed to illustrate the proposed amplifier excellency over previous works.

References

Akbari, M., et al. (2014). Design and analysis of DC gain and transconductance boosted recycling folded cascode OTA. AEU-International Journal of Electronics and Communications,68(11), 1047–1052.

Akbari, M., et al. (2015). High performance folded cascode OTA using positive feedback and recycling structure. Analog Integrated Circuits and Signal Processing,82(1), 217–227.

Aghaee, T., Biabanifard, S., & Golmakani, A. (2017). Gain boosting of recycling folded cascode OTA using positive feedback and introducing new input path. Analog Integrated Circuits and Signal Processing,90(1), 237–246.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2008). Analytical comparison of frequency compensation techniques in three-stage amplifiers. International Journal of Circuit Theory and Applications,36(1), 53–80.

Shahsavari, S., et al. (2015). DCCII based frequency compensation method for three stage amplifiers. AEU-International Journal of Electronics and Communications,69(1), 176–181.

Grasso, A. D., Marano, D., Palumbo, G., & Pennisi, S. (2010). Analytical comparison of reversed nested Miller frequency compensation techniques. International Journal of Circuit Theory and Applications,38(7), 709–737.

Largani, S. M. H., et al. (2015). A new frequency compensation technique for three stages OTA by differential feedback path. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields,28(4), 381–388.

Peng, X., & Sansen, W. (2004). AC boosting compensation scheme for low-power multistage amplifiers. IEEE Journal of Solid-State Circuits,39(11), 2074–2079.

Lee, H., & Mok, P. K. T. (2003). Active-feedback frequency-compensation technique for low-power multistage amplifiers. IEEE Journal of Solid-State Circuits,38(3), 511–520.

Biabanifard, S., et al. (2015). High performance reversed nested Miller frequency compensation. Analog Integrated Circuits and Signal Processing,85(1), 223–233.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2007). Advances in reversed nested Miller compensation. IEEE Transactions on Circuits and Systems I: Regular Papers,54(7), 1459–1470.

Akbari, M., Biabanifard, S., & Hashemipour, O. (2014). Design of ultra-low-power CMOS amplifiers based on flicker noise reduction. In 2014 22nd Iranian conference on electrical engineering (ICEE). IEEE.

Aloisi, W., Palumbo, G., & Pennisi, S. (2008). Design methodology of Miller frequency compensation with current buffer/amplifier. IET Circuits, Devices and Systems,2(2), 227–233.

Shahsavari, S., et al. (2014) A new frequency compensation method based on differential current conveyor. In 2014 22nd Iranian conference on electrical engineering (ICEE). IEEE.

Leung, A. K. N., et al. (1999). Damping‐factor‐control frequency compensation technique for low‐voltage low‐power large capacitive load applications. In 1999 IEEE international solid‐state circuits conference, 1999. Digest of technical papers. ISSCC. IEEE.

Largani, S. M. H., et al. (2014). A new SMC compensation strategy for three stage amplifiers based on differential feedback path. In 2014 22nd Iranian conference on electrical engineering (ICEE). IEEE.

Akbari, M., Biabanifard, S., & Asadi, S. (2015). Input referred noise reduction technique for trans-conductance amplifiers. Electrical and Computer Engineering: An International Journal (ECIJ),4(4), 11–22.

Biabanifard, S., et al. (2018). Three stages CMOS operational amplifier frequency compensation using single Miller capacitor and differential feedback path. Analog Integrated Circuits and Signal Processing,97(2), 195–205.

Biabanifard, S., et al. (2018). Multi stage OTA design: From matrix description to circuit realization. Microelectronics Journal,77, 49–65.

Chaharmahali, I., Asadi, S., & Dousti, M. (2016). Design procedure for three-stage CMOS OTAs with AC boosting frequency compensation technique. IETE Journal of Research,62(5), 705–713.

Chaharmahali, I., et al. (2017). A new method modifying single Miller feedforward frequency compensation to drive large capacitive loads: Putting an attenuator in the path. Analog Integrated Circuits and Signal Processing,93(1), 61–70.

Zaherfekr, M., & Biabanifard, A. (2019). Improved reversed nested miller frequency compensation technique based on current comparator for three-stage amplifiers. Analog Integrated Circuits and Signal Processing,98(3), 633–642.

Khalesi, H., & Ghods, V. (2019). QPSK modulation scheme based on orthogonal Gaussian pulses for IR-UWB communication systems. Journal of Circuits, Systems and Computers,28(1), 1950008 (1–13).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Babazadeh Daryan, B., Khalesi, H., Ghods, V. et al. Multi-stage CMOS amplifier frequency compensation using a single MOSCAP. Analog Integr Circ Sig Process 103, 237–246 (2020). https://doi.org/10.1007/s10470-020-01595-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01595-z