Abstract

This paper describes a CMOS pulse frequency modulation (PFM) buck converter employing a digitally programmable voltage level-shifting technique capable of adjusting peak inductor current and output ripple voltage for different load currents. The conventional PFM buck converters employ either an adaptive delay time control circuit or a fixed delay time control circuit to control output ripple voltage and power efficiency with the switching frequency. However, they suffer from a large peak inductor current, resulting in reduced power efficiency. The digitally programmable voltage level-shifting circuit, based on a common source amplifier, is capable of sensing inductor current through the voltage drop caused by on-resistance of the power switch, and can control peak inductor current. The precision needed to control the magnitude of the peak inductor current can be obtained with the number of bits in the digitally programmable voltage level-shifting circuit that are dependent on the input common mode range of the comparator. Employment of one comparator with pre-control logic and post-control logic circuits allows the proposed circuit to improve power efficiency by removing additional circuits, compared with the conventional PFM buck converters. The proposed converter was implemented with a 180 nm CMOS process. The effective chip size of the core block occupies 900μm × 590μm. The proposed PFM mode buck converter with a precision of four bits to control peak inductor current is capable of accommodating an input voltage range of 2.7–3.3 V, and can produce output voltage of 1.2 V. The operational switching frequency measured is on the order of several to several hundred kHz, the load current range is under 150 mA, and the measured output ripple voltage varied, depending on the digital programming status. The measured power efficiency ranged between 70 and 84%.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the rapid advancement of CMOS technology, circuit performance has drastically improved and power consumption has been reduced owing to the development of circuit design techniques and reductions in power supply voltage. This has allowed portable devices (smart phones, tablets, wearable devices, and IoT devices) to come to market [1, 2]. Most of these portable devices utilize battery resources, so power management integrated circuits (PMICs) are employed that are capable of managing energy in battery resources with efficiency. It is well known in PMICs that PFM buck converters perform at higher efficiency under low load–current conditions than pulse width modulation (PWM) buck converters [3].

In order for a conventional PFM buck converter to control output ripple voltage and power efficiency with a switching frequency, it usually employs either an adaptive delay time control circuit [4] or a fixed delay time control circuit [5, 6]. PFM buck converters with a fixed delay time control circuit produce peak inductor current in proportion to input voltage. As the input voltage becomes high, an over-current may occur due to the steep slope of the inductor current. On the other hand, as input voltage becomes low, the slope of the inductor current stays low, which results in a narrow operational range for the load current. An adaptive delay time control circuit enables PFM buck converters to control the on-time of the p-channel power switch. This circuit technique is able to eliminate the disadvantage of the fixed delay time control circuit—dependence of the peak inductor current on input voltage. However, the adaptive delay time control circuit still suffers from producing large peak inductor current and requiring additional circuitry to improve the accuracy of controlling the inductor peak current, which results in a reduction in power efficiency.

In order to overcome the disadvantages of the conventional delay time control circuit techniques, a current mode PFM buck converter employs a technique to restrict the inductor current to a predetermined peak inductor current [7]. This technique directly detects the inductor current through the sensing circuit and converts it to a voltage through the V-I converter to sense the peak inductor current. The current mode technique takes advantage of controlling the peak inductor current with higher accuracy than the delay time control circuit techniques. However, since this technique requires employment of additional circuits such as inductor current sensing circuit and V-I converter, the power consumption of the control circuit may be increased. A digitally programmable voltage level-shifting technique is proposed to control peak inductor current with the switching frequency, and consequently, the output ripple voltage of the PFM buck converter. In addition, the proposed technique employs a simpler circuit structure than the other techniques [4,5,6,7] by sensing the inductor current through the level shifting circuit consisting of only six MOSFET devices. This paper is organized as follows. The proposed architecture and the digitally programmable voltage level-shifting technique are described in Section II. Measurement results of the proposed circuit are discussed in Sect. 3. Conclusions are drawn in Sect. 4.

2 The proposed architecture

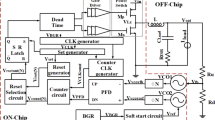

An overall block diagram of the proposed architecture is in Fig. 1. It consists of the on-chip circuit within the dotted line and the off-chip circuit. The on-chip circuit includes power switches with gate drivers, a dead-time control circuit, a comparator, pre-control logic, post-control logic, a digitally programmable voltage level shifter, bandgap reference, and a zero current detection (ZCD) circuit. The inductor, an output capacitor, a resistive feedback network, and the load are enclosed in the off-chip circuit.

When the p-channel power switch turns on in the steady state, the inductor current flowing through the p-channel power switch increases with a slope of \( \left( {{\text{V}}_{\text{in}} - {\text{V}}_{\text{out}} } \right)/{\text{L}} \), where \( {\text{V}}_{\text{in}}, {\text{V}}_{\text{out}} , {\text{and L}} \) are input voltage, output voltage, and inductance, respectively. \( {\text{V}}_{\text{LX}} \) on the LX node shows the voltage waveform slightly lower than \( {\text{V}}_{\text{in}} \) due to the voltage drop across the on-resistance of the p-channel power switch. Hence, this voltage waveform can be utilized to detect the peak inductor current. However, the voltage drop across the on-resistance (on the order of a few hundred milli-ohms) of the p-channel power switch is not significant, and it may not be within the input common mode range (ICMR) of the comparator, since it starts from \( {\text{V}}_{\text{in}} \). Therefore, it requires a voltage level-shifting circuit to bring \( {\text{V}}_{\text{LX}} \) into the ICMR of the comparator. The magnitude of \( {\text{V}}_{\text{LX}} \) can be lowered by a certain level of voltage through the voltage level–shifting circuit, but the shape of the voltage waveform for \( {\text{V}}_{\text{LX}} \) remains unchanged. \( {\text{V}}_{{{\text{SF}},{\text{amp}}}} \) is the level-shifting voltage on the LX node and is compared with the digitally programmable \( {\text{V}}_{{{\text{LS}},{\text{amp}}}} \) made by \( {\text{V}}_{\text{in}} \) to determine the magnitude of the inductor current and output ripple voltage through pre-control logic and post-control logic circuits.

The schematic of the voltage level–shifting circuit to produce \( {\text{V}}_{{{\text{SF}},{\text{amp}}}} \) and \( {\text{V}}_{{{\text{LS}},{\text{amp}}}} \) is illustrated in Fig. 2. Since constant current \( {\text{I}}_{\text{cons}} \) flows through the transistor \( {\text{M}}_{{{\text{N}}1}} \), level-shifting voltage \( {\text{V}}_{\text{SF}} \) can be obtained as follows:

where \( {\text{K}}_{\text{n}} \), \( {\text{V}}_{\text{th}} \), \( {\text{S}}_{1} \), \( {\text{I}}_{\text{L}} \), and \( {\text{R}}_{{{\text{p}},{\text{on}}}} \) are n-channel device trans-conductance parameter, threshold voltage, device aspect ratio (W/L) of \( {\text{M}}_{{{\text{N}}1}} \), inductor current, and on-resistance of the p-channel switch, respectively.

Transistor \( {\text{M}}_{{{\text{P}}1}} \) and resistor R serve as driver and load of the common source amplifier to amplify the small signal variation in \( {\text{V}}_{\text{LX}} \) so that it may prevent the comparator from malfunctioning due to the small variation of \( {\text{V}}_{\text{in}} \), \( {\text{I}}_{\text{L}} , \) and \( {\text{V}}_{\text{LX}} \). The large voltage gain of the common source amplifier should be able to enhance the sensitivity of the voltage-level shifting circuit with respect to the variation of \( {\text{V}}_{\text{LX}} \) and \( {\text{I}}_{\text{L}} \). However, the voltage gain should be carefully designed so that the driver, \( {\text{M}}_{{{\text{P}}1}} \), should always be in the saturation region, and \( {\text{V}}_{{{\text{SF}},{\text{amp}}}} \) should be in the ICMR of the comparator. In a similar manner, the level-shifting voltages, \( {\text{V}}_{\text{LS}} \) and \( {\text{V}}_{{{\text{LS}},{\text{amp}}}} \) are generated as seen in Fig. 2(b). Since two circuits shown in Fig. 2 are implemented with the identical circuit structure, the voltage difference between \( {\text{V}}_{{{\text{GS}}2}} \) and \( {\text{V}}_{{{\text{GS}}1}} \), namely \( {\text{V}}_{{{\text{d}}0}} = {\text{V}}_{{{\text{GS}}2}} - {\text{V}}_{{{\text{GS}}1}} \), should be independent of variation in the process, supply voltage, and temperature. Transconductance(Gm) mismatch was minimized by utilizing the long channel length of 2um for both the transistors Mp1 and Mp2. Common centroid layout technique was applied to minimize the mismatch on the resistor R. In this manner, the effect of device mismatches (Mp1, Mp2, and R) on the level shifting circuit was minimized. And the constant current \( {\text{I}}_{\text{cons}} \) of 10 μA is employed to obtain \( {\text{V}}_{{{\text{GS}}, {\text{M}}_{{{\text{N}}1}} }} \) and \( {\text{V}}_{{{\text{GS}}, {\text{M}}_{{{\text{N}}2}} }} \), so that device mismatch can be minimized.

The magnitude of the peak inductor current can be described by

where \( {\text{I}}_{\text{pk}} \) and \( {\text{t}}_{{{\text{p}},{\text{on }}}} \) are the peak inductor current and the on-time of the p-channel power switch, respectively. It is well known that the conventional PFM mode buck converters suffer from requiring additional circuitries to detect the peak inductor current accurately [4]. Since \( {\text{V}}_{{{\text{d}}0}} \) and \( {\text{R}}_{{{\text{p}},{\text{on}}}} \) stay constant in (4), the peak inductor current, \( {\text{I}}_{\text{pk}} \), remains constant regardless of variations in \( {\text{V}}_{\text{in}} \). Therefore, it is necessary to adjust the amplitude of the peak inductor current, which should be detected by the PFM buck converter with a certain degree of sensitivity.

In order to adjust the magnitude of the peak inductor current, insertion of a digitally programmable voltage level-shifting resistor array is made between \( {\text{M}}_{{{\text{N}}2}} \) and the constant current source, as presented in Fig. 3.

The digitally programmable voltage level-shifting array contains a series of binary weighted resistor arrays associated with switches—b0(LSB), b1,…, bM-1(MSB)—based on transmission gates. The magnitude of level-shifting voltage Varray is determined as follows:

where M is the number of bits to be programmed by the user. The resultant gate voltage of MP2, VLS, is obtained as follows:

Since MP2 remains in the saturation region, the drain voltage of MP2, \( V_{LS,amp} \), can be assumed to be approximately the same as VLS. A block diagram of the comparator with the switches (S1, S2, S3) and the control logic circuit is in Fig. 4. The output voltage signal, VC, of the comparator, and the output signal, \( \bar{Q} \), of the third D flip-flop serve as the clock and clear signal for three D flip-flops in the control logic circuit, respectively.

The logic states (A, B) of the control logic circuit drive the logic circuit shown in Fig. 5 to determine the logic state of the three switches (S1, S2, S3). The connections between the comparator and nine nodes are presented in Table 1.

A timing diagram of the eight signal waveforms associated with the comparator and the control logic circuit is in Fig. 6. It is assumed in the initial state that the logic state (A, B) of the control logic stays (0, 0), and it results in S1 staying high, and S2 and S3 remaining low.

Hence, two input nodes and an output node of the comparator are connected to Vref, VFB, and the S node, respectively. If Vref becomes greater than VFB, clock signal VC at time \( t_{0} \) activates the first D flip-flop, logic state A becomes high, and it results in S2 staying high and S1 and S3 remaining low. It drives the p-channel power switch to turn on, and inductor current IL begins to increase until it reaches the peak current, which will be determined by the logic state of the digitally programmable voltage level–shifting circuit shown in Fig. 3. When VSF,amp reaches the point where it is greater than VLS,amp at time t1, the clock signal activates the first and second flip-flops simultaneously. It results in the logic state of A and B staying high, S3 staying high, and S1 and S2 remaining low. It makes the p-channel power switch turn off and the n-channel power turn on, which results in the inductor current decreasing until it reaches time t2. As the comparator reaches time t2, \( S_{1} \) becomes high. This cycle is repeated over and over again. The time duration (Δt = t1 − t0) in which S2 stays high determines the magnitude of the peak inductor current, as shown in Fig. 7. The longer the time duration, the larger the peak inductor current becomes. The magnitude of the peak inductor current (Ipk) in (5) is proportional to the time duration (Δt), and can be rewritten as

where \( C_{O} \) and \( I_{P2} \) are the load capacitance and drain current of the p-channel device,\( M_{P2} \), shown in Fig. 3.

Substituting (5) into (7), Ipk can be expressed as

where \( I_{pko} = \frac{{V_{in} - V_{out} }}{L} \frac{{ C_{o} \cdot I_{cons} \cdot R}}{{I_{P2} }} \).

The peak inductor current normalized by \( I_{pko} \) determines the programmability of the proposed voltage level-shifting circuit with M bits. The maximum number of bits (M bit) of the digitally programmable voltage level–shifting circuit in Fig. 3 can be restricted by R, \( I_{cons} \), and the ICMR of the comparator.

3 Measurement results

The proposed PFM buck converter was implemented with a 180 nm CMOS process. A microphotograph of the proposed circuit is in Fig. 8. It occupies 900μm × 590μm, excluding bonding pads, gate drivers, and power switches. The analog blocks, such as the band gap reference and the current bias circuit, are on the left-hand side of the photograph, such that they are isolated from the digital blocks. Placement of two power switches and two gate drivers is on the right-hand side of the chip layout. The control logic and comparator block were placed between analog blocks and power switches. Due to the ICMR of the comparator in the given process, the number of bits of the voltage level-shifting circuit in this implementation was chosen as 4.

Figure 9 demonstrated the corner simulated slew rate waveform of VSF,amp in the voltage level-shifting circuit. The slow case(sss), typical case(ttt), and fast case(fff) slew rates of VSF,amp are simulated to be 950 mV/µs, 809 mV/µs, and 620 mV/µs, respectively. The corner simulation result shows that the slew rate of VSF,amp is sufficient to be able to sense the inductor current.

The monte-carlo simulation on the level-shifting circuit, as shown in Fig. 10, was performed to investigate device mismatches due to process variation. Figure 10 demonstrated that the average voltage gain of the level shifting amplifier was 3.45 with standard deviation of the voltage gain as 0.01. Therefore the monte-carlo simulation confirmed the Gm mismatch of Mp1 and Mp2 as well as the mismatch on the resistor R was considered to be small due to process variation.

The number of bits for the digitally programmable voltage level-shifting circuit can be expanded to increase the accuracy in controlling the peak inductor current, depending on the ICMR of the comparator and the design of the common source amplifier. Two measurement results with a programing status of (0000) and (1111) are presented in Fig. 11(a), (b), respectively. Each measurement result with an input voltage of 3.0 V and a load current of 20 mA includes four waveforms (the output voltage of the proposed PFM buck converter, \( {\text{V}}_{\text{out}} \), output voltage of the comparator, \( {\text{V}}_{\text{c}} \), the load current, \( {\text{I}}_{\text{load}} \), and the inductor current, \( {\text{I}}_{\text{L}} \)). The peak inductor current, the switching frequency, and the ripple output voltage with programming status (0000) in Fig. 11(a) were measured at 200 mA, 462 kHz, and 8.25 mV, respectively. The three pulse trains of \( {\text{V}}_{\text{c}} \) in Fig. 11(a) were proven to demonstrate the normal functionality of the comparator with control logic circuit, as shown in Fig. 6. It can be seen in Fig. 11(a) that the time interval between the first and second pulses determined the magnitude of the peak inductor current, 200 mA. In a similar manner, the appropriate functionality of the comparator with control logic circuit and logic status (1111), as presented in Fig. 11(b) can be explained. The peak inductor current, switching frequency, and ripple output voltage were measured at 802 mA, 18 kHz, and 104 mV, respectively. The ratio of time intervals with logic status (1111) between the first and second pulses with respect to the period of the pulse train increased twice, compared to that with logic status (0000), as shown in Fig. 11(a), (b).

Measured waveform of the output voltage of the proposed PFM buck converter, \( {\text{V}}_{\text{out}} \), output voltage of the comparator, \( {\text{V}}_{\text{c}} \), the load current, \( {\text{I}}_{\text{load}} \), and the inductor current, \( {\text{I}}_{\text{L}} \), with a programming status of a (0000) and b (1111)

The switching frequency as a function of the digital programming code (0000–1111) with load currents of 10 mA and 20 mA was measured to decrease quadratically, and is presented in Fig. 12. The switching frequency with a load current of 20 mA was measured at approximately two times higher than with a load current of 10 mA.

The measured peak inductor current as a function of the digital programming code with load currents of 10 mA and 20 mA is shown in Fig. 13 to be almost linear, as expected in Eq. (8), within a tolerance of 10%. Nonlinearity of the peak inductor current as a function of the digital code comes from (1) the nonlinearity of the CS amplifier in the voltage level-shifting circuit, (2) resistance mismatches in the resistor array, and (3) the turn-on resistance of switches.

The power efficiency of the proposed PFM mode buck converter is measured with various load currents ranging from 1 to 150 mA, as presented in Fig. 14. The measured power efficiency starts with 70% at a low load current of 1 mA, increases up to 84% at a load current of 30 mA, and stays at an almost constant 82% at 150 mA.

A performance comparison of the proposed PFM buck converter was made against conventional converters and is shown in Table 2. The pulse skipping methodology of Yuan et al. [8] was adopted to reduce the switching frequency with output ripple voltage fixed at 10 mV, and to increase power efficiency at low-load current. However, since the basic architecture of Yuan et al. [8] is based upon driving the PWM mode, the power efficiency became lower than that of the general PFM circuit at a high load current. The adaptive technique on time, employed by Tsai et al. [9], allows the switching frequency to vary with the output ripple voltage fixed at 20 mV. The complexity of the circuit of Tsai et al. [9] leads to a large conduction loss and lower power efficiency. The proposed circuit employs the digitally programmable voltage level–shifting circuit to allow the peak inductor current, the switching frequency, and the output ripple voltage to be changed as a function of digital code for different load currents.

4 Conclusions

This paper presented a PFM mode buck converter employing a digitally programmable voltage level–shifting technique and control logic circuit with only one comparator to control peak inductor current with the switching frequency, and consequently, output ripple voltage of the PFM buck converter under different load current conditions. The voltage level-shifting circuit, based on a common source amplifier, is capable of sensing inductor current through the voltage drop caused by the on-resistance of the power switch. Employment of one comparator with the pre-control logic and post-control logic circuits allows the proposed circuit to improve power efficiency by removing an additional circuit, compared to the conventional buck converters [4,5,6]. The proposed PFM buck converter was implemented with a 180 nm CMOS process. The effective chip size of the core block occupies 900μm × 590μm. The proposed PFM mode buck converter is capable of accommodating an input voltage range of 2.7–3.3 V and producing output voltage of 1.2 V. The operational switching frequency measured is on the order of several to several hundred kilohertz, the load current range is under 150 mA, and the measured output ripple voltage varied. The measured power efficiency ranged between 70 and 84%. The proposed technique employed by the PFM buck converter in this paper is expected to be useful not only to control peak inductor current, but also to control output ripple voltage and power efficiency, so it may be suited to different applications under various load currents.

References

Hiremath, S.,Yang, G., & Mankodiya, K. (2014). Wearable internet of things: Concept architectural components and promises for person-centered healthcare. In Wireless Mobile Communication and Healthcare (Mobihealth) 2014 EAI 4th International Conference on, pp. 304–307.

Ko, U. (2016). Ultra-low power SoC for wearable & IoT. In VLSI Technology, Systems and Application (VLSITSA), pp. 1–1.

Yoon, SW., Petrov, B., & Liu, K. (2015). Advanced wafer level technology: Enabling innovations in mobile. In IoT and wearable electronics, Electronics Packaging and Technology Conference (EPTC).

Sahu, B., & Rincon-Mora, G. A. (2007). An accurate, low-voltage, CMOS switching power supply with adaptive on-time pulse-frequency modulation(PFM) control. IEEE Transactions on Circuits and Systems I: Regular Papers, 54(2), 312–321.

Tao, C., & Fayed, A. A. (2012). A low-noise PFM-controlled buck converter for low-power applications. IEEE Transactions on Circuits and Systems I, 59(12), 3071–3080.

Chen, C.-L., Hsieh, W.-L., Lai, W.-J., Chen, K.-H., & Wang, C.-S. (2008). A new PWM/PFM control technique for improving efficiency over wide load range. In Proceedings of IEEE International Conference Electron, Circuits, Systems, pp. 962–965.

Ma, F., Chen, W., & Wu, J. (2007). A monolithic current-mode buck converter with advanced control and protection circuits. IEEE Transactions on Power Electronics, 22(5), 1836–1846.

Yuan, B., Lai, X.-Q., Wang, H.-Y., & Shi, L.-F. (2013). High-efficient hybrid buck converter with switch-on-demand modulation and switch size control for wide-load low-ripple applications. IEEE Transactions on Microwave Theory and Techniques, 61(9), 3329–3338.

Tsai, C.-H., Chen, B.-M., & Li, H.-L. (2016). Switching frequency stabilization techniques for adaptive on-time controlled buck converter with adaptive voltage positioning mechanism. IEEE Transactions on Power Electronics, 31(1), 443–451.

Fu, W., Tan, S. T., Radhkrishnan, M., Byrd, R., & Fayed, A. A. (2016). A DCM only buck regulator with hysteretic-assisted adaptive minimum-on-time control for low-power microcontrollers. IEEE Transactions on Power Electronics, 31(1), 418–429.

Kim, S. J., Choi, W. S., Pilawa-Podgurski, R., & Hanumolu, P. K. (2018). A 10 MHz 2-800 mA 0.5-1.5 V 90% peak efficiency time-based buck converter with seamless transition between PWM/PFM modes. IEEE Journal of Solid-State Circuits, 53(3), 814–824.

Park, Y. J., Park, J. H., Kim, H. J., Ryu, H. C., Kim, S. Y., Pu, Y. G., et al. (2017). A design of a 92.4% efficiency triple mode control DC–DC buck converter with low power retention mode and adaptive zero current detector for IoT/Wearable applications. IEEE Transactions on Power Electronics, 32(9), 6946–6960.

Acknowledgements

This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2010-0020163). The chip was fabricated under the IDEC MPW program.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kim, J.G., So, JW. & Yoon, K.S. A CMOS PFM buck converter employing a digitally programmable voltage level-shifting technique. Analog Integr Circ Sig Process 98, 321–329 (2019). https://doi.org/10.1007/s10470-018-1369-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1369-0