Abstract

In this paper, a single-inductor dual-output (SIDO) converter is proposed to generate stable output voltages with low load- and cross-regulations for mobile applications. The proposed converter, which operates in the buck–boost or boost mode, employs an adaptive current sensor and a low-dropout regulator with a selectable charge pump to achieve low load- and cross-regulations. In addition, an error amplifier and comparators are implemented to provide stable dual output voltages of 1.8 and 3.3 V at an input voltage range of between 1.0 and 3.2 V. The proposed SIDO converter was fabricated using a 0.18-μm CMOS process technology and occupies a chip area of 1568 μm × 728 μm. The measurement results show that the maximum power efficiency, load-regulation, and cross-regulation are 89.2%, 0.120 and 0.088 mV/mA, respectively, when the load current changes from 10 to 50 mA.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the increasing use of smart mobile devices such as wireless sensor devices, smart phones, smart watches, and smart glasses, various technologies have been developed to extend the battery life and reduce the chip area [1,2,3]. To achieve a longer battery life, the power management integrated circuit (PMIC), which generates multiple supply voltages, requires a high power efficiency and needs a wide voltage range for the battery. For compact power management systems, the PMIC should have fewer power transistors and external components, such as inductors and capacitors.

To meet the aforementioned requirements, single-inductor multiple-output (SIMO) and single-inductor dual-output (SIDO) converters have been researched [4,5,6,7,8,9,10,11,12,13]. In [4,5,6,7], the time-multiplexing and time-sharing methods regulated the multiple output voltages of the converter, but showed poor ripple and cross-regulation characteristics. In [8], the power-distributive control method with freewheeling switching achieved reasonable cross-regulation, but was still limited in lowering cross-regulation further because the cross-regulations of all outputs were interdependent. In [9], the hybrid converter using the current sensor and a low-dropout (LDO) regulator improved cross-regulation, but only when the input voltage was higher than the output voltage. The extended-PWM control method in [10] only employs the current sensor without using the LDO, thereby performing poor load- and cross-regulations. Furthermore, it occupies a large area due to many power switches needed to implement a buck and boost topology. The SIMO converter controlled by the freewheel charge pump in [11] uses the current sensor with the charge-pump, but the charge pump is only used for generating the additional output voltage, not for improving the regulation characteristic. Thus, it occupies a large area due to many power switches and requires a large output capacitor for the charge pump, and shows a poor regulation of the final output. Moreover, its power efficiency would be estimated to be low due to many switches and diodes, and charge pump operation at steady state.

In this paper, a SIDO converter is proposed to generate stable output voltages and achieve low load- and cross-regulations while minimizing the chip area; this is accomplished by using a fewer number of power switches with a small-sized freewheeling switch at a zero inductor current. The proposed converter using an error amplifier and comparators generates stable step-up and step-down output voltages, which are greater and less than the input voltage of the battery, respectively. The adaptive current sensor, which accurately detects the inductor current, and the LDO regulator with selectable charge pump is implemented in the proposed converter to achieve low load- and cross-regulations in both the buck–boost and boost modes. In Sect. 2, we describe the detailed architecture and operation principle of the proposed SIDO converter with an adaptive current sensor. In addition, the LDO regulator with a selectable charge pump is explained in detail. In Sect. 3, the experimental results are analyzed and compared with prior works. Finally, conclusions are given in Sect. 4.

2 The proposed SIDO converter

2.1 Architecture and operation principles

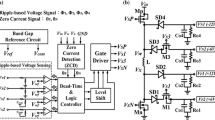

Figure 1 shows the block diagram of the proposed SIDO converter with four power switches (M FR , M N , M OP1, and M OP2), of which the main power switches (M FR and M N ) control the inductor current (I L ) to adjust the load currents (I OUT1 and I OUT2), and the output power switches (M OP1 and M OP2) deliver I OUT1 and I OUT2 to the dual outputs (V OUT1 and V OUT2), respectively. The proposed converter operates in the buck–boost or boost mode according to the mode selection signals (V B ) generated from the mode selector by comparing the input voltage (V IN ) with the target dual output voltages (V REF1 and V REF2).

An adaptive current sensor detects I L , then scales down and mirrors the peak I L . The sensor subsequently generates the sensing voltage (V SEN ), which is used in the power delivery control block to improve the regulation characteristics using the current-programmed control [12,13,14]. A 4-input folded cascade error amplifier compares V OUT1 and V OUT2 with V REF1 and V REF2, respectively, and generates an output error voltage (V ERR ) by accumulating all output errors. The comparators (CMP 1 and CMP 2) compare V OUT1 and V OUT2 with V REF1 and V REF2, and generate V CM1 and V CM2, which control V OP1 and V OP2, respectively, to prevent the dual outputs from the over-voltage. The power delivery control block then generates the non-overlapping gate driving signals (V FR , V N , V OP1, and V OP2) according to V SEN and V ERR in order to adjust the energizing and de-energizing periods of the inductor. V FR controls the free-wheeling switch (M FR ) at a zero inductor current to avoid a reversely flowing inductor current, whereas V N , V OP1, and V OP2 control the switches (M N , M OP1, and M OP2, respectively) to energize and de-energize I L . The energizing and de-energizing periods, along with V CM1 and V CM2, determine the amount of power to be delivered to the dual outputs so that V OUT1 and V OUT2 can be regulated to V REF1 and V REF2, respectively. In addition, the LDO regulator with a selectable charge pump having a high bandwidth is implemented to improve the regulation characteristics of the proposed converter, while rapidly regulating the dual outputs by activating the charge pump for a step-up voltage, which will be explained in detail in Sect. 2.3.

Figure 2(a–c) respectively show the input voltage of the proposed converter, the timing diagram of the operation of switches (M OP1, M OP2, and M N ), and I L in the buck–boost and boost modes.

When V IN is between V REF1 and V REF2, the proposed SIDO converter operates in the buck–boost mode, in which the I L flows through paths (3), (1), and (2) in sequence, where the inductor is energized in paths (3) and (1), and de-energized in path (2). First, when M OP1 and M OP2 are turned off and M N is turned on, I L flows through path (3) and increases with a slope of V IN /L. Second, when M OP2 and M N are turned off, and M OP1 is turned on, I L flows through path (1) and increases with a slope of (V IN − V OUT1)/L. Last, when M OP1 and M N are turned off, and M OP2 is turned on, I L flows through path (2) and decreases with a slope of (V IN − V OUT2)/L.

When V IN is less than V REF1 and V REF2, the proposed SIDO converter operates in the boost mode, in which I L flows through paths (3), (1), and (2) in sequence, where the inductor is energized in path (3), and de-energized in paths (1) and (2). First, when M OP1 and M OP2 are turned off, and M N is turned on, I L flows through path (3) and increases with a slope of V IN /L. Second, when M OP2 and M N are turned off, and M OP1 is turned on, I L flows through path (1) and decreases with a slope of (V IN − V OUT1)/L. Last, when M OP1 and M N are turned off, and M OP2 is turned on, I L flows through (2) and decreases with a slope of (V IN − V OUT2)/L. Thus, in the buck–boost and boost modes, the energizing and de-energizing periods are adjusted differently by controlling the flowing path of I L using V N , V OP1, and V OP2, and thereby V OUT1 and V OUT2 are regulated to V REF1 and V REF2, respectively.

2.2 Proposed adaptive current sensor

Figure 3(a) shows the schematic of the proposed adaptive current sensor, which consists of a current_sensor1, a current_sensor2, and a summing circuit.

In the current_sensor1, when I L flows through path (3), the peak I L is scaled down by 1/K, where K is the scaling ratio of the transistor size between M N and M SC1, and then flows through M SC1. The scaled current (I SC1) is mirrored to the currents of switches (M N1–M N5) (I SEN ) through OTA 1, where M N5 and OTA 1 are used to achieve a high current accuracy by minimizing the channel length modulation effect [15].

In the current_sensor2, when I L flows through path (1) [or path (2)], the peak I L is scaled down by 1/K, where K is the scaling ratio of the transistor size between M OP1 (or M OP2) and M SC2 and then flows through M SC2 and M K1. The scaled current (I SC2) is mirrored to the currents of switches (M K1–M K6) (I SEN ) through OTA 2, where M K1 and OTA 2 are also used to achieve a high current accuracy. To have an accurate scaling ratio, K, the source-drain voltage of M SC2 is designed to be equal to that of M OP1 and M OP2, assuming that M S1 and M S2 have a large size so that their resistance values can be ignored.

In the summing circuit, I SEN is converted to the summing voltage (V S ) via the sensing resistor (R SEN ). However, when M N and M OP1 (or M OP2) are simultaneously turned on, glitches such as switching noise and voltage drop at V S occur during the transition. Thus, to remove these glitches, a diode (D 1) and a capacitor (C 1) are used in the summing circuit, and M K7 periodically refreshes V SEN using a reset signal (V CLK ) synchronized at the operating clock of the converter.

Since I SC1 and I SC2 of the current sensor should be regulated within a minimum on-time of V N and V OP1 (or V OP2), respectively, the required bandwidth of the current sensor should be greater than 1/[minimum on-time of V N and V OP1 (or V OP2)]. The minimum on-time of V N and V OP1 (or V OP2) can be obtained by the product of the minimum on-duty of V N and V OP1 (or V OP2), and the operating period of the proposed converter, respectively [14]. In addition, the tolerable error of I SEN can be determined according to an acceptable variation in V OUT .

Figure 3(b, c) show the timing diagrams of I L and V SEN in the buck–boost and boost modes, respectively. In the buck–boost mode, the peak I L in paths (3) and (1) is sequentially sensed by enabling both current_sensor1 and current_sensor2, and I SEN is then converted to V SEN through the summing circuit. In the boost mode, the peak I L in path (3) is sensed by enabling current_sensor1 and disabling current sensor2, and I SEN is converted to V SEN . Therefore, the proposed adaptive current sensor accurately detects the peak I L and generates V SEN , which is used in the power delivery control block to improve the regulation characteristics.

2.3 LDO regulator with selectable charge pump

When the load current of the proposed SIDO converter abruptly changes, the LDO regulator is used to achieve a fast transient response by compensating for the insufficient inductor current of the switching converter because the bandwidth of the LDO regulator is greater than that of the switching converter [16,17,18,19,20]. The selectable charge pump, which is used to generate two step-up voltages of V CP1 and V CP2 according to the input and output voltages, always operates both in the steady state and in the load transient, whereas the LDO regulator only operates in the load transient. The LDO regulator with selectable charge pump is designed with smaller-sized power transistors compared with the switching converter [21, 22], thereby achieving low load- and cross-regulations without degrading power efficiency.

Figure 4 shows the structure of the LDO regulator with a selectable charge pump. The selectable charge pump consists of a pumping ratio control and driving block, and pumping blocks for V CP1 and V CP2. Each pumping block has three stages, which are used to sufficiently pump up V CP1 and V CP2 to regulate V OUT1 and V OUT2, respectively. The LDO regulator, which consists of two error amplifiers (OTA 3 and OTA 4), pass transistors (M P1 and M P2), and a transient detection block, has a dropout voltage (V LDO ). In the selectable charge pump, a pumping ratio control and driving block determines the pumping ratios according to V IN , V REF1, and V REF2 by enabling or disabling each stage using the driving switches and capacitors. When a stage is enabled, its output voltage increases by V IN , whereas when a stage is disabled, its output voltage remains at its input voltage.

When V IN is greater than V REF1 + V LDO , considering the dropout voltage of the LDO regulator, the proposed SIDO converter operates in the buck–boost mode. In this case, the selectable charge pump enables only one stage for V CP2 and disables the rest of the stages for V CP1 and V CP2, and so V CP1 and V CP2 become V IN and 2 × V IN , resulting in being greater than V REF1 + V LDO and V REF2 + V LDO , respectively. When V IN is less than V REF1 + V LDO , the proposed SIDO converter operates in the boost mode. In this case, the selectable charge pump enables one, two, or three stages among stages in the pumping blocks according to V IN , V REF1, and V REF2, thereby generating 2×, 3×, or 4 × V IN , respectively, for both V CP1 and V CP2. Thus, V CP1 and V CP2 can be sufficiently pumped up to be greater than V REF1 + V LDO and V REF2 + V LDO , respectively. The sizes of the pumping capacitors for V CP1 and V CP2 (C Ln and C Hn ) are determined given that the supplied charge to the charge pump should be larger than or equal to the released charge from the charge pump. Furthermore, the sizes of the load capacitors for V CP1 and V CP2 (C CP1 and C CP2) are determined by considering the output ripple voltage [23].

In the LDO regulator, the transient detection block detects the load transition at V OUT1 and V OUT2, and enables OTA 3 and OTA 4 to convert V CP1 and V CP2 to V REF1 and V REF2 through M P1 and M P2, respectively, with a voltage drop of V LDO . Therefore, V OUT1 and V OUT2 can be rapidly regulated to V REF1 and V REF2, respectively.

3 Experimental results

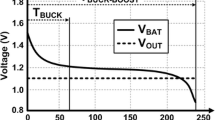

Figure 5(a) shows the chip microphotography of the proposed SIDO converter, which is fabricated using a 0.18-µm CMOS technology and occupies an area of 1142 mm2 (1568 μm × 728 μm). Figure 5(b) shows the photograph of the printed circuit board (PCB) with a module size of 18 mm × 16 mm, including the proposed chip, an inductor, and capacitors. To verify the performance of the proposed converter, an input voltage ranging between 3.2 and 1.0 V is used and two output voltages are designed to be 1.8 and 3.3 V with a maximum output current of 200 mA at an operating frequency of 500 kHz.

Figure 6 shows the measured input and output voltages, and I L at V OUT1 = 1.8 V, V OUT2 = 3.3 V, I OUT1 = 100 mA, and I OUT2 = 100 mA: (a) when V IN = 3.1 V in the buck–boost mode and (b) when V IN = 1.0 V in the boost mode. Figure 7 shows that the dual output voltages can be regulated in an extended range of between 1.0 and 4.5 V.

Figure 8 shows the measured load-regulation of V OUT2 and cross-regulation of V OUT1 when I OUT2 changes from 10 to 50 mA and vice versa. Without the LDO regulator and selectable charge pump, the load- and cross-regulations are 0.375 and 0.264 mV/mA, respectively, as shown in Fig. 8(a). With the LDO regulator and selectable charge pump, the load- and cross-regulations are 0.120 and 0.088 mV/mA, respectively, as shown in Fig. 8(b), showing that the voltage fluctuation is not noticeable. When V IN changes from 2.0 to 3.0 V and from 3.0 to 2.0 V as shown in Fig. 9(a, b), respectively, V OUT2 varies by less than 63 mV, and thereby the proposed converter has a line regulation of less than 0.063 mV/mV. On the other hand, V OUT1 varies unnoticeably. These measurement results demonstrate that the output voltages of the proposed SIDO converter are well regulated using the LDO regulator with selectable charge pump regardless of the changes in the load current and input voltage.

Figure 10(a, b) show the power efficiencies according to the load currents at V OUT1 = 1.8 V and V OUT2 = 3.3 V, where the maximum efficiencies are 89.2% in the buck–boost mode at the I OUT1 and I OUT2 of 100 mA, and 88.3% in the boost mode at a I OUT1 of 100 mA and a I OUT2 of 0 mA, respectively. Although the proposed converter achieves small-area and high current density, the maximum power efficiency was limited to 89.2% mainly due to the conduction and switching losses of power switches, having 5.490 and 4.476%, respectively.

Table 1 shows the performance summary of the proposed converter compared with prior works. The proposed SIDO converter achieves the low load- and cross-regulations of 0.120 and 0.088 mV/mA, respectively. Moreover, it has the highest current density of 350.00 mA/mm2, which is represented as the ratio of the maximum load current to the chip area and the smallest value of the product of LC, compared with prior works.

4 Conclusions

In this paper, a SIDO converter that operates in the buck–boost and boost modes is proposed to generate stable output voltages and achieve low load- and cross-regulations. The proposed adaptive current sensor detecting the peak inductor current without glitches and an LDO regulator with a selectable charge pump are adopted to achieve low load- and cross-regulations. The proposed SIDO converter was fabricated using a 0.18-µm CMOS process technology and occupies an area of 1568 μm × 728 μm. The regulated dual output voltages are 1.8 and 3.3 V and can be extended to be between 1.0 and 4.5 V. The measured load- and cross-regulations of the proposed SIDO converter are reduced to 0.120 and 0.088 mV/mA when the load current changes from 10 to 50 mA. In addition, the proposed SIDO converter achieves a high current density and the smallest value for LC product compared with prior works. Therefore, the proposed SIDO converter is suitable for mobile devices, which require low load- and cross-regulations, a high current density, and a small form factor.

References

Sze, N., Su, F., Lam, Y., Ki, W., & Tsui, C. (2008). Integrated single-inductor dual-input dual-output boost converter for energy harvesting applications. In Proceedings of IEEE ISCAS (pp. 2218–2221).

Penella, M. T., & Gasulla, M. (2010). Runtime extension of low-power wireless sensor nodes using hybrid-storage units. IEEE Transactions on Instrumentation and Measurement, 59(4), 857–865.

Nakase, Y., Ido, Y., Oishi, T., Kumamoto, T., & Shimizu, T. (2013). Wide input range from 80 mV to 3 V operation on-chip single-inductor dual-output (SIDO) DC–DC boost converter with self-adjusting clock duty for sensor network applications. In IEEE Asian Solid-State Circuits Conference (A-SSCC) (pp. 41–44).

Ma, D., Ki, W. H., & Tsui, C. Y. (2003). A pseudo-CCM/DCM SIMO switching converter with freewheel switching. IEEE Journal of Solid-State Circuits, 38(6), 1007–1014.

Bonizzoni, E., Borghetti, F., Malcovati, P., Maloberti, F., & Niessen, B. (2007). A 200 mA 93% peak efficiency single-inductor dual-output DC–DC buck converter. In IEEE ISSCC Digest of Technical Papers (pp. 526–619).

Leung, C. Y., Mok, P. K. T., & Leung, K. N. (2005). A 1-V integrated current mode boost converter in standard 3.3/5-V CMOS technologies. IEEE Journal of Solid-State Circuits, 40(11), 2265–2274.

Belloni, M., Bonizzoni, E., Kiseliovas, E., Malcovati, P., Maloberti, F., Peltola, T., et al. (2008). A 4-output single-inductor DC–DC buck converter with self-boosted switch drivers and 1.2 A total output current. In IEEE ISSCC Digest of Technical Papers (pp. 444–626).

Le, H.-P., Chae, C.-S., Lee, K.-C., Wang, S.-W., Cho, G.-H., & Cho, G.-H. (2007). A single-inductor switching DC–DC converter with five outputs and ordered power-distributive control. IEEE Journal of Solid-State Circuits, 42(12), 2706–2714.

Zhang, Y., & Ma, D. (2014). A fast-response hybrid SIMO power converter with adaptive current compensation and minimized cross-regulation. IEEE Journal of Solid-State Circuits, 49(5), 1242–1257.

Xu, W., Li, Y., Hong, Z., & Killat, D. (2011). A 90% peak efficiency single-inductor dual-output buck–boost converter with extended-PWM control. In IEEE ISSCC Digest of Technical Papers (pp. 394–396).

Huang, M.-H., Tsai, Y.-N., & Chen, K.-H. (2013). Freewheel charge-pump controlled single-inductor multiple-output step-up DC–DC converter. Analog Integrated Circuit Signal Processing, 74(1), 215–225.

Lee, Y.-H., Yang, Y.-Y., Wang, S.-J., Chen, K.-H., Lin, Y.-H., Chen, Y.-K., et al. (2011). Interleaving energy-conservation mode (IECM) control in single-inductor dual-output (SIDO) step-down converters with 91% peak efficiency. IEEE Journal of Solid-State Circuits, 46(4), 904–914.

Lee, Y.-H., Huang, T.-C., Yang, Y.-Y., Chou, W.-S., Chen, K.-H., Huang, C.-C., et al. (2011). Minimized transient and steady-state cross regulation in 55-nm CMOS single-inductor dual-output (SIDO) stepdown DC–DC converter. IEEE Journal of Solid-State Circuits, 46(11), 2488–2499.

Erickson, R. W., & Maksimovic, D. (2001). Fundamentals of power electronics (2nd ed.). Boston: Kluwer.

Gray, P., Hurst, P. J., Lewis, S. H., & Meyer, R. G. (2001). Analysis and design of analog integrated circuits (4th ed.). New York: Wiley.

Shih, C.-J., Chu, K.-Y., Lee, Y.-H., & Chen, K.-H. (2011). Hybrid buck-linear (HBL) technique for enhanced dip voltage and transient response in load-preparation buck (LPB) converter. In Proceedings of IEEE European Solid-State Circuits Conference (ESSCIRC) (pp. 431–434).

Ertl, H., Kolar, J. W., & Zach, F. C. (1997). Basic considerations and topologies of switched-mode assisted linear power amplifiers. IEEE Transaction on Industrial Electronics, 44(1), 116–123.

Van der Zee, R. A. R., & van Tuijl, A. J. M. (1999). A power-efficient audio amplifier combining switching and linear techniques. IEEE Journal of Solid-State Circuits, 34(7), 985–991.

Stauth, J. T., & Sanders, S. R. (2007). Optimum biasing for parallel hybrid switching-linear regulators. IEEE Transaction on Power Electronics, 22(5), 1978–1985.

Liu, Y., Zhan, C., & Ki, W.-H. (2012). A fast-transient-response hybrid buck converter with automatic and nearly-seamless loop transition for portable applications. In Proceedings of IEEE European Solid-State Circuits Conference (ESSCIRC) (pp. 165–168).

Teh, C. K., & Suzuki. A. (2016). A 2-output step-up/step-down switched-capacitor DC–DC converter with 95.8% peak efficiency and 0.85-to-3.6 V input voltage range. In IEEE ISSCC Digest of Technical Papers (pp. 222–223).

Schaef, C., Kesarwani, K., & Stauth, J. T. (2015). A variable-conversion-ratio 3-phase resonant switched capacitor converter with 85% efficiency at 0.91 W/mm2 Using 1.1 nH PCB-trace inductors. In IEEE ISSCC Digest of Technical Papers (pp. 360–361).

Texas Instruments. (2016). TPS60150 5-V, 140-mA charge-pump. http://www.ti.com/lit/ds/symlink/tps60150.pdf. Accessed Dec 2008.

Acknowledgements

This work was supported by the Silicon Mitus Company.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jung, YH., Hong, SK. & Kwon, OK. A low load- and cross-regulation SIDO converter using an adaptive current sensor and LDO regulator with a selectable charge pump for mobile devices. Analog Integr Circ Sig Process 92, 293–301 (2017). https://doi.org/10.1007/s10470-017-0990-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0990-7