Abstract

In this paper, memristor emulator circuit which is built with off the shelf electronic devices is presented. It consists of three operational transconductance amplifiers (OTA) and four second generation current conveyors (CCII). Using OTA offers an extra control parameter, operational transconductance parameter (gm), in addition to frequency (f) and amplitude value of voltage across emulator (v m ). Since gm is proportional to current flowing through the bias terminal of OTA, it is possible to change the memristance variation via a simple change of amplitude value. Since gm parameter is adjustable via an external dc voltage/current source, the memristance of presented emulator circuit is electronically tuneable. Mathematical model is derived to characterize the behaviour of the emulator circuit. Frequency analysis is performed to determine how to maintain the pinched hysteresis loop at high frequencies. The presented emulator circuit is simulated with SPICE simulation program. The breadboard experiment of emulator circuit is built using CA3080 and AD844 ICs for OTA and CCII devices respectively. Frequency dependent pinched hysteresis loop in the current versus voltage plane holds up to 10 kHz. Mathematical model and theoretical analyses show a good agreement with SPICE simulation and experimental test results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

There are four circuit variables in circuit theory; namely charge, voltage, current and flux. Five of possible six combinations between circuit variables are well known. Three of them defines resistor, capacitor and inductor. Current and voltage are defined by two of remaining possible three combinations. Prof. Leon Chua, postulated the mathematical relations of the fourth fundamental two terminal circuit element, memristor, which defines the missing relation between flux and charge [1]. Memristor is a nonlinear resistor with memory. In 1976, Chua and Kang generalized memristor concept to much broader class called memristive systems [2]. Both memristor and memristive devices have the pinched hysteresis loop in the current versus voltage plane. Thus, the resistance of the device depends on the time history of the current flowing through it. Under sinusoidal excitation, the area of the pinched hysteresis loop is inversely proportional to frequency of voltage signal across the memristor [2]. On May 1, 2008 Stanley Williams and his group fabricated two terminal memristor using titanium dioxide (TiO2) nanoscale device [3]. Recently, Di Ventra et al. [4] extended the notion of memristive systems to memcapacitive and meminductive systems and defined the special cases of the newly extended systems as memcapacitors and meminductors. Scientists have used memristor in wide application areas such as; programmable logic, signal processing, neural networks, oscillators, image processing, etc. [5–10] since the first physical realization of memristor.

It is important to have a simulation model for memristive devices to investigate their effects in circuits and verify the theoretical analyses. In the literature, several SPICE models for memristor [12–23] memcapacitor [24] and meminductor [25] elements have been proposed.

Memristor is still unavailable commercially. It is difficult to fabricate it due to technical drawbacks and high cost. In the literature several emulator circuits for memristor have been presented in order to experimentally explore dynamics of memristor in electronic circuits [26–40]. Indeed, Prof. Leon Chua proposed the first emulator circuit with relatively complex and bulky structure [1]. Many of the emulator circuits in the literature were realized using analog multiplier to obtain flux controlled memristance [26, 30, 31, 34–37, 39]. Analog multiplier circuit is used to multiply the flux of the emulator with the voltage across emulator circuit. Some emulator circuits have grounded restriction [26, 28, 29, 32, 33, 38, 39]. In [26], a flux controlled emulator circuit with smooth piecewise-quadratic nonlinearity was proposed and used in a chaotic circuit. The emulator circuit was complex and bulky. Pershin and Ventra proposed a memristor emulator using digital potentiometer, microcontroller and analog to digital converter and used in programmable analog circuits. The presented memristor emulator was based on threshold-type behaviour. The emulator had some drawbacks since the resolution of digital signal and digital potentiometer is finite [27]. Biolek et al. [28] presented a mutator which transform a nonlinear resistor into memristor. In [29], memristor emulator that consists of an integrator and a controllable resistor. JFET was used as a controllable resistor by the output voltage of integrator block in presented emulator circuit. In [30], an incremental/decremental memristor emulator was proposed. It requires several integrated circuits and it is bulky with limited operation frequency. Abuelma’atti and Khalifa [32, 33] presented memristor emulator using current feedback operational amplifiers and used in digital circuits. In [34], floating flux controlled memristor emulator is presented using two op amps and single analog multiplier. Presented memristor emulator circuit in the same study was transformed to memcapacitor circuit by using current conveyors. In [35, 36], floating flux controlled memristor emulator using current conveyors was presented. Elwakil et al. [38] proposed a mathematical model capable of generating double loop hysteresis behaviour and an emulator circuit using current conveyors and analog multiplier which satisfies the model. In [39], a grounded charge controlled memristor emulator was presented using CMOS DDCC and analog multiplier.

In this paper, memristor emulator circuit using OTA and CCII elements is proposed. Using OTA offers an extra control parameter, transconductance parameter (gm), in addition to frequency (f) and amplitude values of applied voltage across emulator (v m ), in order to adjust memristance variation. Furthermore, the proposed emulator circuit has continuous state levels to achieve several memristance levels different from emulators with binary state levels. It is shown by frequency analysis that the pinched hysteresis loop holds up to 10 kHz. In Sect. 2, we introduce our emulator circuit with its mathematical model. In Sect. 3, frequency analysis is performed. Simulation results are given in Sect. 4. Conclusion of the paper is given in Sect. 5.

2 Memristor emulator circuit

Memristor defines a nonlinear relationship between charge q and flux φ. It is the fourth fundamental circuit element since its characteristics cannot be duplicated by any combination of other fundamental circuit elements. For a charge controlled memristor, its relation is φ(t) = φ(q), where its relation becomes q(t) = q(φ) for flux controlled memristor. For a flux controlled memristor, nonlinear constitutive relationship between the memristor terminal voltage v and the internal current i can be written as following equation.

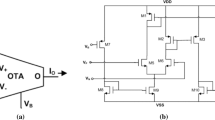

In this paper, flux controlled memristor emulator which works only for floating state is proposed. In case of grounding one of the terminal, the mathematical relations for memristance become obsolete. It uses three operational transconductance amplifiers, four second generation current conveyors, six resistors and one capacitor elements as given in Fig. 1. The gm parameters of U5 and U6 are used for multiplication process. Therefore only gm parameter of U1 (gm1) can be used to change memristance characteristic besides f and v m .

In ideal case, current flowing through input terminals of operational transconductance amplifier and terminal Y of CCII is zero. Hence, for the presented circuit, all current passes through the resistor R1. Input current can be written as following where v A (t) defines voltage at node A.

U1 with capacitor C (omitting R2) perform integral function. R2 is used to eliminate the output offset of the integrator. When DC level is ignored the mathematical relation of the integrator block can be given as the following;

where gm1 denotes the transconductance parameter of U1. Since the flux is defined as φ AB (t) = ∫ (v A (τ) − v B (τ))dτ, relation given in (3) can be written as;

U2 and U3 are used to copy voltages v A (t) and v φ (t) without any current copying to their terminal X, since the current flowing through terminal Y of CCII is zero [11]. U4 is used to perform the input–output current equality with U7 since the current flowing through terminal X of CCII is equal to current flowing through terminal Z. Thus the following relations are obtained.

OTA pairs U5 and U6 are used to multiply the voltages v 1(t) and v 2(t) denoted in Fig. 1 [41]. The mathematical description of the multiplying process using U5 and U6 devices can be obtained as;

where VT is the thermal voltage given by KT/q. Thermal voltage (T) is 26 mV at room temperature, K is Boltzmann’s constant and q is charge. When there is not an important change in room temperature, the effect of VT on circuit operation becomes negligible.

U7 is used to copy the voltage v 3(t) to node B and provides all current at outputs of U5 and U6 to flow through resistor R3. Hence, the voltage across the emulator circuit can be written as;

By making use of (2) the following equation can be obtained;

It is obvious from (8) that the memristance expression for flux controlled memristor emulator circuit can be obtained as;

3 Frequency behaviour analysis

The emulator circuit has a memristance expression which consists of connected series of a linear time invariant resistor with a flux and gm1 controlled linear time varying resistor. Assuming that the power supply for used ICs is ± Vdd and a sinusoidal voltage v AB (t) = v m sin (2πft) is imposed on terminals A and B, the memristance can be calculated as;

The relationship between time variant and time invariant parts of memristance denotes the frequency and gm1 dependence of pinched hysteresis loop. The relationship between two parts can be described by the ratio of amplitudes of time variant and time invariant parts as following.

where \(\tau = \frac{{4\pi V_{T} R_{5} C}}{{g_{m1} R_{3} v_{m} }}\) is the time constant of the emulator circuit. It is obvious from (11) that k is inversely proportional to f. On the other hand increasing gm1 will increase k on the contrary f. Therefore, gm1 and f can be used for holding pinched hysteresis loop at high frequencies. There are three conditions between k and pinched hysteresis loop of memristance.

-

1.

k → 0, the memristance approximates to linear resistor.

-

2.

k → 1 the memristance has the maximum pinched hysteresis loop.

-

3.

k ≥ 1 the memristance value will have negative or zero value due to “cos(2πft)” expression in Eq. (10).

Consequently the numerical value of k must be on the interval, i.e., 0 < k < 1 for achieving pinched hysteresis loop. Since “cos(2πft)” can take values in the interval ± 1, in order to obtain positive memristance value, f must satisfy the following denoted in (11). Since voltages on circuit branches must be bounded by power supply voltage Vdd, it is more logical to use f and gm1 as control parameters of pinched hysteresis loop rather than v m . Capacitor C, with other parameters; f, v m , gm1, can be used to for holding pinched hysteresis loop at high frequencies. The approximated values for C in function f are given in Fig. 2 for k = 0.5.Values of the other elements are given in Table 1.

Therefore, based on (10) and (11), and the configuration of v A (t) − v B (t), all the possible values of memristance satisfy the following;

The additional control parameter, gm1, is adjusted via an external DC voltage source, Vcontrol, as shown in Fig. 1. The value of gm1 is determined by the relation which is given in (14). It is derived by taking the schematic diagram of OTA type CA3080 into account [42].

4 Simulation and experimental test results

Theoretical analyses are verified using PSPICE simulation program. SPICE models of CA3080 and AD844 ICs are used for OTA and CCII devices, respectively. The circuit parameters used in simulations are given in Table 2. In order to hold loop up at 10 kHz, values of R2 and C are altered. The new values are given in Table 2. Comparison of presented memristor emulator circuit with other published studies is given in Table 1.

Simulation results given in Fig. 3 are obtained for two distinct gm1 parameters; i.e., 1.13 and 0.28 mA/V. The emulator circuit is simulated for different frequencies for each gm1 parameter. These gm1 values are determined randomly. It is obvious from (10) and (11) that for bigger gm1 parameter, the area of pinched hysteresis loop increases and vice versa. In order to maintain the pinched hysteresis loop, value of capacitor C is changed together with R2 as given in Table 2. Therefore, it is possible to maintain memristance characteristic at high frequencies. SPICE simulation results given in Fig. 3(a–f) are obtained for 10 Hz, 100 Hz, 1 kHz, 5 kHz, 8 kHz and 10 kHz respectively. It is seen from the figures that the area of pinched hysteresis loop increases for higher gm1 parameters for each frequency value as it is expected from (10) and (11). It is obtained from simulation results that the reaction of pinched hysteresis loop is different for each frequency value due to the value of capacitor C in the integrator block. This situation confirms (10) and (12). When the value of C is choose high, the variation of memristance becomes smaller and vice versa. As it is seen in Fig. 3(a–f), frequency dependence of hysteresis loop can be controlled by g m1 parameter and mainly with C and R2 elements. Therefore, it becomes possible to hold up memristance characteristic at high frequencies. The power consumption of the presented emulator circuit is calculated as 1.2 µW.

The breadboard experiment of proposed emulator circuit is built using commercially available ICs; CA3080 and AD844 for OTA and CCII elements, respectively. Numerical values of passive elements are given in Table 2. Measurements are obtained for each gm1 parameter as performed in SPICE simulations. Circuit parameters given in Table 2 are used. Since v A (t) is R1 times of input current, the numerical values of voltages v A (t) and v AB (t) are taken by a flash memory and plotted using Grapher plot program. Figure 4(a–d) show the Grapher program outputs for 100 Hz, 1 kHz, 5 kHz, and 10 kHz respectively. Frequency dependence of the pinched hysteresis loop shows high accuracy with simulation results and mathematical model of memristor emulator circuit. Also, the picture of i−v hysteresis for each gm1 parameter is included for f = 1 kHz in Fig. 5.

5 Conclusion

In this paper, an emulator circuit of a flux-controlled memristor which is composed of OTAs and CCIIs has been presented. The most significant feature of the proposed emulator circuit is the possibility of controlling memristance value by changing transconductance parameter of one of the used operational transconductance amplifier by a bias voltage. By this way, in addition to frequency and amplitude values of input voltage across memristor, transconductance parameter is added as a control parameter for memristance variation. The mathematical expressions are given to describe the behavior of presented circuit. CA3080 and AD844 ICs are used to build the emulator circuit for practical application of memristor. It has continuous state levels to achieve several memductance levels which are different from emulators with binary state levels. Frequency analysis has been performed to present a design guideline to hold pinched hysteresis loop of current–voltage curve at high frequencies. Moreover, our emulator works for different frequency ranges with a simple change in capacitor C. The oscilloscope measurements from the breadboard experiment circuit and SPICE simulation results verifies the theoretical analyses.

References

Chua, L. O. (1971). Memristor-the missing circuit element. IEEE Transactions on Circuit Theory, 18(5), 507–519.

Chua, L. O., & Kang, S. M. (1976). Memristive devices and systems. Proceedings of the IEEE, 64(2), 209–223.

Strukov, D. B., Snider, G. S., Stewart, D. R., & Williams, R. S. (2008). The missing memristor found. Nature, 453, 80–83.

Di Ventra, M., Pershin, Y. V., & Chua, L. O. (2009). Circuit elements with memory: Memristors, memcapacitors, and meminductors. Proceedings of the IEEE, 97(10), 1717–1724.

Kim, H., Sah, M. P., Yang, C., Roska, T., & Chua, L. O. (2012). Memristor bridge synapses. Proceedings of the IEEE, 100(6), 2061–2070.

Pershin, Y. V., & Di Ventra, M. (2012). Neuromorphic, digital, quantum computation with memory circuit elements. Proceedings of the IEEE, 100(6), 2071–2080.

Merrikh-Bayat, F., Bagheri-Shouraki, S., & Rohani, A. (2011). Memristor crossbar-based hardware implementation of IDSmethod. EEE Transactions on Fuzzy Systems, 19(6), 1083–1096.

Shin, S., Kim, K., & Kang, S. M. (2013). Resistive computing: Memristors enabled signal multiplication. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(5), 1241–1249.

Talukdar, A., Radwan, A., & Salama, K. (2011). A memristor-based third-order oscillator: Beyond oscillation. Applied Nanoscience, 1(3), 1–3.

Yilmaz, Y., & Mazumder, P. (2013). Image processing by a programmable grid comprising quantum dots and memristors. IEEE Transactions on Nanotechnology, 12(6), 879–887.

Sedra, A., & Smith, K. (1970). A second-generation current conveyor and its applications. IEEE Transactions on Circuit Theory, 17(1), 132–134.

Zhang, Y., Zhang, X., & Yu, J. (2009). Approximated SPICE model for memristor. In International conference on communications, circuits and systems (ICCCAS), Milpitas, CA (pp. 928–931).

Benderli, S., & Wey, T. A. (2009). On SPICE macromodelling of TiO2 memristors. Electronics Letters, 45(7), 377–379.

Biolek, D., Biolek, Z., & Biolkova, V. (2009). SPICE modeling of memristive, memcapacitative and meminductive systems. In Proceedings of the European conference on circuits theory and design (ECCTD’09), Antalya, Turkey (pp. 249–252).

Mahvash, M., & Parker, A. (2010). A memristor SPICE model for designing memristor circuits. In Proceedings of the 53rd IEEE international midwest symposium on circuits and systems (MWSCAS), Seattle,USA (pp. 989–992).

Batas, D., & Fiedler, H. (2011). A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling. IEEE Transactions on Nanotechnology, 10(2), 250–255.

Rak, A., & Cserey, G. (2010). Macromodelling of the memristor in SPICE. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 29(4), 632–636.

Sharifi, M. J., & Banadaki, Y. M. (2010). General SPICE models for memristor and application to circuit simulation of memristor-based synapses and memory cells. Journal of Circuits, Systems and Computers, 19(2), 407–424.

Abdalla, H., & Pickett, M. D. (2011). SPICE modelling of memristors. In IEEE international symposium on circuits and systems (ISCAS), Rio de Janeiro (pp. 1832–1835).

Abraham, I., Kaya, S., & Pennington, G. (2012). A closed form memristor SPICE model and oscillator. In IEEE 55th international midwest symposium on circuits and systems (MWSCAS), Boise, ID (pp. 1192–1195).

Jameel, S., Koraslı, C., & Nacaroglu, A. (2013). Realization of biquadratic filter by using memristor. In International conference on technological advances in electrical, electronics and computer engineering, (TAEECE), Konya, Turkey (pp. 52–56).

Ascoli, A., Tetzlaf, R., Corinto, F., & Gilli, M. (2013). PSpice switch-based versatile memristor model. In IEEE international symposium on circuits and systems, (ISCAS), Beijing (pp. 205–208).

Berdan, R., Lim, C., Khiat, A., Papavassiliou, C., & Prodromakis, T. (2014). A memristor SPICE model accounting volatile characteristics of practical ReRAM. IEEE Electron Device Letters, 35(1), 135–137.

Biolek, D., Biolek, Z., & Biolkova, V. (2010). Pspice modeling of memcapacitor. Electronics Letters, 46(7), 520–522.

Biolek, D., Biolek, Z., & Biolkova, V. (2011). Pspice modeling of meminductor. Analog Integrated Circuits and Signal Processing, 66(1), 129–137.

Bo-Cheng, B., Jian-Ping, X., Gua-Hua, Z., Zheng-Hua, M., & Ling, Z. (2011). Chaotic memristive circuit: Equivalent circuit realization and dynamical analysis. Chinese Physics B, 20(12), 120502-1–120502-6.

Pershin, Y. V., & Di Ventra, M. (2010). Practical approach to programmable analog circuits with memristors. IEEE Transactions Circuits and Systems I: Regular Papers, 57(8), 1857–1864.

Biolek, D., Bajer, J., Biolkova, V., & Kolka, Z. (2011). Mutators for transforming nonlinear resistor into memristor. In 20th European conference on circuit theory and design (ECCTD) (pp. 488–491).

Valsa, J., Biolek, D., & Biolek, Z. (2011). An analogue model of the memristor. International Journal of Numerical Modelling, 24(4), 400–408.

Kim, H., Sah, M. P., Yang, C., Cho, S., & Chua, L. O. (2012). Memristor emulator for memristor circuit applications. IEEE Transactions Circuits and Systems I: Regular Papers, 59(10), 2422–2431.

Mutlu, R., & Karakulak, E. (2010). Emulator circuit of TiO2 memristor with linear dopant drift made using analog multiplier. In National conference on electrical, electronics and computer engineering (ELECO), Bursa, Turkey (pp. 380–384).

Abuelma’atti, M. T., & Khalifa, Z. J. (2014). A new memristor emulator and its application in digital modulation. Analog Integrated Circuits Signal Processing, 80, 577–584.

Abuelma’atti, M. T., & Khalifa, Z. J. (2015). A continuous-level memristor emulator and its application in a multivibrator circuit. International Journal of Electronics and Communications, 69, 771–775.

Yu, D. S., Chen, H., & Iu, H. C. (2013). Design of a practical memcapacitor emulator without grounded restriction. IEEE Transaction On Circuits and Systems- II, 60(4), 207–211.

López, S. C., López, J. M., Carrasco-Aguilar, M. A., & Montero, M. C. (2014). A floating analog memristor emulator circuit. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(5), 309–313.

Yu, D., Iu, H., Fitch, A. L., & Liang, Y. (2014). A floating memristor emulator based relaxation oscillator. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(10), 2888–2896.

Yu, D. S., Chen, H., & Iu, H. H. C. (2013). A meminductive circuit based on floating memristive emulator. In IEEE international symposium on circuits and systems (ISCAS), Beijing (pp. 1692–1695).

Elwakil, A. S., Fouda, M. E., & Radwan, A. G. (2013). A simple model of double-loop hysteresis behavior in memristive elements. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(8), 487–491.

Yesil, A., Babacan, Y., & Kacar, F. (2014). A new DDCC based memristor emulator circuit and its applications. Microelectronics Journal, 45(3), 282–287.

Sozen, H., & Cam, U. (2015). New memristor emulator circuit using OTAs and CCIIs. In International conference on electrical and electronics engineering, Bursa, Turkey.

Martinez, J. S., & Sinencio, E. S. (1986). Analogue OTA multiplier without input voltage swing restrictions, and temperature-compensated. Electronics Letters, 22(11), 599–600.

Data Sheet CA3080. www.intersil.com.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sözen, H., Çam, U. Electronically tunable memristor emulator circuit. Analog Integr Circ Sig Process 89, 655–663 (2016). https://doi.org/10.1007/s10470-016-0785-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0785-2