Abstract

The complexity of radiofrequency circuit design comes from the large number of parameters to be adjusted. Constant node shrink in CMOS process and variation of technology skills significantly contribute to this complexity. The paper reports on a reliable and portable design methodology based on a low-power figure of merit (FOM) and inversion coefficient applied to the design of a low noise amplifier (LNA). The design procedure considers the circuit specifications and the optimization of the FOM. As a case of study it is applied to 2.4 GHz LNA designed in a 28 nm technology then exploited to compare different CMOS technology nodes: 28, 65, 130 nm.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The market of connected mobile devices is booming with the development of Smartphone, tablets, watches, and the emergence of new needs such as wireless sensor networks (WSN) and bio-data networks (BAN). The tight time to market, and cost of development, impose companies to improve design procedures for new product generations. Among the most famous optimization algorithms exploited in the design of analog/RF circuits are: genetic algorithms [1] or neural networks [2]. However the complex description of the circuit parameters to set up the optimization procedure, the simulation time and the final circuit performances do not significantly improves the design procedure of wireless circuits and systems. New design methodologies are mandated to address the development of future RF circuits.

The small form factor of modern electronic devices imposes power saving and advanced energy management. For the RF functions the use of a figure of merit (FOM) which represents the trade-off between the performances and the power consumption, is a relevant approach to perform both power saving and/or the optimization of the circuit characteristics.

Finally, in advanced Silicon technologies, the increase of the cut-off frequency (fT) in CMOS contributes to the reduction of the power consumption of RF blocks, however the variation of technology characteristics from one node to another makes difficult the portability of circuits and design methodologies. In order to address this issue, a design approach is proposed based on the inversion coefficient (IC) [3]. The IC is a normalization of MOS drain current which allows a description of the transistor behavior independently of technological parameters.

The paper is organized as follows: Sect. 2 discusses a low-power FOM for biasing optimization based on an IC description. This approach is validated with measurement results. Section 3 proposes a design methodology which is exploited to compare different technological nodes. Section 4 describes the normalization of MOS transistor characteristics with the IC. Section 5 presents a complete design methodology applied to the implementation of a 2.4 GHz LNA based on a current reuse topology in a 28 nm CMOS process of STMicroelectronics.

2 FOM Polarization

2.1 Inversion Coefficient, IC

The IC description of MOS drain current is derived from the charge-based model [3]. Unlike surface-potential-based models, it provides a simple and continuous model of transistor in all operating regions. Furthermore, IC parameter allows a comprehensive analysis and optimization of circuits, according the biasing conditions.

The IC (1) [3, 4] is the measure of the channel inversion level when the transistor is in saturation. The transistor work in saturation when the voltage VDS is higher than the pinch-of voltage (or VDSsat) [3]. IC is a drain-current normalization over the technological parameter Ispec⋄, defined in (2), and the ratio between transistor width (W) and length (L):

In (2), C ox is the oxide capacitance per unit area, U T (=kT/q) is the thermal voltage, μ 0 is the low-field surface mobility; n is a slope factor (which moves from 1.4 for Weak Inversion to 1.6 for Strong Inversion, but it is fixed at 1.5). The different operating regions in saturation are: Weak Inversion (or subthreshold voltage; WI: IC <0.1), Moderate Inversion (close to the threshold voltage; MI: 0.1 < IC < 10) and Strong Inversion (higher than threshold voltage; SI: IC >10).

2.2 FOM optimization

Since the 1970s, low power analog designs have been optimized by maximizing the metric «gm/ID» [5], namely current efficiency, which is maximum in weak inversion region—i.e. IC <0.1—in Fig. 1. For RF applications, the transistors are usually biased in SI region—i.e. IC >10—where the fT is high (Fig. 1). Unfortunately the current efficiency is low in the SI region which is not relevant for power saving. Since the 2000s, new metrics such as «gm2/ID» [6] and «gm fT/ID» [7] have been introduced for the design of low power RF. The (gm fT/ID), Fig. 1, is maximum in MI region which represents a good trade-off between current efficiency and speed. Interestingly the technology scaling improves the fT which becomes now considerably higher than the operating frequency of RF applications: fT >350 GHz in 28 nm CMOS. The design of RF circuits in MI region becomes more and more attractive as the circuits performances benefit from technology scaling, and the FOM are optimized.

In LNA design, the two most important characteristics are the voltage gain (Av) and the noise factor (F) which define the receiver sensitivity. The linearity (IIP3) is also considered but the optimization of the IIP3 is critical in base-band signal. Indeed the level of non-linearity and inter-modulation is magnified by the gain of the receiver chain, and base-band circuits have to process signals with large distortions. Hence the linearity of a LNA has to meet the standard specification, and does not need to be optimized. For this reason we will further use the FOM defined in (3) [6] which considers: the minimum noise factor (Fmin), the unmatched voltage gain (Avabs) and the power consumption (ID Vdd) at the operating frequency (freqGHZ).

A basic NMOS common source configuration with capacitive load, Fig. 2, is simulated in a 28 nm CMOS technology for a fixed VDD. The simulation results are reported in Fig. 3 versus the IC. We can observe Av and Fmin are respectively maximum and minimum in MI region [6]. The degradation of these performances in strong inversion is due to the carriers’ velocity saturation.

For the circuit of Fig. 2, the FOM defined in (3) and the (gm fT/ID) of the transistor are reported in Fig. 4. The two metrics exhibit a close-form evolution, and reach a maximum in the MI region. The IC value for FOMmax, 2, is close to the value for (gm fT/ID)max, 3.5. Unlike the (gm fT/ID) the FOM actually represents the performances of the circuit which makes it a relevant metric for the design of low power LNA.

2.3 FOM measurement

Two low power RF LNA, implemented in a 130 nm CMOS technology and dedicated to the 2.4 GHz ISM band are measured. These circuits were designed and optimized with the (gm fT/ID) approach.

The first LNA, Fig. 5, is a cascode topology with an inductive degeneration and a body bias tuning. The control of the substrate voltage (VBS) is intended for performance optimizations in various regions of inversion. The circuit takes place in a 2 mm2 silicon area.

The second circuit is based on a current-reuse configuration, Fig. 6. A capacitive divider combined with the series inductor LG performs the input matching. The circuit only needs one inductor (LG), Lpk belongs to the buffer, which reduces the silicon footprint to 0.63 mm2.

The two circuits are measured at 2.4 GHz with a fixed VDD. The transistor inversion region is adjusted by changing the gate biasing (VGS). For the two circuits, the measured S21 and the noise figure NF are reported in Fig. 7. For the two circuit configurations, the gain and NF characteristics exhibit the same evolution, in good agreement with the simulation presented in Fig. 3. Furthermore the FOM figures out a maximum in the moderate inversion for an IC close to 1.5. These measurement results confirms the existence of an optimum polarization in the moderate inversion region for RF low power LNA. At this operating point, the measured performances for each LNA are reported in the Table 1. The inductively degenerated cascode have a gain of 8.8 dB and a noise figure of 3.3 dB for a power consumption of 400 µW. The current reused have a gain of 14.3 dB and a noise figure of 5 dB for a power consumption of 80 µW.

This section demonstrates an optimum biasing in the design of LNA according the FOM defined in (3). This optimum biasing occurs when the amplifying transistors operate in Moderate Inversion (MI) region. The values of the ICopt as well as the magnitude of the FOM depend on the technology node and the circuit topology. Unlike the metrics reported so far, such as the (gm fT/ID), the FOM embeds the performances of the LNA, which can be further exploited to adjust and optimize the circuit characteristics. We propose in the next sections a comprehensive description of a design methodology based on this FOM, and dedicated to the sizing of low power LNA.

3 Design methodology based on the FOM

3.1 “Active part” design flow

The MOS transistor model allows to use only to three design parameters: the biasing with the IC and the size with the width (W) and the length (L). With this parameters, it is possible to define the circuit performances (4): the voltage gain (A v ), the noise figure (F min ) and the current (I D ).

The FOM calculation at (3) allows us to find the optimal biasing and the circuit performances (Sect. 2.2). This approach allows to realize a design methodology for the “Active Part” to finds the size and optimal biasing for transistor(s), represented in the Fig. 8. Two steps are required to find the “Active Part”; based on A v and F min specifications, the first step we find the optimum IC (IC opt ) calculating FOM. In the second step, we estimate the performances at fixed gate width (W) and length (L). The loop runs over these two steps, incrementing W and L, until the LNA characteristics meet the specifications. For a complete design flow, the input matching is added in the Sect. 4.

3.2 Method relevance

The method relevance is demonstrated by simulation for a capacitive common source in CMOS 28 nm (Fig. 2). The required performances are: a capacitive load of 100 fF, a frequency of 2.4 GHz, the noise figure must be below 1 dB and the voltage gain is constant at 10 dB. For a fixed length (L) of 40 nm, in Fig. 9 current and FOM are shown for different widths (W). In the same figure, the operating point of the method FOMopt at ICopt is obtained, according with the required performances. The method allows to work nearest the minimum current with a difference below 1 %. However, FOMopt does not match with maximum FOM and the difference is 0.15 %: it is necessary to include weights in the FOM equation but we decide to keep a generic FOM formula. Our principal objective is not to find the circuit with the best FOM but to respect the performances and have the lowest power consumption. FOMopt method allows to find quickly the minimum current respecting the required performances.

For different gate lengths (Table 2) and constant gain, the method allows to obtain size and transistor biasing close to the minimum current configuration. Moreover, the inversion coefficient ICopt(FOMopt) obtained by the method is close to IC(FOMmax). However the method is not efficient in some cases: for the 30 nm gate length it has been observed a difference of 5 % between Idmin and Id(FOMopt) and 22 % between FOMmax and FOMopt. Anyway, the method can quickly size a circuit configuration close to the minimum current.

3.3 FOM evolution versus gate length

The minimum channel length is a parameter often used to increase the operating frequency and reduce the circuit consumption. However, reducing the gate length consequently decreases the maximum intrinsic gain. For advanced technologies and low power RF applications using the minimum length is not necessarily the best solution. For a capacitive load common source in CMOS 28 nm, the design method shown in Fig. 8 is applied to obtain: a voltage gain of 10 dB, a noise lower than 1 dB for the operating frequency of 2.4 GHz. The circuit is optimized for different gate lengths (L) and the simulation results are reported in Fig. 10. We observe that, for a constant gain, the minimum noise figure increases with the channel length. The FOM should decrease with the noise figure. However, it is observed that current decreases from gate length of 30–60 nm and then increases. This current variation induced a maximum FOM for a length of 40 nm.

We explain the current variation with the effect of velocity saturation and parasitic capacitances. The effect of the velocity saturation carrier generates a transconductance saturation in the strong inversion for advanced technologies. This phenomenon is represented by the coefficient λc [8], detailed in Sect. 4. We assume that there is a correlation between the a minimum current and the coefficient λc [8]. Evolution of λc compared to the Idopt(ICopt) method is shown in Fig. 11. Value of λc does not change linearly with the gate length (L), and its slope increases with gate length (L) decreasing. The relationship between λc and Idopt(ICopt) is not direct, but minimum current matches to the slope variation of λc. The increase of λc causes transconductance saturation, and consequently gain saturation. To keep a constant gain, it is necessary to increase the transconductance, so the current. From a gate length of 30–60 nm, current decreases according with the λc. For length higher than 60 nm, current increases because there are more parasitic capacitances: it is necessary to increase the current to keep a constant gain. It is necessary a trade-off between velocity saturation and parasitic capacitances to size gate length and minimize the current.

We compare different technologies to check if the minimum channel length is the best choice for advanced technologies in low power RF applications.

3.4 Technologies comparison

For circuits with same gain and similar noise figure, FOM maximization allows to decrease current consumption. The method is applied on different technologies and N-MOS transistors of STMicroelectronics: 28 nm-nfet, 28 nm-N Low Voltage Threshold (nlvt), 28 nm-N Super Low Voltage Threshold (nslvt), 65 nm-nlvt and 130 nm-nrfhsmos4.

The capacitive load common source topology is designed to obtain: a voltage gain of 10 dB with a noise figure lower than 1 dB at 2.4 GHz, for a load capacity of 100 fF. The method is applied for different gate lengths and the simulations results are shown in Figs. 12, 13 and 14.

In previous sections, we found that it exists an optimal gate length (L) to maximize the FOM. The same behavior is shown in Fig. 12 for the 28 and 65 nm technologies, but not for the 130 nm technology. For 28 and 65 nm technologies, the minimum length is not the best choice to design a low power RF LNA. For 28 nm CMOS, the optimal length is 40 nm and for the 65 nm CMOS is 75 nm. For 130 nm technology, the optimal length is the minimum length. The transistor transition frequency (fT) has a strong impact on this phenomenon: 90 GHz for 130 nm, 180 GHz for the 65 nm and 350 GHz for the 28 nm.

Figure 12 highlights several behaviors:

-

Technological progress allows to increase FOM, using the minimum gate length.

-

FOM slopes depends on technologies: in 65 and 130 nm technologies slopes decrease similarly while in 28 nm slope decreases faster.

-

In 28 nm CMOS, “lvt” and “slvt” have a FOM twice higher than the “fet”. Threshold voltage reduction is clearly favorable to the FOM.

The IDopt evolution for different gate lengths is shown in Fig. 13. Some behaviors can be observed:

-

A minimum current is highlighted according to gate length particularly on 28 nm CMOS.

-

Transistor length for the minimum current does not match to the maximum FOM. For the 28 nm-nlvt, the maximum FOM is for L = 40 nm while the minimum current is for L = 55 nm.

-

In Fig. 12, the FOM of 65 nm-nlvt is higher than 28 nm-nlvt for L = 75 nm. Figure 13 shows that the current of 65 nm-nlvt becomes lower than 28 nm-nlvt for L ≥ 100 nm.

Figure 14 shows IC for different gate lengths at the FOMopt. The three technologies are biased in moderate inversion (0.1 < IC < 10). Technological progress allows to reduce the optimal IC. The circuit in 130 nm CMOS works at the limit of strong inversion and circuits in 28 nm CMOS are closed to weak inversion.

In order to develop the method analytically, we normalize transistor as described in the next section.

4 Transistor normalization

The literature proposes different models of MOS transistor [9–11] whose complexity usually increases with the operating frequency. For applications below 10 GHz, a RC model provides enough accuracy. A small-signal model, including noise sources, is proposed in Fig. 15. The model is composed by transconductance (gm) and conductance (gds) for the active part, and by capacitances and a resistance for the passive part.

4.1 Transconductance & conductance

The transistor transconductance gm is defined in (5) [8] and it depends on the IC with Gm(IC, λc), transistor size (W, L) and the technologic parameter Ispec⋄. In deep-submicron technology (L < 200 nm), velocity-saturation increases the transconductance saturation and is represented by the coefficient λc, which depends on the technology and gate length (L). For a long channel, the coefficient λc is null.

The transistor’s output conductance gds (6) depends on the drain current and the early voltage VM [3]. It is simplified and represented by the IC, the size (W, L), Ispec⋄ and an empirical technological parameter αGds.

The analytic expressions of gm (5) and gds (6) are compared with electrical simulations for 28 nm CMOS technology of STMicroelectronics in Fig. 16 for a capacitive common source (W = 6 µm and L = 30 nm). The model of gm (5), accounting for velocity saturation λc, is validated in all operating regions. The conductance model (6), not including λc, fits the simulation results in weak and moderate inversion regions. The analytic gds overestimates the simulated gds in the SI region (IC >10). However, the effect of this is minor on the design methodology and circuit optimization, as shown in Sect. 2.

According (5) and (6), only 3 parameters are required to described gm and gds: Ispec⋄, λc and αGds. Our design methodology is persistently based on these characteristics. These parameters can be extracted throughout two DC simulations of each transistor type.

The first simulation provides a plot of (ID − VGS) to find gm for Ispec⋄ and λc extraction. According Fig. 17, the representation of the gm to drain current ratio, namely current efficiency, over the drain current, ID, exhibits two trends: a constant in WI region and a negative slope in SI region. The intersection of the representative asymptotes of WI and SI regions occurs when ID equals Ispec for long channel and depends of λc for short channel. Ispec⋄ will be further deduced with (2) and λc with Fig. 17. The parameters λc depends to gate length (L).

The second simulation is the characteristics (ID − VDS) to find gds; αGds is deduced from (6) for a fixed size and current.

The gm and gds parameters are solely dependent on the size (W, L) and the IC for a given technology (Ispec⋄,λc, αGds).

4.2 Parasitic transistor capacitances and resistances

The parasitic capacitances and resistances depend on technological parameters Cw and R⋄, respectively, and are normalized to the transistor size W and L according to (7) and (8).

To extract the capacitances and resistances, a S-parameter simulation is used on a single transistor at fixed size (W, L) in order to work out the admittances Yij [1] (Eq. 9).

For noise analysis, the gate resistance noise \( \overline{{v_{ng}^{2} }} \) and the channel noise \( \overline{{i_{nd}^{2} }} \) (10) are considered accordingly [3].

In next section we combine the transistor normalization and the bias with the FOM method to define an analytical design methodology.

5 LNA design methodology base on the FOM opt and transistor normalization

5.1 Complete design flow

In previous section, we have shown that only three design parameters, IC, W and L, are needed to represent MOS transistor. Consequently with the same parameters, it is possible to define the LNA performance (11): voltage gain (A v ), noise figure (F min ), current (I D ) and input impedance (Z IN ).

The FOM calculation at (3) allows to find the optimal biasing and the LNA performances (Sect. 2). With this approach we can realize a complete design methodology including the input matching represented in Fig. 18. This methodology has two parts; the “Active Part” finds the size and optimal biasing for transistor(s) and the “Passive Part” finds the input matching.

The “Active Part”, explained in Sect. 3.1, is based on A v and F min specifications. In the first step FOM calculation provides the optimum IC (IC opt ). In the second step, we check the performances (A v , F min ) for ICopt and fixed gate width (W) and length (L). The loop runs over these two steps, incrementing W and L, until the LNA characteristics respect the specifications. In the most of the case, use a smaller length (L) allows to reduce the current consumption. Consequently, the width (W) is increment the first than a minimum size to a maximum size define by the layout size. Then, the length (L) is incremented for a small size, the width (W) redo a loop in the range of the minimum to the maximum size.

For a complete design flow, the input matching is also designed with the “input passives”. In the “Passive Part”, the input matching is designed with the parameters previously obtained in the “Active part”: IC opt , W opt , L opt ,. If the LNA performances do not respect the targeted specifications, the initial specifications are adjusted.

In next paragraph the circuit performances (A v , F min , I D , Z IN ) are described in terms of circuit components: g m , g ds , C gs , C gd , C bd , R G , “input passives” in order to make an analytical methodology.

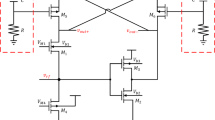

5.2 Application on a current reused circuit

The current reused circuit that we implemented in 28 nm CMOS is shown in Fig. 19. The LNA core is composed of two transistors, one NMOS (M1) and PMOS (M2) using the same bias current. The transistor M1 is biased with the voltage Vgs_LNA. The transistor M2 is self-biased by the feedback resistance RF and the current of M1. The input matching is achieved with a capacitive divider setting the real part at 50 ohms. It is composed by: the parasitic capacitances and the transconductances of the LNA transistors (M1 and M2), the load capacitance (input capacitance of transistor M3) and a tunable capacitance Cin. The imaginary part is set to zero by the series inductance LG. The output matching is achieved with a resistive common source (M3). Polarizations are separated to control each stage independently.

In Fig. 20, the analytical description of the circuit is made from the small signal schema. Current reused topology model can be represented as two capacitive common sources in parallel: NMOS and PMOS. The transistors M1 and M2 are grouped (12) through equivalent components, denoted eq.

The LNA core voltage gain (Av), without input matching, is described in Eq. (13). To simplify Av equation we distinguish the output impedance Zout and the feedback impedance Zeq_fb in Eqs. (14) and (15). The gate resistance (RG) impact is negligible.

The extraction of the 28 nm CMOS technologic parameters allows to compare in Fig. 21, the analytical gain Eq. (14) and gain simulation. The analytical gain behavior fits perfectly to the simulation up to IC = 1. Then, simulated gain decreases rapidly. We have observed in Fig. 15, that conductance (gds) analytical model diverges for IC>1.

The circuit noise, generated by gate resistors, the inductance (LG) and the channel conduction require noise matching. The minimum noise figure (Fmin) of the circuit is shown in Eq. (16). The influence of the feedback resistor (RF) can be skipped if its value is important. The input matching network introduces a Q-factor (Qπ) or passive gain. The minimum noise factor is often calculated with only the transconductance. However the use of voltage gain allows to take into account the complete transfer function. Analytical minimum noise figure is compared to the simulation in Fig. 22. We observe that analytical noise equation and simulation are the same behavior differing by 0.4 dB for 0.01 > IC > 1. The noise factor diverges due to gds.

We compare the analytical and simulation of FOM in Fig. 23. The shapes of the curves are close. The maximum analytical and simulated FOM appears in moderate inversion, for an IC = 1.2 and an IC = 1.5 respectively. These curves show that the circuit design by analytical method is relevant and reliable.

The circuit input matching (Zin) is represented in Eq. (17).

The LNA is designed to operate at 2.4 GHz for 0.5 V supply; it is expected to achieve more than 15 dB gain and a NF lower than 1 dB. The design flow allows to get a current of 30 µA and to size the components as shown in Fig. 19. The inversion coefficients (ICopt) at FOMopt are 0.5 (MI) for the NMOS (M1) and 0.02 (WI) for the PMOS (M2). The biasing in MI for the two transistors should be applied; however a trade-off between the parasitic capacitance and carrier mobility put the PMOS transistor in WI which decreases the global current consumption.

LNA is implemented in 28 nm STMicroelectronics CMOS technology and cover a surface of 0.39 mm2, including the PADs without inductance (Fig. 24). Simulations are realized with a supply voltage of 0.5 V and a current of 30 µA (15 µW), excluding the 50 Ω buffer (Fig. 25; Table 3). The gain represented by S21 reaches a maximum of 17 dB at 2.4 GHz; therefore the current-reused topology provides a large voltage gain with a low voltage supply. The fine tuning of input matching gives an S11 of −19 dB at 2.4 GHz. The output matching has no resonance which allows a broadband use with a S22 under −20 dB. The noise reaches a value of 0.25 dB at 2.4 GHz. The very low current degrades the linearity: ICP1 is −23 dBm and IIP3 is −18 dBm.

6 Conclusion

A new approach of design methodology for RF low power LNA is presented in this paper. The method efficiency comes from the association of circuit’s performances (Av, Fmin, ID) in low power FOM calculation and the optimum polarization. The local optimum bias in moderate inversion is confirmed with the measurements of two RF LNAs in CMOS 130 nm. This approach allows to size the core of the LNA and secondly to set the matching. This method is used to compare different technologies: we observe that for advanced technologies, such as 65 nm CMOS or 28 nm CMOS, the use of the minimum gate length is not the best choice to reduce current consumption. Using analytical representations of the circuits from the transistor normalization and the IC, it is possible to size the components automatically. This automation is a major asset to quickly design a circuit, modifying the performances or the CMOS technology. Finally, this design methodology is used to design a 2.4 GHz LNA in 28 nm CMOS technology of STMicroelectronics.

References

Dumesnil, E., Nabki, F., and Boukadoum, M. (2014). « RF-LNA circuit synthesis by genetic algorithm-specified artificial neural network. In 2014 21st IEEE international conference on electronics, circuits and systems (ICECS) (pp. 758–761).

Rahnama, M., Gilmalek, Y. M., and Kordalivand, A. M. (2010). Ultra wide-band LNA using RFCMOS technology and tunability band with neural network. In 2010 IEEE control and system graduate research colloquium (ICSGRC) (pp. 75–79).

Enz, C. C., & Vittoz, E. A. (2006). Charge-based MOS transistor modeling. Chichester: Wiley.

Tsividis, Y. (1999). Operation and modeling of the MOS transistor (2nd ed.). New York: Mc-Graw Hill.

Vittoz, E. A., & Fellrath, J. (1977). CMOS analog integrated circuits based on weak inversion operation. IEEE Journal of Solid-State Circuits, 12(3), 224–231.

Song, I., & Park, B.-G. (2008). A simple figure of merit of RF MOSFET for low-noise amplifier design. IEEE Electron Device Letters, 29(12), 1380–1382.

Shameli, A., Heydari, P. (2004). Ultra-low power RFIC design using moderately inverted MOSFETs: An analytical/experimental study, RFCI.

Mangla, A., Chalkiadaki, M.-A., Fadhuile, F., Taris, T., Deval, Y., & Enz, C. C. (2013). Design methodology for ultra low-power analog circuits using next generation BSIM6 MOSFET compact model. Microelectronics Journal, 44(7), 570–575.

Deen, M. J., Chen, C.-H., Asgaran, S., Rezvani, G., Tao, J., & Kiyota, Y. (2006). High-frequency noise of modern MOSFETs: Compact modeling and measurement issues. IEEE Transactions on Electron Devices, 53(9), 2062–2081.

Ng, T. C., Swe, T. N., Yeo, K.-S., Chew, K. W., Ma, J.-G., & Do, M. (2001). Small signal model and efficient parameter extraction technique for deep submicron MOSFETs for RF applications. IEEE Proceedings of Circuits Devices Systems, 148(1), 35–39.

Enz, C. C., & Cheng, Y. (2000). MOS transistor modeling for RF IC design. IEEE Journal of Solid-State Circuits, 35(2), 186–201.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Fadhuile, F., Taris, T., Deval, Y. et al. Design methodology for low power RF LNA based on the figure of merit and the inversion coefficient. Analog Integr Circ Sig Process 87, 275–287 (2016). https://doi.org/10.1007/s10470-016-0718-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0718-0