Abstract

Quantum-dot cellular automata (QCA) as a technology in the nanoscale is used for designing the future circuits. It has high density, speed, and low power dissipation. Besides, arithmetic and logic unit (ALU) is one of the main bases to define the system performance. Its plan depends on combinational circuits that decrease complexity and it has reasonable simulation times. Cell misalignment, cell displacement, cell omission (missing cell), and the extra (additional) cell are considered as the weaknesses of these circuits. Designing Fault tolerance of ALU in QCA is very important but there is no survey about the details. A three-level fault-tolerant ALU based on QCA is discussed in this paper, which performs “AND”, “OR”, “XOR” and “Full adder”. Also, the used rotated majority gate in the proposed ALU is fault tolerance. This structure tolerances a single stuck-at 0 and 1 and related faults are covered using test patterns {11100, 11101, 11010, 11001}. Furthermore, the presented ALU, under omission errors of cells in layers 2 and 3 is tolerated using the test patterns. The presented method has high fault tolerance compared to the similar methods according to the simulation results using QCAdesigner. It also has 0.78 µm2 of circuit area and the outputs are delivered after three clock cycles. Also, it has lower area consumption and delay compared to other schemes.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Quantum-dot cellular automata (QCA) as a new Nano-based technology presents a novel model rather than traditional complementary metal–oxide–semiconductor (CMOS) technology (Angizi et al. 2015; Afrooz and Navimipour 2017; Barughi and Heikalabad 2017; Mohammadi and Mohammadi 2014; Sen et al. 2017). At Nanoscale, it introduces another method for calculation and data change (Tougaw et al. 2016; Farazkish and Khodaparast 2015; Khan et al. 2016; Rashidi et al. 2016; Sa-nguansin 2014). The QCA performs with the coulombic interaction among adjoining cells (Gladshtein 2013; Karkaj and Heikalabad 2017; Sasamal et al. 2016). The QCA offers small size and low power utilization to realize binary operations using the single electrons in different types of quantum dots (Mukhopadhyay and Dutta 2015; Khosroshahy et al. 2017; Karkaj and Heikalabad 2017; Choi and Choi 2008; Karim et al. 2009). Furthermore, this structure has high dense and provides fast responses depending on the interaction repulsion of electrons (Hashemi and Navi 2012; Farazkish 2014; Khordad 2016).

On the other hand, arithmetic and logic unit (ALU) is the main part of the processor to perform the arithmetic and logical operations (Sen et al. 2012, 2014; Kretzschmar et al. 2016). The ALU is an energy efficient and fast circuit in view of processing force. It plans to decrease complexity depends on combinational circuits (Gupta et al. 2013). The ALU can be realized utilizing the QCA technology. However, cell misalignment, cell displacement, cell omission (missing cell), and extra (additional) cell are considered as four weaknesses of this circuit. Therefore, fault tolerance and presence of error are very important in this circuit. So, designing fault tolerance QCA-based ALU is very challenging.

The main advantages of QCA are low power consumption and zero power dissipation in signal emission as well as high speed and density. In the multilayer design, the QCA offers more tolerance and reduced area. Also, the ALU is one of the important elements that determine the function of the system. Therefore, optimization of speed, area, delay, and error tolerance of QCA-based ALU is an important issue. Since there are some disadvantages in the previous QCA-based designs such as low fault tolerance ability, the design and evaluation of three-level fault tolerance ALU based on QCA are described in this paper. The proposed design uses the fault tolerant rotated majority gate. This ALU design includes “AND”, “OR”, “XOR” and “ADD”. This structure can tolerate a single stuck-at faults using test patterns {111000, 11101, 11010, 11001}. Briefly, the contributions of this paper are as follows:

-

Designing an optimized three-level fault tolerance ALU based on QCA.

-

Assessment of the faults in the proposed ALU using the test patterns {11100, 11101, 11010, 11001}.

-

Providing a comparison among the proposed method and other methods in terms of fault tolerance, area, and delay.

The rest of the paper is organized as follows: Sect. 2 gives a brief description of the related work on ALU designing methods using the QCA technology. Section 3 describes the proposed designs in three levels. Section 4 presents and analyzes the obtained results. Finally, the concluding remark and future work are presented in Sect. 5.

2 Related work

Waje and Dakhole (2013) have proposed a four-bit ALU using QCA technology. The proposed design has four operations, including AND, OR, XOR and ADD. ADD operation is composed of three-level and XOR, AND, OR logics are designed in one-level. Also, 4:1 multiplexer incorporates three 2:1 multiplexers. A one-bit ALU also works based on the two control signals. The proposed four-bit ALU is simulated using QCAdesigner. The design of the proposed four-bit QCA-based ALU has fewer components contrasted with CMOS plan. Also, it is quicker and has better outcomes in terms of area and power consumption. But, the fault tolerating is not considered in this design.

Also, Ghosh et al. (2013) have proposed a basic 12 ALU utilizing QCA technology. The design performs the A + B, A − B, A OR B, A AND B, B, B + 1 and Reset operations. The A + B and A − B are executed utilizing the adder unit as a part of the ALU. The second layer of QCA is utilized to exchange input signals to the points located inside the muddled circuits. QCADesigner is utilized to simulate the proposed circuit. The obtained results indicate that this design minimizes the number of gates, cells, and area consumption. However, the acquired signal on the simulator is somewhat weaker to be utilized as input to the next circuit. The latency is expanded using different clock zones for long wires latency. Also, the fault tolerating is not considered in this design.

Furthermore, Teja et al. (2008) have designed an arithmetic and logical function generator (ALFG) using QCA technology. The utilization of computing paradigm based on QCA is additionally presented to describe the design and layout of ALFG. The design of the generator is made for employing the essential components of technology such as an inverter and majority voter. The simulation results are introduced utilizing QCADesigner. A combined 16 arithmetic and logical operations can be performed on a combine of four-bit vectors. The presented configuration offers some new operations compared to an ordinary ALU, for example, Shift, Parity, XOR, Rotate and Multiplication alongside essential operations. The complexity of the design is decreased according to the obtained results. But, the fault tolerating is not considered in this design.

Moreover, Sen et al. (2014) have designed a reversible ALU utilizing QCA technology. Low power consuming circuits is suggested through the reversible circuit by canceling the energy dissipation during the computation. It comprises of two separate modules such as reversible logic and reversible arithmetic unit. The design is based on the reversible multiplexer in which compact 2:1 QCA multiplexers unify the RM introduced in this paper. The proposed reversible multiplexer can accomplish fault tolerance within the sight of single missing or additional cell defects in QCA design. The reversible arithmetic and the reversible logic unit are combined in light of reversible multiplexer without fault tolerance capacity in QCA technology as the limitation of this method.

Finally, Sen et al. (2012) have proposed a QCA-based 2:1 multiplexer design for reversible ALU. The reversible structure of 2:1 multiplexer is used to integrate the required reversible arithmetic and logic unit (RALU). The circuit comprises of 19 cells, which are considerably lower than some existing designs based on the results of using the QCAdesigner. The proposed ALU has high density and the energy effectiveness. However, the fault tolerating is not considered in this design.

Goswami et al. (2017) have designed one bit ALU based on QCA by a testable (t) adder. T-adder gate includes A, B, C inputs and P, Q, R outputs. The design of one bit ALU by t-adder includes two original outputs F1, F2 and inputs A, C1, 0, B, C2, C and eight garbage outputs (G1…G8) and four t-adder gates. This design has simple structure and 2.34 μm2 area and two clocks delay. But, this design suffers from high area consumption. The side-by-side comparison of the evaluated techniques is shown in Table 1.

3 Proposed method

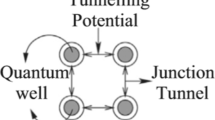

The design of a new fault tolerance one-bit ALU for AND, OR, XOR and ADD operations utilizing QCA is proposed through this section. The design of one-bit QCA-based ALU is straightforward in this structure and it has fewer components in comparison with CMOS plan. Majority gate has an important role in this design. The rotated majority gate (RMG) has higher fault tolerance capability in comparison with the original majority gate (OMG), which is shown in Roohi et al. (2015) and Tahoori et al. (2004). The OMG and the RMG are depicted in Figs. 1 and 2, respectively. Also, the inverter gate is shown in Fig. 3, a 45-degree wire is used to convey the opposed polarization. This design utilizes an exceedingly improved vigorous and fault tolerance full adder in the ALU utilizing QCA technology and uses an RMG gate instead of OMG gate for better fault tolerance and also uses an improved XOR gate in terms of a number of cells, area. The logic functions of the full adder can be expressed as follows:

The structure of the proposed Full Adder in (Roohi et al. 2015) is based on RMG and modified RMG. A control cell (ctrl) is located in the upper layer of the device cell where a modified RMG is developed. Figure 4 shows the function of ABC + D′(A + B + C) when the ctrl cell (drive cell) in the modified RMG operates as an input cell (D). This capacity can be used to execute a productive one-bit full adder by allocating the input cell (D) to Cout.

Proof The Boolean function of the sum for modified RMG and carry out for RMG bits for a one-bit full adder is given by Roohi et al. (2015):

In designing a one-bit full adder in ALU, three clock phases are necessary to get a stable output, as shown in Fig. 5. All cells with the exception of Cout have an inverting impact on polarizations of the device cells. Therefore, Cout has an inverting effect on the output. There is no need of wire crossover in order to feed into the other designs due to the output locations that are not surrounded by other cells. So, using multilayer structure could reduce the required area and complexity (number of QCA cells), and thus reduce fault exposure. Gate level schematic of the proposed full adder in Roohi et al. (2015) is shown in Fig. 6 which is used for stuck-at 0 and 1 faults in the proposed ALU.

Gate level schematic of the proposed full adder (Roohi et al. 2015)

3.1 Design of fault tolerance one-bit ALU using QCA

The proposed design employs the RMG for designing one-bit ALU using QCA instead of OMG for increasing the fault tolerance capabilities (Tahoori et al. 2004; Momenzadeh et al. 2004). Displacement and misalignment faults are identified with the RMG chronicled in Table 2. The comparison results of the OMG and the RMG are also illustrated in Table 3. RMG is completely robust with respect to the rotation of all input and output cells around the central cell. This gives a noteworthy level of freedom for integrating designs in light of QCA technology. Therefore, an RMG can be utilized as the original majority gate block. However, the original block is more dependent on the middle input (B) than the other inputs (A and C) in terms of displacement and misalignment. In the rotated version, this dependence can be totally changed in light of the level of revolution. The comparison in the table shows that RMG is more fault-tolerant than the OMG. The proposed full adder shows the improvements in terms of cell count (complexity) and the area in comparison to previous one-bit full adders in the ALU designs. Further, this paper presents the functionality and the defect tolerance of the proposed full adder in the ALU in the presence of QCA deposition faults (Roohi et al. 2015). Also, the proposed XOR has low area and number of cells in comparison to Waje and Dakhole (2013), Niemier (2008) and Angizi et al. (2014). This article performs “AND”, “OR”, “XOR”, “ADD” operations in ALU using RMG gate in Roohi et al. (2015).

The circuit functionality of a one-bit ALU depending upon the control signal S1 and S0 is shown in Table 4. The ALU has three layers, including layer1, layer2, and layer3.

Output equation F of one-bit ALU using QCA logic is

F = Maj(Maj(Z1,S1′,0),Maj(Z2,S1,0),1),

Z1 = Maj(Maj(D0,S0′,0),Maj(D1,S0,0),1),

Z2 = Maj(Maj(D2,S0′,0),Maj(D3,S0,0),1),

D0 = Maj(A,B,0),

D1 = Maj(A,B,1),

D2 = Maj(Maj(A,B′,0),Maj(A′,B,0),1),

D3 = Sum = ABC + Cout′(A + B + C).

Cout is carry output of full adder.

4 Result and analysis

The simulation tool is presented in the first section, the second section presents the simulation parameter and the last section presents the simulation result of the proposed design.

4.1 Simulation tool

Choosing the simulation tool is the first step in analyzing the proposed design. In this paper, all the designs are verified using QCADesigner version 2.0.3. A quick and precise simulation and design layout tool are used by QCA logic and circuit planners to decide the usefulness of QCA circuits. QCADesigner gives the capacity to layout a QCA configuration by giving a broad arrangement of CAD devices. QCADesigner is equipped for simulating complex QCA circuits on most standard stages (Walus et al. 2004).

4.2 Simulation parameter

The following parameters are used for simulation: cell size = 18 nm, convergence tolerance = 0.001, radius of effect = 80 nm, relative permittivity = 12.9, clock high = 9.8 × e22, clock low = 3.8 × e23, clock amplitude factor = 2.000, temperature = 1 K, layer separation = 11.5 nm. The utilized coherence vector engine for simulations appears in Table 5.

4.3 Simulation

Fault tolerance AND unit are shown in Fig. 7, which has two inputs A, B, and an output D0 = AB. Also, the fault tolerance OR is depicted in Fig. 8, which has two inputs A, B, and an output D1 = A+B. Fault tolerance XOR unit is shown in Fig. 9, which has two inputs A, B, and an output D2 = XOR = \({\text{A}}\bar{B}\) + \(\bar{A}B.\) The simulation of the fault tolerance full adder circuit (Roohi et al. 2015) is appeared in Fig. 10, which has three data sources A, B, Cin and output D3 = sum = ABC + Cout′(A + B + C), Cout and three layers are appeared. The simulation of MUX 2:1 is depicted in Fig. 11 that it has three inputs A, B, S and output Y = \({\text{A}}\bar{S}\) + SB. Also, in structure of ALU unit, three mux 2:1 are used with outputs Z1 = D0\(\cdot \bar{S}0\) + D1·S0, Z2 = D2\(\cdot \bar{S}0\) + D3·S0, F = Z1\(\cdot \bar{S}1\) + Z2·S1.

The simulation of the full adder (layer 1) (a), (layer 2) (b), (layer 3) (c) (Roohi et al. 2015)

Simulation of fault tolerance ALU (first layer) is depicted in Fig. 12, which has two inputs A, B and the outputs F = Z1\(\cdot \bar{S}1\) +Z2·S1, Cout and AND, OR, XOR, ADD gates and three mux 2:1 and control signals S1, S0. Table 4 showed the functionality of a one-bit ALU. The surface of the second layer is appeared in Fig. 13 and the third layer is appeared in Fig. 13.

4.4 Results

The simulation result for AND is shown in Fig. 14 that output AB shows the result of AND. The simulation result for OR is shown in Fig. 15 that output A + B shows the OR result. The simulation result for XOR is shown in Fig. 16 that output XOR = A\(\bar{B}\) + \(\bar{A}B\) shows XOR result. Also, the simulation result for MUX 2:1 is shown in Fig. 17 that output Y = A·\(\bar{S}\) + B·S shows the result of MUX 2:1. Furthermore, the simulation result for the fault tolerance of three level ALU when inputs A = 1, B = 1, Cin = 0 is shown in Fig. 18. The results show that the D0 output for AND is one, D1 output for OR is equal to one, D2 output for XOR is equal to zero, D3 = sum output for the full adder is zero, Cout is one. According to S0 and S1 control signals, there are four modes that are mentioned previously in Table 4. The ALU output will be equal with the XOR output for S0 = 0 and S1 = 1, in that case, F output is equal to zero.

4.5 Testing the fault tolerance capabilities

Defects in QCA designs may occur during the individual cell production as well as the movement of cells to a surface. Cell misalignment, cell displacement, cell omission (missing cell), and extra (additional) cell are considered as the types of defects. In cell misalignment sort, the defected cell is not appropriately adjusted to its neighboring cells. In other words, the defected cell gets closer to one or a few cells and far from the others. Cell displacement occurs when a cell is not placed in its original direction. So, the separation between the defected cells and all other cells decreases or increases. Cell omission happens when a cell is missing in evaluation with the basic fault-free device. Finally, when an extra cell is incorrectly saved on the substrate, this imperfection happens (Roohi et al. 2015).

In this section, the proposed ALU is tested against the faults especially cell omission fault. In order to achieve the better design, each cell in 2 and 3 layers is tested in order to maximize the degree of tolerance. At the logic level, test sequences that are similar to those are used in conventional CMOS to detect single stuck-at (SA) faults (SSF). Here, stuck-at faults for ALU is analyzed in Table 6 and the related defect coverage test vector {11100, 11101, 11010, 11001} is obtained by Table 6 and all stuck-at1and stuck-at0 faults are detected. Also, the faulty behavior of proposed ALU, under single missing cell defect in both layer2 and layer3 are tested and shown in Table 7. In this table, the expression (x, y) represents the location of a square cell situated x horizontally and y vertically. For instance, for the missing cell in position (50,5) (like (55, 5)), the F and Cout are dominated by A. The faulty behavior of the outputs is stuck-at A and can be detected by the following test vectors S1S0ABC = {11100/11100}. For missing cell (52, 3) and (57, 3), the fault is detectable by any of the test vectors. As mentioned before, cells (56, 4), (58, 4) and (56, 2) can be removed. After studying this defect in layers 2 and 3, it is discovered that the test vectors} 11100, 11101, 11010, 11001} provide 100% coverage of SSF.

4.6 Comparisons

The performances of these designs for the area and the delay and fault tolerance optimization results are shown in Table 8. According to the experimental results, the proposed ALU unit offers more fault tolerance in comparison with the ALU units in Sen et al. (2012, 2014), Waje and Dakhole (2013), Ghosh et al. (2013), Goswami et al. (2017) and Teja et al. (2008). The proposed structure provides 100% coverage of SSF by proposed test vectors and it has lower area and delay ratio to others. Table 9 compares the proposed Full Adder (Roohi et al. 2015) with three Full Adder designs (Waje and Dakhole 2013; Cho and Swartzlander 2009; Navi et al. 2010). Also, Table 10 shows the comparison of the proposed XOR with (Waje and Dakhole 2013; Niemier 2008; Angizi et al. 2014).

5 Conclusion and future research

Fault tolerance is an important issue in the QCA technology. In this paper, a three-level fault-tolerant ALU based on QCA is designed to perform “AND”, “OR”, “XOR” and “ADD”. This structure tolerances a single stuck-at 0 and 1 and related faults are covered using test patterns {11100, 11101, 11010, 11001}. Furthermore, the presented ALU, under omission errors of cells in layers 2 and 3 is tolerated using the test patterns. The presented method has high fault tolerance in comparison with the similar methods according to the simulation results of QCAdesigner. It also has 0.78 µm2 of circuit area and the outputs are delivered after three clock cycles. Also, it has lower area consumption and delay. Finally, the comparison of fault tolerance, area, and delay with other methods for one-bit ALU based on QCA is done in this paper.

Designing the four-bit fault tolerance ALU utilizing QCA technology will be quicker than area productive circuit, which is the central component of future Nano processors. Additionally, 16-bit ALU in light of QCA with some abilities like IC 74181 can be gotten utilizing this productive nanotechnology.

Change history

18 January 2018

Unfortunately, the Fig. 12 was incorrectly published in the original article. Hereby, the correct figure is given below:

References

Afrooz S, Navimipour NJ (2017) Memory designing using quantum dot cellular automata: systematic literature review, classification, and current trends. J Circuits Syst Comput. doi:10.1142/S0218126617300045

Angizi S, Alkaldy E, Bagherzadeh N, Navi K (2014) Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J Low Power Electron 10:259–271

Angizi S, Moaiyeri MH, Farrokhi S, Navi K, Bagherzadeh N (2015) Designing quantum-dot cellular automata counters with energy consumption analysis. Microprocess Microsyst 39:512–520

Barughi YZ, Heikalabad SR (2017) A three-layer full adder/subtractor structure in quantum-dot cellular automata. Int J Theor Phys. doi:10.1007/s10773-017-3453-0

Cho H, Swartzlander EE Jr (2009) Adder and multiplier design in quantum-dot cellular automata. IEEE Trans Comput 58:721–727

Choi M, Choi M (2008) “Scalability of globally asynchronous QCA (quantum-dot cellular automata) adder design. J Electron Test 24:313–320

Farazkish R (2014) A new quantum-dot cellular automata fault-tolerant five-input majority gate. J Nanopart Res 16:2259

Farazkish R, Khodaparast F (2015) Design and characterization of a new fault-tolerant full-adder for quantum-dot cellular automata. Microprocess Microsyst 39:426–433

Ghosh B, Kumar A, Salimath AK (2013) A simple arithmetic logic unit (12 ALU) design using quantum dot cellular automata. Adv Sci Focus 1:279–284

Gladshtein M (2013) Design and simulation of novel adder/subtractors on quantum-dot cellular automata: radical departure from Boolean logic circuits. Microelectron J 44:545–552

Goswami M, Sen B, Mukherjee R, Sikdar BK (2017) Design of testable adder in quantum-dot cellular automata with fault secure logic. Microelectron J 60:1–12

Gupta N, Choudhary K, Katiyal S (2013) Two bit arithmetic logic unit (ALU) in QCA. Int J Recent Trends Eng Technol 8:35

Hashemi S, Navi K (2012) New robust QCA D flip flop and memory structures. Microelectron J 43:929–940

Karim F, Ottavi M, Hashempour H, Vankamamidi V, Walus K, Ivanov A et al (2009) Modeling and evaluating errors due to random clock shifts in quantum-dot cellular automata circuits. J Electron Test 25:55–66

Karkaj ET, Heikalabad SR (2017a) “Binary to gray and gray to binary converter in quantum-dot cellular automata. Optik Int J Light Electron Optics 130:981–989

Karkaj ET, Heikalabad SR (2017b) “A testable parity conservative gate in quantum-dot cellular automata. Superlattices Microstruct 101:625–632

Khan A, Chakrabarty R, De D (2016) Static hazard elimination for a logical circuit using quantum dot cellular automata. Microsyst Technol 1–9

Khordad R (2016) Effect of impurity bound polaron on optical absorption in a GaAs modified Gaussian quantum dot. Optical Quantum Electron 48:251

Khosroshahy MB, Moaiyeri MH, Angizi S, Bagherzadeh N, Navi K (2017) “Quantum-dot cellular automata circuits with reduced external fixed inputs. Microprocess Microsyst 50:154–163

Kretzschmar U, Gomez-Cornejo J, Astarloa A, Bidarte U, Ser JD (2016) Synchronization of faulty processors in coarse-grained TMR protected partially reconfigurable FPGA designs. Reliab Eng Syst Saf 151:1–9

Mohammadi Z, Mohammadi M (2014) “Implementing a one-bit reversible full adder using quantum-dot cellular automata. Quantum Info Process 13:2127–2147

Momenzadeh M, Tahoori MB, Huang J, Lombard F(2004) Quantum cellular automata: new defects and faults for new devices. In: Parallel and distributed processing symposium, 2004. Proceedings. 18th International, p 207

Mukhopadhyay D, Dutta P (2015) A study on energy optimized 4 dot 2 electron two dimensional quantum dot cellular automata logical reversible flip-flops. Microelectron J 46:519–530

Navi K, Farazkish R, Sayedsalehi S, Azghadi MR (2010) A new quantum-dot cellular automata full-adder. Microelectron J 41:820–826

Niemier MT (2008) Designing digital systems in quantum cellular automata. University of Notre Dame, Notre Dame

Rashidi H, Rezai A, Soltany S (2016) High-performance multiplexer architecture for quantum-dot cellular automata. J Comput Electron 15:968–981

Roohi A, DeMara RF, Khoshavi N (2015) Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron J 46:531–542

Sa-nguansin S (2014) Bit corruption correlation and autocorrelation in a stochastic binary nano-bit system. J Korean Phys Soc 65:1001–1009

Sasamal TN, Singh AK, Mohan A (2016) “An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik Int J Light Electron Optics 127:8576–8591

Sen B, Dutta M, Singh DK, Saran D, Sikdar BK (2012) QCA multiplexer based design of reversible ALU. In: Circuits and Systems (ICCAS), 2012 IEEE International Conference on, 2012, pp 168–173

Sen B, Dutta M, Goswami M, Sikdar BK (2014) Modular Design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron J 45:1522–1532

Sen B, Mukherjee R, Mohit K, Sikdar BK (2017) Design of reliable universal QCA logic in the presence of cell deposition defect. Int J Electron 104:1285–1297

Tahoori MB, Momenzadeh M, Huang J, Lombardi F (2004) Defects and faults in quantum cellular automata at nano scale. In: VLSI Test Symposium, 2004. Proceedings. 22nd IEEE, pp 291–296

Teja VC, Polisetti S, Kasavajjala S (2008) QCA based multiplexing of 16 arithmetic & logical subsystems-A paradigm for nano computing. In: Nano/micro engineered and molecular systems, 2008. NEMS 2008. 3rd IEEE International Conference on, 2008, pp 758–763

Tougaw D, Szaday J, Will JD (2016) A signal distribution grid for quantum-dot cellular automata. J Comput Electron 15:446–454

Waje MG, Dakhole P(2013) Design and implementation of 4-bit arithmetic logic unit using quantum dot cellular automata. In: Advance Computing Conference (IACC), 2013 IEEE 3rd International, pp 1022–1029

Walus K, Dysart TJ, Jullien GA, Budiman RA (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3:26–31

Author information

Authors and Affiliations

Corresponding author

Additional information

A correction to this article is available online at https://doi.org/10.1007/s00542-018-3716-6.

Rights and permissions

About this article

Cite this article

Rahimpour Gadim, M., Jafari Navimipour, N. A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst Technol 24, 1295–1305 (2018). https://doi.org/10.1007/s00542-017-3502-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-017-3502-x