Abstract

We investigated vertical super-thin body (VSTB) FET performance in presence of different interface (HfO2/Si) trap distributions (uniform and Gaussian) and concentrations using TCAD tools. For trap concentration (TC) of 1013 eV−1 cm−2, the percentage change in on-to-off current ratio (Ion/Ioff) is 93.91% for uniform trap (UT) and 49.8% for Gaussian trap (GT) distribution. For the same TC, subthreshold swing (SS) shows percentage change of 5.1% for UT and 11.41% for GT distribution. Thus, the device performance shows good immunity for TC up to 1013 eV−1 cm−2. However, for TC = 1014 eV−1 cm−2 SS degrades significantly. The influence of traps on the cumulative effect of three noise sources (diffusion + generation–recombination/G–R + flicker) and on individual noise sources (G–R and diffusion) is explained qualitatively at low and high frequencies (f = 1 MHz and 10 GHz). The study shows that the overall noise cannot disturb the device performance at very high frequency. Various radio-frequency (RF) parameters like transconductance (gm), total input capacitance (Cgg), gate-drain capacitance (Cgd), unit-gain cutoff frequency (fT), and gain–bandwidth-product (GBP) are also studied for variation of trap types. For TC = 1014 eV−1 cm−2, the percentage change in fTmax (GBPmax) is − 21.43% (− 8%) for UT and − 22.86% (− 9.6%) for GT distribution.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Since the invention of transistor, outstanding evolution of semiconductor industry has made the world’s electronic life faster and easier beyond imagination [1]. The origin of this tremendous growth of microelectronic industry is the continuous down-scaling of transistor size. Various parasitic capacitances involved in a circuit also reduce with the down-scaling of device size and thereby, speed of the circuit is enhanced [2,3,4]. However, the adverse effect of various short channel effects (SCEs) on device electrical characteristics is becoming more severe with every advancement of transistor technology [5]. At different phases of time, microelectronic industry came up with unique solutions to the increasing problem of SCEs. Down-scaling of planer 2-D MOSFETs has achieved its physical limit long ago and hence, these are being replaced by new FET architectures such as SOI FETs, multi-gate FETs, FinFETs etc. However, these contemporary devices have their own limitations. SOI FETs, which outperform 2-D planer FETs in terms of speed and power consumption, are not being largely produced anywhere in the world due to its costly wafer development process [6,7,8,9]. Using double-gate in a planer FET enhances gate control and provides increased drive current (Ion) by creating two separate 2-D inversion layers. However, these inversion layers may overlap with each other beyond a critical body thickness (5 nm or less) [10, 11]. In such case, carriers in the overlapped channels encounter two opposite gate-fields as a consequence of which carrier–carrier scattering and surface roughness scattering increases and thereby Ion degrades [11,12,13,14]. Further, on-current (Ion) degradation due to SOI-thickness-fluctuation-induced-scattering in thin-body multi-gate transistors limits scaling of device size [14]. Double/triple gate FinFETs with very thin fins also suffer from Ion degradation for the same reason explained for multi-gate planer FETs. Besides, down-scaling of FinFETs demands high aspect ratio (height to width) fins. But, manufacturing of such fins is becoming a challenging task for lower technology nodes, as these 3-D fins standing alone may be damaged/washed away during cleaning, particularly when using sonication for enhanced particle removal, which is important for cleaning of 3-D relief [10, 11, 15, 16].

Therefore, we need a reliable FET architecture which is capable of mitigating the current limitations of various contemporary devices (SOI FETs, multi-gate FETs, and FinFETs). In 2014, a new FET structure called vertical super-thin body (VSTB) FET [11] was proposed. VSTB FET is a single-gate structure, in which its vertical thin body is firmly supported by one or more shallow trench isolation (STI) dielectric walls. Unlike multi-gate FETs, a single gate controls overall electrostatics of such device; thus for ultra-thin body (UTB) dimensions, carrier–carrier scattering reduces in the channel and Ion improves [10,11,12,13,14]. Also, STI dielectric wall supports the vertical thin body to enhance its mechanical strength and hence, helps reliable scaling process [10, 11]. 2-D analytical modeling for surface potential and threshold voltage of VSTB FET has also been developed [17]. But, an extensive study on vertical super-thin body (VSTB) FET performance in presence of various device constraints is needed to be developed to establish its reliability for circuit applications. For deep-submicron FETs, substantial increase in gate leakage current through thin SiO2 gate dielectric layer is a serious concern [18, 19]. To solve this issue, replacement of SiO2 gate dielectric by several high-k dielectrics such as Y2O3, Al2O3, La2O3, HfO2, and their related compounds has been investigated [20, 21], out of which, Hf-based oxides have drawn most research attention as the interface quality of these oxides with bulk Si is better than any other high-k dielectric/Si interface [22,23,24]. However, it has been reported in many research papers that HfO2/Si interface suffers from large number of trap charges [25,26,27]. Therefore, performance assessment of transistors with such oxide–semiconductor (HfO2/Si) interface is needed to be investigated in terms of various trap distribution types and concentrations. Apart from that, MOS device operation is affected by various noise sources such as diffusion, generation–recombination/G–R, and flicker noise [28,29,30,31].

In this work, a simulation study on net noise (diffusion + generation–recombination + flicker) and RF performance of VSTB FET in presence of uniform and Gaussian trap distributions is reported. The basic physics working behind the degradation of device performance due to trap presence at the oxide–semiconductor (HfO2/Si) interface is discussed. The dependency of individual noise power spectral density (PSD) on trap distribution types, trap concentrations, and operating frequency is also addressed here.

2 Device geometry and simulation strategy

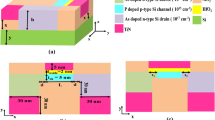

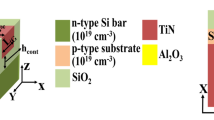

Figure 1a depicts the complete 3-D view of VSTB FET and Fig. 1b shows 2-D cross-sectional view of the same. Different steps for fabrication method of such structure are also described [11]. The thin vertical body is supported by STI dielectric wall at one side. Arsenic (As) is used as the doping element in the source and drain regions and phosphorus (P) is used for doping in the body region. The doping concentrations used for various regions are: source: 1019 cm−3, channel: 1015 cm−3, drain: 1017 cm−3, and substrate: 1015 cm−3. To reduce leakage current (Ioff), lower doping is used in the drain region as compared to the source region. However, on-current (Ion) degradation due to increased drain resistance in the lightly doped drain (LDD) is an issue. High-k dielectric oxide HfO2 (εr = 22) and TiN (work function = 4.66 eV) are used as gate dielectric oxide and gate metal, respectively. Various device dimensions used are: channel length (LCH = 26 nm), gate thickness (Tg = 5 nm), body thickness (Tb = 5 nm), and oxide thickness (Tox = 2 nm). Equal source and drain extension length (w = 4 nm) are used. Height of body (h1) and substrate (h2) uses are 35 and 20 nm, respectively. Height of SiO2 layer (h) placed between source/drain/gate contacts and substrate is 15 nm.

3-D and 2-D Sentaurus TCAD tool based on drift diffusion transport model [17, 32, 33] was used to perform the work. Initially, the input and output characteristics were studied using 3-D TCAD tool [32]. As the ITRS outlined all the desired values of various figures of merit (FoM) of future technology nodes in terms of per micrometer [34], we eventually focused on device cross-sectional performance in presence of traps and various noises. Therefore, device noise characteristics and RF performance were investigated by 2-D TCAD tool [32]. Relevant physics models were activated in the simulator to study various realistic phenomena effecting device electrical characteristics. Influence of high doping concentrations was taken care of by activating the Fermi–Dirac statistics and doping-dependent Shockley–Read–Hall (SRH) recombination model [32]. Bandgap narrowing was enabled to take care of highly doped source and drain regions [32]. Influence of device doping profile and high-k dielectric oxide on carrier mobility was accounted by enabling doping-dependent Masetti model and enhanced Lombardi model with high-k degradation, respectively [32]. Velocity saturation effect, which is a very common SCE for nanoscale device, was taken care of by triggering high-field saturation model [32]. Quantum density gradient model was also enabled to consider quantum correction effect [32]. Stress and strain may be induced in the thin vertical body by the thick STI dielectric wall. To acknowledge the stress effect, stress-induced electron mobility model and stress-dependent saturation velocity model were included [32, 35, 36]. Deformation potential model was activated to consider strain effect [32, 35, 36]. Device performance in n-type FET mainly gets degraded due to acceptor-like traps [37]. Regarding traps located at the insulator–semiconductor (HfO2/Si) interface, two types of trap (acceptor-type) distribution were considered in this work: uniform and Gaussian [28, 32] as below:

Various parameters related to the above distribution functions are described in Table 1. Also, both the trap distributions over an energy range considered in this work are shown in Fig. 2 [28].

Uniform and Gaussian trap distribution vs. energy [28]

3 Results and discussion

The main objective of the work is to study device performance dependency on trap distribution type and concentration. In Sect. 3.1, input characteristics of FinFET and VSTB FET are compared. Also, a basic study on output characteristics of 3-D VSTB FET device is presented with the help of energy band diagram. Section 3.2 presents the transfer characteristics (ID–VGS) degradation in presence of various types of trap distributions and concentrations. Net noise parameters for the cumulative effect of three noise sources (diffusion + generation–recombination/G–R + flicker) at low and high frequencies (f = 1 MHz and f = 10 GHz) are also discussed. In Sect. 3.3, frequency and trap dependency of G–R and diffusion noise are addressed. Lastly, in Sect. 3.4, variation of RF FoM with respect to variation in trap concentration and distribution type is presented.

3.1 Study of basic characteristics (input and output)

TCAD extracted 3-D simulated views of single gate FinFET, inner view of FinFET, and VSTB FET are shown in Fig. 3a–c, respectively. The simulation set up, various dimensional parameters, and materials used for FinFET is kept as the same (described in Sect. 2) as used for VSTB FET. The input characteristics (ID–VGS) of both the devices are compared in Fig. 3d, which demonstrates that VSTB FET exhibits much better off-current (Ioff) and subthreshold swing (SS) as compared to the same-scale FinFET device. Such superiority in Ioff and SS is found since, vertical STI dielectric wall in VSTB FET offers pseudo-SOI type of isolation between source and drain [11]. On the other hand, absence of such isolation in FinFET device increases Ioff and thus, SS deteriorates significantly. Table 2 presents a comparative overview between various electrical parameters of FinFET and VSTB FET. Drain-induced barrier lowering (DIBL) for VSTB FET is calculated from Fig. 3e using the relation [38]:

where \(V_{{{\text{DS}}_{{{\text{sat}}}} }} = 1\;{\text{V}}\) and \(V_{{{\text{DS}}_{{{\text{lin}}}} }} = 0.05\;{\text{V}}\). VT,lin and VT,sat are threshold voltages (estimated for a constant current of 10–7 A) at \(V_{{{\text{DS}}_{{{\text{lin}}}} }}\) and \(V_{{{\text{DS}}_{{{\text{sat}}}} }}\), respectively. The output characteristics (ID–VDS) of the device is depicted in Fig. 3f, which shows that the device works for low values of VDS too. At VDS = 0, a little ID flow is observed (Fig. 3f) and the reason for that has been explained later on.

Device energy band (E-band) diagrams corresponding to three different bias conditions: zero bias/equilibrium (VGS = 0, VDS = 0), bias 1 (VGS = 0.8, VDS = 0), and bias 2 (VGS = 0.8, VDS = 0.4), are shown in Fig. 4a–c, respectively, from which the internal physics working behind device electronics can be understood. Under equilibrium condition, source-to-channel transition barrier (Fig. 4a) is very high for which channel cannot form. Besides, level of conduction band (EC) at drain side (64–94 nm) is higher than that of source side (0–30 nm) due to the doping nature of the device (source: 1019 cm−3, drain: 1017 cm−3). Thus, ID is zero for zero bias condition. Under bias 1 (VGS = 0.8, VDS = 0), gate field reduces source to channel barrier height, which is also evident from Fig. 4b; thus source electrons move to channel region and form inversion layer. Another observation of Fig. 4b is that in the channel region (34–60 nm), conduction energy level (EC) lies below the electron Fermi level (Efn), which illustrates that the channel behaves as degenerate semiconductor. At such condition, although VDS = 0, gate fringing fields contribute a little amount of lateral fields which lead to weak movement of the channel electrons to the drain [39]. Thus, at VDS = 0 too, a negligible flow of ID is observed (Fig. 3f), which increases with the increase in VGS. In Fig. 4c, under bias 2 (VGS = 0.8, VDS = 0.4) EC at the drain side goes down that of source and channel region; thus channel electrons can easily move to the drain and contribute to significant ID flow. Here also, channel behaves as degenerate semiconductor.

3.2 Study of device characteristics in presence of traps and corresponding net noise performance

This section presents device performance in presence of various trap distributions and the net noise (diffusion + G–R + flicker) characteristics. From Fig. 5a, b, which depict ID–VGS plot for uniform trap (UT) and Gaussian trap (GT) distributions, respectively, it is clear that with increasing trap concentration (TC) for both the distributions (UT and GT), the transfer characteristics deteriorate from their ideal nature (under no trap condition). Traps present in the semiconductor-insulator surface create extra energy states, which randomly capture and later release carriers moving through the channel and thus, alter E-band diagram of the device. Figure 5c, d represent, respectively, E-band diagrams for UT and GT distribution. For both the distributions, at the channel region (34–60 nm) EC goes up of Efn, which illustrates the fact that interface trap reduces carrier density at the channel region. Thus, at a fixed value of VGS, number of channel charges decreases more and more with increasing TC and hence, ID degrades (Fig. 5a, b). For a particular trap concentration, degradation of ID is more severe in case of GT (Fig. 5b). This happens due to non-uniform distribution of Gaussian traps. Although, degradation in ID for any type of trap (UT/GT) is negligible for lower TC [(1011–1013) eV−1 cm−2], effect of the traps on ID becomes prominent for TC = 1014 eV−1 cm−2 (Fig. 5a, b).

For ideal condition (no trap), the estimated value of cross-sectional ID is 114.562 µA/µm at VGS = 0.65 V and 127.18 µA/µm at VGS = 0.7 V. In this section, at VDS = 0.4 V, Ion is calculated as ID at VGS = 0.65 V (VGS = 0.7 V) for UT (GT) distribution. For such estimated Ion, in ideal condition (no trap), value of Ion/Ioff is 0.73 × 108 for UT and 0.81 × 108 for GT. The values of Ioff (at VGS = 0 V and VDS = 0.4 V) and SS under no trap condition are 1.56477 pA/µm and 66.17 mV/dec, respectively. Variations of Ioff, Ion, Ion/Ioff, and SS with respect to trap distribution type and TC are shown in Fig. 6a–h. Figure 6a, c, e, g corresponds to UT and Fig. 6b, d, f, h corresponds to GT. Both, Ioff (Fig. 6a, b) and Ion (Fig. 6c, d), decrease for the presence of UT/GT traps. However, since, decrease in Ioff is relatively higher than decrease in Ion, Ion/Ioff (Fig. 6e–f) shows improvement for increasing TC (UT/GT) except for the case of GT of TC = 1014 eV−1 cm−2 (Fig. 6f). For GT with such high TC (1014 eV−1 cm−2), Ion reduces drastically (Fig. 6d), which leads to fall of Ion/Ioff. On the other hand, to attain any particular value of ID, since, device with interface traps needs more VGS than any ideal device (with ideal interface), deterioration in SS increases with increasing TC (Fig. 6g, h). Percentage changes in Ion/Ioff and SS in trap-affected device with respect to ideal condition (no trap) is presented in Table 3.

Figure 7a, b represents gate voltage electron noise spectral density (Svgee) as a function of VGS for UT and GT, respectively. Electron density across the channel length for maximum GT concentration of 1014 eV−1 cm−2 at two frequencies is shown in Fig. 7c. Plots of drain current noise spectral density (Sid) vs. VGS for UT and GT are shown in Fig. 7d, e, respectively. From Fig. 7a, b, d, e, it is clear that at a fixed VGS value, PSDs of both types of noise (Svgee and Sid) fall by a large order for high frequency (f = 10 GHz), as the charge trapping probability also reduces at higher frequencies [40]. This property helps the device to work efficiently at higher frequencies.

At f = 1 MHz, under no trap condition and for both the trap distributions (Fig. 7a, b), Svgee plots, following several spikes, gradually decrease with increase in VGS. Such nature of plot can be explained by the carrier concentration variation in the channel for varying VGS values. At lower VGS, channel consists of very low concentration of charges. In such a state, random capturing and releasing of charges by the traps lead to large variation in the number and velocity of channel charges, which eventually reflect on Svgee values. At higher VGS, inversion layer is formed and channel charge concentration becomes very high. Therefore, any type of variation in charge concentration due to traps is now weakly felt by the high concentrated channel charges, and hence, Svgee decreases for higher VGS.

However, at f = 10 GHz, for lower values of VGS (Fig. 7a, b), Svgee initially increases and then slowly gets saturated at higher VGS. For the same VGS value, charge density developed across the channel at high frequency is lower than that of low frequency (Fig. 7c). As such, at lower VGS, very less number of charges exist in the channel and hence, probability of charge trapping also becomes low at high frequency. But, beyond a critical value of VGS charge concentration in the channel increases, and due to this, charge trapping probability becomes high; thereby, Svgee also starts to increase (for VGS > 0.15 V in Fig. 7a, b). However, for very high VGS (> 0.75 V in Fig. 7a, b), Svgee gets saturated due to the same reason explained for reduction in Svgee at f = 1 MHz for high VGS. Another observation of Fig. 7a, b is that the net value of Svgee at any particular frequency increases with increasing trap (UT/GT) concentration. This happens due to the greater charge-trapping probability with higher TC. Also, compared to UT distribution, GT distribution contributes to higher Svgee.

Sid variations with respect to change in VGS follow such pattern (Fig. 7d, e), which increases initially for lower VGS, but gets saturated for VGS> 0.6 V, as ID also saturates at higher VGS. Also, PSD of Sid is lesser at f = 10 GHz due to reduction in the charge trapping probability at high frequency [40]. It is observed that for TC of the order of 1014 eV−1 cm−2, Sid pattern deteriorates to a large extent from its linear characteristics at lower VGS. Also, GT distribution (Fig. 7e) has more significant effect on Sid compared to UT distribution (Fig. 7d).

3.3 Individual noise (G–R and diffusion) performance

It is observed that at low and high frequencies, the net noise (diffusion + G–R + flicker) characteristics of the device are dominated by generation–recombination (G–R) noise and diffusion noise, respectively [28]. Flicker noise, the origin of which is the conductance fluctuation of charge carriers moving through a channel affected by contaminants, is much prominent at lower frequencies and decreases significantly with increase in frequency [29, 30]. As the primary focus is on high frequency, flicker noise effect can be ignored for advanced devices. In this section, we perform a study on G–R and diffusion noise nature of the device. We have considered only Gaussian trap (GT) distribution, as with this type of distribution device performance gets more affected, which have already been seen in Sect. 3.2. Figure 8a, b shows Svgee vs. VGS plots for G–R noise at f = 1 and 10 GHz, respectively. Same type of plots for diffusion noise are shown in Fig. 8c (f = 1 MHz) and (d) (f = 10 GHz).

Comparing Fig. 8a, c, it is clear that for any given value of VGS in the case of G–R noise, the PSD of Svgee is much higher at f = 1 MHz than that of diffusion noise. At low frequency, the fluctuation in concentration and velocity of the carriers is mainly caused by Shockley–Read–Hall (SRH) and defect centres associated with the channel [31] and hence, Svgee for G–R noise becomes high. Also, PSD of Svgee increases for higher trap concentration (Fig. 8a). Again, at f = 1 MHz for a given value of VGS comparing Figs. 7b and 8a (Sect. 3.2), it can be seen that the net Svgee curves (Fig. 7b of Sect. 3.2) for different trap concentrations are also following almost the same pattern of Svgee corresponding to G–R noise only (Fig. 8a). At f = 10 GHz, for all values of VGS, amplitude of Svgee exhibits higher values in case of diffusion noise (Fig. 8d) than that of G–R noise (Fig. 8b). At high frequency, probability of charge trapping and de-trapping by recombination centres is reduced. For fast variation of VGS, channel charges undergo a diffusion mechanism, the rate of which is a strong function of VGS. Thus, if VGS varies very fast, the average diffusion rate of carriers also changes significantly with time, leading to a prominent diffusion noise at high frequency. Irrespective of VGS values, the net noise PSDs (Svgee in Fig. 7b of Sect. 3.2) at f = 10 GHz are comparable to diffusion noise Svgee curves (Fig. 8d).

3.4 Device RF performance in presence of traps

The RF performance is studied under three cases: no trap (NT), uniform trap (UT), and Gaussian trap (GT). Figure 9a–f correspond to various RF parameters like transconductance (gm) at f = 10 GHz, total input capacitance (Cgg) at f = 10 GHz, total input capacitance (Cgg) at f = 1 kHz, gate-drain capacitance (Cgd) at f = 10 GHz, unit-gain cutoff frequency (fT) at f = 10 GHz, and gain–bandwidth-product (GBP) at f = 10 GHz as a function of VGS, respectively. The variations shown are for trap concentration of 1014 eV−1 cm−2.

It can be seen from Fig. 9a that as VGS starts to increase, gm rises sharply at three different VGS values for three different cases (NT, UT, and GT). The point of VGS, at which gm rise occurs, shifts towards right as we go from NT to UT to GT. Generally, for a fixed value of VDS, when VGS is applied, rise in ID occurs at the lowest VGS under NT condition. But, presence of traps hinders the normal ID rise nature by participating in channel transport mechanism. At such condition, effective channel charge becomes a function of interface traps and mostly reduces. Therefore, both ID and gm fall. This is the reason behind the right shifting of gm rise point across VGS axis. As the effect of GT is more prominent than that of NT and UT distribution, gm rise requires larger VGS in case of GT as compared to the other two cases. From Fig. 9b, it is clear that at f = 10 GHz for a given amplitude of VGS as we go from NT to UT to GT, the value of Cgg follows a descending order. Also, distortion/stretch out in capacitance–voltage (C–V) plot (Fig. 9b) is not observed. The reason of such nature of C–V plot is as follows: at high-frequency (f = 10 GHz) interface traps, which have longer charging/discharging time constant compared to time-period of applied high-frequency gate bias, cannot response as fast as applied gate field; thus the distortion/irregularity in charge distribution caused by interfacial traps becomes minimal at high frequency. However, at low frequency (f = 1 kHz), interfacial traps actively participate in channel charge distribution and thus randomness/distortion is added to the C–V plot, which is also observable in Fig. 9c. The peak value of Cgd (Fig. 9d) is seen to follow an ascending order going from NT to UT to GT. The unit-gain cutoff frequency (fT) and GBP are calculated from the relations [28, 41, 42]:

fT and GBP (Fig. 9e, f) attain peak values at smaller VGS under NT condition. But, introduction of traps degrades fT and GBP at lower VGS by suppressing gm (Fig. 9a). All the values of different RF FoM: peak transconductance (gmp), peak input capacitance (Cggp), peak gate-drain capacitance (Cgdp), maximum cutoff frequency (fTmax), and maximum gain–bandwidth product (GBPmax) for the three cases (NT, UT, and GT) are listed in Table 4, from which it can be concluded that VSTB FET is suitable for high-frequency operations.

4 Conclusion

In this work, the effect of various interfacial trap (HfO2/Si) distributions on VSTB FET performance is presented. It is observed that the Gaussian trap (GT) distribution disturbs fundamental parameters such as Ion, Ion/Ioff, and SS significantly. Irrespective of trap distribution types (UT/GT), for trap concentration < 1014 eV−1 cm−2 device performance shows negligible deterioration. The change in energy band diagram for a particular bias condition in presence of interfacial traps (UT or GT) is also discussed. A qualitative analysis of net noise (diffusion + G–R + flicker) and individual noise PSD dependency on trap distribution type and concentration is also reported. It is observed that for lower values of VGS too, the values for unity-gain cutoff frequency (fT) and gain–bandwidth-product (GBP) of the device are in gigahertz (GHz) range; this property helps the device to work efficiently in low-power high-speed circuits.

References

M. Riordan, L. Hodesson, C. Herring, The invention of the transistor. Rev. Mod. Phys. 71, S336–S345 (1999)

K. Han, H. Shin, K. Lee, Analytical drain thermal noise current model valid for deep submicron MOSFETs. IEEE Trans. Electron Devices 51(2), 261–269 (2004). https://doi.org/10.1109/TED.2003.821708

R.T. Bühler, R. Giacomini, M.A. Pavanello, J.A. Martino, Fin cross-section shape influence on short channel effects of MuGFETs. J. Integr. Circuits Syst. 7, 137–144 (2012)

J.C. Tinoco, J. Alvarado, A.G. Martinez-Lopez, J. Raskin, Impact of extrinsic capacitances on FinFETs RF performance, in 2012 IEEE 12th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Santa Clara, CA, 2012, pp. 73–76. 10.1109/SiRF.2012.6160141

T. Skotnicki, J.A. Hutchby, T.-J. King, H.-S.P. Wong, F. Boeuf, The end of CMOS scaling: toward the introduction of new materials and structural changes to improve MOSFET performance. IEEE Circuits Devices Mag. 21(1), 16–26 (2005). https://doi.org/10.1109/MCD.2005.1388765

F. Balestra, Silicon-on-Insulator Devices, Wiley Encyclopedia of Electrical and Electronics Engineering, edited by John G. Webster (Wiley, 2014).

V. Jaju, V. Dalal, Silicon-on-insulator technology, in EE 530 Advances in MOSFETs, pp. 1–12, 2004.

S. Cristoloveanu, Silicon on insulator technologies and devices: from present to future. Solid State Electron. 45(8), 1403–1411 (2001)

X. Zhang, D. Connelly, H. Takeuchi, M. Hytha, R.J. Mears, T.K. Liu, Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7-/8-nm node. IEEE Trans. Electron Devices 64(1), 329–332 (2017). https://doi.org/10.1109/TED.2016.2626397

N.P. Maity, R. Maity, S. Maity, S. Baishya, Comparative analysis of the quantum FinFET and trigate FinFET based on modeling and simulation. J. Comput. Electron. 18, 492–499 (2019)

V. Koldiaev, R. Pirogova, Vertical super-thin body semiconductor on dielectric wall devices and methods of their fabrication. U.S. Patent 8 796 085 B2, 2014.

C. Riddet, C. Alexander, A.R. Brown, S. Roy, A. Asenov, Simulation of “ab initio” quantum confinement scattering in UTB MOSFETs using three-dimensional ensemble Monte Carlo. IEEE Trans. Electron Devices 58(3), 600–608 (2011). https://doi.org/10.1109/TED.2010.2095422

B. Majkusiak, T. Janik, J. Walczak, Semiconductor thickness effects in the double-gate SOI MOSFET. IEEE Trans. Electron Devices 45(5), 1127–1134 (1998)

K. Uchida, J. Koga, S.-I. Takagi, Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs—Coulomb scattering, volume inversion, and δTSOI-induced scattering, in IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 2003, pp.33.5.1–33.5.4. 10.1109/IEDM.2003.1269402

Y. Omura, H. Konishi, K. Yoshimoto, Impact of fin aspect ratio on short-channel control and drivability of multiple-gate SOI MOSFETs. J. Semicond. Technol. Sci 8(4), 302–310 (2008)

Y. Liu, K. Ishii, M. Masahara, T. Tsutsumi, H. Takashima, H. Yamauchi, E. Suzuki, Cross-sectional channel shape dependence of short channel effects in fin-type double-gate metal oxide semiconductor field effect transistors. Jpn. J. Appl. Phys. 43(4S), 2151 (2004)

S. Roy, A. Chatterjee, D.K. Sinha, R. Pirogova, S. Baishya, 2-D analytical modeling of surface potential and threshold voltage for vertical super-thin body FET. IEEE Trans. Electron Devices 64(5), 2106–2112 (2017). https://doi.org/10.1109/TED.2017.2687465

G.D. Wilk, R.M. Wallace, J.M. Anthony, High-k gate dielectrics: Current status and materials properties considerations. J. Appl. Phys. 89, 5243–5275 (2001)

S.Y. Tan, Challenge and performance limitations of high-K and oxynitride gate dielectrics for 90/65 nm CMOS technology. Microelectron. J. 38, 783–786 (2007)

M.H. Cho, D.H. Ko, Y.G. Choi, K. Jeong, D.Y. Noh, H.J. Kim, C.N. Whang, Structural and electrical characteristics of Y2O3 films grown on oxidized Si(100) surface. J. Vac. Sci. Technol. A 19, 192–199 (2001)

I. De, D. Johri, A. Srivastava, C.M. Osburn, Impact of gate work function on device performance at the 50 nm technology node. Solid State Electron. 44, 1077–1080 (2000)

R. Jiang, E. Xie, Z. Wang, Interfacial chemical structure of HfO2/Si film fabricated by sputtering. Appl. Phys. Lett. 89(14), 142 907-1–142 907-3 (2006)

D. Schmeiser, E. Zschech, Silicate formation at the interface of Hf-oxide as a high-k dielectrics and Si(0 0 1) surfaces. Mater. Sci. Semicond. Process 9, 934–939 (2006)

S.J. Chang, W.C. Lee, J. Hwang, M. Hong, J. Kwo, Time dependent preferential sputtering in the HfO2 layer on Si (100). Thin Solid Films 516, 948–952 (2008)

N. Miyata, Study of direct-contact HfO2/Si interfaces. Materials 5, 512–527 (2012)

N.P. Maity, R. Maity, R.K. Thapa, S. Baishya, Study of interface charge densities for ZrO2 and Hf02 based metal-oxide-semiconductor devices. Adv. Mater. Sci. Eng. 2014, 1–6 (2014)

S.Y. Tan, Control of interface traps in HfO2 gate dielectric on silicon. J. Electron. Mater. 39, 2435–2440 (2010)

R. Goswami, B. Bhowmick, S. Baishya, Electrical noise in circular gate tunnel FET in presence of interface traps. Superlattices Microstruct. 86, 342–354 (2015)

P. Anandan, A. Nithya, N. Mohankumar, Simulation of flicker noise in gate-all-around silicon nanowire MOSFETs including interface traps. Microelectron. Reliab. 54, 2723–2727 (2014)

L.K.J. Vandamme, F.N. Hooge, What do we certainly know about 1/f noise in MOSTs? IEEE Trans. Electron. Devices 55(11), 3070–3085 (2008). https://doi.org/10.1109/TED.2008.2005167

S.Y. Wu, Theory of generation–recombination noise in MOS transistors. Solid State Electron. 11, 25–32 (1968)

Sentaurus Device User Manual, Version J 2014.09 (Synopsis Inc., Mountain View, 2014)

P. Saha, P. Banerjee, S.K. Sarkar, 2D modeling based comprehensive analysis of short channel effects in DMG strained VSTB FET. Superlattices Microstruct. 118, 16–28 (2018)

International Technology Roadmap for Semiconductors. (2015). [Online]. https://eps.ieee.org/images/files/Roadmap/ITRSFacInt2015.pdf.

X. Chen, C.M. Tan, Modeling and analysis of gate-all-around silicon nanowire FET. Microelectron. Reliab. 54, 1103–1108 (2014)

K.R. Barman, S. Baishya, Performance analysis of vertical super-thin body (VSTB) FET and its characteristics in presence of noise. Appl. Phys. A 125, 401 (2019). https://doi.org/10.1007/s00339-019-2682-x

X.Y. Huang et al., Effect of interface traps and oxide charge on drain current degradation in tunneling field-effect transistors. IEEE Electron Device Lett. 31(8), 779–781 (2010). https://doi.org/10.1109/LED.2010.2050456

Y. Eng et al., Importance of ΔV DIBLSS/(I on/I off) in evaluating the performance of n-channel bulk FinFET devices. IEEE J. Electron Devices Soc. 6, 207–213 (2018). https://doi.org/10.1109/JEDS.2018.2789922

M. Schlosser, K.K. Bhuwalka, M. Sauter, T. Zilbauer, T. Sulima, I. Eisele, Fringing-induced drain current improvement in the tunnel field-effect transistor with high-к gate dielectrics. IEEE Trans. Electron Devices 56(1), 100–108 (2009). https://doi.org/10.1109/TED.2008.2008375

C. Shen, M.-F. Li, H. Yu, X. Wang, Y.-C. Yeo, D. Chan, D.-L. Kwong, Physical model for frequency-dependent dynamic charge trapping in metal oxide-semiconductor field effect transistors with HfO2 gate dielectric. Appl. Phys. Lett. 86, 093510 (2005)

V. Vijayvargiya, S.K. Vishvakarma, Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans. Nanotechnol. 13(5), 974–981 (2014). https://doi.org/10.1109/TNANO.2014.2336812

KWJ Chew et al., RF performance of 28 nm PolySiON and HKMG CMOS devices, in 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, 2015, pp. 43–46. 10.1109/RFIC.2015.7337700

Acknowledgements

This work is an outcome of a project under CSIR-EMR-II (Sanction no. 22 (0737)17/EMR-II dated 16th May, 2017), Govt. of India awarded to Electronics and Communication Engineering, NIT Silchar, Silchar 788010, India. The authors would also like to acknowledge Mr. Saurav Roy and Mr. Ravi Singh Kurmvanshi for their aid in proper handling of related software.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Roy Barman, K., Baishya, S. An insight to the performance of vertical super-thin body (VSTB) FET in presence of interface traps and corresponding noise and RF characteristics. Appl. Phys. A 125, 865 (2019). https://doi.org/10.1007/s00339-019-3165-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-3165-9