Abstract

In this paper, a gate-all-around junctionless tunnel field effect transistor (JLTFET) based on heterostructure of compound and group III–V semiconductors is introduced and simulated. In order to blend the high tunneling efficiency of narrow band gap material JLTFETs and the high electron mobility of III–V JLTFETs, a type I heterostructure junctionless TFET adopting Ge–Al x Ga1−x As–Ge system has been optimized by numerical simulation in terms of aluminum (Al) composition. To improve device performance, we considered a nanowire structure, and it was illustrated that high-performance logic technology can be achieved by the proposed device. The optimal Al composition founded to be around 20 % (x = 0.2). The numerical simulation results demonstrate that the proposed device has low leakage current I OFF of ~1.9 × 10−17, I ON of 4 µA/µm, I ON/I OFF current ratio of 1.7 × 1011 and subthreshold swing SS of 12.6 mV/decade at the 40 nm gate length and temperature of 300 K.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Over the past several decades, the continuous scaling of metal oxide semiconductor field effect transistors (MOSFETs) beyond constraints of planar structure requires multigate devices like FinFETs [1], omega-gate FETs [2] and gate-all-around FETs [3]. However, these structures are also subjected to various physical limits such as short-channel effects (SCEs) and high standby power dissipation. In order to dominate these stringent demands, newly junctionless field effect transistor (JLFET) has been proposed and fabricated which does not require PN junctions and ultra-shallow concentration gradient at lateral junctions [4, 5]. However, it has significant leakage OFF-state current due to its bulk conduction which leads to high values of power consumption. Lately, tunneling filed effect transistors (TFETs) based on band-to-band tunneling (BTBT) mechanism are achieving popularity as one of the most promising devices for ultra-scaled MOSFETs, due to their low-OFF-state current (I OFF) and steep subthreshold swing (SS) below the thermionic limit of 60 mV/decade [6–9]. Results that stem from atomistic modeling have shown that TFETs potentially can perform superior than conventional FETs at low supply voltages [10, 11]. On the other hand, it has been pointed out that silicon-based TFETs have rather low ON-state current (I ON), which makes it inappropriate in high-performance (HP) applications [12, 13]. In order to achieve high tunneling current (I ON), various kinds of compound semiconductors like III–V material [14] with small effective mass and narrow staggered energy band are required [15]. Recently, a new structure named junctionless tunnel field effect transistor (JLTFET) has been proposed which is tunnel FET without any abrupt doping profile [16–19]. It has presented good ON-state current and low subthreshold swing as blends advantages of JLFETs and TFETs. JLTFET also features lower subthreshold slope than conventional MOSFET and JLFET at the room temperature opens new future for low-power application devices [16]. In this paper, we have performed a comparative study on type I heterostructure junctionless TFET (IH-JLTFET) with homojunction JLTFETs based on various materials. Also, we have achieved an optimum design for an IH-JLTFET of Ge–Al x Ga1−x As–Ge system by 2D device simulation to meet HP requirements. It is proved that the aluminum (Al) composition (x) in the Al x Ga1−x As channel affects the total current, whereas it was simulated for 0 (GaAs) to 0.4 Al mole fraction with 0.05 step. It is shown that higher mole fraction x of aluminum leads to further degradation of ON-state current (I ON), defect formation at the channel interface and high values of threshold voltage (V th) for HP logic technology. Moreover, we have investigated the energy band diagram profile in the ON state and OFF states for a Ge–Al x Ga1−x As–Ge H-JLTFET. The lateral electric field and potential pattern of the device are examined in both the states. Further, transfer characteristics of the proposed structure compared with prior homo- and heterostructure JLTFETs are simulated for constant drain voltage V DS = 1 V. Finally, the overall optimization of the device structures such as I ON, I OFF, ON/OFF current ratio, subthreshold swing (SS) is analyzed by adjusting the different mole fraction of Al x Ga1−x As configurations.

2 Device structure and simulation

2.1 Device structure

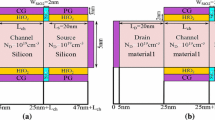

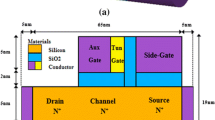

The 3D schematic view and cross section along the channel of the IH-JLTFET are shown in Fig. 1. The type I heterostructure junctionless tunnel field effect transistor (IH-JLTFET) does not contain any doping junctions as the channel is uniformly n-type doped. Therefore, it is potential solution to the problem of random dopant fluctuations. It is fundamentally a hetero-channel heavily n-type-doped (1 × 1019 cm−3) JLFET by the concept of band-to-band tunneling. The device is the junctionless-based TFET with a channel length of 40 nm, source/drain extension length of 30 nm and nanowire film thickness of 10 nm. The gate oxide thickness is 2 nm and isolation layer in between middle gate (MG) and side gate (SG) is 2 nm, which works as a spacer. In order to provide better electrostatic controllability of gate over channel region, gate-all-around technology is used. Also, HfO2 as gate the dielectric is included. It could be implemented utilizing atomic layer deposition (ALD) and this technique resulted in lower surface oxide defects. Preset parameters used for device simulation of IH-JLTFET as shown in Fig. 1 are tabulated in Table 1.

Typically, the IH-JLTFET is a lateral n-type JLFET, which uses two isolated gates (MG and SG) of two different metal workfunctions, to make the layer beneath the gates intrinsic and p-type, respectively [17, 18]. The proposed device is a quantum mechanical device (QMD), and tunneling of electrons depends on the barrier width between the energy band of source–channel and drain–channel. Hence, in order to implement higher I ON and I ON/I OFF device with lower subthreshold swing, steeper energy bands have to be created with propinquity of bands in tunneling region with higher band overlap [20, 21]. Use of heterojunction of Ge at source and Al x Ga1−x As at channel side satisfies above condition.

In order to make the layers beneath MG and SG intrinsic and p-type, respectively, we have deliberately varied the metal workfunction from 4.2 to 4.6 and 5.1 to 5.7 eV, respectively. For all the devices in this study, the workfunction of 4.45 and 5.6 eV for MG and SG has chosen which give the superior result in terms of SS and ON-/OFF-state current values. The integration of MG and SG together in the fabrication process, whose workfunctions are different, could be done by using the techniques as reported in Refs. [22–24]. The formation of the isolation layer with thickness of 2 nm of SiO2 could be done either by using a sputtering process or by a modern photolithography process (such as electron beam lithography, X-ray lithography, extreme ultraviolet lithography and ion projection lithography) after formation of the field oxide by wet oxidation.

The simulated energy band diagrams of the proposed Ge–Al x Ga1−x As–Ge H-JLTFET with the position at the channel and gate dielectric interface for operating mode (V MGS = V DS = 1 V) and standby mode (V MGS, V DS) = (0, 1 V) are shown in Fig. 2. In the absence of gate voltage, there is no overlap between the occupied band of the source and the unoccupied band of the channel. In this case, the probability of tunneling of electrons is negligible, so the OFF-state current flows only because of an N+–I–P+←diode leakage and consequently gives extremely small current (I OFF). Contrarily, as the gate voltage becomes increasingly positive from the OFF state, band edges at the source end will bend more, making the tunneling barrier increasingly thinner. Hence, there is a high possibility of tunneling of electrons from a valence band of the source to the conduction band of the channel which result in a significant amount of current flows due to the quantum tunneling mechanism. Like in a TFET, we apply gate voltage only on the MG (the gate above the intrinsic region of the device) to turn the device on. The voltage of MG is varied from 0 to 1 V for turning the device on.

The lateral electric field profile of the suggested device as a function of position along x-direction for ON state and OFF state is illustrated in Fig. 3. In the OFF state, because the formation of band diagram profile looks like N+–I–P+-doped device structure, it has been created two electric field peaks at the source–channel and drain–channel interface. However, In the ON state, because of the application of gate-to-source voltage, the band diagram profile behaves similar to N+–N–P+-doped device structure, so it has been created one strong electric filed peak at the source–channel interface. The strong electric field peak in between the source and channel regions implicates that tunneling is taking place in that region due to the quantum tunneling phenomenon. It is also seen that this high electric field peak is observed at the source contact side in both states. This peak is because of reversed biased P–N junction formation near the interface of the source region, since near the interface of the source region electrons do not get completely depleted. Because of this the interface near the source region is still an n-type region. The surface potential distributions along the channel for both the ON state and OFF state are further investigated in Fig. 4. From the figure, it is explicit that the voltage is gradually varying from the drain toward the source side with the flat region. This trend indicates the region below the gate electrode where no doping junctions are present, and the electric field is almost zero, as shown in Fig. 3. In the ON state as the gate-to-source voltage increases, the electron concentration of the device layer below the drain and channel regions increases and becomes almost an n-type region. This results in narrowing of the barrier between the source and channel of the device, and consequently, the potential increases.

The remarkable numerical simulation work has been reported on type I heterostructure TFET [25, 26]. In fabrication, Al x Ga1−x As can be epitaxially grown on Ge substrate by molecular beam epitaxy (MBE) or metal–organic chemical vapor deposition (MOCVD) to make up the Ge–Al x Ga1−x As–Ge heterostructure. In a similar fashion, Ge:AlGaAs H-JLTFET could be fabricated through epitaxial growth process. Al x Ga1−x As can be grown directly on Ge since their lattice constants are very similar at room temperature, 5.6533 + 0.0078x and 5.658 Å, respectively. It is noteworthy that in analyzing the simulation results, the average subthreshold swing (SSAVG) was defined as the average slope between the onset point of drain to source where current crosses I DS = 1 × 10−7 A/μm current (I DS) and the reference point at I DS = 1 × 10−15 A/μm on the I D–V GS transfer curve [27]. The I ON and I OFF were calculated by supply voltages of (V DS = 1 V, V MGS = 1 V) and (V DS = 1 V, V MGS = 0 V), respectively.

2.2 Simulation configuration

All simulations evaluated using 2D TCAD simulator Silvaco Atlas™ version 5.16.2.R [28]. We use nonlocal band-to-band tunneling (BTBT) model [29] to account for the amount of current accumulated due to tunneling of electron from source to channel side of the regime. We comprise the effect of Fermi–Dirac statistics in the calculation of the intrinsic carrier concentration required in the expressions for Shockley–Read–Hall (SRH) recombination. To capture the effect of temperature-dependent mobility, a concentration-dependent mobility (CONMOB) model and parallel and perpendicular electric field-dependent mobility (FLDMOB) model are used. Due to the presence of high doping concentrations, band gap narrowing (BGN) and auger recombination (AUGER) models are included in the simulations. Moreover, in order to assume high impurity atom in the channel and also to take into account an interface trap (or defect), the SRH recombination mode is enabled [30]. To include quantum confinement effects at the Si/SiO2 interface due to heavy doping concentration and thin oxide thickness, quantum confinement (HANSCHQM) model given by Hansch [31] is considered. Trap-assisted tunneling (SCHENK.TUNN) model given by schenk [32] to account for interface trap effect on electron band-to-band tunneling in TFETs is enabled.

3 Results and discussion

3.1 Advantages over prior homo- and heterostructure JLTFETs

Figure 5 compares the simulated I D–V GS characteristics from homostructure JLTFETs of which materials are Si, Ge [16]. Also, a simulated transfer curves from InAs–GaSb and SiGe–Si–Si heterostructure JLTFETs in the previous researches have been brought to make further comparison with the proposed device [17, 18]. The doping concentrations of all the JLTFETs are 1 × 1019 cm−3 within the source, drain and channel region. For the high doping concentration, the ON/OFF current ratio is high due to enhancing the energy band overlap between the source and channel at ON-state. From Fig. 5, it is explicit that Ge homostructure JLTFET encompasses higher I ON tunneling current compared with silicon one. The E G’s of Ge and Si are 0.66 and 1.12 eV, respectively. In sequence, since a smaller E G intensifies the BTBT proficiency and the electron mobilities of Ge and Si are 3900 cm2/V s and 1400 cm2/V s, respectively, I ON of a Ge JLTFET is much higher than that of a Si device. SiGe source for higher tunneling proficiency and Si drain for reducing I OFF more effectively can be adjoined to improve the device performances. Process attempts on Si:Si1−x Ge x interface resulted significant progress and indicated it as most suited candidate in heterostructure TFETs [33, 34]. In that case, values of I ON /I OFF and subthreshold swing are finer with the presence of SiGe at source side while they drop drastically in the presence of larger band gap silicon material at source side. In the InAs–GaSb H-JLTFET, GaSb with a band gap of 0.726 eV in the drain side and InAs with a band gap of 0.354 eV in the source side enhances BTBT current between the source and the channel. As indicated in the Figure, relatively small leakage I OFF current flows due to the large barrier width for tunneling in the drain and channel interface. Finally, the proposed device with Ge–AlGaAs–Ge heterojunction shows superior transfer characteristics comparable to other homo- and heterostructure JLTFETs. For a good comparison, no Al composition was introduced to match gate-to-source voltage where the minimum I OFF’s appear. The suggested device presents higher tunneling barrier width modulation at higher gate voltage which reasons higher I ON and steeper switching.

Here, I ON is determined by the mixture effect of magnitude of E G for BTBT at the source-to-channel junction and electron mobility in the channel. Despite the small value of Ge band gap at the source-to-channel junction, larger value of electron mobility of GaAs about 8000 cm2/V s results in excellent transition probability. In that situ, I ON converges to that of Ge JLTFET while I OFF is kept lower that other features as shown in Fig. 5, which is the best performance achievable by the group III–IV semiconductor materials.

One of the main obstacles of Ge JLTFET is high leakage OFF current as shown in Figs. 5 and 6. A smaller band gap of Ge enhances the tunneling current by gate-induced drain leakage (GIDL) at the channel-to-drain junction when a negative gate voltage is applied. Figure 6 illustrates I D–V GS curves for Ge JLTFET and the proposed IH-JLTFET based on Ge–Al x Ga1−x As–Ge system for aluminum mole fraction x = 0, 0.15 and 0.3. It is clear that the current drivability is reduced as x composition increases. For the value of x = 0.15, I ON of Ge JLFET and a Ge–Al x Ga1−x As–Ge H-JLTFET are comparable, but I OFF of the latter is much lower. By introducing more Al atoms, band gap gets larger which is the technique for suppressing I OFF. On the other hand, the electron mobility is degraded which lowers I ON. As a result, the analysis results support that introducing a heterojunction formed by Ge and Al x Ga1−x As enables to expect improved I ON due to a small E G of the source-side Ge and high electron mobility of Al x Ga1−x As channel. It is also retaining I OFF sufficiently low by a large E G of Al x Ga1−x As which reduces GIDL at the same time.

3.2 Design improvement in the nanowire IH-JLTFET

It is necessary to optimize the proposed device performance by introducing more mole fraction x of aluminum in the channel side Al x Ga1−x As. Figure 7 illustrates the transfer curves for the proposed IH-JLTFETs with different Al composition (x) values at a given V DS = 1 V. It is explicit from the figure, as the Al fraction gets further, E G become larger and in sequence effectively suppressed ON-state tunneling current (I ON). From the I OFF and ambipolar behavior points of view, the I OFF current conductibility becomes a few lower and consequently limited ambipolar behavior substantially due to gate-induced drain leakage (GIDL) at the drain and channel junction. Figure 8 presents the extracted I ON, I OFF, SS and I ON /I OFF as a function of Al composition where mole fraction x = 0 of Aluminum corresponds to Ge–GaAs–Ge H-JLTFET. As shown in Fig. 8a, it is observed that both I ON and I OFF decrease as mole fraction x increases. These metrics are in trade-off relation, and higher I ON and lower I OFF cannot be obtained at the same time. Hence, it is necessary to put a weight on a narrowed number of parameters of interest in determining the Al fraction. Also, Fig. 8a reveals that the permissible x values required to meet HP application should be limited between 0 and 0.2 due to the reason that the upper limit of I ON (minimum I ON) is in Al mole fraction x = 20 %. The average subthreshold swing and the ON/OFF current ratio as a function of x are presented in Fig. 8b. It was already shown that the proposed IH-JLTFETs had better SS characteristics than other homo- and heterostructure JLTFETs in Figs. 5 and 6. The obtained SS values in Fig. 8b were below 25 mV/dec and reduced monotonically up to an Al composition of 0.25, where a local minimum was observed. Although the SS characteristics were significantly degraded at x = 0.4, it was still very low value. Since low SS and high I ON/I OFF are desirable for HP applications, altogether it can be seen from Fig. 8 that the value of x = 20 % is a suitable choice when I ON/I OFF and SS are 1.77 × 1011 and 12.6 mV/decade, respectively. It is observed that the proposed Ge–Al x Ga1−x As–Ge H-JLTFET with the variation of Al composition is well suited for HP logic technology. Also, x = 20 % can be good selection for I ON, I OFF, SS, I ON/I OFF point of view, simultaneously with remarkable simplicity in the fabrication progress.

4 Conclusion

In summary, we have examined a gate-all-around type I heterostructure junctionless TEFT (IH-JLTEFT) contingent upon Ge–Al x Ga1−x As–Ge heterostructure which has been designed and optimized in terms of Al fraction and its performance characteristics were explored using 2D numerical simulation. When mole fraction x of aluminum for active region Al x Ga1−x As was selected to be 0.2 as an optimum value, device metrics have reasonable value to meet HP logic requirements. For 40-nm active region, very low I OFF leakage current ~1.9 × 10−17, high ON/OFF current ratio (I ON/I OFF) about 1.77 × 1011 and steep subthreshold swing (SS) of order of 12.6 mV/decade at the V DS = 1 V are extracted. Due to these superior characteristics for ultra-scaled geometries within its compatibility with nanowire structure, Ge–Al x Ga1−x As–Ge H-JLTFET would be a promising candidate to complementary MOSFET technology.

References

A. Anwar, I. Hossain, A comparative numerical simulation of a nanoscaled body on insulator FinFET, in Proceedings of the 27th International Conference on Microelectronics (MIEL) (2010), pp. 16–19

R. Coquand et al. Strain-induced performance enhancement of tri-gate and omega-gate nanowire fets scaled down to 10 nm width, in IEEE Symposium on VLSI Technology Digest of Technical Papers (2012), pp. 13–14

J.Y. Song et al., Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans. Nanotechnol. 5(3), 186–191 (2006)

J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, R. Murphy, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N.D. Akhavan, P. Razavi, J.P. Colinge, Performance estimation of junctionless multigate transistors. Solid State Electron. 54(2), 97–103 (2010)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J. King Liu, Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Dev. Lett. 28, 743–745 (2007)

Qin Zhang, Wei Zhao, Alan Seabaugh, Low-subthreshold-swing tunnel transistors. IEEE Electron Dev. Lett. 27, 297–300 (2006)

O.M. Nayfeh, C.N. Chleirigh, J. Hennessy, L. Gomez, J.L. Hoyt, D.A. Antoniadis, Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Dev. Lett. 29, 1074–1077 (2008)

Y. Khatami, K. Banerjee, Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Electron Dev. Lett. 56, 2752–2761 (2009)

U. E. Avci, I. A. Young, Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9 nm gate-length, in Proceedings of the IEEE International Electron Device Meeting (IEDM), Washington, DC, USA (2013), pp. 4.3.1–4.3.4

M. Luisier, G. Klimeck, Performance comparisons of tunneling field-effect transistors made of InSb, Carbon, and GaSb–InAs broken gap heterostructures, in Proceedings of the IEEE International Electron Device Meeting (IEDM), Baltimore, MD, USA (2009), pp. 1–4

A.C. Seabaugh, Q. Zhang, Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

L. Knoll et al., Inverters with strained Si nanowire complementary tunnel field-effect transistors. IEEE Electron Dev. Lett. 34(6), 813–815 (2013)

K. Ganapathi, Y. Yoon, S. Salahuddin, Analysis of InAs vertical and lateral band-to-band tunneling transistors: leveraging vertical tunneling for improved performance. Appl. Phys. Lett. 97, 033504 (2010)

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energyefficient electronic switches. Nature 479(7373), 329–337 (2011)

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron Dev. Lett. 35(5), 584–586 (2013)

P.K. Asthana, B. Ghosh, S.B. Rahi et al., Improved performance of junctionless tunnel filed effect transistor with Si and SiGe hetro-structure for ultra low power application. RSC Adv. (2015). doi:10.1039/C5RA03301B

P.K. Asthana, High performance 20 nm GaSb/InAs junctionless fiels effect transistor for low power supply. J. Semicond. 36(2), 1–6 (2015)

B. Ghosh, P. Bal, P. Mondal, A junctionless tunnel field effect transistor with low subthreshold slope. J. Comput. Electron. (2013). doi:10.1007/s10825-013-0450-2

Y. Taur, T.H. Ning, Fundamentals of Modern VLSI Devices (Cambridge University Press, Cambridge, 1998)

R. Eisberg, R. Resnick, Quantum Physics of Atoms, Molecules, Solids, Nuclei and Particles, 2nd edn. (Wiley Student Edition, New York, 2012)

W. Long, H. Ou, J.M. Kuo et al., Dual-material gate (DMG) field effect transistor. IEEE Trans. Electron. Dev. 46(5), 865 (1999)

K.Y. Na, Y.S. Kim, Silicon complementary metal–oxide–semiconductor field-effect transistors with dual work function gate. Jpn. J. Appl. Phys. 45(12), 9033 (2006)

C.H. Wang, H. Chu, Y.S. Lai, et al., Dual work-function metal gates. US Patent, No. 73 81619B2, Jun. 3, 2008

U. Konig et al., N- and p-type Si–SiGe hetero FETs, in IEEE International Symposium on High Performance Electron Devices for Microwave and Optoelectronic Applications, vol. 8 (2000), pp. 1–7

B.M. Borg, K.A. Dick, B. Ganjipou et al., InAs/GaSb heterostructure nanowires for tunnel field-effect transistors. Nano Lett. 10(10), 4080 (2010)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron Dev. 54(7), 1725–1733 (2007)

Silvaco, Version 5.15.32.R. (2009). http://www.silvaco.com

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with High-κ gate dielectric. IEEE Trans. Electron Dev. 54(7), 1725–1733 (2007)

A. Villalon et al., First demonstration of strained SiGe nanowires TFETs with ION beyond 700 μA/μm, in Proceedings Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA (2014), pp. 66–67

W. Hansch, T. Vogelsang, R. Kirchner, M. Orlowski, Carrier transport near the Si/SiO2 interface of a MOSFET. Solid State Electron. 32(10), 839–849 (1989)

A. Schenk, A model for the field and temperature dependence of SRH lifetimes in silicon. Solid State Electron. 35(11), 1585–1596 (1992)

C. Wang, S.Y. Chou, Self-aligned fabrication of 10 nm wide asymmetric trenches for Si/SiGe heterojunction tunneling field effect transistors using nanoimprint lithography, shadow evaporation, and etching. J. Vac. Sci. Technol. B 27(6), 2790–2794 (2009)

O.M. Nayfeh, C.N. Chleirigh, J. Hennessy, L. Gomez, J.L. Hoyt, D.A. Antoniadis, Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Dev. Lett. 29(9), 1074–1077 (2008)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Molaei Imen Abadi, R., Sedigh Ziabari, S.A. Representation of type I heterostructure junctionless tunnel field effect transistor for high-performance logic application. Appl. Phys. A 122, 616 (2016). https://doi.org/10.1007/s00339-016-0151-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-016-0151-3