Abstract

An energy-efficient, low-noise, and high-speed dynamic comparator is proposed in this work. The comparator uses two pre-amplifiers to have a two-stage operation for reduced kickback noise. It also incorporates the adaptive current reuse (ACR) technique for reduced latency and high-speed operation. The proposed comparator is designed and simulated in a 65-nm UMC CMOS process using a 1.2-V power supply. The performance of the design is verified using post-layout simulation and also through Monte Carlo simulations. The resultant offset standard deviation of 8 mV is observed, which is 3 times less compared to the conventional design. The maximum operating frequency of the comparator is 1 GHz. The worst-case energy consumption is 67 fJ with an average latency of 70 ps. The kickback noise of 5.5 mV is observed for the entire working range, which is almost 10 times less compared to the conventional dynamic comparator at 500 MHz clock frequency.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The advancements in IoT technology have increased the requirements of the number of sensors, wherein each sensor requires the corresponding high-precision, high-speed, low-power, and low-noise readout circuit. In recent times, the focus of IoT-based systems is towards device portability, which requires the readout circuits to be designed with low power for improved battery life. The other major challenge being faced by IoT systems is the latency introduced by different sensors, which varies with temperature and voltage. Therefore, it becomes absolutely necessary to reduce the latency up to the tolerable limit.

Analog-to-digital converter (ADC) is the key component of all the readout circuits being used in application areas like communication receivers, CMOS image sensors, health care, and others. ADC converts the analogue output of sensors to digital form for further processing. Among various possible data converters, successive-approximation register (SAR) ADC is popular for low power as it requires a minimal number of analogue elements compared to other ADCs. SAR ADC inherently consists of a comparator, SAR register, and a digital-to-analogue converter (DAC). The power of SAR ADC is limited by the comparators.

In general, dynamic comparators are preferred over static comparators for high-speed and high-resolution applications. In the literature, various techniques to increase the speed and to reduce power consumption are reported. In the comparator design reported in [18], high speed is achieved by adding parallel paths to the output node. The two-stage dynamic comparator presented in [10] uses a pre-defined clocking pattern to reduce power consumption. The high-speed comparator with a transconductance-enhanced latching stage is reported in [19]. The latching stage uses separated gate-biasing cross-coupled transistors instead of a standard cross-coupled inverter structure. In [16], a current recycling approach is used for lower energy and high-speed applications. The comparator presented in [9] uses the concept of adaptive current-biasing technique to increase the speed of the comparator. In [15], high speed is achieved by directly connecting the pre-amplifier output to the regenerative latch, which reduces the effective capacitive load. In [5], high-speed and low-power consumption in a double-tail comparator are achieved by using a charge-steering approach. In [22], A comparator with a wide input range is reported by using a variable current source. The work reported in [8] implements a fully differential double-tail structure to improve the dynamic range. A wide input range comparator for LVDS receiver is presented in [12]. Moreover, [3, 4, 11] techniques are also reported to increase the energy efficiency of the dynamic comparators. In [6, 21] VCO-based comparators are reported, whereas in [13] inverter-based pre-amplifier comparator is proposed. In [2], dynamic bias pre-amplifier in which the nodes are partially discharged to save energy consumption at a cost of higher kickback noise. All the above-discussed techniques suffer from high kickback noise, which becomes more prominent at high frequency and scaled technology nodes.

The kickback noise is introduced due to coupling of large voltage variations or perturbations at the regenerative nodes through parasitic capacitances, to the comparator input, due to nonzero output impedance of the preceding circuit. In [14], kickback noise is reduced by providing a pre-amplifier before the latching stage; however, the technique is less effective during high-frequency operation. In [7], a neutralization technique with few sampling switches is used to reduce the kickback noise at the cost of speed and area. In [20], binary-weighted gate capacitance is used to reduce the kickback noise, which is very complex to design and also reduces the speed. In [23], three stages are used to enlarge the gain of the pre-amplifier, and in [17], two techniques are proposed and compared to reduce the kickback noise at a low frequency of operation. Moreover, a double-tail technique is also reported in [1] to mitigate the kickback noise at low-power consumption. In all the above-discussed techniques, the observed values of kickback noise are large, which affects the comparator decision. Hence, it is necessary to either reduce the amplitude of noise or to reduce the transient duration of kickback noise in order to improve the design accuracy and resolution.

In this work, a low-latency, low-noise, and energy-efficient comparator are proposed. The comparator consists of three stages, wherein the first two stages are used to reduce the effect of kickback noise. Further, an adaptive current recycling (ACR) technique through a P-type pre-amplifier is used to provide additional strength to PMOS pairs of the regenerative latch. Both the conventional and proposed comparator are designed and simulated in a 65-nm CMOS process using a 1.2-V power supply at 500 MHz operating frequency. The rest of the paper is organized as follows: section II discusses the proposed comparator. Section III presents the simulation results, and also compares the performance of the proposed comparator with state-of-the-art, and section IV discusses input-referred noise. The conclusion and future scope of the work are discussed in section IV.

2 Proposed Comparator

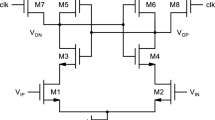

A comparator circuit mainly consists of a pre-amplifier and a regenerative latch. As an example, a conventional comparator with a pre-amplifier formed by transistors MN0–MN2, MP0–MP1, and a regenerative latch formed by transistors MP2–MP6, MN3–MN6 is shown in Fig. 1. The input voltage is applied to the transistors MN0–MN1, and the output of preamplifier (Vc outn+, Vc outn−) is directly coupled to the input of the latch through transistors MP2–MP3. During the rising edge of CLK, output nodes of the pre-amplifier are reset to V DD, and the output nodes of latch (Vc outn+, Vc outn) are reset to GND. During the falling edge of CLK or in the decision-making phase, the parasitic capacitance at the output nodes of pre-amplifier starts discharging at a different rate, which is sensed by the latch through transistors MP2–MP3. The positive feedback formed by MP5–MP6, MN3–MN4 results in high-voltage swing. Compared to the conventional design, the proposed dynamic comparator core consists of N-type pre-amplifier (PA1), P-type pre-amplifier (PA2), regenerative latch (RL), and an adaptive current recycling (ACR) technique (highlighted in the grey shade) as shown in Fig. 2. In addition to conventional design, the PA2 is formed by transistors MN3–MN4 and MP6–MP8, whereas MP2–MP5 and MP9–MP12 used to implement the ACR technique. The W/L ratio of all the devices are listed in the Table 1.

The operation of the proposed dynamic comparator is explained in two phases: the reset phase and the decision-making/regenerative phase. During the rising edge of CLK or falling edge of CLKb, outputs of PA1 (Voutn+,Voutn−) and PA2 (Voutp+, Voutp−) are reset to V DD and GND, respectively. In the same phase, the regenerative nodes of RL (Vout+, Vout−) are reset to GND using MN5 and MN10 by discharging any unwanted accumulated charge. During the falling edge or in the decision-making phase, the parasitic capacitance on the output nodes of the PA1 start discharging with different rates through the tail transistors MN2, which is determined by appliedinput voltage (Vin+, Vin−). The outputs of PA1 are fed to the input of PA2 and the instance when (Voutn+, Voutn−) discharge to the minimum threshold requirement of MP7/MP8, the PA2 turns on and output nodes of PA2 (Voutp+, Voutp−) start charging towards VDD with a different rate. The difference in the charging rate of parasitic capacitance at the output node of PA2 is sensed by the input transistors MN8–MN9 of RL. The sensed difference in voltage is amplified by the positive feedback of RL formed by transistors MN6–MN7 and MP14–MP15 to achieve rail-to-rail voltage swing. One of the major advantages of using two pre-amplifiers is to increase the effective parasitic capacitances between the regenerative nodes and pre-amplifier inputs to suppress the kickback noise. It can be seen from the circuit operation that the decision by the latch is being made during the later part of CLKb (edge) when the second preamplifier is turned ON, which reduces the overall kickback noise of the comparator. The increase in coupling capacitance between the output nodes (Vout+, Vout), and the input of comparator (Vin+, Vin) affects the comparator speed. To compensate for the degradation of speed, an adaptive current recycle technique is implemented in this work. There are three control signals: CLK and CLKb are complementary and CLKbNEW is synchronized with the edges of the CLK with a duty cycle of 90% with respect to CLK as shown in the Fig. 2 used to implement the technique.

2.1 ACR Technique

In order to match the driving strength of PMOS devices of RL with NMOS devices, the proposed comparator uses the ACR technique highlighted in Fig. 2 with grey colour. In the ACR technique, the current from the PA2 is copied and reused in the regenerative nodes of RL during the falling edge of CLKb for a faster decision compared to the conventional comparator. To copy the current, two P-type dynamic current mirrors are implemented to maintain the same source potential, which is labelled as PSW+, PSW− using transistor MP3–MP9 and MP5–MP11, respectively, as shown in Fig. 2. Moreover, four switches labelled as MP2–MP4, and MP10–MP12 are used to synchronize the operation in the decision-making phase only, which are controlled by the signal CLKbNEW. In the decision-making phase, the parasitic capacitance at the output nodes of PA2 (Voutp+, Voutp−) is charged towards V DD at a different rate, wherein the rate of charge of capacitors depends on the applied input difference. The resulting current flowing through these capacitances is (Icopy+), (Icopy), and acts as a current source for both the current mirrors. This current is reused in the RL by applying it to the drain terminal of transistors MP14, MP15 by the switches MP10, MP12. Simulations are performed to find out the region where the transistors are in saturation region for the entire range of the comparator, and based on the observation, the duty cycle of the control signal CLKbNEW is decided, which operates all four switches, ensuring the current reuse.

3 Simulation Results and Analysis

The conventional as well as the proposed comparator is designed and simulated in 65 nm CMOS process using 1.2-V power supply, which is shown in Figs. 1 and 2. Both the comparator operates at a clock frequency of 500 MHz, and the maximum operating frequency of 1 GHz can be achieved. The layout of the proposed comparator is shown in Fig. 3, and it occupies an area of 20 µm 8 µm. To check the robustness of the proposed comparator, different post-layout simulations are performed including transient, Monte Carlo, and corner analysis as discussed in the below subsections.

3.1 Transient Analysis

The transient analysis of the comparator is shown in Fig. 4, wherein a ramp signal varying in the input range of 500 mV to 1.2 V and step size of 1 mV, is applied to the one input, say Vin− of the comparator and a fixed DC signal of 801 mV is applied to the other input, Vin+. The plot is shown with a double Y-axis, wherein the output signals (Vout+, Vout−) and CLKb are plotted with respect to the left Y-axis, and the input signals (Vin+, Vin−) are plotted with respect to right Y-axis. The switching of comparator output can be shown in Fig. 4. The region representing comparator switching is zoomed in and shown as an inset graph. The switching in output voltages is observed at 0.802 V in the duration of 4.52 ns and 4.55 ns. The proposed comparator, therefore, has a resolution of 1 mV and latency of 30 ps.

3.2 Effect of Process Corners, Temperature, and Supply Voltage on Comparator Latency

The variation in comparator latency as a function of different corners including process, supply voltage, and temperature is analyzed to check the design’s robustness. It is observed from Fig. 5 that for the entire input range, the latency of the proposed comparator for different process corners is within 70 ps. It is noted that the maximum variation in the latency is observed in the slowN and slowP (SS) corner as the threshold voltage of the devices is increased. Similarly, the effect of variations in supply voltage on latency for different process corners is observed as shown in Fig 6. It is observed that the worst-case latency is 81 ps below 1 V power supply at SS corner. The latency is decreased with an increase in the input voltage range due to an increase in the driving strength of the device. Further, the effect of varying temperature at different supply voltages on latency is analyzed in Fig. 7 and the latency of the comparator is varied from -5% to 12% with respect to the room temperature. All these simulations are performed for a fixed test bench wherein Vin− is applied with a ramp signal covering the comparator input range and other input is fixed at 600 mV.

3.3 Input-Referred Noise

The input-referred noise of the comparator is a summation of flicker noise and thermal noise introduced due to device components. Flicker noise is mainly dominated at low frequencies, whereas thermal noise is introduced due to change in the operating region of the devices. To estimate the total input-referred noise, noise analysis is performed both for conventional and proposed comparator. The observed noise over a bandwidth of 2 GHz for the conventional comparator is found to be 3.2 µV, whereas, for the proposed design, it is 5 µV as shown in Fig. 8.

3.4 Kickback Noise Analysis

The equivalent model for evaluating kickback noise is shown in Fig. 9, wherein the Thevenin equivalent of the preceding circuit is modelled with an output resistance of 1 kΩ. The input signal with a difference of 1 mV(∆Vin) is applied and the variations in the regenerating nodes coupled back to the comparator input are observed. In Fig. 10, the input signals are plotted with respect to the left y-axis (green colour), and the clock, as well as output signals, are plotted with respect to the right y-axis (purple colour). For better visualization, an inset representing the reduced effect of kickback noise at the comparator inputs is also shown. It is observed that when the CLKb is making a transition from low to high state, at the first half of the edge, the effect of kickback noise is prominent on the input signal Vin+ and Vin with a maximum error of 40 mV. However, during this period, latch is still in off condition as output of the second stage (Voutp+, Voutp−) is still at ground potential making MN8–MN9 in cutoff state. When the rate of discharge with respect to the input difference of the first stage (Voutn+, Voutn−) is enough to maintain the minimum threshold voltage requirements of the second stage, the outputs of PA2 (Voutp+, Voutp−) start charging at a different rate compared to the outputs of the first stage. As the RL becomes active based on the signals received from PA2, the additional delay introduced due to PA2 helped in reducing the effect of kickback noise from the regenerative nodes to the PA1 or comparator input. It can also be shown in Fig. 10 that the RL turns ON during the latter half of the falling edge of CLK and at the same time the differential inputs Vin+ and Vin are less affected by the kickback noise, and the peak error is reduced from 40 mV to 3 mV (with pre-layout simulations). The inset is also added to show a reduction in kickback noise with more clarity. In Fig. 11, kickback noise is evaluated considering post-layout simulations for the entire input range of the comparator. The worst-case noise of 5.5 mV is observed at 1.2 V power supply for post-layout design. However, the same analysis when performed for conventional comparator results in a worst-case noise of 55 mV. Therefore, the proposed design reduces the worst-case kickback noise by a factor of 10 compared to the conventionally designed comparator. As kickback noise is a frequency-dependent parameter, the noise is plotted for a different set of frequencies as shown in Fig. 12. It is known that the kickback noise increases with frequency, an increment in noise by approximately 5 times is observed for the wide input frequency range. However, the observed kickback noise is low compared to the comparators designed for 500 MHz–1 GHz operating frequency range [16, 18] due to the two-stage operation of pre-amplifiers.

3.5 Monte Carlo Analysis

The Monte-Carlo simulations are performed to analyze the effect of process and device mismatch in the proposed comparator. The simulations are performed for 200 samples keeping one input signal fixed to 600 mV and the other input is a ramp signal. The histogram shown in Fig. 13 represents the offset voltage of 8 mV. Further, the variations in offset for the entire working range of the comparator are also observed and the results are plotted in Fig. 14. It is seen that offset voltage increases with an increase in input voltage and worst case offset is 10 mV for an input voltage of 1.2 V.

As discussed earlier, the proposed comparator implements an additional ACR technique for high speed. Therefore, it becomes apparent to estimate total energy consumed by the proposed comparator. The total energy consumed by the comparator for different operating frequencies is evaluated and plotted in Fig. 15. It can be seen that at the operating frequency of 500 MHz, the energy consumed by the comparator is 67 fJ, which gets reduced to 30 fJ at 1 GHz operating frequency.

The performance of the proposed comparator is compared with the state-of-the-art as shown in Table 2. Compared to [17], the proposed design has almost 1.5 times less kickback noise and energy consumption per conversion cycle compared to [7]. On comparing with the work mentioning the similar technology node of 65 nm [18], it is observed that the proposed design reduces the kickback noise by 35 times and energy by 1.2 times making the proposed comparator suitable for low noise and energy-efficient applications.

4 Conclusion and Future Scope

An energy-efficient, low-noise, and high-speed dynamic comparator is presented in this paper. The proposed comparator uses two pre-amplifiers having N-type and P-type input pairs for the two-stage operation to reduce the effect of kickback noise. It further incorporates an adaptive current reuse technique to increase the driving strength of the pull-up network of the regenerative latch, which ensures low latency for the entire working range. The comparator is designed in UMC 65 nm CMOS technology using a 1.2-V power supply. The performance of the comparator is observed for post-layout simulations. It operates at 500 MHz frequency and can reach the maximum operating frequency of 1 GHz. The proposed comparator occupies an area of 20 µm–8 µm and consumes 67 fJ of energy at 500 MHz. The average latency of the comparator is 70 ps throughout the input range, and the input-referred noise is 2 mV at 1 GHz frequency. The worst-case kickback noise for the entire working range is 5.5 mV, which is verified through simulations, and it is 10 times less compared to the conventionally designed comparator. The future work includes the integration of the designed comparator into SAR ADC followed by design tape-out.

References

S. Babayan-Mashhadi, R. Lotfi, Analysis and design of a low- voltage low-power double-tail comparator. IEEE Transact. Very Large Scale Integrat. (VLSI) Syst. 22(2), 343–352 (2014)

H.S. Bindra, C.E. Lokin, D. Schinkel, A. Annema, B. Nauta, A 1.2- V dynamic bias latch-type comparator in 6.5-nm CMOS With 0.4-mV input noise. IEEE J Solid-State Circuits 53(7), 1902–1912 (2018)

H. S. Bindra, C. E. Lokin, A. -J. Annema and B. Nauta, A 30fJ/compar- ison dynamic bias comparator, in: ESSCIRC 2017—43rd IEEE European Solid State Circuits Conference, (Leuven, Belgium, 2017), pp. 71–74. https://doi.org/10.1109/ESSCIRC.2017.8094528.

S. Chevella, D. O’Hare, I. O’Connell, A low-power 1-V supply dynamic comparator. IEEE Solid-State Circuits Letters 3, 154–157 (2020). https://doi.org/10.1109/LSSC.2020.3009437

S.A. El-Sayed, G.A. Fahmy, A.I. Hussein and F.A. .E. Al Geldawy, A low-power dual-mode sigma-delta modulator using charge-steering opamps, in: 2016 33rd National Radio Science Conference (NRSC), (Aswan, 2016), pp. 415-420, https://doi.org/10.1109/NRSC.2016.7450856

M. Esmaeilzadeh, Y. Audet, M. Ali, M. Sawan, A Low-offset VCO- based time-domain comparator using a phase frequency detector with reduced dead and blind Zones. IEEE Trans. Circuits Syst. I Regul. Pap. 70(3), 1017–1029 (2023). https://doi.org/10.1109/TCSI.2022.3227802

P.M. Figueiredo, J.C. Vital, Kickback noise reduction techniques for CMOS latched comparators. IEEE Trans. Circuits Syst. II Express Briefs 53(7), 541–545 (2006). https://doi.org/10.1109/TCSII.2006.875308

P.P. Gandhi and N.M. Devashrayee, Differential double tail dynamic CMOS voltage comparator, in: 2017 International Conference on Intelligent Communication and Computational Techniques (ICCT), (Jaipur, India, 2017), pp. 8–11.https://doi.org/10.1109/INTELCCT.2017.8324011.

A. Kaur and M. Sarkar, A low power low latency comparator for ramp ADC in CMOS imagers, in: 2016 IEEE International Symposium on Circuits and Systems (ISCAS), (Montreal, QC, Canada, 2016), pp. 1466-1469, https://doi.org/10.1109/ISCAS.2016.7527534

A Khorami, M.B Dastjerdi and A.F Ahmadi, A low-power high-speed comparator for analog to digital converters, In: 2016 IEEE International Symposium on Circuits and Systems (ISCAS), (Montreal, QC, Canada, 2016), pp. 2010-2013, doi: https://doi.org/10.1109/ISCAS.2016.7538971

A. Khorami, M. Sharifkhani, A low-power high-speed comparator for precise applications. IEEE Transact. Very Large Scale Integrat (VLSI) Syst. 26(10), 2038–2049 (2018)

K.-M. Kim, S. Hwang, J. Song, C. Kim, An 112-Gb/s LVDS receiver with a wide input range comparator. IEEE Transact. Very Large Scale Integrat. (VLSI) Syst. 22(10), 2156–2163 (2014)

L. Qiu, T. Meng, B. Yao, Z. Du, X. Yuan, A high-speed low- noise comparator with auxiliary-inverter-based common mode-self- regulation for low-supply-voltage SAR ADCs. IEEE Transact. Very Large Scale Integrat. (VLSI) Syst. 31(1), 152–156 (2023)

B. Razavi, B.A. Wooley, Design techniques for high-speed, high- resolution comparators. IEEE J. Solid-State Circuits 27(12), 1916–1926 (1992). https://doi.org/10.1109/4.173122

A. Rezapour, H. Shamsi, H. Abbasizadeh and K. -Y. Lee, ”Low power high speed dynamic comparator,in: 2018 IEEE International Symposium on Circuits and Systems (ISCAS), (Florence, Italy, 2018), pp. 1-5, https://doi.org/10.1109/ISCAS.2018.8351548

B. Satapathy and A. Kaur, a high speed, low energy comparator based on current recycling approach, in: 2021 IEEE International Sym- posium on Circuits and Systems (ISCAS), (Daegu, Korea, 2021), pp. 1-5, https://doi.org/10.1109/ISCAS51556.2021.9401086

B. Satapathy and A. Kaur, A low kickback noise and low power dynamic comparator,in: 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), (Lansing, MI, USA, 2021), pp. 146-149, https://doi.org/10.1109/MWSCAS47672.2021.9531668

R.K. Siddharth, Y. Jaya Satyanarayana, Y.B. Nithin Kumar, M.H. Vasantha, E. Bonizzoni, A 1-V, 3-GHz strong-arm latch voltage comparator for high speed applications. IEEE Transact on Circuits and systems II: express briefs 67(12), 2918–2922 (2020)

Y. Wang, M. Yao, B. Guo, Z. Wu, W. Fan, J.J. Liou, A Low-power high-speed dynamic comparator with a transconductance-enhanced latching stage. IEEE Access 7, 93396–93403 (2019). https://doi.org/10.1109/ACCESS.2019.2927514

S.-H. Wang, C.-C. Hung, A 0.3V 10b 3MS/s SAR ADC With comparator calibration and kickback noise reduction for biomedical applications. IEEE Transact. Biomed. Circuits Syst. 14(3), 558–569 (2020)

K. Yoshioka, VCO-based comparator: a fully adaptive noise scaling comparator for high-precision and low-power SAR ADCs”. IEEE Transact. Very Large Scale Integrat. (VLSI) Syst. 29, 2143–2152 (2021)

K. Yoshioka, A. Shikata, R. Sekimoto, T. Kuroda and H. Ishikuro, ”An 8bit 0.35–0.8V 0.5–30MS/s 2bit/step SAR ADC with wide range threshold configuring comparator,in: 2012 Proceedings of the ESSCIRC (ESSCIRC), (Bordeaux, France, 2012), pp. 381-384, https://doi.org/10.1109/ESS- CIRC.2012.6341365.

H. Zhuang, W. Cao, X. Peng, H. Tang, A three-stage comparator and its modified version with fast speed and low Kickback. IEEE Transact.Very Large Scale Integrat. (VLSI) Syst. 29(7), 1485–1489 (2021)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Satapathy, B., Kaur, A. An Energy-efficient and High-speed Dynamic Comparator for Low-noise Applications. Circuits Syst Signal Process 42, 5108–5120 (2023). https://doi.org/10.1007/s00034-023-02375-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02375-6