Abstract

Quantum dot Cellular Automata (QCA) has more popularity in the near market due to its advantages over CMOS technology such as high device density, low power consumption and high computing efficiency. The major concern in circuits is to achieve improvement in QCA parameters like number of QCA Cells, cells area, total area, delay, energy consumption and single or multilayer layout. In this paper we will discuss about various techniques or methodologies to achieve improvement in these parameters. Different methodologies need to be designed to have optimization, automation and verifications in design. These techniques are primarily based on Logic synthesis, layers, clocking in QCA, feedback in QCA, QCA cell arrangements, use of tools to design the circuits, use of 3 × 3 or 5 × 5 QCA tiles etc. In today’s era, less energy consumption is also a very important parameter. The main objective of this paper is to get the details of these techniques to improve the parameters. QCADesigner 2.0.3 and QCADesigner–E software are used to get the implementations in QCA field.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

- QCA (quantum dot cellular automata)

- SRAM (static random access memory)

- MV (majority voter)

- 5-input majority gate (MV5)

- PPDD (priority-phased decomposition-driven)

- CLA (carry look-ahead adder)

1 Introduction

International Technology Roadmap for Semiconductors (ITRS) [1] has devised Nano devices like Carbon nanotube transistors (CNT), Single Electron Transistors (SET), Resonant Tunnelling devices (RTD), Quantum dot Cellular Automata (QCA) etc. as shown in Fig. 1. These are used to overcome the limitations of CMOS devices scaling. QCA is the best nanotechnology device among all these Nano devices.

Nano devices [1]

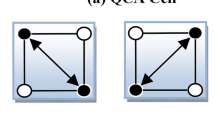

QCA is efficient, has very high device density and low power consumption. It is transistor less and can operate at Terahertz (THz) range. CMOS technology works on current switching whereas QCA represent binary information on the cells.

QCA is now used to design digital circuits in almost all the fields. Researchers have designed the circuits with different methodologies in QCA. In this paper, these different methodologies are discussed with their method and achievements in terms of various parameters.

In the remainder of this work, in Sect. 2, earlier reported work on QCA methodology is reviewed and compared. Section 3 shows the implementations of different methodologies for different circuits. This paper is one umbrella under which different methods are compared and analyzed. In Sect. 4, the work is concluded.

2 Methodologies

Till now, researchers have proposed different ways to design digital circuits to achieve optimization in terms of circuit area, number of cells, speed and complexity. In this section, these different methodologies are studied, analyzed and compared with standard parameters of interest. Various methodologies used are coplanar, multilayer, novel input technique, Bottom up design approach with special cell arrangements, keeping fixed input cells, inter cellular effect technique, PPDD technique, using 3 input standard MV gate and 5 input MV gate, using only one type of cell, tile based, models based, with simplified Boolean expressions, using different clocking etc. Circuits like NOT gate, XOR gate, the one used in building almost all the complex circuits, multiplexer, full adder, parity generator, latch, RAM etc. are implemented with these methodologies. Tables 1, 2 and 3 shows the comparison of all methods with respect to parameters and circuits implemented.

Comparative table for the methodologies shows that cell interaction or intercellular effect technique is the best to implement XOR gate and parity generator (4 bit, 8 bit, 16 bit and 32 bit) with low power consumption, less number of cells, less area and increased speed. Novel input technique is the best way to implement 2:1 multiplexer. Many implementations are seen for full adder but using MV5 is the best method with least cells, area and delay as indicated in Table 4.

3 Implementations

This section shows the implementations of best methodologies for various circuits. QCADesigner tool is used to build the layout of various circuits and to observe the simulation result. Cell interaction method is the best method as per as cell area is concerned. Table 1 clearly indicates that, with the other methodologies the parametric values are high for XOR gate. As a case study the XOR gate implementation with other best methods is as shown in Fig. 2a–c.

Graphical representation indicates that cell interaction or intercellular effect technique [6] is the best methodology among the all as it shows the optimization in all the parameters with respect to the other methodologies. This methodology can build all other circuits using this XOR gate with best optimization. Cell count is indicated in Fig. 3, device density in Fig. 4 and delay in Fig. 5 for all methodologies considered here for different circuits.

4 Conclusion

Optimizing key metrics like delay, cell count and cell area will help improving logic computation and information flow at the physical level implementation. Although QCA logic components can be designed with QCA gates, extra delays will be introduced, which can lead to incorrect timing relationships. These timing issues present difficulties for interconnection and feedback which can affect the performance of QCA circuits. Therefore, assigning correct and efficient clocking zones to circuits is a major challenge in QCA circuit design. These all issues lead to design an efficient methodology to optimize all the parameters especially density, speed and less power consumption.

References

Sasamal TN, Singh AK, Mohan A (2020) Quantum dot cellular automata based digital logic circuits: a design perspective. ISSN 1860-949X, ISSN 1860-9503 (electronic) studies in computational intelligence. ISBN 978-981-15-1822-5, ISBN 978-981-15-1823-2 (eBook). Springer Nature Singapore Pte Ltd. https://doi.org/10.1007/978-981-15-1823-2

Singh R, Sharma DK (2020) Design of efficient multilayer RAM cell in QCA framework, circuit world © Emerald Publishing Limited [ISSN 0305-6120]. https://doi.org/10.1108/CW-10-2019-0138. Accepted 2 Apr 2020

Raj M, Kumaresan RS, Gopalakrishnan L (2019) Optimized multiplexer and Xor gate in 4-dot 2 electron QCA using novel input technique. In: 10th ICCCNT 2019 July 6–8, 2019. IEEE, IIT—Kanpur, Kanpur, India

Hashemi S, Farazkish R, Navi K (2013) New quantum dot cellular automata cell arrangements. J Comput Theor Nanosci 10:798–809. https://doi.org/10.1166/jctn.2013.2773

Khosroshahy MB, Moaiyeri MH, Angizi S, Bagherzadeh N, Navi K (2017) Quantum-dot cellular automata circuits with reduced external fixed inputs, microprocessors and microsystems.https://doi.org/10.1016/j.micpro.2017.03.009

Chen H, Lv H, Zhang Z, Cheng X, Xie G (2019) Design and analysis of a novel low-power exclusive-OR gate based on quantum-dot cellular automata. J Circ Syst Comput 28(8):1950141. https://doi.org/10.1142/S021812661950141X

Sheikhfaal S. A QCA layout design methodology. Part I

Waje MG, Dakhole PK (2016) Analysis of various approaches used for the implementation of QCA based full adder circuit. In: International conference on electrical, electronics, and optimization techniques (ICEEOT), 978-1-4673-9939-5/16/$31.00 ©2016. IEEE

Abdullah-Al-Shafi M, Shariful Islam M, Bahar AN (2020) 5-input majority gate based optimized full adder circuit in nanoscale coplanar quantum-dot cellular automata. Int Nano Lett https://doi.org/10.1007/s40089-020-00304-y

Sardinha LHB, Orlandi VB, Neto OPV, Campos SVA (2017) Simplified model for automatic QCA circuitry verification, SBCCI 2017. 2017 Association for Computing Machinery, ACM ISBN 978-1-4503-5106-5/17/08. https://doi.org/10.1145/3109984.3110011

Angizi S, Alkaldy E, Bagherzadeh N, Navi K (2014) Novel robust single layer wire crossing approach for exclusive OR sum of products logic design with quantum-dot cellular automata. J Low Power Electron 10:259–271. https://doi.org/10.1166/jolpe.2014.1320

Huang J, Momenzadeh M, Schiano L, Lombardi F (2005) Simulation based design of modular QCA circuits. In: 5th IEEE conference on in nanotechnology, pp 533–536

Zhang R, Walus K, Wang W, Julien GA (2004) A method of majority voter reduction for QCA. IEEE Trans Nanotechnol 3(4):443–450

Tougaw PD, Lent CS (1994) Logical devices implemented using quantum cellular automata. J Appl Phys 75:1818–1825

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Repe, M.R., Waje, M. (2022). Evaluation of Digital Circuit Methodologies in Nanotechnology Using QCA - Quantum Dot Cellular Automata. In: Kumar, A., Mozar, S. (eds) ICCCE 2021. Lecture Notes in Electrical Engineering, vol 828. Springer, Singapore. https://doi.org/10.1007/978-981-16-7985-8_61

Download citation

DOI: https://doi.org/10.1007/978-981-16-7985-8_61

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-7984-1

Online ISBN: 978-981-16-7985-8

eBook Packages: EngineeringEngineering (R0)