Abstract

Bandgap Reference (BGR) circuit plays a vital role in analog and digital circuit design. BGRs provide temperature-insensitive reference voltages subject to silicon bandgap (1.2 eV). Implementation of BGR circuit zero temperature coefficient (TC) by using P–N diodes and making temperature independent by combining proportional to absolute temperature (PTAT) and complimentary to absolute temperature (CTAT) voltages. PTAT generation and start-up circuits are the two basic elements of BGR to anticipate in nano-watt applications. Start-up circuit requires for PTAT to avoid undesirable zero bias condition. The start-up circuit consists a potential divider with resistors between supply rails. The DC current flows through a resistance path which is larger than leakage current to make the start-up circuit in stable operation. This work proposes bandgap reference circuit with PTAT generation by avoiding the need of start-up circuit and assumption made for PTAT as strong forward bias. This simulation is carried with cadence environment in UMC 180 nm technology. This proposed work results show low temperature coefficient, high accuracy in output voltage, and temperature is varied from −20 to 200 ppm/°C with 1.8 V supply voltage.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

A reference is mandatory for integrated circuit (IC)-based analog and digital signal processing applications, and it may be either a voltage, current, or time. The reference creates a node which is stable that can be used by other subcircuits to produce expected and fair results. Fundamentally, the reference point should be constant as per operating conditions such as variations in supply voltage, temperature, and loading transients. These reference circuits are basically required in design of subsystems like data converters (ADCs and DACs), voltage converters (DC–DC, AC–DC), operational amplifiers, and linear voltage regulators. The reference conduction is measured by its variation and is narrated by its functional conditions. The reference specifications are line regulation, temperature drift, flow of bias current, input supply voltage range, and load conditions. The steady state changes in supply voltage and temperature which gives variations in reference voltage can be correlated with line regulation and temperature drift. The temperature coefficient (TC) is a metric for variations over temperature [1]. As a rule, TC is formulated in parts per million per degree Celsius (ppm/°C) [2].

Conventionally, voltage across the diode is taken as \( V_{\text{CTAT}} \) and the difference of two \( V_{\text{CTAT}} \)s provide the \( V_{\text{PTAT}} \). The BJT transistor with \( V_{\text{BE}} \) or P–N junction diode with forward bias condition exhibits a negative temperature coefficient (NTC).

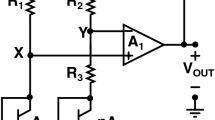

If two bipolar transistors as shown in Fig. 1 operate at unequal current densities, then the difference between base-emitter voltages is directly proportional to absolute temperature.

Basic bandgap reference is shown in Fig. 2; output voltage is given by

for n = 31 and taking ratio of \( R_{2} \), \( R_{3} \) = 4 assume resistors are temperature independent.

2 Related Works

Wan et al. [3] proposed a low-voltage second-order high-precision CMOS bandgap reference circuit. The achieved results are 2.5 ppm/°C, supply rejection of −53 dB, line regulation of 0.23 mV/V with 1 V supply voltage. Ji et al. [4] proposed a ultra-low-power BGR suitable for the future IoT applications. This ULP BGR is simulated in 0.18 μm technology and shows results of voltage and current reference generation values of 1.238 V and 6.64 nA. The temperature coefficients are 26, 283 ppm/°C, respectively. Quan et al. [5] implemented a low voltage and high PSRR BGR with Brokaw topology which is adopted for low output voltage. Wang et al. [6] proposed a PTAT with a current compensation method. In this work, emitter area ratios of differential pair npn transistors are used to produce a current which is proportional to PTAT. Hu et al. [7] presented a high-performance CMOS BGR which adopted a current mode architecture for low-voltage applications. Brokaw architecture is employed in portion of circuit, in which a three-stage opamp is selected to avail high PSRR. First-order temperature compensation method is employed to have low TC. Saidulu and Manoharan [8] presented a CMOS amplifier with high gain using a low-power methodology. This high gain amplifier helps to improve precision in BGR circuits in the place of error amplifier. Yi and Laleh [9] presented a new temperature coefficient compensation technique for Si–Ge reference circuits. This work employed two-step temperature compensation technique for the cancellation of major nonlinear temperature-dependent terms. This compensation technique provides an output voltage proportional to difference of bandgap voltages Si and Si–Ge.

3 Proposed Bandgap Reference

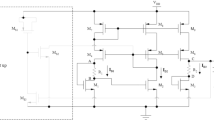

Analysis of bandgap references noted the currents in the bipolar junction transistors are proportional to the absolute temperature. PTAT is directly proportional to the diode voltage. The current in the diode is varied exponentially from fA to nA range as temperature changes. This PTAT voltage generated by small amount of current in a circuit at low temperature can be dominated by unwanted leakage current from gate to be connected to the PTAT node. The dependence of leakage current on temperature is very less. MOS-based \( V_{\text{PTAT}} \) generation is shown in Fig. 3.

Implementation of P–N diode, considered a npn bipolar junction transistor with twin-well technology is placed on the resistors which provide \( V_{\text{CTAT}} \) voltage is shown in Fig. 4.

The schematic of proposed bandgap reference (BGR) is shown in Fig. 5. This BGR has three stages which are \( V_{\text{PTAT}} \), error amplifier stage, and \( V_{\text{CTAT}} \) stage. The opamp sense the voltage at nodes of \( V_{\text{PTAT}} \) and node at voltage division between \( R_{1} \), \( R_{2} \) and fed to the PMOS transistor in the \( V_{\text{CTAT}} \) generation stage. This PMOS device draws the current from \( V_{\text{DD}} \) which is proportional to the error voltage fed by the opamp. This current passes through the resistors, provides the \( V_{\text{PTAT}} \) voltage. This error amplifier has NMOS differential pair input stage, and second stage is source follower-based level sifter to receive low \( V_{\text{PTAT}} \). The current consumption in the opamp is less than 1 nA at room temperature. The temperature dependency can be eliminated by adjusting the ratio of resistors (\( R_{1} \), \( R_{2} \)), and the reference voltage is derived as

If temperature is increased by \( \Delta T \), then

Select proper R values to remove the effect of \( \Delta \) T

4 Results

V OUT | Temp range (°C) | Power consumption | |

|---|---|---|---|

[10] | 1.176 | −10 to 110 | 28.7 nW |

This work | 1.695 | −20 to 120 | 151.8 μW |

5 Conclusion

The proposed bandgap reference circuit is implemented in UMC 180 nm technology. The temperature that is swept from −20 to 200 °C is shown in Figs. 6 and 7 for variation in reference voltage, current, respectively. This BGR circuit achieves high accuracy in output voltage with the cost of 151.8 μW power consumption, with \( V_{\text{DD}} \) of 1.8 V at room temperature while compared to similar state of the art of BGR circuit.

References

G.A. Rincon-Mora, Voltage references (Wiley-Inter science, London, 2002)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York, 2001)

M. Wan, Z. Zhang, K. Dai, X. Zou, A 1-V 2.5-ppm/°C second-order compensated bandgap reference, in ASIC (ASICON), 2015 IEEE 11th International Conference on IEEE, 2015, pp. 1–4

Y. Ji, C. Jeon, H. Son, B. Kim, H.-J. Park, J.-Y. Sim, 5.8 A 9.3 nW all-in-one bandgap voltage and current reference circuit. in Solid-State Circuits Conference (ISSCC), 2017 IEEE International, IEEE, 2017, pp. 100–101

L. Quan, Y. Yin, X. Yang, H. Deng, Design of a high precision band-gap reference with piecewise-linear compensation. in Anti-Counterfeiting, Security and Identification (ASID), 2012 International Conference on IEEE, 2012, pp. 1–5

S. Wang, S. Wang, A bandgap reference circuit with temperature compensation. in Microwave and Millimeter Wave Technology (ICMMT), 2016 IEEE International Conference on IEEE, 2016, vol. 1, pp. 111–113

J. Hu, Y. Yin, H. Deng, Design of a high-performance brokaw band-gap reference. in Anti-Counterfeiting Security and Identification in Communication (ASID), 2010 International Conference on IEEE, 2010, pp. 126–129

B. Saidulu, A. Manoharan, Design of low power amplifier for neural recording applications using inversion coefficient methodology. Int. J. Control Theory Appl. 10(6), 719–727 (2017)

H. Yi, N. Laleh, A precision SiGe reference circuit utilizing si and SiGe bandgap voltage differences. IEEE Trans. Electr. Dev. 64(2), 392–399 (2017)

J.M. Lee, Y. Ji, S. Choi, Y. Cho, S. Jang, J.S. Choi, B. Kim, H. Park, J. Sim, A 29 nW bandgap reference circuit, in Proceedings IEEE International Solid-State Circuits Conference 2015, pp. 100–102

Acknowledgements

The authors are grateful for the support of UGC (Government of India) and Research Groups, VLSI Laboratory, VIT University, India.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Saidulu, B., Manoharan, A., Bhavani, B., Sk, J.B. (2018). An Improved CMOS Voltage Bandgap Reference Circuit. In: Dash, S., Naidu, P., Bayindir, R., Das, S. (eds) Artificial Intelligence and Evolutionary Computations in Engineering Systems. Advances in Intelligent Systems and Computing, vol 668. Springer, Singapore. https://doi.org/10.1007/978-981-10-7868-2_59

Download citation

DOI: https://doi.org/10.1007/978-981-10-7868-2_59

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7867-5

Online ISBN: 978-981-10-7868-2

eBook Packages: EngineeringEngineering (R0)