Abstract

To design a high performance bandgap reference circuit in nanoscale CMOS technology becomes a great challenge. Many negative effects of nanoscale CMOS technology in high performance bandgap reference design are discussed in this chapter. A bandgap reference circuit design with both voltage output and current output is presented also. In this design, low threshold voltage MOSfet have been utilized in this design to ensure the circuit at suitable DC operation points under extreme low temperature. Operational transconductance amplifier (OTA) has been used to achieve high DC power supply rejection rate (PSRR). Two opposite temperature coefficient resistors have been connected in series to obtain a one-order temperature independent resistor which also achieves a weak curvature compensation effect for reference voltage’s generation. This bandgap reference is implemented in a 65 nm CMOS technology, occupies 0.75 × 0. 67 mm including bond pads, Measured results show that this circuit can operate at supply voltage from 1.1 to 1.3 V, and the temperature coefficient of voltage output is 30 ppm/°C with 60 dB PSRR (DC, 30°C), and the temperature coefficient of current output is 52 ppm/°C with 70 dB PSRR (DC, 30°C), among −55°C to 125°C without any trimming or calibration.

Access provided by CONRICYT-eBooks. Download chapter PDF

Similar content being viewed by others

Keywords

- Reference Voltage

- Operational Transconductance Amplifier

- Reference Circuit

- Bandgap Reference

- Junction Voltage

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

1 Introduction

Reference circuit is a critical block in analog and mixed-signal circuits such as A/D converters, D/A converters or SOCs, and it can be used as an accurate reference signal or a steady bias source. Based on the development of semiconductor technology, IC’s power supply voltage is becoming lower, so as the analog signal swing. But the resolution demands (by data converters for an example) may be constant, and that means the demand for reference signal is actually more critical. Most of the reference circuit concentrates on its DC performance than its AC performance, so the fast speed benefit from technology improvement had done nothing to a reference circuit design. On the contract, there are many negative effects in bandgap reference design caused by technology shrinking, such as low source voltage, large temperature coefficient of on-chip resistors, low EARLY voltage, large drain leakage current, etc., that will cause a great challenge to achieve a high performance bandgap reference circuit among a large temperature variation range.

This chapter is arranged as follows. Sect. 2.2 discusses five negative effects of nanoscale CMOS technology in bandgap reference design. Sect. 2.3 presents a bandgap reference circuit implementation with measurement results and comparison. Sect. 2.5, conclusion.

2 Negative Effects of Nanoscale CMOS Technology in Bandgap Reference Design

2.1 Voltage Headroom Decrease

As CMOS technology is shrinking, MOSfet’s power supply voltage is becoming lower, as shown in Fig. 2.1, there are not enough voltage headroom to achieve the conventional bandgap reference circuit.

To deal with this problem, many low voltage reference circuit schemes are presented in recent published literatures [1–18]. Figure 2.2 shows the first kind of low voltage bandgap reference circuit named current-mode bandgap reference [1] which utilizes a reference current (temperature independent) and a resistor to generate a reference voltage. The value of reference current and resistor can be choosed freely, so the reference voltage output will not be limited by the source voltage headroom. The lowest source voltage of the example circuit is about VBE + VDSAT which can be lower than 1 V (regardless OTA’s limitation).

Figure 2.3 shows the second kind of low voltage bandgap reference circuit named fractional bandgap reference [2] which utilizes a fraction of the P-N junction voltage (VBE) added a PTAT voltage (which is achieved by a PTAT current with a resistor) to generate the reference voltage. The value of reference voltage is a fraction of the conventional bandgap voltage (≈1.2 V), and it also can be lower than 1 V. The lowest source voltage of the example circuit [13] is the minimum of VREF + VDSAT with VBE + VDSAT (regardless OTA’s limitation).

Figure 2.4 shows the third kind of low voltage bandgap reference circuit which principle likes the output common voltage extraction in full differential operational amplifier [3]. The common voltage of a PTAT voltage and a CTAT voltage will achieve a temperature independent reference voltage if the opposite temperature coefficient can be counteracted perfectly. The value of reference voltage is 1/2 of conventional bandgap voltage (≈0.6 V). The lowest source voltage of the example circuit is the minimum of VPTAT + VDSAT with VBE + VDSAT (regardless OTA’s limitation).

MOSfet can be used to replace the bipolar transistor, because the threshold voltage (VTH) has the similar temperature characters as P-N junction voltage (VBE). As shown in Fig. 2.5, MD1 and MD2 have been used to replace the bipolar transistor [4]. Due to the threshold voltage of MOSfet is lower than P-N junction voltage, the source voltage of reference circuit can be even lower. Figure 2.5 shows that the current-mode bandgap reference circuit’s lowest source voltage is VTH + VDSAT (regardless OTA’s limitation). Comparing with P-N junction voltage, the threshold voltage of MOSfet is considered as unsteady, the variation range of process corner is large, so some extra process step must be utilized to adjust it.

There are many other architectures and methods of low voltage reference circuit. Some method utilizes special devices (DTMOS [5]) and some others utilize special technology (CMOS/SOI [6], hybrid with Germanium diode [7]). In now days, the level of source voltage decreasing is slowed down, but the trend is inevitable. In the future, some new architectures and methods would be innovated continuously.

2.2 Large Temperature Coefficient of On-Chip Resistors

As shown in Fig. 2.1, the conventional bandgap reference circuit output a reference voltage directly, and it can be expressed as Eq. (2.1):

When R1 and R3 use the same type of resistor, temperature coefficient of the resistors will not affect the reference voltage (VREF).

But the current-mode bandgap reference circuit can only get a reference voltage through a reference current, and it can be expressed as Eq. (2.2) and Eq. (2.3):

Temperature coefficient of the R3 will directly affect the reference voltage (VREF). Current-mode bandgap reference circuit cannot obtain a high performance reference voltage if the used resistor’s temperature coefficient are a large. On the other hand, when utilize the conventional bandgap circuit’s reference voltage and a resistor to generate a reference current, this reference current will be affected by the resistor’s temperature coefficient too.

Unfortunately, all the on-chip resistors provided by nanoscale CMOS technology have a large temperature coefficient. As shown in Fig. 2.6, the temperature sweep simulation results of all the resistors which is provided by a 65 nm CMOS technology.

As shown in Fig. 2.7, the smallest temperature coefficient on-chip resistor the variation value is ΔR = 2.4% among −55 to 125°C which temperature coefficient is about 133 ppm/°C. This temperature coefficient is still large compared with a one-order bandgap reference.

As shown in Fig. 2.2, if R3 set as only the smallest temperature coefficient on-chip resistor cannot achieve a high performance reference voltage.

2.3 EARLY Voltage Decreasing

As CMOS technology is shrinking, MOSfet’s EARLY voltage is becoming lower. As shown in Figs. 2.8 and 2.9, a PMOSfet V-I curve comparison between a 65 nm CMOS technology and a 0.18μm CMOS technology. It can be seen from Fig. 2.8 that in 65 nm CMOS technology EARLY voltage of PMOSfet with the smallest gate length decreased sharply. It can be seen from Fig. 2.9 that in different technology, even choosing the same transistor size the EARLY voltage is still different.

The negative effect of EARLY voltage decreasing to a reference design is when using one stage current mirror [8, 9, 14] (even cascode current mirror [13] which needs more voltage headroom) with small gate length can not achieve an accurate current replication. Even large gate length MOSfet (which means large VTH consumed more voltage headroom) also cannot achieve an accurate current replication here. The reason is that the drain voltage of MP2 is a P-N junction voltage (VBE), and the drain voltage of MP3 is expected to be a temperature independent voltage (VREF). Due to VBE has a large variation range among −55°C to 125°C, and with the EARLY voltage decreasing, one stage current mirror can not copy a current accurately.

Figure 2.10 shows the method which utilizes one stage current mirror to generate VREF. Figure 2.11 shows the MP2 and MP3’s drain current simulation result of Fig. 2.10, the length of MP2 and MP3 is set as 2 μm. The replication error is very large.

As shown in Fig. 2.12, a cascode current mirror is used for IREF current replication. MP4’s gate length is set as 2 μm too. The bias voltage of MP4 is generated from a diode-connected PMOSfet with a drain current which has a certain ratio with ID2.

Figure 2.13 shows the MP2 and MP3’s drain current simulation result of Fig. 2.12. The replication error is smaller than one stage current mirror, but for a high performance reference circuit this accuracy level is not enough.

2.4 Effect to DC Operation Points at Extreme Low Temperature

Due to P-N junction voltage (VBE) and MOSfet’s threshold voltage (VTH) all have a negative temperature coefficient, and a low voltage design is difficult to maintain suitable DC operation points in an extremely low temperature condition. Most of the published literatures’ temperature range were not lower than −40°C [1–18].

As mentioned in Sect. 2.2.1, all the lowest source voltages of the example reference circuits are regardless OTA’s limitation. As Fig. 2.14 shows the lowest source voltage must fulfil Eq. (2.4):

This is much larger than VBE + VDSAT (the lowest source voltage limitation regardless of OTA), and the MOSfets of OTA may exceed the saturation zone in the extreme low temperature, so the OTA must be carefully designed.

2.5 Large Drain Leakage Current

Another negative effect in nanometer CMOS technology is the MOSfet’s large drain leakage current. As shown in Fig. 2.15, a PMOSfet with a size as 300 nm/60 nm, and the source voltage (VS) is 1.2 V, and the drain voltage (VD) is 0 V. The gate voltage is swept from 0 V to 1.2 V in different temperature. The simulation result shows that in the temperature of 125°C VGS is 0.2 V, the drain leakage current is beyond 100 nA.

The negative effect of large drain leakage current to a reference design is mainly the startup circuit. That because the start-up circuit will be designed as lower power as possible, the operation current of the startup circuit may be less than 1 uA. If the leakage current and start-up circuit’s operation current are at the same quantity level, the start-up circuit may lose its effectiveness, or the output state may be flipped and then affect the reference circuit’s normal operation.

2.6 Summary

The discussed five effects caused by nanoscale CMOS technology are negative for a high performance reference circuit design. The only positive fact caused by CMOS technology shrinking is the higher manufacture accuarcy which means a smaller element mismatch. But the quantitative level of mismatch improvement cannot compensate all the negative effects. Furthermore, when a large temperature variation range is demanded, many reference circuits may not maintain a suitable DC operating point at every process corner and source voltage corner, and that will affect the circuit’s yield. So, to design a high performance bandgap reference circuit among a large temperature variation range in nanoscale CMOS technology is very difficult.

3 A Bandgap Reference Circuit in 65 nm CMOS

3.1 Circuit Implementation

Figure 2.16 shows the schematic of the presented bandgap reference circuit. The bandgap core uses a classic low voltage bandgap architecture as literature [8], but due to low threshold voltage NMOSfets are utilized, the OTAs can use a simple architecture.

The principle of bandgap core can be explained as follows: MP1 and MP2 have the same W/L, and the emitter area ratio of PNP1 to PNP2 is set as 64. The node voltage V1≈V2 because of the feedback of OTA1, and lets R1 = R4, R3 = R5, so it can get V3≈V4≈VBE2. The drain current of MP1(and MP2) can be expressed as Eq. (2.5):

When a suitable value of R1–R5 is set, ID can be temperature independent. It needs to be considered that the temperature coefficient of R1–R5 can not affect ID’s temperature characteristic if all the resistors are the same type (this will be verified by the measured results in Sect. 2.3.2).

The input common-mode voltage of OTA1 (V1/V2) is a fraction of VBE2, and this voltage must fulfil the Eq. (2.6):

VDSAT is the drain-source saturation voltage of MOSfet. V1/V2 may not fulfil Eq. (2.6) under extreme low temperature, to avoid this case, the input MOSfets of OTA1 (MN1/MN2) are choosed as low threshold voltage NMOSfet. PMOSfet input OTA also can be used here as literature [8], but in order to fulfil the output voltage range of OTA, two stage architecture must be utilized.

As Fig. 2.16 shown, the presented reference voltage output and current output circuit utilize the familiar architecture. OTA2 and OTA3 are used to obtain an accurate current replication and high DC PSRR performance. The principle is that let the drain voltage of MP3 and MP4 tracking MP1 and MP2 (and the gate voltage and source voltage of MP1–MP4 are equal) can obtain an accurate current replication under every PVT corner even the gate length of MP1–MP4 are small. Figure2.17 shows the simulation result of current replication performance, compared with Fig. 2.11 and Fig. 2.13, the accuracy of the current replication are significantly improved.

The input common-mode voltage of OTA2 and OTA3 (V4/V6) is VBE2, so MN4 and MN5 can utilize normal threshold voltage NMOSfet. The output voltage of OTA2&OTA3 must fulfil the Eq. (2.7) and Eq. (2.8):

VREF is the reference output voltage. In order to fulfil the output voltage range of OTA2&OTA3, the MP5 and MP6 are choosed as low threshold voltage PMOSfet.

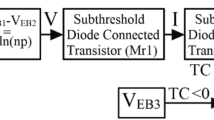

As shown in Fig. 2.18, R6 and R7 have the opposite temperature coefficient which is connected in series with suitable ratio to obtain a one-order temperature independent characteristic. This series connection’s temperature curve also achieve a curvature which is inverse to the curvature of reference current’s, as shown in Fig. 2.19, so a weak curvature compensation effect for voltage reference can be achieved.

Comparing with normal MOSfets, low threshold voltage MOSfets have many disadvantages such as large parameter variation range under PVT corners, large leakage current under very high temperature, inaccurate simulation model, etc. In this design, low threshold voltage MOSfets are only used in the feedback loop, and all those negative effects will be alleviated by OTA’s close-loop feedback.

3.2 Measurement Results and Comparison

Figure 2.20 shows the photograph of this bandgap reference, and the chip is implemented in a 65nm CMOS technology, occupies 0.75 mm × 0. 67 mm including bond pads, bonded in a D16S package. Test equipments include: Agilent 34401 multimeter, Agilent N6705B DC power analyzer, and THERMOJET-ES environmental testing apparatus.

Figure 2.21a shows the measured result of sampler1’s current output, and Fig. 2.21b shows sampler1’s voltage output. When measuring the current output, an external resistor is utilized to set the drain voltage of MP6 as similar as MP5’s, and the external resistor is put outside of the temperature control box, so the temperature coefficient of external resistor will not affect the temperature performance of current output, and the measurement of current output’s PSRR (DC) also utilizes this external resistor.

Figure 2.22a shows the measured DC power supply rejection performance of samplers1’ current output under three temperature, and Fig. 2.22b shows the measured DC power supply rejection performance of samplers1’ voltage output under three temperature.

Figure 2.23 shows the measured temperature performance of all 5 samplers’ current output as VDD = 1.2 V.

As shown in Fig. 2.23, all the five samplers’ current output temperature curve is symmetric, that because the reference current output’s temperature characteristic is based on a ratio of one type of resistor as mentioned in Sect. 2.3.1.

Figure 2.24 shows the measured temperature performance of all 5 samplers’ voltage output as VDD = 1.2 V.

As shown in Fig. 2.24, most of the five samplers’ voltage output temperature curve is asymmetric, that because the reference voltage output’s temperature characteristic is based on two types of resistors in series connection. Good matching for two types of resistors at only one time is nearly impossible, so a layout optimization can be done in the next manufacture to trimming this temperature curve, and an improved temperature performance can be expected.

Figure 2.25 shows the measured DC power supply rejection performance of all 5 samplers’ current output as T = 30°C.

Figure 2.26 shows the measured DC power supply rejection performance of all 5 samplers’ voltage output as T = 30°C.

Figure 2.27 shows the measured temperature performance of all 5 samplers’ current and voltage output as VDD = 1 V.

From Fig. 2.27, when VDD = 1 V, all the 5 samplers start becoming invalid as the temperature below 0°C, and this is due to the unsuitable DC operation points.

Table 2.1 summarizes the measured performance.

Table 2.1 compares the measured performance of the bandgap reference with several other published literatures’.

As shown in Table 2.2, because of low threshold voltage MOSfets are utilized, temperature range of the presented bandgap reference is larger than all of the listed literatures, and it can operate at the extreme low temperature (−55°C). The temperature coefficient of voltage output is better than current output, that due to the weak curvature compensation effect. DC PSRR also achieves a high performance as OTAs are utilized.

3.3 Summary

The presented bandgap reference circuit is implemented in 65 nm CMOS. To achieve a larger temperature range and a higher DC power supply rejection rate (PSRR), low threshold voltage MOSfet and operational transconductance amplifiers have been utilized. A weak curvature compensation effect for reference voltage’s generation have been achieved by two opposite temperature coefficient resistors in series connection. The measured results shows that the bandgap reference achieves all the design targets.

4 Conclusion

In this chapter, the authors discuss five negative effects caused by CMOS technology shrinking in high performance bandgap reference design, and then present a bandgap reference circuit implemented in a 65 nm CMOS with both voltage output and current output. The design includes three tips: first, low threshold voltage MOSfet have been utilized to obtain a suitable DC operating point at low temperature. Second, OTA has been used to obtain an accurate current copy and a high DC PSRR. Third, two opposite temperature coefficient resistors have been connected in series to obtain a one-order temperature independent resistor which also achieves a weak curvature compensation effect for reference voltage’s generation. The measured results shows that the reference circuit achieves a higher DC PSRR and a smaller temperature coefficient, and the temperature range is −55°C to 125°C which is larger than most of the published literatures.

References

H. Banba, H. Shiga, A. Umezawa, et al., A CMOS bandgap reference circuit with sub 1-V operation. IEEE J. Solid State Circuits 34(5), 670–674 (1999)

M.D. Ker, J.S. Chen, C.Y. Chu, A CMOS bandgap reference circuit for sub 1-V operation without using extra low-threshold voltage device. IEICE Trans. Electron. E88(11), 2150–2155 (2005)

J. Doyle, Y.J. Lee, Y.B. Kim, et al., A CMOS subbandgap reference circuit with 1-V power supply voltage. IEEE J. Solid-State Circuits 39(1), 252–254 (2004)

T. Ytterdal, CMOS bandgap voltage reference circuit for supply voltages down to 0.6 V, IEEE. Electron. Lett. 39(20), 1427–1428 (2003)

A.-J. Annema, Low-power bandgap references featuring DTMOSTs. IEEE J. Solid State Circuits 34(7), 949–955 (1999)

M. Ugajin, K. Suzuki, T. Tsukahara, A 0.6 V supply, voltage-reference circuit based on threshold-voltage summation architecture in fully depleted CMOS/SOI. IEICE Trans. Electron. E85(8), 1588–1595 (2002)

J.W. Kim, B. Murmann, R. Dutton, in International Symposium on Quality Electronic Design (ISQED). Hybrid Integration of bandgap reference circuits using silicon ICs and germaninum devices (Stanford University, San Jose, CA, 2008), pp. 429–432

K.N. Leung, P.K.T. Mok, A Sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE J. Solid State Circuits 37(4), 526–530 (2002)

G. Giustolisi, G. Palumbo, M. Criscione, F. Cutrì, A low-voltage low-power voltage reference based on subthreshold MOSFETS. IEEE J. Solid State Circuits 38(1), 151–154 (2003)

T. Raymond, Perry, S.H. Lewis, A. Paul Brokaw, T.R. Viswanathan, A 1.4 V supply CMOS fractional bandgap reference. IEEE J. Solid State Circuits 42(10), 2180–2186 (2007)

K. Sanborn, D. Ma, A. Paul Brokaw, V. Ivanov, A sub-1-V low-noise bandgap voltage reference. IEEE J. Solid State Circuits 42(11), 2466–2481 (2007)

V. Ivanov, R. Brederlow, J. Gerber, An ultra low power bandgap operational at supply from 0.75 V. IEEE J. Solid State Circuits 47(7), 1515–1523 (2012)

B. Ma, F. Yu, A novel 1.2–V 4.5-ppm/°C curvature-compensated CMOS bandgap reference. IEEE Trans. Circuits Syst. I Regul. Pap. 61(4), 1026–1035 (2014)

M.-D. Ker, J.-S. Chen, New curvature-compensation technique for CMOS bandgap reference with sub-1-V operation. IEEE Trans. Circuits Syst. II Express Briefs 53(8), 667–671 (2006)

Y. Osaki, T. Hirose, N. Kuroki, M. Numa, 1.2-V Supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOS LSIs. IEEE J. Solid State Circuits 48(6), 1530–1538 (2013)

A.J. Annema, P. Veldhorst, G. Doornbos, B. Nauta, A sub-1V bandgap voltage reference in 32 nm FinFET technology. ISSCC. 331–333 (2009)

D.F. Bowers, E.J. Modica, Curvature-corrected low-noise sub-bandgap reference in 28 nm CMOS technology. Electron. Lett. 50(5), 396–398 (2014)

V.V. Ivanov, K.E. Sanborn, I.M. Filanovsky, Bandgap voltage references with 1 V supply. Proceedings of the 32nd European Solid-State Circuits Conference. ESSCIRC 2006, pp. 311–314 (2006)

Acknowledgments

This work is supported by National Natural Science Foundation of China (No.61006027, No.61176030), Research Foundation of Key Laboratory of Analog Integrated Circuit (No.0c09YJTJ1505, No.9140c090105140C09041, No.0c09YJTJ1602), and Fundamental Research Funds for the Central Universities of China (No.ZYGX2012J003).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer International Publishing AG

About this chapter

Cite this chapter

Jun-an, Z. et al. (2017). Challenge of High Performance Bandgap Reference Design in Nanoscale CMOS Technology. In: Li, T., Liu, Z. (eds) Outlook and Challenges of Nano Devices, Sensors, and MEMS. Springer, Cham. https://doi.org/10.1007/978-3-319-50824-5_2

Download citation

DOI: https://doi.org/10.1007/978-3-319-50824-5_2

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-50822-1

Online ISBN: 978-3-319-50824-5

eBook Packages: EngineeringEngineering (R0)