Abstract

Quantum-dot Cellular automata (QCA) is nanotechnology that can be acquired to replace transistor-based design. The approach of transistor is based on charge transport; the primitive element in QCA is a cell; the communication between cells is solely Columbic hence there is no physical transport of charge. The major feature includes higher packaging density and lower power consumption. QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and functional verification of the proposed structures.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

As VLSI technology has made striking development which is continuously waning in future. The fundamental limit of MOSFET technology is its dimensional scaling which suffers from short channel and narrow channel effect which reduces performance. Other limitation deals with it is interconnects problem and power dissipation of the devices. In the trend of minimization of device size, researchers are trying to find other alternatives supplement to conventional transistors [1]. And QCA technology is one of its representatives.

In this paper, a QCA EX-OR circuit is proposed which is further being used in a half adder circuit as reposing the severe clocking scheme. There are three majority gates, and one inverter is being used in the proposed circuit. In QCA, the device can be used as an interconnect [2].

The QCA approach is firstly introduced in [3] as an effective ultra dense devices with higher performance. Basically a QCA cell is quadratic in shape that exhibits 3D quantum confinement. There are four quantum dots in a single cell oriented at the corner sides of the square which are coupled capacitively and tunnel barrier [4]. A quantum dot is a region of low potential encompasses by higher potential region which is able to detain electron of lower energies known as potential well [5]. These quantum dots comprise by the constitute of group II-VI, III-V, and IV-V Ex-CdSe, PbSe, and InP [1, 6].

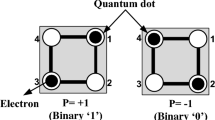

These QCA cell can contain two electrons, which are free to move between adjacent dots known as tunneling. In a QCA cell, transfer of information does not depend on the transport of electron as in conventional transistor, while on the location and adjustment of electron in a small area. And when feature size approaches to nanometer size, then quantum effect tunneling take place [3] by which electrons changes their position as depicted in Fig. 1.

There exist two charged electrons in a cell which always try to achieve the opposite corners due to repulsive electrostatic force. According to electron position in a cell, these two kinds of cell polarization or binary values take place and the values of these polarizations are defined by following equation:

where P j is the columbic charge at dot j. This equation shows that location of electrons at site 2 and 3 yield P = +1 polarization and location at site 1 and 4 will give P = −1 polarization. The fundamental idea of QCA cell is generic and can be implemented by various methods: molecular implementation, semiconductor implementation, and magnetic implementations [5, 7, 8]. Arrangement of these cells in an array is used to perform all logical functions like wires, memories, logic gates, all combinational and sequential circuits.

QCA designer tool is being used for an extant work of layout for quantum-dot cellular automata (QCA) by the Walus Group of B. Columbia University produces a fast and accurate simulation [9] by providing the powerful CAD features. QCA designer can simulate more complex computational circuits for general purpose.

2 Clock Zone

To attain the controllable data direction, cells are set into the four clock zones. For the synchronization of QCA circuit, clock plays a very crucial role [5]. A QCA array is categorized into four clock zones which are 90 degree in phase shift from one clock zone to another (Fig. 2).

QCA clocks zones [2]

These clock zones have four states: low-to-high, high, high-to-low, and low which are correspondingly referred as relax, switch, hold, and release [10]. These cells start computing during the high-to-low and hold the value during the low state [5]. Switch phase occurs when cells being unpolarized and having low potential barrier in increasing order. High potential barriers are achieved in the hold phase and lower potential barriers attained in release phase [11]. In relax phase, barriers cells are kept in unpolarized state at low level [12, 13].

3 QCA Wire

A series of Quantum cell driven by the fixed polarization work as a wire and flow of signal is controlled with clock. The binary signals propagate from one end to another end by the electrostatic interaction between cells [14]. The state of the first polarized drive cell induces the same polarization in the complete series of the cells [15]. By this method, information propagated from first cell to last cell. There are two kinds of configuration of wire (Fig. 3).

4 Logic Gates Based on QCA Logic

4.1 Majority Gate

It is the fundamental logic function being used in QCA which uses odd number of input more than one. In Fig. 4, majority gate has been shown. It is denoted as M (A, B, C) = AB + BC + CA. By using these majority gates, two input AND gate and OR gate can be implemented by fixing one of its input at polarization−1 (binary 0) and polarization+1 (binary 1), respectively.

-

For AND operation: −M (a, b, 0) = a ∙ b,

-

For OR operation: −M (a, b, 1) = a + b.

4.2 Inverter

It is another basic logic gate used in QCA. On applying 1 at input, output 0 is attained and vice versa. It is denoted in (Fig. 5).

To implement the circuit of an inverter cell should be arranged at overlapping condition at input side and at other ends corner of the cells should be matched to invert the value at output.

5 QCA Cell Placement Technique: Crossover Technique

The printing area is 122 mm; crossover techniques introduce the concept of building QCA devices which are able to execute computation as a function of synchronization. QCA follows two kinds of crossover or can say interconnection technique known as coplanar and multilayer techniques. A coplanar technique is one layer technique either regular or rotated or simultaneous cell configuration technique. While multilayer technique uses bridge kind of structure, i.e., one layer deposited over another layer. It is complex in nature due to deposition of one layer over another and it is fiddle to implement [10, 11, 16, 17] (Fig. 6).

6 Conventional Circuit Using Multilayer Architecture

6.1 EX-OR Gate

It is a universal gate and used in various adder circuits and comparator and so many. EX-OR gate gives high at different level input and low at same level input.

This Boolean expression has been implemented in the circuit designing depicted in Fig. 7, using the multilayer crossover technique and can be realized more than one way. This technique uses the three majority gates and two inverters.

6.2 Half Adder

Half adder is an arithmetic circuit which is used for addition of two numbers and produces a sum and carries as the output, e.g., if P and Q are the inputs then the sum will be the EX-OR of P and Q and the carry will be the AND of P and Q [6] (Figs. 8 and 9; Tables 1 and 2).

6.3 Full Adder

A one-bit full adder used to add three one-bit numbers and generate a carry. If P, Q, and R three input bits then the sum will be the EX-OR of P, Q, and R and the carry will be PQ + QR + PR. Layout and simulation of full adder have been shown in Figs. 14 and 15, respectively, (Table 3).

7 Proposed Circuit of EX-OR Gate, Half Adder, and Full Adder Using Coplanar Technique

In the proposed circuits, three majority gates and one inverter are being used [14].

The layout of the above Boolean expression has been shown in Figs. 10 and 12 along with the simulation result in Fig. 11 and in Figs. 13, 14 and 15.

8 Comparison

See Table 4.

9 Conclusion

QCA is the answer for transistor-less design. In this paper, it is demonstrated how QCA cells can be arranged to obtain exclusive or operation. Further, it was proposed that half adder and full adder operation can be implemented employing the QCA cell-based structure. It was also observed that coplanar crossover architecture for EX-OR gate was less complex in terms of implementation when compared to multilayer crossover structure. Area was significantly reduced in half adder and full adder designs when the proposed architecture for EX-OR operation was used. This fact is illustrated in Table 4 where comparison of various adder structures has been provided. All the QCA cell-based structures were implemented on QCA designer tool with multi-phase clock propagation.

References

Kim, K., Wu, K., Karri, R.: The robust QCA adder designs using composable QCA building blocks. IEEE transactions on computer-aided design of integrated circuits and systems, 26(1), 176–183 (2007).

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE transactions on very large scale integration (VLSI) systems, 19(9), 1535–1548 (2011).

Lent, C.S., Tougaws, P.D., Porod, W., Bernestine, G.H.: Quantum cellular automata. Nanotecnology, Vol. 4, pp. 49–57 (1993).

Snider, G.L., Orlov, A.O., Amlani, I., Bernstein, G.H., Lent, C.S., Merz, J.L., Porod, W.: Quantum-dot cellular automata: Line and majority logic gate. Japanese Journal of Applied Physics, 38(12S), 7227 (1999).

Radhika, P., Tiwari, N., Pant, Y.: Design of adder and multiplier using quantum dot cellular automata based on nanotechnology. In Presented at the National Conference on Emerging Technologies (2011).

Cho, H., Swartzlander, Earl E.: Adder designs and analyses for quantum-dot cellular automata. IEEE Transactions on Nanotechnology, 6(3), 374–383(2007).

Wang, W., Walus, K., Jullien, G.A. (2003, August). Quantum-dot cellular automata adders. In Nanotechnology, 2003. IEEE-NANO 2003. 2003 Third IEEE Conference on Vol. 1, pp. 461–464 (2003).

Azghadi, M.R., Kavehie, O., Navi, K.: A novel design for quantum-dot cellular automata cells and full adders. Journal of Applied Sciences, Vol. 7, No. 22, pp. 3460–3468 (2007).

Lent, C.S., Tougaw, P.D., Porod, W.: Quantum cellular automata: the physics of computing with arrays of quantum dot molecules. In Physics and Computation, 1994. PhysComp’94, Proceedings, Workshop on IEEE, pp. 5–13 (2014).

Srivastava, S., Bhanja, S.: Hierarchical probabilistic macromodeling for QCA circuits. IEEE Transactions on Computers, 56(2), (2007).

Walus, K., Jullien, G.A.: Design tools for an emerging SoC technology: Quantum-dot cellular automata. Proceedings of the IEEE, 94(6), 1225–1244 (2006).

Blair, E.P., Yost, E., Lent, C.S. (2010). Power dissipation in clocking wires for clocked molecular quantum-dot cellular automata. Journal of computational electronics, 9(1), 49–55 (2010).

Graunke, C.R., Wheeler, D.I., Tougaw, D., Will, J.D. (2005). Implementation of a crossbar network using quantum-dot cellular automata. IEEE Transactions on Nanotechnology, 4(4), 435–440 (2005).

Walus, K., Dysart, T. J., Jullien, G. A., Budiman, R. A.: QCA Designer: A rapid design and simulation tool for quantum-dot cellular automata. IEEE transactions on nanotechnology, 3(1), 26–31(2004).

Perri, S., Corsonello, P.: New methodology for the design of efficient binary addition circuits in QCA. IEEE Transactions on Nanotechnology, 11(6), 1192–1200 (2012).

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata. IEEE transactions on nanotechnology, 3(1), 26–31(2004).

Galatsis, K., Khitun, A., Ostroumov, R., Wang, K.L., Dichtel, W.R., Plummer, E., Kim, K.W.: Alternate state variables for emerging nanoelectronic devices. IEEE transactions on Nanotechnology, 8(1), 66–75 (2009).

Sridharan, K., Pudi, V.: Design of arithmetic circuits in quantum dot cellular automata nanotechnology. Spinger Vol. 599 (2015).

Reddy, D.T., Reddy, S.P., Reddy, K.S.K., Reddy, S.N., Khasid, S.K.: Area-Delay Efficient Binary Adders in QCA. Editorial Committees, 52.

BASU, S.: Realization of Xor and Xnor gates using qca basic gates (2014).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kumari, P., Sharma, A., Singh, A. (2018). Implementation of Adder Circuit Using Quantum-Dot Cellular Automata-Based Logic Gates. In: Singh, R., Choudhury, S., Gehlot, A. (eds) Intelligent Communication, Control and Devices. Advances in Intelligent Systems and Computing, vol 624. Springer, Singapore. https://doi.org/10.1007/978-981-10-5903-2_20

Download citation

DOI: https://doi.org/10.1007/978-981-10-5903-2_20

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-5902-5

Online ISBN: 978-981-10-5903-2

eBook Packages: EngineeringEngineering (R0)