Abstract

This paper demonstrates design of analog circuits using g m /I D method. It explains the effectiveness of g m − I D approach and then generates required plots using any simulator. Other than complex method of generating g m − I D plots, which requires advanced simulators, it is shown that a plot of I D /g m can be easily generated directly using simulator or through a simple program capable to manipulate device current–voltage data. The success of g m /I D technique lies on the fact that it employs a simple rule of scaling device dimension (w) and scales the current as well as transconductance (g m ) equally, when other parameters are constant. Therefore, when a reference device with required g m and I D is found, it can be scaled up to generate desired g m at the given bias current (power) I D . Proposed method is not only technology independent, it is also free from complex mathematical expressions associated with the device as it employs data generated from simulators. As it is not based on analytical methods or models, its accuracy (independent of BSIM or ACM; and their parameter values) is much better specially for analog design. Most importantly incorporating simulator in the design process, analysis of the designed circuit, using the same simulator, is expected to match the desired performance closely. Using this simple approach, design time becomes shorter and a workable design can be made very quickly. Two basic amplifier circuits are designed using the proposed method, and simulation results are discussed.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Analog designs are carried out traditionally by analytical methods [1, 2] and then fine-tuned using a simulator to reach the final design. It is often observed that final design variables (device dimensions) differ largely from the estimated values obtained analytically. The difference in the predicted and the final design values can be reduced if complex models like BSIM are used while carrying out the design analytically. The designer often seeks for the help of another simulator, optimizer or programming method to reach the specifications [3, 4]. Whatever may be the approach, the net time to design any analog block increases, specially for designs using short-channel devices. Moreover, such methods increase the design complexity and make the task difficult for beginners designing analog circuits in submicron CMOS.

To overcome this challenge, a technology-independent approach is proposed by Kaspers [5–7] where g m /I D ratio is used to as key design parameter. It is found that this ratio-based technique can be applied to all kind of devices, both long and short channel [8]. Being free from complex analytical models, even novice designers can design analog blocks with desired performance within a short span of time with fewer iteration.

In the following sections, the principle of g m /I D approach is explained and the method is tested by designing amplifiers using 180 nm CMOS.

2 Basic Principles

Typically, analog designers first design any analog circuit with pen and paper using some device model whose equations can be manipulated with hand calculations (SPICE level 1 or 2). Usually, these models are based on long-channel devices. Once this design is complete, the designer implements the schematic using the device sizes projected analytically on a simulator. State-of-the-art simulators, however, use extremely complex and accurate deep submicron device models like BSIM3,4 to analyse the designed circuit. Consequently, simulation results do not match with the mathematical expectations. It may be mentioned that this error is primarily due to the modelling of short-channel devices with long-channel equations. The designer now adopts an ad hoc approach, adjusts the device dimensions, bias and attempts to meet the desired response from the circuit. In CMOS technology, keeping all the transistors in saturation is one of the most challenging tasks, specially in cascaded structures.

This work investigates the use of g m /I D model in the design of analog circuits through simulator. Simplified circuit technique is used to generate I D /g m plots, so that any basic SPICE like simulator can be employed. Plot of device output impedance versus length is also generated to estimate minimum geometry of the required transistor. Finally, simple programming-based design is discussed to make an optimized design with improved accuracy. The design process comprises of the following steps.

2.1 Theory

The current–voltage relationship of a MOS can be written as:

Above equation has two important characteristics. One, drain current I D can be scaled by scaling the device width (w) if other parameters remain constant and it is independent of technology node. This simply means, maintaining bias and other parameters constant, and connecting devices in parallel will simply add their drain currents. Second, transconductance of the device (g m = δI D /δV GS) is found to be:

which is gain found to be scalable, provided other parameters are constant. In other words, if we connect N devices with identical bias condition but of different width w i in parallel, overall g m of the composite device can be written as

Above two points can be summarized as follows. When multiple devices of identical gate length are connected in parallel, both current and transconductance scale up (down) equally. Dividing (1) by (2) we get,

And it is independent of device size and becomes function of bias voltages applied across different terminals. In other words,

To elaborate this issue, we have calculated g m /I D using α power model [9–11], where drain current is expressed as

Therefore, g m /I D = α/(V GS − V T ), clearly depends only on V GS, where α, V T could be treated as constant.

To understand its implication, consider the I D –V GS plot of a reference device shown in Fig. 1. We are required to find the relative width of a device which will operate at a bias current of \( I_{D} (\max) = I_{D2} \) and offer a g m = g m2 which could provide desired amplification. Therefore, we are required to find out the operating point of the reference device where it will have an I D = I D1 with g m = g m1 such that when device is scaled by k, the scaled device (w2 = kw1) will operate at \( I_{D} (\max) = I_{D2} = kI_{D1} \) and offer g m2 = kg m1.

Let us summarize the steps to be followed to design an amplifier of gain A v . From the given specifications, we need to find out (i) maximum drain current permissible (from P D , SR, or UGF, etc.) (ii) the required load impedance R L (from output DC bias point, output swing, etc.) then (iii) g m required to achieve desired gain A v and lastly calculate the ratio of drain current to required transconductance (I D /g m ). We now take a reference device and plot its I D /g m ratio under varying bias. In this plot, we have to locate the bias point (\( I_{D} \, {\text{or}}\,V_{\text{GS}} \)) where desired \( I_{D} \, g_{m} \) ratio is available. Scaling this device by k, where

will give the dimension of the amplifying device. When I D /g m (or g m /I D ) is plotted with respect to V GS, we need to measure its I D1 at the same V GS and use (7) to find the required device.

In case the ratio k is found abnormally large, which could happen if I D1 is small or V GS1 is close to V T , designed amplifier will operate near subthreshold which may not return a reliable design. In such case, it is suggested to lower the g m requirement and increase R L (if permissible). Alternatively, one may use other I D /g m reference plots of devices of higher gate length l.

3 Generation of I D /g m Plots

This section describes how to generate I D /g m plots using simulator. Plenty of literature on this matter is available on web, and plotting technique exploits waveform manipulation tools generally available from advanced simulators like cadence. However, basic SPICE like freely downloadable simulators do not support such manipulation of plots and it becomes quite difficult to generate where I D has to be divided by g m under varying bias conditions.

Most preferred approach to calculate I D /g m ratio would be with the help of simple computer program (or SCILAB/MATLAB) which can manipulate \( I_{D} - V_{\text{GS}} \) data easily. In this technique, simulator is required to generate a datafile where I D as function of V GS is stored by sweeping V GS. Once the table of data is available, g m can be calculated as

MATLAB/SCILAB can easily manipulate I–V data of reference device and plot I D /g m as a function of either I D or V GS based on (8). Alternatively, if we wish to plot it directly in simulator, we must compute (8) while running DC sweep. To carry out the computation, we have separated 3 factors in (8). We propose to compute third factor assuming other two terms (or their ratio) are known. To appreciate this, let us rewrite (8) as follows.

Let us assume we can vary I D in a manner such \( I_{D1} = (1 - \delta ) \cdot I \quad {\text{and}} \quad I_{D2} = (1 + \delta ) \cdot I \) so that \( (I_{D2} + I_{D1} )/(I_{D2} - I_{D1} ) = 1/\delta \). Under this condition, I D /g m can be written as

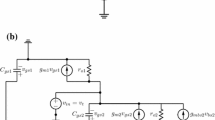

If \( \delta = 0.005,\, I_{D} /g_{m} \) becomes 100 times difference between two gate–source voltages driven by current having small differential drain current. A schematic to plot I D /g m is shown in Fig. 2 where two controlled sources are used to drive two NMOS. Estimation of I D /g m could be done from differential gate–source voltages (V GS1 − V GS2). One may use current ramps (\( I(t) = mt \pm \delta t \)) in place of controlled sources to achieve similar plot.

A better way of computing g m /I D is to use a logarithmic amplifier. In this approach, drain current (I D ) of the reference device is applied to a log amplifier and then output current is differentiated in time domain using a simple RC differentiator. Mathematically stated,

4 Amplifier Design

In this section, we explain the design procedure of a CS amplifier with specifications given as follows: DC gain A v = 10, UGF = 1 MHz, power dissipation = 1 mW, C L = 5 pF, V DD = 1.8 V, etc. Following basic steps [2], one can find out the DC bias current and load resistance which meet the gain and other requirements. Let us assume that the required value of DC bias current is (I D = 20 μA) and R L = 45 K. Ignoring g ds, we get required \( g_{m} = A_{v} /R_{L} = 222\,\upmu{\text{A/V}} \). From the I D /g m plot (Fig. 3) of a reference device of w/l = 240/180 nm, we find desired I D /g m at V GS1 = 428 mV, at I D1 = 4.42 μA. Thus, amplifying device needs to be scaled by 4.5x (=20/4.42) to have desired g m at drain current of 20. Finally, when amplifier is simulated using the projected device, a voltage gain of 7.8 is measured. The deviation from the expected value is due to the fact that we had neglected the effects of r o in gain calculation (\( A_{v} \propto R_{L} \parallel r_{o} \)) and approximations involved in I D /g m measurement. The ratio plotted using the schematic is actually \( I_{D} /(g_{m} + g_{\text{ds}} ) \). More investigation on this is under process.

4.1 CS Amplifier with Current Source Load

Now, we turn our attention to the design of a CS amplifier with a PMOS current source load. The procedure is simple when we employ a simulator to measure the output impedance accurately. To measure \( g_{\text{ds}}\,{\text{or}}\,r_{o} \), we use a setup where two identical devices with same gate bias are driven by \( V_{D} = (0.5V_{\text{DD}} \pm 50\,{\text{mV}}) \) and their differential I D (ΔI D ) is measured. Thus, \( g_{\text{ds}} = 10 \times\Delta I_{D} \). Such plots are generated for different lengths. To find out the desired length of the load to achieve desired r o , required length of the device is adjusted using \( r_{o1} /l_{1} = r_{o2} /l_{2} \). If r o measured from simulation is less than the desired R L , we need to scale up the length of the device proportionately. On the other hand, if the device r o is higher, we expect more gain from the designed amplifier. However, one may redesign the circuit with lower current and obtain a low-power design solution. Same approach may be used if load device r o is smaller than desired by scaling down current, provided it satisfies other specifications like slew rate.

5 Conclusion

In this paper, an extremely simple design methodology for analog circuits is discussed. Besides being technology independent, it is also free from complex mathematical expressions. Analog designers with less experience can also design opamps in a short time using the proposed approach. Being directly based on the simulator, which uses state-of-the-the-art MOSFET models like BSIM, the results obtained from this method are highly accurate. In this work, design of simple amplifiers for a given specification is described to validate the method. All the design formulations have been tested in UMC 180 nm CMOS process.

References

Mallya, S.M., Nevin, J.H.: Design procedures for a fully differential folded-cascode cmos operational amplifier. IEEE J. Solid State Circ. 24(6), 1737–1740 (1989)

Allen, P.E., Holberg, D.R.: CMOS Analog Circuit Design. Oxford University Press, Oxford (2007)

Mandal, P., Vishvanathan, V.: CMOS op-amp sizing using a geometric programming formulation. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 20(1), 22–38 (2001)

Boyed, S., Hershenson, M., Lee, T.: Optimal design of a cmos op-amp via geometric programming. IEEE Trans. Comput. Aided Des. 20(1), 1–21 (2001)

Silveira, D., Jespers, P.G.A.: A gm/ID based methodology for the design of CMOS analog circuits and application to the synthesis of a SOI micropower OTA. IEEE J. Solid State Circ. 31(9), 1314–1319 (1996)

Jespers, P.: The gm/ID methodology, a sizing tool for low-voltage analog CMOS circuits. Springer, Boston (2009)

Rao, A.J: Analog front-end design using the gm/ID method for a pulse-based plasma impedance probe system. MS thesis, Utah State University, Utah (2010)

Todani, R., Mal, A.K.: Simulator based device sizing technique for operational amplifiers. WSEAS Trans. Circ. Syst. 13(1), 11–28 (2014)

Sakurai, T., Newton, R.: Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas. IEEE J. Solid State Circ. 25, 584–593 (1990)

Sakurai, T., Newton, R.: A simple MOSFET model for circuit analysis. IEEE Trans. Electron Devices 38, 887–894 (1991)

Sakurai, T., Newton, R.: Alpha power-law MOS model. Solid State Circ. Soc. Newslett. 9(4), 4–5 (2004)

Acknowledgments

The authors would like to acknowledge the support of VLSI Lab at NIT Durgapur, originated from SMDP project funded by DeitY, Govt. of India.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer India

About this paper

Cite this paper

Mal, A., Mal, A.K., Datta, S.K. (2015). CMOS Amplifier Design Using Simplified g m /I D Technique . In: Mandal, D., Kar, R., Das, S., Panigrahi, B. (eds) Intelligent Computing and Applications. Advances in Intelligent Systems and Computing, vol 343. Springer, New Delhi. https://doi.org/10.1007/978-81-322-2268-2_55

Download citation

DOI: https://doi.org/10.1007/978-81-322-2268-2_55

Published:

Publisher Name: Springer, New Delhi

Print ISBN: 978-81-322-2267-5

Online ISBN: 978-81-322-2268-2

eBook Packages: EngineeringEngineering (R0)