Abstract

Considering that the induction heating power supply controlled by pulse density modulation operated in the free resonance state, it was impossible to precisely detect a very small amount of load current, a conventional PLL (Phase-Locked Loop) circuit does not work properly, so a improved PLL frequency tracking control technology is presented in this paper. When the power stage decreased the discharge power into 1–10 % of the full power, the S/H (Sample and Hold) circuit and the PCD (Peak Current Detector) were used to guarantee the inverter working at the vicinity of the resonant frequency. The output signal from PCD opened and closed the S/H to drive the VCO (voltage-controlled oscillator), and a selected load peak current reference value was compared with the actual load peak current to control the PCD. Finally the control strategy is verified by using the Matlab / Simulink simulation results, the power stage can always work in the state of zero current and zero voltage switching and the phase-locked failure is avoid.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

- Induction heating power supply

- Pulse density modulation

- Frequency tracking control

- Improved phase-locked loop

1 Introduction

Induction heating technology is developed in the direction of high-power and high frequency. Different heating process such as smelting, diathermy, annealing and hardening have special requirements for the power and frequency, and then leads to a variety of power conditioning and frequency tracking control method. According to the adjustment link, the power modulation method can be divided into rectifier regulation, DC side control and inverter power regulation [1, 2].

The inverter side power regulation in line with different control ways can be divided into pulse frequency regulation [3], pulse phase shift modulation [4] and pulse density modulation. Power switching devices using the pulse frequency regulation and pulse phase shift modulation method [5, 6] will work incessantly in the non-zero current and non-zero voltage switching state, it will lead to the increase of switching losses and electromagnetic noise interference [7]. In addition, the pulse frequency regulation and pulse phase shift modulation will change the phase between output voltage and current during regulating the output power, thus affecting the performance of the frequency tracking controller or phase-locked loop controller [8]. The pulse density modulation proposed in literature [9] adopt a reasonable choice of pulse sequence to realize a greater adjustment range in the output power and ensure that the inverter always operating in a quasi- resonance state, thus achieving zero current and zero voltage switching. However, the restoration from the free resonance state to the output power state needs to re-lock the operating frequency of the inverter, which could easily lead to the system out of control.

To avoid phase lock failure after the end of the pulse density modulation period, a improved phase-locked loop control scheme based on the load peak current is proposed in this paper, when the induction heating power supply changes from the powering state to a free resonance state and again returned to the powering state, according to the sampling hold circuit, two different reference current values are analyzed and calculated, a current selection scheme corresponding to the minimum pulse density value is proposed, the simulation results verified the feasibility of the proposed scheme.

2 The Principle of Pulse Density Modulation

According to the main circuit structure shown in Fig. 1, the equation can be expressed as follows:

Only considering the fundamental voltage component added to the load when the load circuit is at the resonance state. Where, ω = ωr = 1/(LC)1/2, assume that 2ωrL/r = 2Q>> 1, Q represents the quality factor of the resonant circuit, so load current can be given:

Although the load resonant circuit is a second order system, however, Fig. 2 shows that the envelope line of the load resonant current is fist-order response, and the time constant τ = 2 L/r, then the envelope line of the resonant current iE can be expressed as:

Where:

\( \hat{\mathrm{ I}} \) is the current when the modulation ratio is D = TA/T = 1.

3 Improved Phase-Locked Loop Control Based on the Load Peak Current Comparison

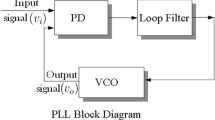

This paper uses the load current comparison control method, introduces the load peak current detection section and compares the load current with the preset reference current value, when the peak current is higher than the set reference value, the sample hold circuit works at the state of sampling, the frequency tracking circuit still operating in the normal phase-locked loop, however, when the peak current detection value is lower than the reference current, sample and hold circuit will no longer receive the output signal of the filter, but keep the signal in the last moment before the state transition to drive the VCO continue working, the control principle is shown in Fig. 3.

However, induction heating surface treatment sometimes needs to reduce the output power to 10 % of the rated power or even lower, namely, when the pulse density modulation ratio decreases, the output load current will be small, according to present resolution and accuracy, the peak current detector have been unable to accurately detect such a small current, thus the frequency tracking circuit will not function properly. So how to select the appropriate current reference value ensure that the frequency tracking control circuit to work properly must be solved.

Further analysis, consider the main circuit parameters shown in Fig. 1, the load quality factor Q = 10, the difference of the maximum peak current Imax and the minimum peak current Imin is shown in Fig. 4.

Noted from Fig. 4 that when D > 0.1, the difference between the maximum value Imax and the minimum value Imin increases as the modulation ratio significantly increases, when D = 0.5 the difference is the maximum, the performance of the phase-locked loop frequency tracking control circuit in the small fluctuations of the sampled signals is much better than the larger signal fluctuations, the smaller the signal fluctuations, the higher the resolution of the phase-locked loop, the more sensitive to changes in the signal phase, while for the large disturbance is not sensitive, which leads to the judgment delay, even in some cases beyond its phase capture range leads to lock failure.

Based on the above analysis, D = 1/16 as the lower bound and 1 ‰ as the gain, infinitely approaching to D = 0.1, the function relationship of the phase-locked angle and the corresponding minimum current of the peak current Imin ranging from D = 1/16 to D = 0.1 is obtained, as shown in Fig. 5.

It can be reduced that when the phase-locked angle is a very small inductive angle ranging from 0 to 0.1, Imin can be equal to 9.5, 10.5, 11.5A. Then the optimal peak current reference value selection scheme will be obtained by simulation analysis.

4 Simulation Analysis

A single phase series resonant inverter model is built by utilizing the Matlab/Simulink tools, main circuit parameter is shown in Fig. 1, DC source voltage is Ud = 500 V, the resonant load parameters are L = 5 μH,C = 0.0398 μF, r = 1.2Ω, the rated power is P = 200 kW, the resonant frequency is fr = 350 kHz, RC snubber parameters are R = 11.5Ω,C = 2200 pF, the main circuit lead inductance is Ls = 0.01 μH, the output power control using pulse density modulation.

Adopting improved phase-locked loop control based on the peak load current comparison, phase-locked switching process is analyzed as follows. Under the condition that the DC voltage Ud = 500 V is invariable, regulating the DC side current achieves the purpose of adjusting the output power, Fig. 6 shows that when DC current reduced from 90A to 40A the corresponding output load current and voltage waveform.

-

1.

When the peak load current comparison control is not considered, the pulse density modulation ratio D = 1: 2 corresponding to the condition that the output power decrease, the output voltage and current waveforms are shown in Fig. 7,the phase-lock tracking control circuit output waveform is shown in Fig. 8.

In Fig. 7, at the free resonance state, the load power flows through the RC snubber and anti-paralleled diode, then the phase angle selection must be accurate, and can predict the phase-locked position angle in the next pulse density modulation cycle, when the modulation ratio is 1: 2 or even smaller, as shown in Fig. 8, the inductive angle is so large that a voltage spike is produced during the free resonance state, the switch loss increases, which leads to the power loss increasing, even at the beginning of the next modulation period, entering the capacitive area, causing the phase lock failure and then burning power electronic devices.

-

2.

Considering the load current comparison control, the pulse density modulation ratio is D = 0.3 or even lower values, we can consider a limit state, when D = 1/16, the corresponding pulse density modulation minimum value is calculated by the formula (6) that Iref = 7.95A, the phase control angle is shown in Fig. 9.

Figure 9 shows, set Iref = 7.95A as the peak current reference value, when the load current works at the free resonance state, the sampling hold circuit works at the hold state, keep the lock phase signal in the last moment before the state transition to drive the VCO to generate the control pulses, as the linear part shown in the graph; but when changes from the free resonance state back to the powering state, if switching phase-locked state at the minimum current reference value Iref = 7.95A, as shown in Fig. 9, a large inductive angle running at an initial state can be observed, repeating the separate-excitation turns to self-excitation process when the inverter startup, at that time the separate-excitation control circuit has stopped the work, which shows the frequency tracking control circuit is out of control, turns into the “free resonance” state, at this time any external electromagnetic disturbance or fault will cause this condition amplifying, switching devices loss increasing even being burned.

According to the above analysis, when the frequency tracking control circuit turns from the powering state to the free resonance state, set a small load current as the reference value of the peak current comparison to ensure reliable work, a load current value is also calculated as the peak current reference value when changes free resonance state back to the powering state to further improve the phase-locked loop load resonant frequency tracking speed. According to the analysis of 3.2 and phase angle and the minimum current Imin distribution relationship in Fig. 5, select Iref = 9.5, 10.5, 11.5A respectively, the corresponding phase angle experimental waveforms are shown in Fig. 10. The Imin = 10.5A is the most appropriate peak current reference value when changing from the free resonance state back into the powering state.

5 Conclusion

In order to meet the requirement of switching frequency constant when the output power drops below 10 % of the rated power in the heating process, an improved phase-locked loop control method based on the load peak current comparison is proposed in this paper. Adding the sampling hold device to the existing phase-locked loop circuit without changing the capture range and accuracy condition, furtherly improving the tracking speed of the phase-locked loop on the load resonant frequency even the load current is quite small, which ensures the inverter switching devices continue working at zero voltage and zero current switching state when switching between the free resonance state and the powering state. Compared with the traditional phase-locked loop control, the proposed control method can further reduce the power loss of power switching devices and improve the operating efficiency of equipment.

References

Fujita H, Akagi H (1996) Pulse density modulated power control of a 4 kW, 450 kHz voltage-source inverter for induction melting applications. IEEE Trans Ind Appl 32(2):279–286

Hong Lv, Yushui Huang, Zhongchao Zhang (2003) The PWM-PFM control method of induction heating power supply. Power Electron Technol 37(1):8–11

Hong Mao, Zhaolin Wu, Zhencheng Hou (1998) Induction heating power supply zero phase difference frequency tracking control circuit. Power Electron Technol 32(2):69–72 (In Chinese)

Jun Yang (2004) Research on the IGBT super audio frequency induction heating power supply phase tracking. Tsinghua University, Beijing

Liqiao Wang, Yushui Huang, Changyong Wang, Zhongchao Zhang (2001) Research on induction heating power supply based on a novel phase-shifted control. Power Electron Technol 35(1):3–4 (In Chinese)

Tianming Pan (1996) Modern induction heating device. Metallurgical Industry Press, Beijing, pp 125–196

Tianming Pan (1983) Power frequency and medium frequency induction furnace. Metallurgical Industry Press, Beijing, pp 68–89

Yabin Li, Yonglong Peng, Heming Li (2006) The optimal ZVS control of series resonant inverter. Power Electron Technol 40(3):14–16 (In Chinese)

Zonggang Qi, Peng Liu, Huiming Chen (2003) Research on power modulation for induction heating[J]. Heat treatment metals (China) 2003(7):54–57 (In Chinese)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2014 Springer International Publishing Switzerland

About this paper

Cite this paper

Qi, B., Zhu, H., Peng, Y., Li, Y. (2014). Improved Phase-Locked Loop Based on the Load Peak Current Comparison Frequency Tracking Technology. In: Wang, W. (eds) Mechatronics and Automatic Control Systems. Lecture Notes in Electrical Engineering, vol 237. Springer, Cham. https://doi.org/10.1007/978-3-319-01273-5_78

Download citation

DOI: https://doi.org/10.1007/978-3-319-01273-5_78

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-01272-8

Online ISBN: 978-3-319-01273-5

eBook Packages: EngineeringEngineering (R0)