Abstract

Phase Frequency Detector (PFD) being one of the important block of the high frequency clock generator encounters two major problems in its design. One being the dead zone and other is blind zone. The presence of the dead zone leads to phase noise. Blind zone increases the lock time of the clock generator. This paper presents a novel edge detector based PFD. In the proposed PFD, zero blind zone is achieved by eliminating the reset pulse beyond the dead zone region. The proposed PFD is designed in UMC 0.18 \(\upmu \)m CMOS process. It consumes power of 648 \(\upmu \)W at an operating frequency of 1 GHz. It is observed that the proposed PFD locks 43\(\%\) faster than the conventional PFD.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

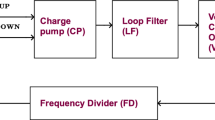

High frequency clock generators commonly known as Phase Locked Loop (PLL) is being used in numerous applications across the globe that includes Wi-fi routers, televisions, Zigbee, etc. The widely used PLL is the charge pump based PLL. It consists of five blocks. PFD being the first block of the PLL detects the phase and frequency differences between the reference clock (REFCLK) generated by the crystal oscillator and the feedback clock (FBCLK) generated by the Frequency Divider (FD). It generates UP and DOWN (DN) signals. These signals are converted as a control signal (VCTRL) to the Voltage Controlled Oscillator(VCO) by the Charge pump (CP) and Loop filter (LF) which helps in the locking of the PLL loop. Thus, the ability of the PFD to detect all the phase differences in the range of [−2\(\pi \), 2\(\pi \)] is very essential as it helps in fast acquisition of the PLL and also helps in the generation of low phase noise, high frequency clock.

1.1 Issues Related to Conventional PFD

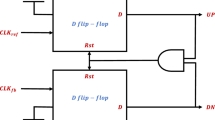

Conventional PFD is shown in Fig. 1. The operation of the PFD can be easily visualised with the help of the state diagram as shown in Fig. 2.

Conventional PFD encounters two issues in its architecture namely dead zone and blind zone that affects the linearity as presented in Fig. 3, thereby reducing the PFD operating range.

In the PFD phase characteristics, dead zone occurs in the neighbourhood of zero phase difference. Due to the presence of finite parasitic capacitances, the PFD output doesn’t have enough time to reach a particular logical level 0 or 1 (that is, 0 or Vdd) when small phase difference exists between the input clocks. Thus, PFD fails to trigger the CP leading to accumulation of static phase error until the PFD comes out of the dead zone region. This static phase error translates to phase noise in the PLL. Using finer and finer technology, the dead zone can be reduced but we cannot completely eliminate it. To eliminate completely we can add delay elements in the reset path of the PFD equal to the minimum ON time of the CP switches to turn ON. Hence, even for small phase difference, the charge pump will now be able to turn ON for correcting the phase error and making the PFD as a dead zone free circuit. Thus, increasing the delay in the reset path reduces the dead zone in the conventional PFD. As the delay in the reset path is increased, the highest frequency of operation of the PFD gets limited and also it leads to high blind zone.

The highest frequency of operation(\(f_{max}\)) of the PFD is inversely proportional to the reset path delay (\(T_{Rst}\)) and is given by [8],

Thus, high reset path delay limits the highest operating frequency of the PFD.

In the PFD phase characteristics, blind zone occurs in the neighbourhood of 2\(\pi \) phase difference. The PFD fails to detect the rising transition of the leading input clock signal due to high reset pulse. Thus, the PFD produces wrong output, misleading the PLL. This leads to increase in the lock acquisition of the PLL. Hence, need to eliminate the blind zone is necessary to reduce the lock acquisition which is a major concern for high speed applications. The PFD introduces wrong output for phase differences greater than \(2\pi -\phi \) where,

Here, \(T_{R}\) = the reference clock time period.

As seen from the above equation, blind zone depends on the reset pulse. Blind zone is lower, when the reset path delay is lower. If reset path is zero, from the equation we obtain zero blind zone.

There are various PFD designs in the literature to overcome the problems of the PFD. In [5], PFD using transmission gate is designed. It is blind zone free but has an operating range of [\(-\pi \), \(\pi \)] severely affecting the PLL locking time. In [7], PFD using selective reset technique is designed to reduce the blind zone. It has a blind zone of 3 ps. In [1], differential PFD is designed. It is blind zone free but has an operating range of [\(-\pi \), \(\pi \)]. In [3], composite PFD is implemented to eliminate blind zone. This leads to PLL design complexity as it requires two charge pumps and a switchable loop filter. In [9], delays were used to push the leading input clock signal edge out of the reset pulse to get the correct output to reduce the blind zone. The problem with such a design is that it may fail across process, temperature, voltage variations. In [2], edge detector is used to design the PFD. It has a reset pulse of 80 ps, thus introducing significant blind zone. In [6], latch based PFD is designed. The reset path is reduced to obtain high operating frequency and fast locking of the PLL. It has a highest operating frequency of 1.5 GHz. The presence of reset path indicates the presence of blind zone in the latch based PFD.

This paper introduces a novel blind zone free PFD using edge detector for fast locking of PLL. Section 2 introduces the proposed design. Section 3 and Sect. 4 presents the simulation results and the conclusion of the work respectively.

2 Proposed PFD

PFD requires reset pulse only in the dead zone region [4]. Thus, in the proposed circuit the reset pulse is eliminated after the dead zone region in the PFD. The circuit diagram of the novel PFD is presented in Fig. 4. In the PFD, REFCLKD and FBCLKD are the delayed version of the reference clock (REFCLK) and feedback clock (FBCLK) respectively, to completely eliminate the blind zone. RH and FH signals are generated using edge detectors. Edge detectors are used in the discharging path so as to get the correct output beyond the dead zone region. Transistors Mu4 and Md4 are used to ensure proper operation of the PFD.

2.1 PFD Operation

Let us assume REFCLK leads FBCLK. Initially node x and y are precharged to Vdd. Here, we consider two cases: (1) PFD operation beyond the dead zone region (2) PFD operation in the dead zone region.

Case 1. In Fig. 4, when REFCLK goes high, node U goes high. Thus, UP signal goes high. Transistor Md7 gets activated since, UP is high. Now, when FBCLK goes high, node D doesn’t go high as it gets discharged through transistor Md7. Hence, DN is zero throughout the operation. FH gets activated since FBCLK is high. As both the transistors Mu5 and Mu6 are activated simultaneously, U is discharged to zero. Thus, UP goes low.

Hence, in the operation of PFD beyond the dead zone region, no reset pulse is generated making the PFD blind zone free.

Case 2. In Fig. 4, when REFCLK goes high, UP goes high. Since, in the dead zone region, the phase difference between REFCLK and FBCLK is small, transistor Md7 doesn’t find enough time to discharge node D to zero. Thus, when FBCLK goes high, DN goes high. As the transistors Mu7 and Md7 are activated, UP and DN goes low.

Hence, in the operation of PFD in the dead zone region reset pulse is generated making PFD dead zone free.

3 Simulation Results

The proposed PFD is implemented in UMC 180 nm CMOS process. The proposed PFD consumes power of 65 \(\upmu \)W at an operating frequency of 100 MHz and 648 \(\upmu \)W when operated at frequency of 1 GHz. It is observed that the PFD is not sensitive to duty cycle variations of the REFCLK and FBCLK signals.

The timing diagram of the PFD is presented in Fig. 5 for a phase difference of 9.5 ns between the clocks.

It is observed that no signal is generated at the DN node as stated in the discussion.

The timing diagram of the PFD when REFCLK leads FBCLK by 2 ps is shown in Fig. 6. It is observed that the reset pulse is generated by the PFD when there is small phase difference.

In the proposed PFD, the reset pulse is generated within the dead zone region and is eliminated beyond the dead zone region. Thus, neither the dead zone nor the blind zone is present in the PFD designed in this work.

Figure 7 shows the PFD operation when REFCLK and FBCLK are in phase.

Figure 8 presents the UP and DN signals when REFCLK and FBCLK exhibits different frequencies.

The PFD is simulated across different process corners to obtain the PFD transfer curves as shown in Fig. 9. It is found that the PFD maintains its linearity across different process corners.

To analyse the PFD performance in the PLL loop, it is important to design a PLL using the PFD designed in this work. The simulation setup is shown in Fig. 10.

The PLL is designed to have an PLL OUTPUT of 1.6 GHz. The REFCLK frequency is considered as 100 MHz. The parameters of loop filter are chosen such that it has sufficient phase margin to maintain the stability of the overall PLL loop.

The conventional PFD is designed in UMC 180 nm process for the purpose of comparison. The locking of the PLL with the PFD designed in this work is shown in Fig. 11. It can be observed that the PLL locks with minimum steady state error between the UP and DN pulse which is caused due to the discrepancy between the source and sinking current of the next block, that is, CP.

The PLL is simulated using both the PFDs as shown in Fig. 12. It is observed that the PLL lock time using the novel PFD is 450 ns and using the conventional PFD is 790 ns.

The PFD designed in this paper is compared with the recent PFD designs as shown in Table 1. All the PFDs are operated at supply voltage of 1.8 V. It is observed that the PFD in [1] has an operating range of [\(-\pi \), \(\pi \)] which will severely affect the locking time of the PLL. Also, it has dead zone of 40 ps. Even though the PFD in [5] is free from dead zone and blind zone, it has an operating range of [\(-\pi \), \(\pi \)], thus leading to increase in lock time of the PLL.

In [7], the PFD architecture has an ideal operating range of [\(-2\pi \), 2\(\pi \)], but has a blind zone of 3 ps. The power consumed is 2600 \(\upmu \)W when operated at frequency of 100 MHz which is 97.5\(\%\) higher than that of the proposed PFD. In [4], the PFD is designed such that it is free from dead zone and blind zone. It has an operating range of [\(-2\pi \), 2\(\pi \)]. The power consumed is 1.36 mW which is 52.3\(\%\) higher than that of the proposed PFD. Thus, the PFD designed in this work has good performance when compared to the existing literatures.

4 Conclusion

In this paper, edge detector based PFD is designed and proposed. The reset pulse is not present in the PFD after the dead zone region, leading to a blind zone free PFD. The PLL using the proposed PFD acquires 43\(\%\) faster locking than with the conventional PFD. The power consumption is significantly reduced when compared to the existing literatures. Thus, the designed PFD is suitable for low power high speed applications.

References

Abolhasani, A., Mousazadeh, M., Khoei, A.: A high-speed, power efficient, dead-zone-less phase frequency detector with differential structure. Microelectron. J. 97, 104719 (2020)

Chen, W.H., Inerowicz, M.E., Jung, B.: Phase frequency detector with minimal blind zone for fast frequency acquisition. IEEE Trans. Circuits Syst. II: Express Briefs 57(12), 936–940 (2010)

Abdul Majeed, K.K., Kailath, B.J.: PLL architecture with a composite PFD and variable loop filter. IET Circuits Devices Syst. 12(3), 256–262 (2018)

Kuncham, S.S., Gadiyar, M., Sushmitha, D.K., Lad, K.K., Laxminidhi, T.: A novel zero blind zone phase frequency detector for fast acquisition in phase locked loops. In: 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), pp. 167–170. IEEE (2018)

Majeed, K.A., Kailath, B.J.: Low power, high frequency, free dead zone PFD for a PLL design. In: 2013 IEEE Faible Tension Faible Consommation, pp. 1–4. IEEE (2013)

Mansuri, M., Liu, D., Yang, C.K.: Fast frequency acquisition phase-frequency detectors for Gsamples/s phase-locked loops. IEEE J. Solid-State Circuits 37(10), 1331–1334 (2002). https://doi.org/10.1109/JSSC.2002.803048

Ravi, H., Mukherjee, J.: PFD with improved average gain and minimal blind zone combined with lock-in detection for fast settling PLLs. Microelectron. J. 116, 105233 (2021)

Soyuer, M., Meyer, R.G.: Frequency limitations of a conventional phase-frequency detector. IEEE J. Solid-State Circuits 25(4), 1019–1022 (1990)

Tak, G.Y., Hyun, S.B., Kang, T.Y., Choi, B.G., Park, S.S.: A 6.3-9-GHZ CMOS fast settling PLL for MB-OFDM UWB applications. IEEE J. Solid-State Circuits 40(8), 1671–1679 (2005). https://doi.org/10.1109/JSSC.2005.852421

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Divya, M., Sundaram, K. (2022). A Novel Blind Zone Free, Low Power Phase Frequency Detector for Fast Locking of Charge Pump Phase Locked Loops. In: Arunachalam, V., Sivasankaran, K. (eds) Microelectronic Devices, Circuits and Systems. ICMDCS 2022. Communications in Computer and Information Science, vol 1743. Springer, Cham. https://doi.org/10.1007/978-3-031-23973-1_8

Download citation

DOI: https://doi.org/10.1007/978-3-031-23973-1_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-23972-4

Online ISBN: 978-3-031-23973-1

eBook Packages: Computer ScienceComputer Science (R0)