Abstract

Based on the negative temperature characteristics of threshold voltage and positive temperature characteristics of a multiple of thermal voltage, adding them with proper weight coefficient A voltage reference circuit was proposed with a zero temperature coefficient (TC). The device consists of pure MOSFET operated in subthreshold region and uses no resistors and bipolar transistors. The triple-branch current reference structure is adopted for independence of supply voltage instead of cascade structure and embedded operational amplifier structure with the merit of chip area and power consumption. Simulation results showed that based on standard CMOS 0.18 um process, the circuit can operate at 0.75 V supply voltage with the output voltage only 563 mV. The TC of the voltage was 17.5 ppm/℃ in a range from −40 ℃–125 ℃. The line sensitivity was 569.5 ppm/V in a supply voltage range of 1.2 V–1.8 V, and the power supply rejection ratio (PSRR) was 66.5 dB at 100 Hz. The power dissipation was only 187.4 nW.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Voltage reference and current reference are the important part in analog and mixed signal integrated circuits, e.g. sensors, portable mobile devices and biomedical chip [1]. It can provide reference for other blocks so its characteristics directly affect the performance of all the system [2]. Traditional bandgap reference (BGR) circuit [3, 4] got the zero TC by weighting the negative temperature characteristics of base-emitter voltage of NPN bipolar transistor and positive temperature characteristics of thermal voltage [5], which produces a voltage that is basically independent of power supply voltage, process and temperature [6]. While the traditional circuit invoked operation amplifier structure or cascade structure to stabilize the voltage for improving the PSRR with the drawback of power dissipation and chip area, and also the noise and speed of the op-amp can affect the output voltage [7].

To solve above problems, a low power voltage reference circuit is proposed in this paper with all the MOSFETs working in the subthreshold region. To provide bias for the voltage reference a triple-branch current reference is developed with high PSRR. The circuit consists of all-CMOS devices without resistors and bipolar transistors so as to save the chip area and power consumption. Simulation results shows the benefits of the circuit.

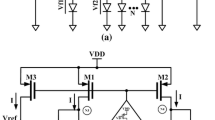

2 A Traditional Current Source

A typical circuit for generating the bias current independent of the power voltage is shown in Fig. 1 [7]. When the circuit is powered on, M5 provides the access from VDD to the ground through M3 and M1. The M5 can be turned off after the circuit was started up in order to avoid degenerate on the condition that \( V_{TH1} + V_{TH5} + \left| {V_{TH3} } \right| < V_{DD} \) and \( V_{GS1} + V_{TH5} + \left| {V_{GS3} } \right| > V_{DD} \). The output current of the circuit can be expressed as

Thus the reference current independent of the supply voltage is produced. In this block, with the fluctuating of power supply voltage, the drain voltages of M1 and M2 will change in opposite direction. So the transistors M3, M4, M1 and M2 constitute a positive feedback, and resistor Rs acts as the negative feedback of the circuit. On the whole this circuit presents a weak positive feedback loop, so the PSRR of the block will be relatively poor. In order to weaken the sensitivity of the reference current to the power supply voltage, a triple-branch current reference structure was proposed in literature [8] and [9], which constitute a negative feedback loop. In this circuit resistors was used to control the bias current, so the silicon area would be increased in order to get nanoampere current. In standard CMOS technology, not only the resistor model may be unavailable or unreliable, but also the resistors increase susceptibility of the reference to substrate noise coupling [10].

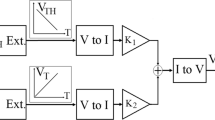

3 Improved Triple-Branch Current Reference

A novel current reference circuit which can increase the PSRR and weaken the sensitivity of the temperature is shown in Fig. 2. The triple-branch structure was adopted and the negative feedback loop was formed to restrain the variation of the power supply. When the power supply voltage VDD increases, the voltage VX decreases at the same time, and the voltage VB increases under the operation of NM2 as common-source amplifier. For the same reason, under the action of common-source NM1, the voltage of A point drops consequently. Thus, a negative feedback loop VX→VB→VA→VX is formed, so the PSRR of the circuit together with linear sensitivity are relatively high. When the voltage at X point increases, the current of I1, I2, Iout, Iref decreases, VY = (I1 + I2 + Iout)RNM5 + (I1 + I2 + Iout + Iref)RNM6 the voltage at Y point decreases rapidly, which makes the voltage at X point drop rapidly. The source of NM2 is connected with the drain of NM5 tube, which forms faster negative feedback loop. The resistor which control the magnitude of the reference current is replaced by NM5 that operates in the diode region. The NM5 gate-voltage is biased by the drain voltage of diode-connected NM4, the gate-source voltage of NM4 has a negative TC, and the drain-source voltage of NM5 has the positive TC, so the voltage of point Q which determines the current I2 can be weighted to zero TC. NM6 is used as big resistor to make the current stable. Such a structure can weaken the influence of temperature in the end.

In order to reduce the power consumption of the circuit, MOSFET is generally used to work in the subthreshold region in the nanoampere current reference. When \( V_{GS} \approx V_{TH} \) or \( V_{GS} \) slightly smaller than \( V_{TH} \), the current is expressed as follows [7]:

S is the aspect ratio of the transistor, I0 is the characteristic current, \( \xi \) represents the subthreshold slope factor, \( C_{ox} \) is the gate-oxide capacitance, \( V_{T} = KT/q \) is the thermal voltage, K is the Boltzmann constant, T is the absolute temperature, q is the elementary charge Vth is the threshold voltage of a MOSFET [11]. For \( V_{DS} > 0.1\;{\text{V}} \), current Id is almost independent of VDS and given by

NM1, NM2 and NM3 operate in the subthreshold region. According to the equation above, the current of NM1 and NM3 can be obtained:

PM6 and PM7 constitute a pair of current mirror structures, PM6 and PM7 have the same size, so \( I_{out} = I_{ref} \), the aspect ratios of NM3 is K times that of NM1, that is \( S_{\text{NM3}} = KS_{NM1} \), we get the formula:

According to the formula (4) and (6) can be obtained:

transistor NM5 operates in deep-triode region, so its resistance is given by

So the current reference can by written as

It can be seen from the above equation the output current depends on the aspect ratio of NM5. The voltage of Q point is easy to change with the temperature, and the current of I2 will also change accordingly. It can be obtained Iout, the voltage Iref changes with the temperature. Only if the voltage at the Q point is stable, the current Iref not change with the temperature be produced. According to the formula (6) and (7), we get:

From Eq. (14) it can be seen that the first term is the multiple of the thermal voltage which has the positive TC, and the second term is the threshold voltage of MOSFET which has a negative TC. Properly weighting, the VQ with zero TC can be derived, and the temperature effect on the reference current is weakened.

At the corner of ttssff, the output current varies versus supply voltage is shown in Fig. 3 and the temperature characteristic of output current is shown in Fig. 4. It can be seen that output current has slightly positive TC, and it can work normally when power supply is 0.75 V.

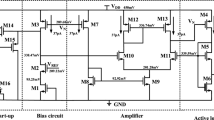

4 Voltage Reference Circuit

The bias voltage circuit is shown in Fig. 5. PM4, PM3, PM2, PM1 have the same aspect ratio and all work in saturation region in order to guarantee the same drain current (IP) of them. It can be seen that the gate-source voltage (from VGS8 to VGS15) of the transistors form a closed loop, and the current in M9, M11 and M13 are 4IP, 3IP and 2IP respectively. Therefore, we find that output voltage VREF of the circuit is given by

according to Eq. (3)

And Eq. (15) can be rewritten as:

where we assumed that the mismatch between the threshold voltage of the transistors can be ignored. Equation (17) shows that VREF can be expressed as a sum of the gate-source voltage VGS9 and thermal voltage VT scaled by the transistor sizes. Because VTH has a negative TC and VT has a positive TC, output voltage VREF with a zero TC can be obtained by adjusting the size of the transistors.

The entire circuit is illustrated in Fig. 6. It is composed of three blocks, which are start-up circuit, current source subcircuit and bias voltage subcircuit. A start-up circuit is used to avoid the stable state in the zero bias condition. When the power is on, PM10 works in the conducting state. Iin injects into the main circuit. At the same time, PM9 is on and MOS capacitor NM7 is charged, the voltage of PM10 gate increases gradually. At last PM10 cuts off and the start-up circuit separates from the main circuit.

5 Simulation Results and Comparison

The performance of our proposed circuit is verified with the aid of SPECTRE simulation using a set of 0.18 um standard CMOS press with 1.8 V power supply.

The TC of output voltage under different corner are shown in Fig. 7 respectively. It can be seen under corner of FF, the TC is 48.88 ppm/℃, with the mean output voltage 506.242 mV; under the corner of TT, the TC is 17.25 ppm/℃, with the mean output voltage 564.39 mV; under the SS corner, the TC is 23.48 ppm/℃, with the output voltage 626.516 mV. It is easy to see that output voltage varies greatly with different corner. Because the threshold voltage changes evidently under different corner, and output voltage of proposed circuit under zero TC is equal to the threshold voltage of the MOSFET at 0 K temperature. So more accurate process should be used in order to achieve excellent reference.

The output voltage exhibits good power independence. Figure 8 shows output voltage VREF at room temperature as a function of supply voltage under different corner. The circuit operates properly when supply voltage is higher than 0.75 V. The line sensitivity is 596.5 ppm/V in the power range of 1.2 V to 1.8 V under TT corner. Figure 9 shows the PSRR at room temperature with 1.8 V power supply. The PSRR is −66 dB@100 Hz, and the worst is −29 dB@63 kHz. At different corner, maximum deviation is less than 2 dB. Thus the voltage reference which is almost independent of temperature and supply voltage is achieved.

The noise characteristic is shown in Fig. 10. It can be seen that the noise is relatively larger in the low frequency band, about 4 uV/sqrt(Hz)@80 Hz. The circuit noise is mainly the flicker noise of MOSFET, which can be reduced by increasing size of MOSFET. It is easy to see the noise of output voltage is not affected under different corner.

Table 1 summarizes the characteristics of our circuit in comparison with other triple-branch structure CMOS voltage references reported in [7, 8, 12]. Our device is comparable to other circuits in PSRR, line sensitivity, and it is superior to other in TC and power consumption. Our circuit gives new improvement to the triple-branch structure circuits, so it is useful as a voltage reference for low power design.

6 Conclusions

A novel ultra-low power voltage reference circuit consist of all-CMOS transistors is developed in this paper. The circuit adopts improved triple-branch current reference structure instead of the traditional embedded operational amplifier and cascade structure. In addition, the circuit works at the subthreshold region in order to reduce the power consumption. The power rejection ratio and linearity of the circuit are improved while the power consumption and chip area are greatly reduced. Using a 0.18 um standard process, Simulation results show that power supply voltage can be as low as 0.75 V, the TC is about 17.5 ppm/℃, the linear sensitivity between 1.2 V to 1.8 V is 569.5 ppm/V, the output voltage is about 563.5 mV, and the PSRR is about −66.5 dB@100 Hz, the power consumption of the whole circuit is only 187.4 nW.

References

Lee, E.K.F.: Low voltage CMOS bandgap references with temperature compensated reference current output. In: IEEE International Symposium on Circuits and Systems, pp. 1643–1646. IEEE (2010)

Yue, M.: A 46.468 µW low-power bandgap voltage reference. In: IEEE International Conference on Computer Science and Information Technology, pp. 256–258. IEEE (2010)

Hua, L., Lüjian, Yadong, J.: A curvature-compensated CMOS bandgap voltage reference for high precision applications. Microelectronics 39(1), 38–41 (2009)

Wang, N., Wei, L.: A low-power high PSRR OMOS bandgap voltage reference. Microelectronics 34(3), 330–333 (2004)

Zhou, Q., et al.: High-PSRR high-order curvature-compensated CMOS bandgap voltage reference. J. Harbin Inst. Technol. 5, 116–124 (2015)

Wadhwa, S.K., Chaudhry, N.: High accuracy, multi-output bandgap reference circuit in 16 nm FinFet. In: International Conference on VLSI Design and 2017, International Conference on Embedded Systems, pp. 259–262. IEEE (2017)

Razavi, B.: Design of Analog CMOS Integrated Circuits. Xi’an Jiaotong University Press (2003)

Yi, W., He, L., Xiaolang, A.Y.: A 30 nA temperature-independent CMOS current reference and its application in an LDO. Chin. J. Semicond. 27(9), 1657–1662 (2006)

Xu, Y., Hu, W.: Design of a novel All-CMOS low power voltage reference source. Microelectronics 43(6), 742–746 (2013)

Buck, A.E., et al.: A CMOS bandgap reference without resistors. IEEE J. Solid-State Circ. 37(1), 81–83 (2002)

Wang, A., Calhoun, B.H., Chandrakasan, A.P.: Sub-threshold Design for Ultra Low-Power Systems. Series on Integrated Circuits & Systems. Springer, Heidelberg (2006). https://doi.org/10.1007/978-0-387-34501-7

Ueno, K., et al.: A 300 nW, 15 ppm/℃, 20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs. IEEE J. Solid-State Circ. 44(7), 2047–2054 (2009)

Acknowledgement

1. Project supported by the National Natural Science Foundation of China (Grant No. 61562074).

2. Project supported by the Guangxi University Science and Technology Research Project (Grant No. KY2015ZD123).

3. Guangxi Innovation Driven Development Special Fund Project.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 ICST Institute for Computer Sciences, Social Informatics and Telecommunications Engineering

About this paper

Cite this paper

Yu, J., Guo, H. (2019). Design of a 200-nW 0.8-V Voltage Reference Circuit in All-CMOS Technology. In: Jia, M., Guo, Q., Meng, W. (eds) Wireless and Satellite Systems. WiSATS 2019. Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering, vol 281. Springer, Cham. https://doi.org/10.1007/978-3-030-19156-6_12

Download citation

DOI: https://doi.org/10.1007/978-3-030-19156-6_12

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-19155-9

Online ISBN: 978-3-030-19156-6

eBook Packages: Computer ScienceComputer Science (R0)