Abstract

This paper presents dynamic voltage restorer (DVR) as a new compensation scheme for power quality improvements in terms of power factor correction and harmonic mitigation for a three-phase four-wire distribution system, supplying a star (Y) connected balanced R–L load. The DVR is a custom power device used to protect sensitive loads in power distribution systems from the most frequent voltage disturbances, such as sags, swells, imbalances, harmonics and low power factor. Indirect proportional integral controller and synchronous reference frame controller are used to generate switching patterns for the pulse width modulated controlled voltage source converter. The DVR system is implemented through extensive simulation using MATLAB software with its Simulink and power system blockset toolboxes. The proposed SRFC is compared with the IPIC scheme and the superior features of this novel approach are established in this research work.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Industrial and commercial consumers of electrical power are becoming increasingly sensitive to the quality of electrical power supply. When interruptions occur due to poor power quality problems, costs, including downtime, defects, and loss of production may occur. This would result in losses, in term of money to both commercial and domestic consumers. Therefore, the study of power quality problem is becoming a popular research topic. It has already been shown that for customers of large loads (from a high kVA to the low MVA range) good solutions are the installation of custom power devices (Ghosh and Ledwich 2002; Hingorani 1995). Dynamic voltage restorer (DVR) is one of the custom power devices for the power factor correction and harmonic mitigation. The DVR injects three-phase compensating voltages in series to the power line through a three-phase series transformer or three single-phase series transformers. The energy required for the compensation is taken from the dc capacitor (Al-Hadidi et al. 2008a) or another energy-storage element such as a double-layer capacitor, a superconducting magnet (Lamoree et al. 1994), or a lead-acid battery (Ramachandaramurthy et al. 2002). Otherwise it may be taken from the power system by the shunt converter (Wang and Venkataramanan 2009; Saleh et al. 2008). There are many control techniques that are used to compute the command voltage component, such as in (Vilathgamuwa et al. 2002) showed the open loop control strategy, closed-loop control (Etxeberria-Otadui et al. 2002; Ghosh and Joshi, 2002; Liu et al. 2002), multi-loop feedback control (Nielsen et al. 2001), selective harmonic closed loop control (Newman et al. 2003) and vector control (Awad et al. 2003). This paper proposes the indirect proportional integral and synchronous reference frame control scheme for improving dynamic performance of DVR specially power factor improvement. The performance of dynamic voltage restorer is illustrated with the help of case study comprising a three phase source supplied to the three phase star (Y) connected balanced R-L load (Padiyar 2007). A new topology of dynamic voltage restorer is proposed for a three-phase four-wire distribution system, which is based on three-leg voltage source converter and six-leg voltage source converter for the indirect proportional integral (IPI) and synchronous reference frame control scheme respectively. The voltage source converter compensates the harmonic voltage, reactive power, and improves the power factor on source side. The insulated gate bipolar transistor (IGBT) based voltage source converter is self-supported with a dc bus capacitor. Comparative assessments of the performance of DVR feeding linear loads, without DVR and with DVR are presented. After giving introduction in this Sect. 1, Sect. 2 describes different components of DVR system. Section 3 presents control strategies based on IPI and synchronous reference frame (SRF). Section 4, discusses a case study for the three-phase four-wire distribution system employing DVR as a power quality improvement device. In Sect. 5 performances have been analyzed from the obtained results under the condition for without DVR and with DVR and finally Sect. 6 concludes the paper.

2 Dynamic voltage restoration

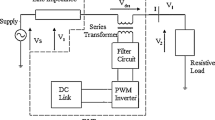

The configuration of a DVR is shown in Fig. 1. The DVR can inject a (fundamental frequency) voltage in each phase of required magnitude and phase. The DVR has two operating modes.

-

1.

Standby i.e. short circuit operation (SCO) mode where the voltage injected has zero magnitude.

-

2.

Boost i.e. DVR injects a required voltage of appropriate magnitude and phase to restore the prefault load bus voltage.

The power circuit of DVR is shown in Fig. 1 has four components listed below:

2.1 Voltage source converter (VSC)

VSC is commonly used to transfer power between a dc system and an ac system or back to back connections for ac systems with different frequencies, such as variable speed wind turbine systems (HU et al. 2008). A dc capacitor is connected on the dc side to produce a smooth dc voltage. The switches in the circuit are controllable semiconductors, such as insulated gate bipolar transistor (IGBT) or power transistors.

2.2 Boost or injection transformers

Three single phase transformers are connected in series with the distribution feeder to couple the VSC at the lower voltage level to the higher distribution voltage level. The three single transformers can be connected with star/open star winding or delta/open star winding. The choice of the injection transformer winding depends on the connections of the step down transformer that feeds the load.

2.3 Passive filters

The filtering scheme in the dynamic voltage restorer can be placed either on the high-voltage-side or the converter side of the series injection transformer. The advantage of the converter-side filter is that it is on the low-voltage side of the series transformer and is closer to the harmonic source. Using this scheme, the high-order harmonic currents will be prevented from penetrating into the series transformer thus reducing the voltage stress on the transformer.

2.4 Energy storage

Energy storage is required to provide real power to the load. The energy storage device used for this work is a DC capacitor which is connected to the DC side of VSC, carries input ripple current of the converter and is the main reactive energy storage element. This capacitor could be charged by a battery source or could be precharged by converter itself.

3 Control strategies

The major objectives of these control strategies are to ensure that the load bus voltages remain balanced and sinusoidal. Since the load is assumed to be balanced and linear, the load currents will also remain balanced and sinusoidal. An additional objective is to ensure that the source current remains in phase with the fundamental frequency component of the point of common coupling (PCC) voltage. In this work control strategies of indirect proportional integral controller (IPIC) and a novel approach of synchronous reference frame controller (SRFC) have been discussed.

3.1 Indirect PI controller

The controller input is an error signal obtained from the reference voltage and the rms value of the terminal voltage. Such error is processed by a PI controller; the output is the angle δ, which is provided to the pulse width modulation (PWM) signal generator. Figure 2 shows that an error signal is obtained by comparing the reference (set) voltage with the rms voltage measured at the load point. The PI controller processes the error signal and generates the required angle to drive the error to zero, i.e., the load rms voltage is brought back to the reference voltage (Kumar and Nagaraju 2007).

From Fig. 3 the sinusoidal signal Vcontrol is phase-modulated by means of the angle δ as:

The modulated signal Vcontrol is compared against a triangular signal in order to generate the switching signals for the VSC valves. The main parameters of the sinusoidal PWM scheme are the amplitude modulation index of signal, and the frequency modulation index of the triangular signal.

The amplitude index is kept fixed at 1 p.u., in order to obtain the highest fundamental voltage component at the controller output.

where \(\mathop {\text{V}}\limits^{\Uplambda }_{\text{control}}\) is the peak amplitude of the control signal, \(\mathop {\text{V}}\limits^{\Uplambda }_{\text{triangular}}\) is the peak amplitude of the triangular signal.

The switching frequency (fs) is set at 1,080 Hz. The frequency modulation index is given by,

where f1 is the fundamental frequency.

The modulating angle is applied to the PWM generators in phase A. The angles for phases B and C are shifted by 1200 and 2400 respectively. It can be seen that the control implementation is kept very simple by using only voltage measurements as the feedback variable in the control scheme. Figure 4 shows simulink model of DVR controller.

3.2 Proposed synchronous reference frame controller

The SRF control approach (Padiyar 2007) is used to generate the reference voltages for the DVR. Figure 5 shows the block diagram representation of SRF control scheme.

The PCC voltage VPa, VPb and VPc are transformed into d–q components using the following equations:

where ω 0 is the operating system frequency. The DC components in VPd and VPq are extracted by using a low pass filter. Thus

\(\overline{{{\text{V}}_{\text{Pd}} }}\) and \(\overline{{{\text{V}}_{\text{Pd}} }}\) are the DC components and G(s) is the transfer function of low pass filter. From Fig. 5 we derive the reference for the active component of the load voltage (V *Ld ) as:

where VCd is obtained as the output of the DC voltage controller (with a proportional gain Kp). A second order butterworth low pass filter is used in the feedback path of the DC voltage controller to filter out high frequency ripple in the DC voltage signal.In steady state, V *Pq = 0, therefore

Kq is chosen to optimize the controller response.

From the reference values of V *Ld and V *Lq we can obtain the desired load voltages in phase coordinates from the following equations:

Finally, the reference compensated voltages for the DVR are given by:

The detailed comparison of the proposed control strategy with the IPIC is given in Sect. 5.

4 Simulation of DVR: a case study

The voltage source converter based DVR connected to distribution system having a balanced load is taken up for study (Padiyar 2007). Table 1 depicts system data and system diagram is shown in Fig. 6. A DVR is connected in series with the linear load to improve the power factor on the source side i.e. at the point of common coupling. The balanced R-L load is star (Y) connected. Figure 7(a, b) is the power circuit of proposed three-leg and six-leg VSC based DVR integrated with three phase transformer. It contains full bridge converters connected to a common DC bus. The DC bus voltage is held by the capacitor Cdc. The function of dc capacitor Cdc is to produce a smooth dc voltage. The switches in the converter represent controllable semiconductors, such as IGBT or power transistors. The IGBTs are connected anti parallel with diodes for commutation purposes and for charging the DC capacitor. For converter the most important part is the sequences of operation of the IGBTs. PWM scheme is used to generate the pulses for the firing of the IGBTs. IGBTs are used in this work because it is easy to control the switch on and off of their gates and suitable for the DVR.

5 Simulation results and analysis

Figure 8a, b shows the basic simulation model of DVR system that correlates to the system configuration shown in Fig. 6 in terms of source, load, DVR, and control blocks. The injection transformer in series with the load, three-phase source, and the series-connected VSC are connected as shown in Fig. 8 (a, b). These DVR models are simulated with the indirect PI and SRFC theory. The models are assembled using the mathematical blocks of SIMULINK block set. Simulation is carried out in discrete mode at a maximum step size of 1 × 10−3 with ode45 (Domand-Prince) solver. The total simulation period is 1 s. There are three numbers of breakers used in these models for the purpose of DVR in operation with the distribution system. Figure 9 represents simulink model of SRF controller that is implemented from the block diagram of the SRF controller as in Fig. 5.

The main purpose of the simulation is to study two different performances of control aspects: (1) harmonic compensation and power factor correction by IPIC; (2) harmonic compensation and power factor correction by synchronous reference frame control. In addition, the Fast Fourier Transform (FFT) is used to measure the order of harmonics in the compensated voltage. The total harmonic distortion (THD) of the compensated voltage is measured without and with DVR for the both cases of control strategies. The system parameters used in these simulations are given in Table 1.

5.1 Harmonic compensation and power factor correction by IPIC

The simulation results of the DVR system with the IPIC are shown in Fig. 10, in which Vc is the compensated voltage, VL is the load voltage, IS is the supply current and Vdc is the dc link voltage. From the results it is observed that the compensated voltage Vc is pure sinusoidal indicating absence of harmonics and load voltage VL remains balanced and sinusoidal because of balanced R-L load. The waveform of three-phase supply current IS is also sinusoidal in nature and the DC link voltage Vdc remains constant i.e. 1.75 V.

Figure 11a, b shows the supply current iSa and fundamental frequency component of PCC voltage vPa in phase a. In case of without DVR as shown in Fig. 11a the waveform of supply current starts at t = 0.203 s but PCC voltage starts at t = 0.200 s, indicating a phase difference between supply current iSa and PCC voltage vPa and hence it is not possible to maintain unity power factor (no power factor correction occurs) but in case of with DVR, as shown in Fig. 11b the waveform of supply current iSa as well as PCC voltage vPa start for the same time at t = 0.200 s. Thus there is no phase difference between supply current and PCC voltage and hence it is possible to maintain unity power factor (power factor correction occurs).

Figure 12a, b shows the harmonic spectrum of the compensated voltage without and with DVR. It is observed that the THD of the compensated voltage is reduced from 27.17 % without DVR to 0.00 % with DVR and hence mitigating harmonics in the compensated voltage.

5.2 Harmonic compensation and power factor correction by synchronous reference frame control

The DVR is tested for harmonic reduction and power factor correction by connecting a balanced linear load. The waveforms of the compensated voltage (Vc), load voltage (VL), supply current (IS) and dc voltage (Vdc) are presented in Fig. 13 to demonstrate the filtering performance of the DVR. It is observed that compensated voltage Vc is not sinusoidal and also indicates availability of small harmonics. Load voltage VL remains balanced and sinusoidal. The waveform of three-phase supply current IS is also a pure sinusoidal wave. The DC link voltage Vdc remains constant near 398 V.

Figure 14a, b shows the supply current iSa and fundamental frequency component of PCC voltage vPa in phase a. In case of without DVR as shown in fig. 14a the waveform of supply current iSa starts at t = 0.2031 s but PCC voltage vPa starts at t = 0.2000 s. This indicates a phase difference between supply current iSa and PCC voltage vPa and hence it is not possible to achieve unity power factor (no power factor correction occurs) but when the DVR is in operation with the distribution system, the waveform of supply current iSa as well as PCC voltage vPa start for the same time at t = 0.2000 s as shown in Fig. 14b. Thus there is no phase difference between supply current iSa and PCC voltage vPa and hence it is possible to achieve unity power factor (power factor correction occurs).

Figure 15a, b shows the compensated voltage spectrum without and with DVR. The corresponding THD of the compensated voltage is reduced from 32.92 % without DVR to 3.84 % with DVR

Thus the fast fourier transform (FFT) analysis of the DVR confirms that the THD of the compensated voltage is less than 5 % for the both cases of control strategies that are in compliance with IEEE-519 and IEC 61000-3 harmonic standards.

From Table 2 it is clear that with DVR, the THD of compensated voltage is 0.00 % for the case of IPIC, indicating completely elimination of harmonics, which is not practically possible but in case of Synchronous Reference Frame Control (SRFC), THD of compensated voltage is 3.84 % indicating less than 5 % of THD value, which is acceptable for three phase four wire distribution system hence proposed SRFC gives better performance in terms of harmonic compensation as compared to IPIC.

6 Conclusion

The modeling and simulation of a new topology of dynamic voltage restorer integrated with three phase linear transformer has been carried out and the performances have been demonstrated for power factor correction and harmonic reduction. The dynamic voltage restorer is implemented with pulse width modulated controlled voltage source converter. The converter switching patterns are generated from IPIC and SRFC. It has been shown that the system has a fast dynamic response and is able to keep the total harmonic distortion of the compensated voltage below the limits specified by the IEEE 519 and IEC 61000-3 harmonic standards. The DVR employing the proposed control strategies have been found suitable for star connected balanced R-L load. The results from the system simulation demonstrate the effectiveness of the DVR in providing balanced, sinusoidal voltages at the load bus.

References

Al-Hadidi HK, Gole AM, Jacobson DA (2008a) A novel configuration for a cascade inverter based dynamic voltage restorer with reduced energy storage requirements. IEEE Trans Power Delivery 23(2):881–888

Awad H, Svensson J, Bollen M H(2003) Static series compensator for voltage dips mitigation. In: IEEE Bologna PowerTech Conf, Bologna

Etxeberria-Otadui I, Viscarret U, Bacha S, Caballero M, Reyero R(2002) Evaluation of different strategies for series voltage sag compensation. In: Conf Rec IEEE PESC, pp. 1797-1802

Ghosh A, Joshi A (2002) A new algorithm for the generation of reference voltage of a DVR using the method of instantaneous sysmmetrical components. IEEE Power Eng Rev 22(1):63–65

Ghosh A, Ledwich G (2002) Power quality enhancement using custom power devices. Kluwer Academic Publishers, Norwell

Hingorani NG (1995) Introducing custom power. IEEE Spectr 32(6):41–48

Hu Y, Chen Z, McKenzie H (2008) Voltage source converters in distributed generation systems. DRPT, Nanjing

Kumar SVR, Nagaraju SS (2007) Simulation of D-STATCOM and DVR in power systems. ARPN J Eng Appl Sci 2(3):7–13

Lamoree J, Tang L, DeWinkel C, Vinett P (1994) Description of a micro-SMES system for protection of critical customer facilities. IEEE Trans Power Delivery 9(2):984–991

Liu JW, Choi SS, Chen S (2002) Design of step dynamic voltage regulator for power quality enhancement. IEEE Trans Power Delivery 18(4):1403–1409

Newman M J,Holmes D G,Nielsen J G, Blaabjerg F (2003) A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level. In: Conf Rec. IEEE IAS, pp. 1228-1235

Nielsen JG, Blaabjerg F, Mohan N (2001) Control strategies for dynamic voltage restorer compensating voltage sags with phase jump. Appl Power Electron Conf Exposition 2:1267–1273

Padiyar KR (2007) FACTS controllers in power transmission and distribution. New age publishers, Bangalore

Ramachandaramurthy VK, Fitzer C, Arulampalam A, Zhan C, Barnes M, Jenkins N (2002) Control of a battery supported dynamic voltage restorer. Proc Inst Electr Eng-Generat Trans Distrib 149(5):533–542

Saleh SA, Moloney CR, Rahman MA (2008) Implementation of a dynamic voltage restorer system based on discrete wavelet transforms. IEEE Trans Power Delivery 23(4):2366–2375

Vilathgamuwa DM, Perera AADR, Choi SS (2002) Performnance improvement of the dynamic voltage restorer with closed-loop load voltage and current-mode control. IEEE Trans On Power Electron 17(5):824–834

Wang B, Venkataramanan G (2009) Dynamic voltage restorer utilizing a matrix converter and flywheel energy storage. IEEE Trans Indust Appl 45(1):222–231

Acknowledgments

The authors are thankful to Ministry of Human Resources Development (MHRD), New Delhi, Govt. of India and All India council of Technical Education (AICTE), for providing financial assistants and supports to do the research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, P., Kumar, N. & Akella, A.K. Six leg DVR topology for compensation of balanced linear loads in three phase four wire system. Int J Syst Assur Eng Manag 5, 524–533 (2014). https://doi.org/10.1007/s13198-013-0201-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13198-013-0201-6