Abstract

We present a MMI-based photonic crystal all-optical logic gate structure for logic functions such as XNOR, XOR, OR and NAND with square-type lattice of Si rods in air host. Phase-based logic inputs produce intensity-based logic outputs with high contrast ratio. The calculated ON to OFF contrast ratio for the logic functions XNOR/XOR and OR/NAND is 40.41 and 37.40 dB, respectively. Further, it is improved by 11.53 and 12.46% for XNOR/XOR and OR/NAND logic functions, respectively, by reducing the back reflection with the introduction of absorbing waveguides. The structure in both the forms has a fast response period that is less than or equal to 0.131 ps. The size of the structure is quite compact with dimension \(6.4\,\upmu \hbox {m} \times 8.8\,\upmu \hbox {m}\).

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Photonic crystal-based logic devices have attracted the major interest of the researchers because of the capability of the photonic crystals in controlling electromagnetic waves due to photonic bandgaps [1]. These devices consist of an advantage of having compact size and high speed [2,3,4]. These are the unique features which lead to miniaturization and large-scale integration of high-speed optical devices in optical computing and networking systems. In recent years, the logic gates which are the basic elements in providing the logical and arithmetic operations in any computing system have been designed using photonic crystals. It is a versatile platform for the design of devices with dimensions of few wavelengths of light being confined and also with unique properties such as high speed, compactness, low power consumption and better confinement. Various techniques have been used in implementing optical logic gates in order to increase the speed as it is the basic property of the optical signal, but photonic crystal-based designs have their own position with convincing output performance. Several phenomena have been used in implementing logic gates based on photonic crystals. Few of them are interference [2, 3, 5,6,7,8,9,10], self-collimation effect [11, 12], resonance [4, 13,14,15], and also the combination of both the resonance and interference phenomena [16]. Under the interference phenomena, the photonic crystal logic gates based on multi-mode interference (MMI) have occupied the superiority in providing high contrast ratio with compact size [8, 9].

MMI devices are the important parts of photonic integrated circuits due to low loss, low polarization dependence and large optical bandwidth [17]. These structures have found many applications in wavelength multiplexers/demultiplexers [18], optical switches [19], logic gates [20], polarization beam splitters [21], power splitters [17]. MMI devices designed using photonic crystal waveguides are much smaller than the conventional MMI devices due to large dispersion in photonic crystals [17]. Recently, MMI waveguides were used to realize the logic gates wherein the input logic is the phase of the light. The logic gate that uses the phase of the light as input logic can be applied to design processing systems for phase-shift-keyed modulations [22]. The MMI-based photonic crystal logic gates for BPSK signals are reported with high contrast ratio [8, 9]. Furthermore, these logic gates are designed with triangular lattice and with bend waveguides. Edge rods in these structures are optimized to get efficient output which increases the fabrication complexity.

In this article, we proposed a MMI-based logic gate structure with cylindrical Si rods in square-type lattice. The contrast ratio of the logical functions performed by the proposed structure is high compared to the triangular lattice-based MMI logic gates [7,8,9]. Further, common radius is being maintained for all the rods which will make an ease in fabrication. The back reflection in this structure is a setback which should be reduced. In this regard, the proposed structure is modified with absorbing waveguides (AWs) to reduce the back reflection which also improves the contrast ratio. The logic gate structure without absorbing waveguides provides a contrast ratio of 40.41 and 37.40 dB for functions XNOR/XOR and OR/NAND, respectively. The logic gate structure with absorbing waveguides, by reducing the back reflection, improves the contrast ratio by 11.53 and 12.46% for the functions XNOR/XOR and OR/NAND, respectively. The remaining part of this article is structured as follows. The logic gate structure and its operating principle is described in Sect. 2, followed by results and discussion on the logic gate functions in Sect. 3. The modified structure with absorbing waveguides is discussed in Sect. 4, and finally, it is concluded in Sect. 5.

2 Design of logic gate structure and operating principle

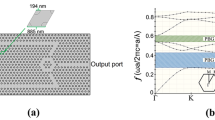

The logic gate structure is composed of an array of 11 \(\times \) 15 cylindrical rods of Si material with waveguides created for input and output ports along with a W5-waveguide as shown in Fig. 1. W5 stands for a photonic crystal waveguide in which 5 rows of dielectric rods are removed along the \(\Gamma \)-K direction of the crystal. It consists of two input ports, A and B as well as an output port Y. The dielectric constant of the Si rod is 3.46 with the radius (r) of 0.2a where a is the lattice constant of value 600 nm. The band diagram of the lattice structure and the dispersion diagram of the W5 waveguide are calculated using plane wave expansion (PWE) method and are shown in Fig. 2a and b. The band diagram shows that three photonic bandgaps are available in the structure wherein two are for TE mode and one is for TM mode. Among them, a band with TE mode, ranging from 0.282568 \((a/\lambda )\) to 0.416924 \((a/\lambda )\), is chosen as it is suitable for optical telecommunication window. The dispersion diagram shows that the W5-waveguide supports four guided modes and these are fundamental mode, first-order mode, second-order mode and third-order mode. Thus, the W5 waveguide is also called as multi-mode interference (MMI) waveguide, as it supports the multiple modes.

MMI devices are based on the self-imaging property by which the guided modes are excited in the MMI region when a small input field is launched and these modes are constructively interfered with each other. Further, these excited modes in the MMI region transmutes periodically along the direction of propagation. The coupling length \(L_\mathrm{c}\) between the fundamental mode and the nth mode is given as [7]

where \(\beta _{0}\) and \(\beta _{n }\) are the propagation constants of the fundamental and the nth order modes, respectively. As shown in Fig. 2b, the working point is chosen to be at \(a/\lambda _{0} = 0.387\), where \(\lambda _{0 }\) is the working wavelength of the light, i.e., 1550 nm. Four guiding modes can be observed at this frequency. The corresponding parameters related to these modes are calculated at the working frequency same as in [17] and are listed in Table 1. In order to get a proper outcome with a small MMI region, fundamental mode and the second-order modes are chosen, i.e., coupling length \(L_\mathrm{c }= 6\hbox {a} \) (nearly 5.88a). Figure 2c shows that this coupling length provides a twofold image of the input in a single-input W5 waveguide and a single image of the input in a two input W5 waveguide. As the waveguide is symmetric and the exciting field enters at the center, i.e., at \(z = 0\) (top of Fig. 2c), two even modes, the fundamental mode and the second-order mode will be excited and the position of first twofold image obtained is at 6a. Similarly, when exciting field enters from both the input waveguides (bottom of Fig. 2c), a single image is obtained at the same coupling length. This coupling length of 6a allows the structure (two input W5 waveguide) shown in Fig. 2c to provide a highly desirable output power level for logic-0 and logic-1 with proper input phase variation if the structure is ended with output waveguide at the center. Further the single-input W5 waveguide with coupling length of 6a allows it to be utilized as beam splitter. Thus, the MMI region of the proposed logic gate structure is set to 6a.

In the proposed logic gate structure, the logical functioning is determined by the phase values of the input light. The phase difference between the input light beams allows the guided modes to be interfered constructively with each other or cancelled out to provide the output. The intensity at the output will determine the type of the output logic. Thus, in this structure, the input logic values are determined by the signal phase, whereas the output logic values are determined by the light intensity at the output port. The phase values of the input light signals chosen for the logic gates are given in Table 2. In this table, the phase equivalent of the input binary logic (i.e., logic-0 and logic-1) can be observed for the four logic functions, XNOR, XOR, OR and NAND. As we can observe from the logic value (phase) of the input light beams, the phase difference between the input beams is either 0, \(\pi \) or \({n}\pi /2\) where n = 1,3,5,...

The phase difference at the input creates different interference patterns of the guided modes. The single image and the multiple images of the light occur alternatively, when the inputs have the same phase, i.e., the phase difference between the input light signals is zero. At a distance of 6a from the starting of the MMI waveguide, a single image with higher intensity appears at the center which allows a high-intensity signal to come out of the port Y. When the input light beams have a phase difference of \(\pi \), these light beams propagate sinusoidally along the two sides of the MMI waveguide but never interfere with each other. The light waves which propagate sinusoidally toward the output will get re-circulated back to the respected input ports as they do not interfere with each other and as a result of which a negligible amount of light intensity appears at the output port Y. When the phase difference is \({n}\pi /2\), the light from both the input ports superimposes at that end of the MMI region whose port provides a light which is lagged by a phase of \(\pi /2\) than the other. A light intensity of nearly same as the applied input will reach the output port Y. The remaining light will be re-circulated back into the same input port which is lagged by a phase of \(\pi /2\) than the other. Input phase values of the proposed structure create one among these phase differences in order to derive the required output logical function. The ON to OFF contrast ratio of the photonic crystal-based all-optical logic gates can be calculated using

where \(P_{1}\) is the power level of logic-1 and \(P_{0 }\) is the power level of logic-0. Most precisely, achieving a high value of the contrast ratio depends on the power level of logic-0 than logic-1. A minute change in the power level of logic-0 highly changes the contrast ratio. All the logical functions that are being realized consist of a negligible power value of logic-0. Thus, a high contrast ratio is achieved with the proposed logic gate structures compared to the existing MMI-based logic gates.

3 Results and discussion

Simulation has been done on the proposed logic gate structure using finite difference time domain (FDTD) method by applying the light input at a wavelength of 1550 nm. In realizing XNOR and XOR logical functions, the phase value of the light beams at the input ports of the structure can be observed from Table 2. As it can be observed from the phase values, the phase difference between the inputs is either 0 or \(\pi \) for XNOR and XOR logical functions. For the input combinations with the phases \(\varphi _{1} = \varphi _{2} = 0\) or \(\pi \), the phase difference \(\varphi _{d}= \varphi _{1}- \varphi _{2 }= 0\) allows the major part of the light to concentrate at the center, and hence a high output power of 1.76 \(P_\mathrm{a}\) is observed at the port Y, as illustrated in Fig. 3a, where \(P_\mathrm{a}\) is the input applied at ports, A and B. For the input combination with the phases \(\varphi _{1} = 0\) and \(\varphi _{2}= \pi \) or \(\varphi _{1}= \pi \) and \(\varphi _{2}= 0\), the phase difference, \(\varphi _{d}= \pi \), allows the light to propagate at the sides of the MMI region by leaving a very low power of 0.00016 \(P_\mathrm{a}\) at the output port Y. The dielectric rods at the right end of the MMI region re-circulate the propagating light back into the input ports. These outgoing waves into the input ports are harmful to the stability of the system [3]. The amount of light that is re-circulated to each of the input is more than 1.4 \(P_\mathrm{a}\) as illustrated in Fig. 3b. The blue, red and green colored curves that are observed in Fig. 3 indicate the output response, power reflected back to port A and power reflected back to port B, respectively. As the output at port Y is nearly zero (0.00016 \(P_\mathrm{a})\) for \(\varphi _{d}= \pi \), the output curve coincides with x-axis. The summary on the output power for XNOR and XOR logic functions is given in Table 3. The calculated value of ON to OFF contrast ratio of the XNOR gate as well as the XOR gate is 40.41 dB.

In OR and NAND gates, the phase value of the inputs applied at ports A and B describes that the phase difference of 0, \(\pi \) and \({n}\pi /2\) between the inputs provides an output for OR and NAND functions. The output response of the structure at phase differences of 0 and \(\pi \) is same as in the XNOR and XOR functions. But for the input combinations with phases \(\varphi _{1}= 0\) and \(\varphi _{2}= -\pi /2\) or \(\varphi _{1}= -\pi /2\) and \(\varphi _{2}= \pi \), the phase difference \(\varphi _{d}= {n}\pi /2\) provides the output power of 0.88 \(P_\mathrm{a}\) at the port Y. Some amount of power is re-circulated back to the input port whose input is lagging by the phase of \(\uppi /2\) and the re-circulated power is more than 1.35 \(P_\mathrm{a }\) as it is shown in Fig. 4. At the other input of the gate, the re-circulated power is 0.365 \(P_\mathrm{a}\). Though the output power for the input combinations with \({n}\pi /2\) phase difference is less compared to the combinations with \(\pi \) phase difference, the ON to OFF contrast ratio is still high with value 37.40 dB. This is due to the negligible output power obtained at port Y as logic-0 for the other input combination with \(\varphi _{d}= \pi \). Table 4 gives the summary on the output of the structure for OR and NAND logic functions. The optical field distribution of the proposed structure for XNOR, XOR, OR and NAND functions is illustrated in Fig. 5.

The response period of the proposed structure, which purely depends on the linear material, is calculated from the time evolving curve [3] shown in Fig. 6. The time (T) required for the structure to provide 90% of the average output power \(P_{\hbox {avg}}\) from 0% is 0.066 ps \((\hbox {cT} = 19.8\, \upmu \hbox {m})\), in this case. This time consists of two components: the transmission delay \((t_{11} = 0.0334 \hbox { ps})\) to reach 0.1% of \(P_{\hbox {avg}}\) and another component is the time required to reach 90% of the \(P_{\hbox {avg}}\) from 0.1%, i.e., \(t_{12}\) = 0.0326 ps. Since the system is based on the linear material, it can be expected that the falling time to move from \(P_{\hbox {avg}}\) to10% of \(P_{\hbox {avg}}\) is approximately equal to \(t_{12}\) [3]. It means a narrow pulse width of \(2t_{12}\) is produced as ON period of output with 50% duty cycle and hence the response period becomes equal to 0.1304 ps \((2 \times \) ON period). Thus, the proposed structure can operate at the bit rate of 7.67 Tbps, which is the reciprocal of the response period. This is the maximum bit rate that the proposed structure can support when the frequency of the applied input bit patterns is equal to or less than 7.67 Tbps.

As compared to the existing MMI-based logic gates reported so far, the contrast ratios of the proposed logic gate structure for XNOR/XOR/OR/NAND logic functions are very high with a fast response period. Furthermore, the dimensions of the edge rods are not required to change in order to improve the contrast ratio unlike the existing MMI-based logic gates with triangular lattice structure [7,8,9]. Apart from this, the size of the proposed logic gate structure based on the values of radius of the Si rod and the lattice constant is quite compact with dimension \(6.4\, \upmu \hbox {m} \times 8.8\, \upmu \hbox {m}\) compared to the existing [7,8,9]. The structural design of the proposed gate makes ease of fabrication too as it uses square lattice with circular rods without any modification of the rod’s radius. Further, the contrast ratio is nearly stable in the entire optical C-band with a little bit variation of less than 1 dB from the value at 1550 nm and it can be clearly observed from Fig. 7.

In the MMI-based logic gate structure discussed above, apart from providing the high contrast ratio and a fast response period as it was discussed earlier, this structure severely suffers from back reflection. This should also be taken into care to avoid the back reflection into the input ports. So, in the proposed logic gate structure, extra waveguides have been created in order to absorb some part of the light reflecting back from the walls of the output waveguide. These waveguides are called as the absorbing waveguides, which prevent the light to reflect back into the input ports. The structural modification that has been carried out on the proposed structure and the results obtained for the logic functions as well as the reduction in the power reflected back is discussed in the following section.

4 Logic gate structure with absorbing waveguides

The proposed MMI-based logic gate structure explained in the last two sections undergoes a severe problem of back reflection, which is about \(1.45 P_\mathrm{a}\) when the phase difference between the inputs is \(\pi \). When the phase difference is \({n}\pi /2\), the back reflection into the input ports is \(1.34\, P_\mathrm{a}\) and \(0.36\, P_\mathrm{a}\), whereas it is 0.26 \(P_\mathrm{a}\) into both the ports when the phase difference is 0. This back reflection is due to the light that hits the Si rods in the output side and forms the standing waves which re-circulates back. In order to reduce the back reflection, the structure is modified by creating the absorbing waveguides in the proposed logic gate structure at the top and the bottom of the output side of the MMI region as illustrated in Fig. 8. These waveguides absorb the light which tries to re-circulate back after hitting the output side of the MMI region and protects the input port from getting back reflection. Due to these waveguides, the back reflection into the input ports is reduced below 0.05 \(P_\mathrm{a}\).

This type of design of logic gate structure with absorbing waveguides also increases the contrast ratio compared to the previous structure. The ON to OFF contrast ratio of this logic gate structure with absorbing waveguides for XNOR/XOR function is 45.07 dB, whereas for OR/NAND function, it is 42.06 dB. When the phase difference between the inputs is \(\pi \), the light from the inputs passes at both the edges of the MMI region without superimposing each other and they are absorbed by the AW waveguides instead of re-circulating back into the input ports. Similarly, when the input phase difference is \(n\pi /2\), the light from both the input ports superimposes with each other at one end of the MMI region and most of the light nearly 1.27 \(P_\mathrm{a}\) is absorbed by the AW waveguide at that side. Less amount of power around 0.485 \(P_\mathrm{a}\) reaches the output port Y, which is considered as logic-1. The summary on the output power levels of the logical functions at different input combinations is given in Table 5.

As illustrated in Fig. 9, the back reflections are completely eliminated (less than 0.05 \(P_\mathrm{a})\) which are indicated by green and red colored curves, and this is due to the absorbing waveguides AW1 and AW2. The blue colored curve observed in all the three graphs indicates the output which is above 0.48 \(P_\mathrm{a}\) at \(\varphi _{d}= 0\) and \(\varphi _{d}= n\pi /2\) to represent logic-1 as shown in Fig. 9a and c, whereas in Fig. 9b, the output is as quite negligible as it coincides with the x-axis to represent logic-0 due to \(\varphi _{d}= \pi \). But the light absorbed by these waveguides will have a severe effect if these are not utilized or manipulated properly. The output from these waveguides can be used in the application wherever high-intensity and low-intensity light signals are required other than the reference input. The optical field distribution in this modified structure can be observed from Fig. 10.

From the time evolving curve shown in Fig. 11, the time (T) required to reach from 0 to 90% of the average output power \(P_{avg}\) is 0.0617 ps \((\hbox {cT} = 18.5\, \upmu \hbox {m})\). The two components of T, the transmission delay \((t_{11})\) and the time \((t_{12})\) required to move from 0.1 to 90% of the \(P_{avg }\) are calculated from the time evolving curve and their values are 0.032 ps and 0.0297 ps, respectively. From the value of \(t_{12}\), the response period is equal to 0.1188 ps and hence the proposed structure can operate at the bit rate of 8.42 Tbps.

The performance of the modified logic gate structure is better than the structure discussed previously with respect to the contrast ratio and response period, and further it can reduce the back reflection entering into the input ports. For the entire C-band, the contrast ratio of this modified structure is nearly constant with a variation of less than 2 dB as illustrated in Fig. 12 and it is quite better than the structure without absorbing waveguides at 1550 nm. Both the proposed basic and the modified structures are offering high contrast ratio than the other logic gates based on different techniques existing so far including the MMI-based structures. Furthermore, the optimization of the dielectric rods for achieving better performance is not necessary unlike other triangular lattice-based MMI logic gates [7,8,9].

5 Conclusion

In this article, we proposed a photonic crystal logic gate structure based on multi-mode interference with square-type lattice of Si rods in air background. Phase-based inputs provide intensity-based output with high contrast ratio for XNOR, XOR, OR and NAND logic functions. In order to avoid the back reflection into the input ports, the proposed structure is modified by creating the absorbing waveguides. The basic logic gate structure provides a contrast ratio of 40.41 and 37.40 dB for XNOR/XOR and OR/NAND logic functions, respectively, at 1550 nm, which has been improved further by 11.53 and 12.46%, with the introduction of absorbing waveguides in the structure. The response period of both the structures is less than or equal to 0.131 ps. The performance of the proposed structure with and without modification ensures that it can be potentially applied in the design of photonic integrated circuits.

References

Joannopoulos, J.D., Johnson, S.G., Winn, J.N., Meade, R.D.: Photonic Crystal: Molding the Flow of Light. Princeton University Press, Princeton (1995)

Rani, P., Yogita, K., Sinha, R.K.: Realization of AND gate in Y-shaped photonic crystal waveguide. Opt. Commun. 298–299, 227–231 (2013)

Wu, C.J., Liu, C.P., Ouyang, Z.: Compact and low-power optical logic NOT gate based on photonic crystal waveguides without optical amplifiers and nonlinear materials. Appl. Opt. 51, 680–685 (2012)

Younis, R.M., Areed, N.F.F., Obayya, S.S.A.: Fully integrated AND and OR optical logic gates. IEEE Photonics Technol. Lett. 26, 1900–1903 (2014)

Zahra, M., Najmeh, N., Farzin, E.: High contrast all-optical logic gates based on 2D nonlinear photonic crystal. Opt. Commun. 355, 130–136 (2015)

Zhu, Z.-H., Ye, W.-M., Ji, J.-R., Yuan, X.-D., Zen, C.: High-contrast light-by-light switching and AND gate based on non-linear photonic crystals. Opt. Express 14, 1783–1788 (2006)

Ishizaka, Y., Kawaguchi, Y., Saitoh, K., Koshiba, M.: Design of ultra compact all-optical XOR and AND logic gates with low power consumption. Opt. Commun. 284, 3528–3533 (2011)

Chunrong, T., Dou, X., Lin, Y., Yin, H., Wu, B., Zhao, Q.: Design of all-optical logic gates avoiding external phase shifters in a two-dimensional photonic crystal based on multi-mode interference for BPSK signals. Opt. Commun. 316, 49–55 (2014)

Liu, W., Yang, D., Shen, G., Tian, H., Ji, Y.: Design of ultra compact all-optical XOR, XNOR, NAND and OR gates using photonic crystal multi-mode interference waveguides. Opt. Laser Technol. 50, 55–64 (2013)

Enaul haq, S., Nakkeeran, R.: Design of photonic crystal based all-optical AND gate using T-shaped waveguide. J. Modern Opt 63, 941–949 (2015)

Zhang, Y.L., Zhang, Y., Li, B.J.: Optical switches and logic gates based on self- collimated beams in two dimensional photonic crystals. Opt. Express 15, 9287–9292 (2007)

Christina, X.S., Kabilan, A.P.: Design of optical logic gates using self-collimated beams in 2D photonic crystal. Cryst. Photonic Sens. 2, 173–179 (2012)

Nirmala, M.D., Vincent, M.: Interference based square lattice photonic crystal logic gates working with different wavelengths. Opt. Laser Technol. 80, 214–219 (2016)

Bao, J., Xiao, J., Fan, L., Li, X., Hai, Y., Zhang, T., Yang, C.: All-optical NOR and NAND gates based on photonic crystal ring resonator. Opt. Commun. 329, 109–112 (2014)

Ghadrdan, M., Mansouri-Birjandi, M.A.: Concurrent implementation of all-optical half-adder and AND & XOR logic gates based on nonlinear photonic crystal. Opt. Quantum Electron. 45, 1027–1036 (2013)

Salmanpour, A., Mohammednejad, S., Bahrami, A.: All-optical photonic crystal AND, XOR and OR logic gates using nonlinear Kerr effect and ring resonators. J. Moder. Opt. 62, 693–700 (2015)

Liu, T., Zakharian, A.R., Fallahi, M., Moloney, J.V., Mansuripur, M.: Multimode interference-based photonic crystal waveguide power splitter. J. Lightwave Technol. 22, 2842–2846 (2004)

Paiam, M.R., Janz, C.F., MacDonald, R.I., Broughton, J.N.: Compact planar 980/1550 nm wavelength multi/demultiplexer based on multimode interference. IEEE Photonics Technol. Lett. 7, 1180–1182 (1995)

Jia, X., Luo, S., Cheng, X.: Design and optimization of novel ultra-compact SOI multimode interference optical switch. Opt. Commun. 281, 1003–1007 (2008)

Li, Z., Chen, Z., Li, B.: Optical pulse controlled all-optical logic gates in SiGe/Si multimode interference. Opt. Express 13, 1033–1038 (2005)

Lu, M.-F., Liao, S.M., Huang, Y.-T.: Ultracompact photonic crystal polarization beam splitter based on multimode interference. Appl. Opt. 49, 724–731 (2010)

Xu, J., Zhang, X., Zhang, Y., Dong, J., Liu, D., Huang, D.: Reconfigurable all-optical logic gates for multi-input differential phase-shift keying signals: design and experiments. J. Lightwave Technol. 27, 5268–5275 (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Shaik, E.h., Rangaswamy, N. Multi-mode interference-based photonic crystal logic gates with simple structure and improved contrast ratio. Photon Netw Commun 34, 140–148 (2017). https://doi.org/10.1007/s11107-016-0683-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11107-016-0683-7