Overview

Access this book

Tax calculation will be finalised at checkout

Other ways to access

About this book

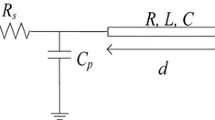

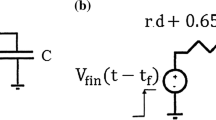

On-Chip Inductance in High Speed Integrated Circuits deals with the design and analysis of integrated circuits with a specific focus on on-chip inductance effects. It has been described throughout this book that inductance can have a tangible effect on current high speed integrated circuits. For example, neglecting inductance and using an RC interconnect model in a production 0.25 mum CMOS technology can cause large errors (over 35%) in estimates of the propagation delay of on-chip interconnect. It has also been shown that including inductance in the repeater insertion design process as compared to using an RC model improves the overall repeater solution in terms of area, power, and delay with average savings of 40.8%, 15.6%, and 6.7%, respectively.

On-Chip Inductance in High Speed Integrated Circuitsis full of design and analysis techniques for RLC interconnect. These techniques are compared to techniques traditionally used for RC interconnect design to emphasize the effect of inductance.

On-Chip Inductance in High Speed Integrated Circuits will be of interest to researchers in the area of high frequency interconnect, noise, and high performance integrated circuit design.

Similar content being viewed by others

Keywords

Table of contents (14 chapters)

-

Front Matter

-

Back Matter

Authors and Affiliations

Bibliographic Information

Book Title: On-Chip Inductance in High Speed Integrated Circuits

Authors: Yehea I. Ismail, Eby G. Friedman

DOI: https://doi.org/10.1007/978-1-4615-1685-9

Publisher: Springer New York, NY

-

eBook Packages: Springer Book Archive

Copyright Information: Kluwer Academic Publishers 2001

Hardcover ISBN: 978-0-7923-7293-6Published: 28 February 2001

Softcover ISBN: 978-1-4613-5677-6Published: 23 October 2012

eBook ISBN: 978-1-4615-1685-9Published: 06 December 2012

Edition Number: 1

Number of Pages: XXII, 303

Topics: Circuits and Systems, Electrical Engineering, Computer-Aided Engineering (CAD, CAE) and Design