## **Specifics of Electromagnetic Radiation Effects on Integrated Circuits**

P. K. Skorobogatov<sup>*a*, *b*, \*, O. A. Gerasimchuk<sup>*c*, \*\*</sup>, K. A. Epifantsev<sup>*a*, \*\*\*</sup>, and V. A. Telets<sup>*a*, \*\*\*\*</sup></sup>

<sup>a</sup>National Research Nuclear University MEPhI, Moscow, 115409 Russia

<sup>b</sup>Specialized Electronic Systems (SPELS), Moscow, 115409 Russia

<sup>c</sup>Impul'snaya tekhnika Research and Production Center, Dukhov All-Russia Research Institute of Automatics, 115304 Russia

\*e-mail: pkskor@spels.ru \*\*e-mail: gerasimchuk@vniia.ru

\*\*\*e-mail: kaepif@spels.ru \*\*\*\*e-mail: VATelets@mephi.ru Received November 1, 2016

Abstract—Modern regulations [1] stress the necessity of testing integrated circuits (ICs) in order to determine the real level of their resistance to single voltage pulses induced by electromagnetic radiation (EMR). With expansion of the EMR spectral composition, however, direct energy release can occur due to the absorption of the EMR field energy by the IC chip itself. To assess this possibility, the relationship is found between different mechanisms of the EMR-induced energy release for the typical irradiation geometry.

DOI: 10.1134/S1063739717030088

# 1. EVALUATING ENERGY RELEASE IN AN IC CHIP EXPOSED TO THE EMR FIELD

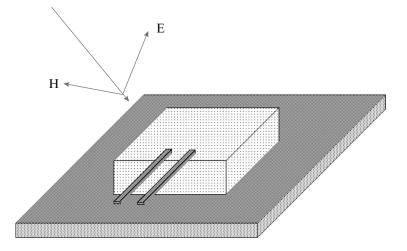

The first experimental investigations and tests of electronic equipment by using microwave generators showed that, as the duration of the acting field's edge gets shorter, protection devices lose their effectiveness; thus, it becomes easier for electromagnetic fields to penetrate through inhomogeneities in frameworks and easier for the induced currents and voltages across integrated circuit (IC) outputs to grow in amplitude. The typical irradiation geometry for the IC exposed to the electromagnetic radiation (EMR) field is shown in Fig. 1.

A semiconductor chip 250 to 700  $\mu$ m thick is placed on a metal base. The EMR energy causes the energy release in the semiconductor with the following two basic mechanisms:

—induction of pickups on the IC power-supply pins with the subsequent energy transfer to the chip;

—direct absorption of some of the EMR field energy by the IC chip.

Fig. 1. IC chip in field of plane electromagnetic wave.

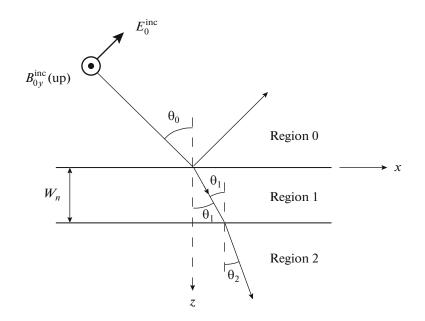

Fig. 2. Incidence of plane electromagnetic wave on interface.

The real irradiation geometry for the IC exposed to the EMR field is complex and has three dimensions. To simplify the problem, we can use the results of the investigation [2] concerning the possibility of modeling the exposure in the semi-infinite geometry, which is shown in Fig. 2.

Region 0 represents air, region 1 is a semiconductor or dielectric substrate, and region 2 represents an aluminum conductor. Here,  $W_n$  is the thickness of the substrate (chip). Figure 2 shows a plane electromagnetic wave moving down from the air to the interface between region 0 and region 1.

In [2], it was shown that, under the effect of an *E*-type wave (the electric field vector is in the incidence plane), the tangential component of the electromagnetic field in the air at the dielectric surface can be written as

$$B_{0y}(x,0) = B_{0y}(0,0)e^{ikx\sin\theta}[1+f_{er}];$$

(1)

$$E_{0x}(x,0) = \frac{\omega}{k_0} B_{0y}(0,0) e^{ikx\sin\theta} [1 - f_{er}] \cos\theta_0,$$

(2)

while under the effect of an *M*-type wave (the magnetic field vector is in the incidence plane), it can be written as

$$E_{0y}(x,0) = E_{0y}(0,0)e^{ikx\sin\theta}[1+f_{mr}];$$

(3)

$$B_{0x}(x,0) = \frac{-k_0}{\omega} E_{0y}(0,0) e^{ikx\sin\theta} [1 - f_{mr}] \cos\theta_0,$$

(4)

where  $f_{er}$  and  $f_{mr}$  are the complex reflection coefficients for *E*-type and *M*-type waves, respectively;  $k_0$  is the wavenumber for air (region 0);  $\theta_0$  is the wave incidence angle; and  $\omega$  is the angular frequency.

The squared absolute value  $0 \le |f_r|^2 \le 1$  represents the energy of the incident wave reflected from the structure, while the value  $1 - |f_r|^2$  represents the energy absorbed by the chip.

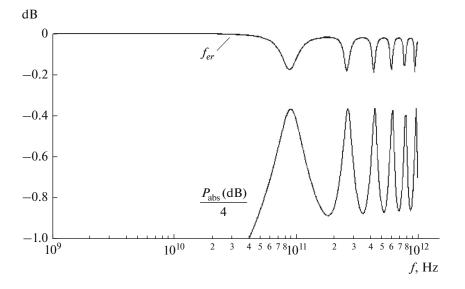

Figure 3 shows the behavior of the reflection coefficient  $f_{er}$  and the absorbed power  $P_{abs}$  for the normal incidence of the *E*-type wave on the substrate  $W_n =$

specific resistance of 100 Ohm cm. It can be seen that, up to the frequencies of about  $4 \times 10^{10}$  Hz, the silicon substrate is electrically thin, and almost all the energy of the wave is reflected. The first absorption peak occurs when the electrical thickness of the substrate becomes one-fourth of the EMR wavelength for silicon.

250 µm thick, which is made of doped silicon with

The analysis shows that, in the frequency range up to  $2 \times 10^{10}$  Hz, the total absorption losses in the silicon substrate do not exceed 0.5 dB. In the case of exposure to the two-exponential EMR pulse with the maximum

Fig. 3. Behavior of reflection coefficient  $f_{er}$  and absorbed power  $P_{abs}$  for normal incidence of E-type wave.

electric field intensity of 300 kV/m, maximum magnetic field intensity of 790 A/m, half-height duration of  $3 \times 10^{-9}$  s, and edge of  $5 \times 10^{-10}$  s, the major portion of the pulse energy is within the frequency spectrum bounded by  $2 \times 10^{10}$  Hz. The energy flow carried by this pulse (the Umov–Poynting vector) is  $\Pi = E_{\text{max}} \times H_{\text{max}} \times t_{i} \cong 0.7 \text{ J/m}^{2}$ , or about  $7 \times 10^{-5} \text{ J/cm}^{2}$ .

For 10% energy losses (which a priori exceed the potential losses throughout the frequency range of the EMR pulse), the maximum energy absorbed per pulse does not exceed  $E_{\rm abs}^s \cong 7 \times 10^{-6} \, {\rm J/cm^2}$  (per unit area).

According to [3–5], this energy may be enough to damage the IC. This, however, depends significantly on the distribution of the absorbed energy over the chip. With the thickness of the skin layer in silicon exceeding that of the substrate throughout the frequency range under consideration, the energy release from the EMR field can be very tentatively regarded as uniform. Then, the maximum density of the energy absorbed per pulse will not exceed  $E_{abs}^{\nu} \cong 28 \times 10^{-4}$  J/cm<sup>3</sup> (per unit volume), and the energy release intensity will not exceed  $10^5$  W/cm<sup>3</sup>. With the specific heat capacity of silicon being 1.6 J/(K cm<sup>3</sup>), the overheating caused by the EMR energy absorbed can be neglected. However, before making a final conclusion, the energy release due to the pickups induced on the IC power-supply pins should be evaluated.

#### 2. EVALUATING ENERGY RELEASE IN AN IC CHIP UNDER THE EFFECT OF AN EMR-INDUCED PICKUP

The irradiation geometry shown in Fig. 1 is analyzed assuming that the EMR-induced pickup is due to the short length (2 cm) of the IC pins.

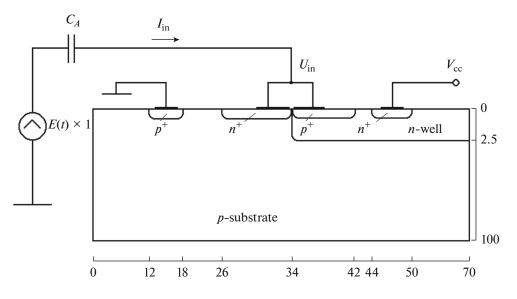

As an input circuit, we selected a CMOS IC with a protection circuit at the input, which is shown in Fig. 4. The protection circuit consists of two diodes (one to the substrate and the other to the power source via the well) and defends the IC against input pulses of any polarity.

Here, E(t) is the electric field intensity, l is the electrical length of the dipole (IC pin), and  $C_A$  is the pin capacitance. For a cylindrical pin, we have

$$C_A = \frac{2\pi\varepsilon_0 l}{\ln(2l/a) - 1},$$

where  $\varepsilon_0 = 8.85 \times 10^{-12}$  F/m and *a* is the diameter of the pin. For a = 0.5 mm, we have  $C_A \cong 3.25 \times 10^{-13}$  F.

The energy release was analyzed using the DIODE-2D physical and topological modeling software [6], which allows us to investigate two-dimensional nonstationary processes of carrier transport in semiconductor structures, including those exposed to external single voltage pulses. As an EMR pulse, we use the two-exponential signal (see above) with the edge  $t_e = 5 \times 10^{-10}$  s, maximum electric field intensity  $E_{\text{max}} = 300 \text{ kV/m}$ , and duration  $t_p = 3 \times 10^{-9}$  s.

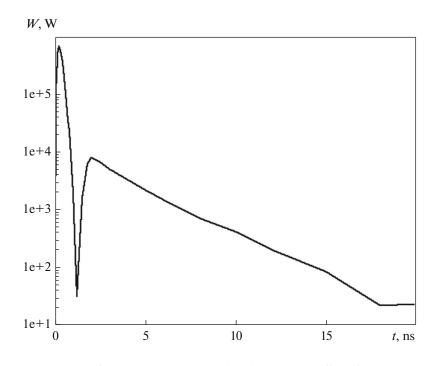

The results of the analysis are shown in Fig. 5. We can clearly see two peaks associated with the leading and trailing edges of the EMR pulse. The first maximum occurs at about 0.2 ns; and the second maximum, at about 2 ns. During exposure to the pickup pulse, the total energy absorbed by the IC input circuits was about  $2.3 \times 10^{-4}$  J with the major portion  $(2.1 \times 10^{-4} \text{ J})$  being released during exposure to the EMR pulse edge.

Note that the energy flow carried by the given EMR pulse through the IC 1 cm<sup>2</sup> in the area is about  $7 \times 10^{-5}$  J. Therefore, in the given geometry, the

Fig. 4. Physical and topological model of CMOS IC input circuit with protection: E(t) is electric field intensity, *l* is electrical length of dipole (IC pin), and  $C_A$  is pin capacitance.

Fig. 5. Time dependence of power consumed by CMOS IC input under effect of EMR-induced pickup.

pickup induced on the 2-cm pin transfers the energy (to the IC chip) that is about thrice as high as that passing through the cross section of the IC 1 cm<sup>2</sup> in area. Thus, the total amount of the energy absorbed by the IC is not increased markedly, which was to be expected because the volume of the object interacting with the EMR (IC plus its pins) nearly triples.

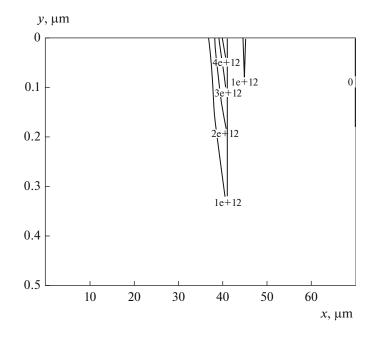

However, the distribution of the absorbed energy (transferred in the form of a pickup through the IC pins) differs considerably from the uniform distribution, which can result in high local densities of energy release. Figure 6 shows the calculated spatial distribution of the energy release over the cross section of the CMOS IC input circuit at the instant 0.2 ns (maximum energy release). It can be seen that the energy release is localized in a narrow near-surface region under the  $p^+$  region in the *n*-well. The energy release intensity reaches  $4 \times 10^{12}$  W/cm<sup>3</sup>, which exceeds that caused by the direct absorption of the EMR energy by more than seven orders. Such a high value is due to the

Fig. 6. Spatial energy release distribution (in W/cm<sup>3</sup>) over cross section of CMOS IC input circuit at instant 0.2 ns.

fact that almost all the energy is released in a very small volume at the chip surface [7].

Thus, in the case of the pickup induced by EMR on circuit pins, the absorbed energy is localized in relatively small (in terms of volume) regions, which gives rise to local overheated areas that can damage the device. The external pins capture the EMR energy, while the internal metallization and heterogeneous structure of the IC localize the energy in small critical volumes. It is this mechanism that is responsible for the primary and secondary effects that can irreparably damage the IC when exposed to EMR.

In conclusion, this investigation demonstrates that, throughout the time, frequency, and intensity ranges that are characteristic of modern and promising EMR sources, the EMR effects on IC pins can be modeled by electric signals generated using special-purpose single voltage pulses generators.

### **ACKNOWLEDGMENTS**

This work was supported by the Russian Foundation for Basic Research, project no. 14-29-09210.

#### REFERENCES

1. Products of electronics, quantum electronics and electrical engineering for military purposes. The order of impulse dielectric strength testing and test equipment requirements, RDV 319.03.30, 1998.

- Shlager, K., Preis, D., and King, R.W.P., Reflecting, coupling and absorption of plane waves incident on an integrated circuits, *IEEE Trans. EMC*, 1998, vol. 30, no. 4, pp. 570–577.

- 3. Ricketts, L.W., Bridges, J.E., and Miletta, J., *EMP Radiation and Protective Techniques*, New York: Wiley, 1976.

- 4. Skorobogatov, P.K., Epifantsev, K.A., and Gerasimchuk, O.A., An analysis of the temperature effect on the impulse electric strength of CMOS chips, *Russ. Microelectron.*, 2015, vol. 44, no. 1, pp. 40–43.

- Skorobogatov, P.K. and Epifantsev, K.A., Latent effects in digital ICs under electrical overstress pulses, in *Proceedings of the 29th International Conference on Microelectronics MIEL 2014, Belgrade, Serbia, May* 2014, 2014, pp. 315–317.

- Syts'ko, Yu.I., Skorobogatov, P.K., Chumakov, A.I., et al., The system of numerical physical-topological 2D simulation of semiconductor structures DIODE-2, in *Radiatsionnaya stoikost' elektronnykh sistem – Stoikost'-99: Tez. dokl. Ross. nauchn. konf., Lytkarino* (Proceedings of the Russian Conference on Radiation Stability of Electronic Systems, Lytkarino, Russia, June 1–3, 1999), Moscow: SPELS-NIIP, 1999, pp. 21–22.

- Kessarinskiy, L.N., Boychenko, D.V., and Nikiforov, A.Y., An analysis of the radiation behavior of pulse voltage stabilizers, *Russ. Microelectron.*, 2012, vol. 41, no. 4, pp. 251–258.

Translated by Yu. Kornienko