# OPEN

Received: 03 June 2015

Accepted: 13 November 2015

Published: 18 December 2015

# High-density carrier-accumulated and electrically stable oxide thinfilm transistors from ion-gel gate dielectric

Mami N. Fujii<sup>1,\*</sup>, Yasuaki Ishikawa<sup>1,\*</sup>, Kazumoto Miwa<sup>2</sup>, Hiromi Okada<sup>1</sup>, Yukiharu Uraoka<sup>1</sup> & Shimpei Ono<sup>2</sup>

The use of indium–gallium–zinc oxide (IGZO) has paved the way for high-resolution uniform displays or integrated circuits with transparent and flexible devices. However, achieving highly reliable devices that use IGZO for low-temperature processes remains a technological challenge. We propose the use of IGZO thin-film transistors (TFTs) with an ionic-liquid gate dielectric in order to achieve high-density carrier-accumulated IGZO TFTs with high reliability, and we discuss a distinctive mechanism for the degradation of this organic–inorganic hybrid device under long-term electrical stress. Our results demonstrated that an ionic liquid or gel gate dielectric provides highly reliable and low-voltage operation with IGZO TFTs. Furthermore, high-density carrier accumulation helps improve the TFT characteristics and reliability, and it is highly relevant to the electronic phase control of oxide materials and the degradation mechanism for organic–inorganic hybrid devices.

Transparent amorphous oxide semiconductor thin-film transistors (TFTs) have been widely investigated with the goal of optimally exploiting their low leakage current and transparency<sup>1</sup>. In particular, TFTs based on amorphous indium–gallium–zinc oxide (IGZO) have demonstrated a field-effect mobility as high as  $10\,\mathrm{cm}^2/(\mathrm{V}\cdot\mathrm{s})$ , which exceeds that of amorphous silicon TFTs<sup>1</sup>. Although IGZO TFTs are produced by using a low-temperature process, they provide high field-effect mobility ( $\mu_{\mathrm{FE}}$ ) despite the amorphous phase induced under low-temperature deposition<sup>2</sup>. Therefore, the use of IGZO has paved the way for high-resolution uniform displays or integrated circuits with transparent and flexible devices. However, achieving highly reliable devices using IGZO in a low-temperature process remains a technological challenge because IGZO deteriorates under the influence of impurities in the atmosphere or the electrical stress of applied voltages.

In order to achieve highly reliable long-term device operation, some research groups have examined inorganic gate insulators and passivation films layered on IGZO thin films, which are fabricated using a high-temperature process<sup>3,4</sup>. However, IGZO TFTs have demonstrated rather poor characteristics and a degradation from their initial performance as a result of electron trap or carrier generation due to the adsorption of oxidation or hydrogen from the atmosphere<sup>5,6</sup>. To avoid these problems, a high-quality passivation film on the channel has been considered in order to reduce oxidation and hydrogen adsorption. In addition, introducing a top-gate structure to TFTs with high-quality gate insulators can address these issues because the gate insulator film acts as a passivation film. In order to further optimise the devices, numerous combinations of semiconductors and dielectrics are being extensively tested because the interfacial phenomena are crucial to determining their long-term stability. However, IGZO TFTs still have the problem of threshold voltage ( $V_{\rm th}$ ) shifts that result from the electrical stress caused by the applied voltage<sup>7,8</sup>.

Furthermore, because a low-voltage operation allows activation under a low electrical field in the channel material and at the interface between the channel and gate insulator, ultra-low voltage TFT operation is essential to reduce the electrical stress for highly reliable TFTs because IGZO TFTs are degraded by an applied voltage, and the amount of  $V_{\rm th}$  shift increases with the applied voltage. Achieving a high current with low-voltage operation

<sup>1</sup>Graduate School of Materials Science, Nara Institute of Science and Technology, 8916-5 Takayama, Ikoma, Nara 630-0192, Japan. <sup>2</sup>Central Research Institute of Electric Power Industry 2-11-2, Iwado-kita, Komae, Tokyo 201-8511, Japan. <sup>\*</sup>These authors contributed equally to this work. Correspondence and requests for materials should be addressed to M.N.F. (email: f-mami@ms.naist.jp)

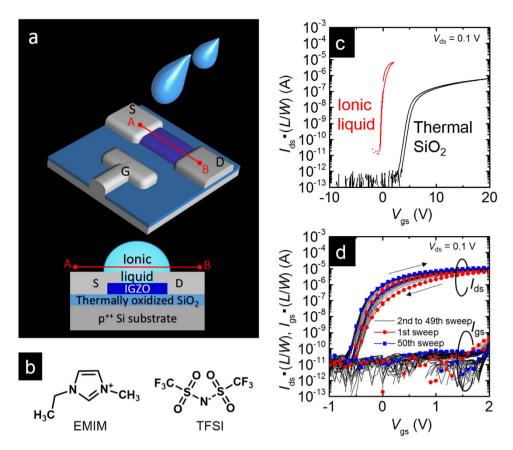

Figure 1. Device structures and characteristics of the IGZO TFT with ionic liquid used in this study. (a) Image and schematic cross-sectional view of the IGZO TFT with ionic liquid. The underside image is the cross-sectional cut between points A and B, which are shown in the upper TFT image. (b) EMIM-TFSI ionic liquid structure. (c) Transfer characteristics and hysteresis curve of the IGZO TFTs with ionic liquid and  $SiO_2$  gate insulators. (d) Fifty-cycle measurement of the IGZO TFTs with ionic-liquid gate dielectric and gate leakage current, where the maximum values of  $V_{\rm gs}$  are 2 and 20 V for the ionic-liquid and thermal  $SiO_2$  gate insulator TFTs, respectively, and  $V_{\rm ds}$  is 0.1 V. The applied  $V_{\rm gs}$  swept from 0 V toward a negative voltage, returned to 0 V, swept toward a positive voltage, and returned again to 0 V.

provides a strong advantage for driving organic light-emitting diode (OLED) displays that operate on a current. For low-voltage operation, insulating materials that can accumulate carriers at a high density in a semiconductor film are necessary. Some studies have demonstrated low-voltage-operation IGZO TFTs with high-capacitance and high-k material gate insulators for driving OLED devices<sup>9-11</sup>. However, the fabrication of these films is generally difficult at temperatures below 150 °C because the gate-leakage current is rather large.

Recently, transistors that employ an electric double layer have been realised by using ionic liquid or electrolytes<sup>12–15</sup>. For example, given an oxide semiconductor and ionic liquid combination, some studies have demonstrated high-density carrier accumulation in the channel<sup>16,17</sup>. Introducing an ionic liquid enables carrier accumulation in the channel to high densities of up to  $10^{14}\,\mathrm{cm}^{-3}$ , which enables operation at an ultra-low voltage<sup>18</sup>. However, the reliability under long-term electrical stress in an organic-inorganic combination has not been discussed. Moreover, choosing a proper ionic liquid can counter the effect of hydrogen on IGZO TFTs, which have top-gate structures, because of the presence of some hydrophobic ionic-liquid materials<sup>19–21</sup>. Therefore, determining the electrical stress reliability of IGZO TFTs by using an ionic-liquid gate dielectric has important implications for the application of organic-inorganic hybrid devices.

In this letter, we present the application of IGZO TFTs with an ionic-liquid gate dielectric in order to achieve high reliability, and we discuss a mechanism for the device degradation of this organic-inorganic hybrid device under long-term electrical stress.

#### Results

Figure 1a displays the image and schematic cross-sectional view of the IGZO TFT used in this study. The underside is shown and represents the cross-sectional image cut between points A and B in the upper TFT image. The image explains the structure of the source-drain electrode and IGZO channel. The highly hydrophobic and highly stable ionic liquid of 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide (EMIM-TFSI), which is shown in Fig. 1b, was used in our experiment. The highly doped Si substrate can act as a gate electrode when driven by the bottom gate, which has a  ${\rm SiO}_2$  gate insulator structure. The platinum-covered molybdenum top-gate electrode was applied to the top-side-gate structure with an ionic-liquid gate dielectric, which allowed us to examine the

| Gate insulator   | Maximum $I_{ds} \cdot (L/W)$ (A)   | SS (mV/dec) | V <sub>th</sub> (V) |

|------------------|------------------------------------|-------------|---------------------|

| ionic liquid     | $\sim 10^{-6}$ at $V_{gs} = 2 V$   | $97\pm25$   | $0.66\pm0.26$       |

| SiO <sub>2</sub> | $\sim 10^{-7}$ at $V_{gs} = 20  V$ | $420\pm18$  | $5.12 \pm 1.47$     |

**Table 1. TFT parameters of ionic-liquid and SiO<sub>2</sub> gate TFTs.** The average values of 10 measurements are given for each gate insulator.

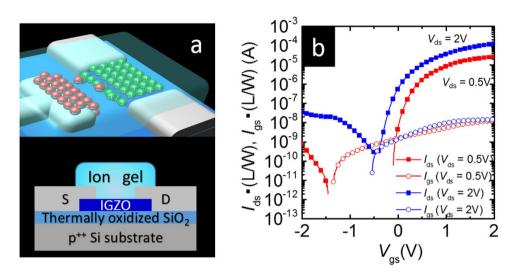

**Figure 2.** Device structures and characteristics of the IGZO TFT with an ion gel. (a) Image and schematic cross-sectional view of the IGZO TFT with an ion gel. The underside image is the cross-sectional cut, which is shown in the upper TFT image. (b) Transfer characteristics and gate leakage current of the IGZO TFTs with an ion gel.

liquid-gate and solid-gate TFT performances on the same substrate. The distance between IGZO and the Mo-gate electrode was  $30\,\mu m$ .

Our selected combination produced excellent TFT characteristics, which are presented in Fig. 1c (red curve). The TFTs that combined the EMIM-TFSI gate dielectric and IGZO channel provided a substantially high drain current ( $I_{\rm ds}$ ) of ~10<sup>-6</sup>A at a gate voltage ( $V_{\rm gs}$ ) of 2 V and a significantly small subthreshold swing (SS) of 97 ± 25 mV/decade, even when the applied drain voltage ( $V_{\rm ds}$ ) was 0.1 V. Here,  $I_{\rm ds}$  was proofed by using the channel width (W) and length (L) as  $I_{\rm ds} \times L/W$ . The threshold voltage ( $V_{\rm th}$ ) was approximately zero. On the other hand, the TFT with a thermal SiO<sub>2</sub> gate insulator demonstrated a lesser value for  $I_{\rm ds}$  (~10<sup>-7</sup> A) when  $V_{\rm gs} = 20$  V and a large SS of  $420 \pm 18$  mV/decade; this is represented by the black curve in Fig. 1c. Table 1 lists the obtained data of the average values for 10 measurements. These parameters were calculated from using the measurements provided by biasing  $V_{\rm gs}$  from 2 V to -2 V. The variations in  $V_{\rm th}$  and SS ( $V_{\rm th-var}$  and SS<sub>var</sub>) over 50 cycles of transfer curves of the ionic-liquid gate IGZO TFT were exceedingly small:  $V_{\rm th-var} = -0.1$  V and SS<sub>var</sub> = -45 mV/decade, as shown in Fig 1d. Although this is currently under study, these variations were most likely due to the carrier generation or filling of the trap states with carriers that were accumulated by the ionic liquid. The relatively large value for  $I_{\rm ds}$  in the off region should be expected. These results clearly indicate low-voltage operation with an extremely small SS, which was achieved by introducing the EMIM-TFSI ionic liquid.

Because the liquid was not in an improper material phase during either the device fabrication process or reliability study, we gelated it as shown in Fig. 2a. Note that the ion gel could maintain a high capacitance of above  $1\,\mu\text{F/cm}^2$  until a frequency of approximately  $1\,\text{kHz}$  was achieved, which is demonstrated in Fig. S1 of the online supplement. Figure 2b shows the IGZO TFT characteristics when using an ion-gel gate dielectric. Given the evidence of its effectiveness, we concluded that the ion gel can be applied to devices.

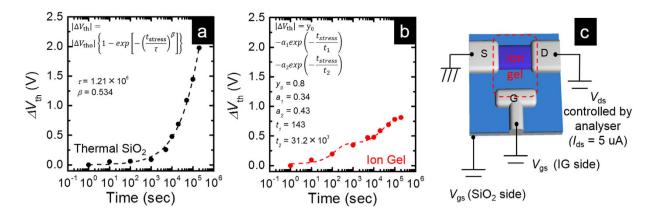

Figure 3 presents the  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ) results under a long-term current stress; Fig. 3a shows the bottom gate, and Fig. 3b shows the ion-gel applied top gate. The drain voltages were controlled in order to maintain  $I_{\rm ds}=5\,\mu{\rm A}$  by using a semiconductor parameter analyser (Agilent B1500A), as shown in Fig. 3c. The gate stress voltages were  $V_{\rm gs}=10\,{\rm V}$  for the SiO<sub>2</sub> gate dielectric structure and  $V_{\rm gs}=2\,{\rm V}$  in the ion-gel gate dielectric structure. The symbols indicate our measured results, and the broken lines signify the results that were calculated by using Equations 1 and 2. These measurements were taken in air.

Figure 3.  $V_{th}$  shifts ( $\Delta V_{th}$ ) under a long-term current stress according to the stress time. (a)  $\Delta V_{th}$  in the IGZO TFT with a thermal SiO<sub>2</sub> gate insulator and (b) with an ion-gel gate dielectric. The applied gate stress voltages were  $V_{gs} = 10 \, \text{V}$  for the SiO<sub>2</sub> gate dielectric and  $V_{gs} = 2 \, \text{V}$  for the ion-gel gate dielectric. The applied drain voltages were fixed at  $I_{ds} = 5 \, \mu \text{A}$ . The symbols indicate the measurement results, and the broken lines represent the results calculated using (a) the stretched exponential equation and (b) the two exponential equations. (c) Image of the device and the measurement method of the reliability.

#### Discussion

The carrier's excitation and recombination mechanisms for amorphous semiconductor materials can be expressed in a stretched exponential equation. Lee *et al.* confirmed that the IGZO TFT degradation follows this relation<sup>22</sup>. Given a SiO<sub>2</sub> dielectric,  $V_{th}$  degradation occurs according to the following stretched exponential equation<sup>23</sup>:

$$|\Delta V_{\rm th}| = |\Delta V_{\rm tho}| \left\{ 1 - \exp\left[ -\left(\frac{t_{\rm stress}}{\tau}\right)^{\beta} \right] \right\}. \tag{1}$$

Here,  $\Delta V_{\text{th}0}$  represents the  $V_{\text{th}}$  shift amount as the time approaches infinity; this is provided by  $V_{\text{g-stress}} - V_{\text{th-initial}}$ .  $V_{\text{g-stress}}$  is the applied stress voltage,  $V_{\text{th-initial}}$  is the initial  $V_{\text{th}}$  voltage before the stress test,  $t_{\text{stress}}$  is the stress time,  $\tau$  is the characteristic trapping time for the carriers, and  $\beta$  is the stretched exponential exponent. In this case, which is shown in Fig. 3a, the measured values for  $\tau$  and  $\beta$  were  $1.21 \times 10^6$  s and 0.536, respectively. When the stress time was  $2 \times 10^5$  s,  $\Delta V_{\text{th}}$  reached approximately 2 V. This equation is commonly used for the relaxation process of the random system. In particular, it can be expressed as a temperature-dependent model of the energy transmission or as an Urbach tail caused by dipole interaction when  $\beta = 0.5^{24.25}$ . This model is understood to represent the carrier trapping that occurs in the TFTs<sup>23</sup>. Therefore, degradation of the IGZO TFTs with an SiO<sub>2</sub> gate insulator results from electron trapping, which is related to semiconductor and insulator films and is caused by electrical stress.

On the other hand, IGZO TFTs with an ion-gel gate dielectric exhibited markedly different behaviour. We can expect stability with ion-gel gate IGZO TFTs when compared with a TFT that uses a conventional  $SiO_2$  gate insulator. Therefore, we successfully fitted the  $V_{\rm th}$  degradation by using Equation 2 rather than the stretched exponential equation:

$$|\Delta V_{\rm th}| = y_0 - a_1 exp\left(-\frac{t_{stress}}{t_1}\right) - a_2 exp\left(-\frac{t_{stress}}{t_2}\right). \tag{2}$$

Figure 3b shows the result of Equation 2, which includes two exponential equations. There were two inflection points at approximate stress times of  $10^3$  and  $10^5$ s. Here, the decay constants  $t_1$  and  $t_2$  were 143s and 31.2 ks, respectively. They indicate that the degradation mechanism included slow and fast reactions rather than an ionic charge  $^{26}$ . Therefore, this degradation mechanism cannot be addressed by using the previously discussed conventional mechanism. We assumed that the  $V_{\rm th}$  shift degradation depends on the progress of the chemical reaction, which is related to the ionic liquid, i.e. the oxidation or hydrogen adsorption of the ion gel or the melting reaction of metal atoms by the ion gel, in addition to the carrier trapping of the IGZO. This implies that the  $V_{\rm th}$  shift in the ion-gel gated TFT was primarily produced by the breaking of the ion gel or chemical reaction of the ion gel with IGZO and not because of the electrical trapping related to IGZO films. The problem of stability remains when using an ionic liquid or gel because these incorporate oxygen or water when stored under atmosphere. Thus, an ion-gel gate IGZO TFT with lamination to protect it from oxygen and water produced a remarkably stable and low-voltage operation device. Although further study on the degradation mechanism is necessary, the ion-gel gate IGZO TFT exhibited extremely stable characteristics.

In summary, we successfully obtained low-voltage IGZO TFTs by using an ionic-liquid gate dielectric, especially when compared with bottom-gate IGZO TFTs that use  $SiO_2$  gate insulators. Ionic-liquid gate IGZO TFTs also produced extremely small SS values near the theoretical limit and an on-state current that was an order of magnitude greater than that of conventional  $SiO_2$  gate IGZO TFTs, even when derived under a voltage of 2 V. In other words, high-density carrier accumulation was achieved in the IGZO channel using a liquid gate dielectric.

Moreover, the ion-gel gate IGZO TFTs exhibited excellent reliability under electrical stress when compared with the IGZO TFTs that used  ${\rm SiO_2}$  gate insulators, even when measured in air. Therefore, the ion gel is a promising insulating material for the low-temperature fabrication of IGZO TFTs and is one solution to achieving flexible IGZO TFTs. Our results explicitly demonstrate that an ionic liquid or gel gate dielectric provides highly reliable and low-voltage IGZO TFTs. The high-density carrier accumulation helps improve TFT characteristics and reliability, and it is highly relevant to discussions of the electronic phase control of oxide materials and degradation mechanism for organic–inorganic hybrid devices.

#### Methods

We fabricated a top-gate type IGZO TFT with ionic liquid, as shown in Fig. 1a. We then examined the transfer characteristics of TFTs and their stability under electrical stress. The fabricated TFT can also serve as a bottom-gate type TFT. IGZO films with stoichiometric ratios of 2:2:1:7 and a thickness of 70 nm were deposited at room temperature by using radio frequency (RF) magnetron sputtering on thermally oxidised 100-nm-thick SiO<sub>2</sub>, which was grown on a highly doped  $p^{++}$  Si substrate (<0.01  $\Omega$ ·cm) and patterned with wet etching. Platinum-covered molybdenum electrodes, which were used as the source, drain, and gate electrodes, were prepared by using RF magnetron sputtering and the lift-off technique. The annealing process, which was performed in air at 300 °C for 2 h, completed the electrode fabrication. Next, we drop-casted the ionic liquid on the TFT channel region.

For ionic liquid gelation, we prepared the solution of ionic liquid with polymer by melting the polymer DM37-M06 (DAISO Co., Ltd.) with acetonitrile solvent and mixing it with the ionic liquid, a cross-linking agent, and a photo-polymerisation initiator (Benzophenon). Here, the mixing ratio of the polymer and ionic liquid was 1:1. After this solution was drop-casted on the channel, the substrates were baked at  $100\,^{\circ}$ C for 5 min and irradiated at an ultraviolet wavelength of  $254\,\mathrm{nm}$  for  $10\,\mathrm{min}$ .

To measure the initial characteristics of the transistor, we used Agilent B1500A in a nitrogen ambient at room temperature at a scanning speed of  $0.065\,\mathrm{V/s}$  by biasing from  $V_\mathrm{gs} = 0\,\mathrm{V}$  to  $2\,\mathrm{V}$ . The bias was turned to  $0\,\mathrm{V}$  and swept to  $-2\,\mathrm{V}$  before being turned to  $0\,\mathrm{V}$  again. Then, we checked the reliability under normal conditions by measuring the TFT characteristics with Agilent B1500A in air at room temperature. The characteristics were measured before and after the current stress each time.

We measured the capacitance of the ionic liquid and its gel by using the AC impedance technique (Solartron 1260 and 1296). We formed a well structure of polydimethylsiloxane (PDMS) and deposited the Au film on the PDMS surface. We then drop-casted the ionic liquid onto the well on the Au metal. Au-coated PDMS was placed in the ionic liquid, and an Au/ionic liquid/Au structure was formed. In the IG case, the Au metal was deposited on the Si substrate and placed on the gel-sheet, and Au was deposited again on the gel-sheet. Here, the gap thickness between Au electrodes was  $25\,\mu\text{m}$ . The structure of the samples is shown in Fig. S1b and c of the online supplement. We also performed the measurement by using a TFT structure as shown in Fig. S2b. The capacitance of the ion gel showed a frequency dependence and was  $3.6\,\mu\text{F/cm}^2$  at  $10\,\text{Hz}$ , as shown in Fig. S2a of the online supplement.

### References

- 1. Kamiya, T. & Hosono, H. Material Characteristics and Applications of Transparent Amorphous oxide semiconductors. *NPG Asia Mater.* **2**, 15–22 (2010).

- 2. Nomura, K. et al. H. Room-Temperature Fabrication of Transparent flexible Thin-film Transistors Using Amorphous Oxide Semiconductors. *Nature* **432**, 488–492 (2004).

- 3. Tu, C.-H. et al. Bias Stress Reliability for w/ and w/o Oxide-passivated IGZO TFTs. SID Symp. Dig. of Tech. Pap. 42, 1151–1153 (2011).

- 4. Yamazaki, H. et al. The Influence of Fluorinated Silicon Nitride Gate Insulator on Positive Bias Stability toward Highly Reliable Amorphous InGaZnO Thin-Film Transistors. ECS J. Solid State Sci. Technol. 3, Q20–Q23 (2014).

- 5. Hanyu, Y. et al. Hydrogen Passivation of Electron Trap in Amorphous In-Ga-Zn-O Thin-Film Transistors. Appl. Phys. Lett. 103, 202114 (2013)

- 6. Korner, W., Urban, D. F. & Elsasser, C. Origin of Subgap States in Amorphous In-Ga-Zn-O. J. Appl. Phys. 114, 163704 (2013).

- 7. Liu, K.-H. et al. Investigation of On-current Degradation Behavior Induced by Surface Hydrolysis Effect Under Negative Gate Bias Stress in Amorphous InGaZnO Thin-Film Transistors. Appl. Phys. Lett. 104, 103501 (2014).

- 8. Yuan, L. et al. High-performance Amorphous Indium Gallium Zinc Oxide Thin-film Transistors with HfO<sub>x</sub>N<sub>y</sub>/HfO<sub>2</sub>/HfO<sub>x</sub>N<sub>y</sub> Tristack Gate Dielectrics. *IEEE Elect. Dev. Lett.* **32**, 42–44 (2011).

- 9. Nomura, K. et al. All Oxide Transparent MISFET Using High-k Dielectrics Gates. Microelectron. Eng. 72, 294-298 (2004).

- Kim, J. B., F-Hernandez, C., Potscavage, W. J. Jr., Zhang, X.-H. & Kippelen, B. Low-voltage InGaZnO Thin-film Transistors with Al<sub>2</sub>O<sub>3</sub> Gate Insulator Grown by Atomic Layer Deposition. Appl. Phys. Lett. 94, 142107 (2009).

- 11. Lee, I.-K., Lee, S.-W., Gu, J., Kim, K.-S. & Cho, W.-J. Comparative Study of Device Performance and Reliability in Amorphous InGaZnO Thin-Film Transistors with Various High-k Gate Dielectrics. *Jpn. J. Appl. Phys.* **52**, 06GE05 (2013).

- 12. Nilsson, D. et al. Bi-stable and Dynamic Current Modulation in Electrochemical Organic Transistors. Adv. Mater. 14, 51–54 (2002).

- 13. Cho, J. H. et al. Printable Ion-gel Gate Dielectrics for Low-voltage Polymer Thin-film Transistors on Plastic. Nat. Mater. 7, 900–906 (2008).

- 14. Ye, J. T. *et al.* Liquid-gated Interface Superconductivity on an Atomically Flat Film. *Nat. Mater.* **9,** 125–128 (2010).

- 15. Uesugi, E., Goto, H., Eguchi, R., Fujiwara, A. & Kubozono, Y. Electric Double-layer Capacitance between an Ionic Liquid and Few-layer Graphene. Sci. Rep. 3, 1595 (2013).

- Yuan, H. et al. High-density Carrier Accumulation in ZnO Field-effect Transistors Gated by Electric Double Layers of Ionic Liquids. Adv. Funct. Mater. 19, 1046–1053 (2009).

- 17. Thiemann, S., Sachnov, S., Porscha, S., Wasserscheid, P. & Zaumseil, J. Ionic Liquids for Electrolyte-gating of ZnO Field-effect Transistors. J. Phys. Chem. C 116, 13536–13544 (2012).

- 18. Ono, S., Miwa, K., Seki, S. & Takeya, J. A Comparative Study of Organic Single-crystal Transistors Gated with Various Ionic Liquid Electrolytes. *Appl. Phys. Lett.* **94**, 063301 (2009).

- Mele, A., Tran, C. D. & Lacerda, S. H. D. P. The Structure of a Room-temperature IonicLiquid with and without Trace Amounts of Water: The Role of C-H···O and C-H···F Interactions in 1-n-butyl-3-methylimidazolium Tetrafluoroborate. *Angew. Chem.* 115, 4500–4502 (2003).

- Cuadrado-Prado, S. et al. Experimental Measurement of the Hygroscopic Grade on Eight Imidazolium Based Ionic Liquids. Fluid Ph. Equilibria 278, 36–40 (2009).

- 21. Qian, Q. et al. Electrochemical Quantification of Hygroscopicity of Ionic Liquids with Solution-dissolved Potassium Ferricyanide as the Redox Probe. Electroanal. 23, 2870–2877 (2011).

- Lee, J.-M., Cho, I.-T., Lee, J.-H. & Kwon, H.-I. Bias-stress-induced Stretched-exponential Time Dependence of Threshold Voltage Shift in InGaZnO Thin Film Transistors. Appl. Phys. Lett. 93, 093504 (2008).

- 23. Libsch, F. R. & Kanicki, J. Bias-stress-induced Stretched-exponential Time Dependence of Charge Injection and Trapping in Amorphous Thin-film Transistors. *Appl. Phys. Lett.* **62**, 1286 (1993).

- Montrollm, E. W. A Note on the Theory of Diffusion Controlled Reactions with Application to the Quenching of Fluorescence. J. Chem. Phys. 14, 202 (1946).

- 25. Berberan-Santos, M. N., Bodunov, E. N. & Valeur, B. Mathematical Functions for the Analysis of Luminescence Decays with Underlying Distributions 1. Kohlrausch Decay Function (Stretched Exponential). *Chemical Physics* 315, 171–182 (2005).

- 26. Yamamoto, R. et al. External Electric Field Dependence of the Structure of the Electric Double Layer at an Ionic Liquid/Au Interface. Appl. Phys. Lett. 101, 053122 (2012).

## **Acknowledgements**

This research was supported by a grant from Nara Institute of Science and Technology.

# **Author Contributions**

M.N.F., Y.I. and S.O. planned the experiments. M.N.F, H.O. and K.M. prepared the ionic liquid gate IGZO TFTs and carried out the measurements. All of the authors analysed and discussed the experimental results.

#### **Additional Information**

Supplementary information accompanies this paper at http://www.nature.com/srep

**Competing financial interests:** The authors declare no competing financial interests.

How to cite this article: Fujii, M. N. et al. High-density carrier-accumulated and electrically stable oxide thin-film transistors from ion-gel gate dielectric. Sci. Rep. 5, 18168; doi: 10.1038/srep18168 (2015).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/