**REGULAR PAPER**

# Full Adder Circuit Design with Novel Lower Complexity XOR Gate in QCA Technology

Ali H. Majeed<sup>1,2</sup> · Mohd Shamian Bin Zainal<sup>1</sup> · Esam Alkaldy<sup>2</sup> · Danial Md Nor<sup>1</sup>

Received: 12 October 2019 / Revised: 15 December 2019 / Accepted: 28 December 2019 / Published online: 7 January 2020 © The Korean Institute of Electrical and Electronic Material Engineers 2020

#### Abstract

Quantum-dot Cellular Automata (QCA) is a new technology for designing digital circuits in Nanoscale. This technology utilizes quantum dots rather than diodes and transistors. QCA supplies a new computation platform, where binary data can be represented by polarized cells, which can define by the electron's configurations inside the cell. This paper explains QCA based combinational circuit design; such as half-adder and full-adder, by only one uniform layer of cells. The proposed design is accomplished using a novel XOR gate. The proposed XOR gate has a 50% speed improvement and 35% reduction in the number of cells needed over the best reported XOR. The results of QCADesigner software show that the proposed designs have less complexity and less power consumption than previous designs.

Keywords Nanotechnology  $\cdot$  Quantum-dot cellular automata  $\cdot$  XOR gate  $\cdot$  Half adder  $\cdot$  Full adder

# **1** Introduction

CMOS technology will reach the scaling limit in nanomaterial progress [1]. Consequently, alternative technology became the goal of numerous researchers. QCA is a new Nano technique that offers a new strategy for information transformation and computation. The main building units in QCA circuits are majority gate and inverter; where any QCA circuit can be constructed using only these two blocks with help of binary wire. Many digital circuits in QCA technology have been introduced in the literature, some of them focused on combinational circuits such as [2, 3] others focused on sequential and memory circuits as in [4–7]. Arithmetic circuits are considered a crucial tool in digital circuits due to

Ali H. Majeed alih.alasady@uokufa.edu.iq

Mohd Shamian Bin Zainal shamian@uthm.edu.my

Esam Alkaldy esam.alkaldy@uokufa.edu.iq

Danial Md Nor danial@uthm.edu.my

<sup>1</sup> Faculty of Electrical and Electronic Engineering, UTHM, Batu Pahat, Johor, Malaysia

<sup>2</sup> Faculty of Engineering, University of Kufa, Kufa, Iraq

their extensive used in many signal processing applications. The addition is one of the basic arithmetic operations. A full adder is the core of any arithmetic unit and is located on its critical path; therefore, its performance directly affects the entire system's performance. Many researchers have studied full adder by QCA, such as [8-15]. This implies that the performance enhancement of Adder will enhance the whole system's performance. Therefore, the design of QCA adder circuits with less complexity, shorter delays, and the lowest area, will be significantly required in the future [8, 16]. In this paper, a novel QCA-XOR gate is presented with minimum complexity. To demonstrate the operation of the proposed gate, it was used to design adder circuits, with the results compared to previous designs. Many programs introduced for QCA circuits evaluation such as [17] but QCADesigner tool is more common and it will be used for circuit simulation and evaluation in this work.

This paper will be arranged as follows: Sect. 2 preliminaries. Section 3 exclusive OR gate. The adder circuit is given in Sect. 4. Simulation results with comparisons will be detailed in Sect. 5. Finally, the conclusion is in Sect. 6.

# 2 Preliminaries

This section will give reviews of QCA basics.

#### 2.1 QCA Basics

#### 2.1.1 QCA Cells

The fundamental QCA cell is illustrated in Fig. 1. QCA cell has a square shape consisting of four dots; where a pair of electrons is occupied within it diagonally, due to columbic repulsion. The injected electrons can transport through the tunnel between the adjacent dots. However, given the high potential between cells, it cannot tunnel between adjacent cells. Therefore, there are two arrangements of the QCA cell, depending on its polarization, as -1 (logic "0") and +1 (logic 1).

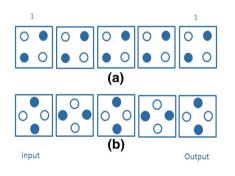

#### 2.1.2 QCA Wire

QCA wire is comprised of fundamental cells that carry the input logical value to the output. The electrons interaction forces cells to take the same polarization of the neighbour cell, in other word each cell consider as a driver cell for the next one. This approach is applied in two configurations. The first is normal (or direct mode) while the second is rotated mode [18]. These two types are shown in Fig. 2.

Fig. 1 Primary QCA cell

#### 2.1.3 QCA Gates

Three types of inverter presented in QCA are shown in Fig. 3.

Furthermore, a dominant gate in QCA circuits is majority gate; which has attracted the attention of many researchers [19–21]. Using this gate, the designer can make AND or OR gates by applying -1 or +1, respectively, on one of the majority inputs. Two forms of 3-input majority voters (Maj-3) are presented in Fig. 4. The Boolean equation of Maj-3 gate is given by Eq. 1 [22, 23].

$$M(A, B, C) = AB + BC + AC \tag{1}$$

The 3-inputs majority gate is expanded to many inputs majority voter with different QCA structures and layouts as in [8, 24, 25].

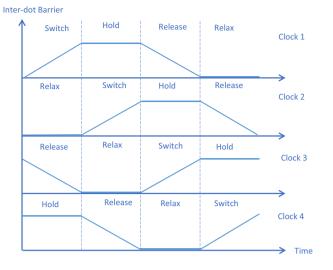

#### 2.1.4 QCA Clock

Clocking is an essential part of QCA circuits due to following reasons: synchronization, power compensation, and controlling the direction of data flow. Furthermore, it gives the power to stimulate the circuit. The clock signal controls the potential barriers between dots inside the cell to achieve synchronization. The polarization of the cell is still undetermined; as long as the cell has low potential barriers, the electrons will then easily move between points. The electrons get them localized whenever the potential barriers rise to their highest value. At this point, the polarization of the cell will be determined. The clock signal contains four clock zones and every zone contains four-phases, starting

Fig. 2 QCA wire a direct mode, b rotated mode

Fig. 3 QCA inverter forms

Fig. 4 Three inputs majority gate forms

Fig. 5 Clock zones signal

from switch phase then hold, release, and relax (as illustrated in Fig. 5) [26].

# 3 The Exclusive-OR (XOR) Gate

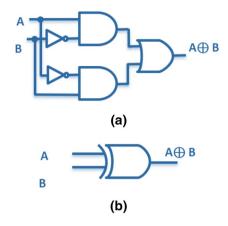

XOR gate is a logic circuit that gives high at the output when the number of high inputs is odd. The Boolean equation of XOR is illustrated in Eq. 2.

$$XOR_{A,B} = A \cdot \bar{B} + \bar{A} \cdot B \tag{2}$$

The XOR logic diagram and its symbol are shown in Fig. 6.

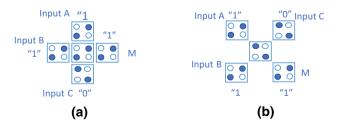

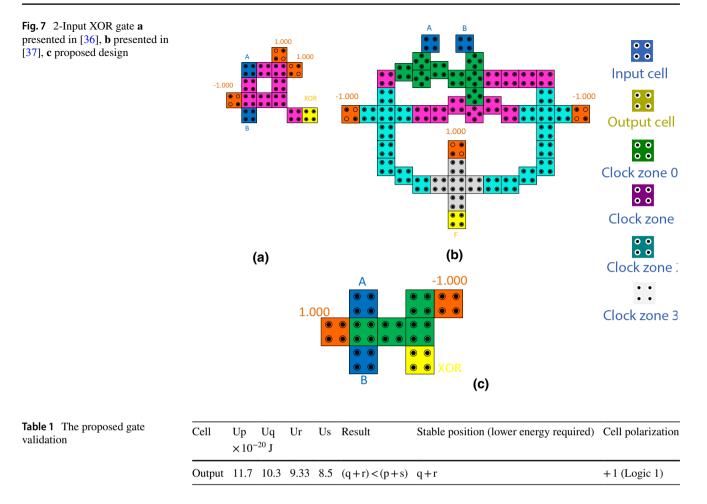

#### 3.1 The Proposed XOR Layout

The XOR gate is the brick unit of many digital circuits, such as arithmetic circuits [27] and parity bit generator circuit [28]. There are several XOR layouts presented previously in QCA technology [29–35] but the goal was to minimize the number of majority gate or inverter used by re-forming the XOR equation. While some of them were design based on the inherent capability of QCA. An example of the conventional XOR structures presented previously is illustrated in Fig. 7a, b; while the proposed XOR layout is illustrated in Fig. 7c.

Fig. 6 XOR gate a logic circuit diagram, b symbol

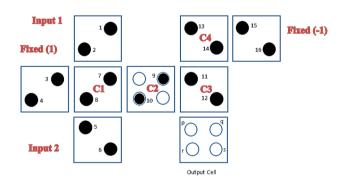

#### 3.1.1 Physical Verification

The proposed structure verified physically as illustrated in Fig. 11 and Table 1. For the two adjacent cells (i, j), the electrostatic energy  $E_{i,i}^k$  can be calculated using Eq. 3.

$$E_{Total} = \sum_{i,j} \frac{q_i q_j}{4\pi\varepsilon_0 \varepsilon_r |r_{i,j}|}$$

(3)

where  $\varepsilon_0$ : free space permittivity;  $\varepsilon_r$ : relative permittivity; q: the charge of electron inside dot; |ri - rj|: the space between the two dots.

The most stable orientation defined by the configuration have lower energy in a certain input.

The electrostatic energy or called "kink energy"  $E^k$ between two cells can be calculated by letting one cell in its original state and switching the other in two contradictory polarization states and then comparing the two results and selecting the smaller one. This was done for many uncertain polarization cells (c1, c2, c3 and c4) as in Fig. 8 before calculating the polarization of the output cell for the proposed gate and the results were the polarization of c1 = 1, c2 = 1, c3 = 0 and c4 = 0. If the input pattern (A, B) = (1, 0), the calculation of the total electrostatic energy at dot p (named Up) for the output cell is shown below: $Up = \frac{K}{D1} + \frac{K}{D2} + \frac{K}{D3} + \frac{K}{D4} + \frac{K}{D5} + \frac{K}{D6} + \frac{K}{D7} + \frac{K}{D8}$  $+ \frac{K}{D9} + \frac{K}{D10} + \frac{K}{D11} + \frac{K}{D12} + \frac{K}{D13} + \frac{K}{40} + \frac{K}{32.28} + \frac{K}{36.89}$  $+ \frac{K}{41.48} + \frac{K}{22.83} + \frac{K}{22.83} + \frac{K}{21.93} + \frac{K}{11} + \frac{K}{40} + \frac{K}{32.28}$  $+ \frac{K}{44.72} + \frac{K}{42.45} = 11.7 \times 10^{-20}$  W h e r e  $k = \frac{q^2}{4\pi e_{x}e_{x}} = 23.04 \times 10^{-20}$  and D is the distance between

Fig. 8 proposed configuration to analysis the proposed XOR gate

two dots. The proposed XOR is verified by simulating it with QCADesigner software and the results are given in Sect. 5.

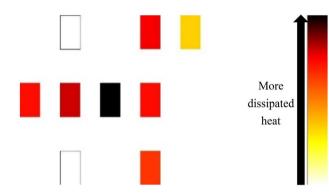

#### 3.1.2 Power Consumption Analysis

The estimation of the dissipated power for the proposed gate can be defined using the most common tool called

QCAPro. This tool has the ability to manipulate large circuit because it uses fast approximation and it can expect the losses of power in non-adiabatic switching.

The analysis of power dissipation at different tunneling energy levels (0.5 Ek, 1 Ek and 1.5 Ek) for the proposed gate in comparison with previously counterparts is shown in Table 2. The power dissipation map for proposed gate at 0.5 Ek is illustrated in Fig. 9.

# **4 Adder Circuits**

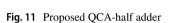

#### 4.1 Half Adder

Half adder responsible for adding two logical inputs and provides two outputs sum and carry, if input variables are A and B. The sum and carry of these two variables can be calculated by Eq. 4.

$$Sum = A \oplus B$$

$$Carry = AB$$

(4)

Half adder logic circuit is illustrated in Fig. 10.

Table 2Power dissipationcomparison at 2 K for manyXOR gates

| Circuit presented in | Average of leakage energy dissipation (meV) |       | Average of switching<br>energy dissipation (meV) |        |       | Total energy consumption<br>(meV) |        |       |        |

|----------------------|---------------------------------------------|-------|--------------------------------------------------|--------|-------|-----------------------------------|--------|-------|--------|

|                      | 0.5 Ek                                      | 1 Ek  | 1.5 Ek                                           | 0.5 Ek | 1 Ek  | 1.5 Ek                            | 0.5 Ek | 1 Ek  | 1.5 Ek |

| [38]                 | 14.82                                       | 40.32 | 68.10                                            | 32.17  | 26.23 | 21.41                             | 46.99  | 66.54 | 89.51  |

| [39]                 | 11.51                                       | 31.91 | 54.69                                            | 35.78  | 30.48 | 25.66                             | 47.28  | 62.39 | 80.34  |

| [40]                 | 11.64                                       | 31.85 | 53.68                                            | 27.42  | 21.78 | 17.40                             | 39.06  | 53.63 | 71.08  |

| [41]                 | 10.78                                       | 28.57 | 48.15                                            | 25.43  | 21.71 | 18.4                              | 36.20  | 50.28 | 66.58  |

| [36]                 | 5.58                                        | 13.99 | 23.90                                            | 5.55   | 5.1   | 4.56                              | 11.13  | 19.09 | 27.46  |

| Proposed             | 2.69                                        | 7.43  | 12.72                                            | 8.16   | 6.94  | 5.87                              | 10.85  | 14.37 | 18.59  |

**Fig. 9** The power dissipation map for the proposed 2-input XOR gate with the level 0.5 Ek tunnelling energy at 2-Kelvin temperature

Fig. 10 Half adder logic diagram

On the other hand, the full adder adds three logical variables and provides two outputs, sum and carry. If the input variables are A, B, and  $C_{in}$ , the two outputs can be found using Eq. 5.

$$Sum = (A)XOR(B)XOR(C_{in})$$

Carry = (AB) OR (B C<sub>in</sub>) OR (C<sub>in</sub>A) (5)

By following the logic circuit previously given in Fig. 10, the half adder can be easily designed with proposed XOR gate as illustrated in Fig. 11.

# 4.2 Full Adder

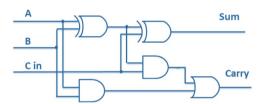

The full adder logic circuit is illustrated in Fig. 12.

Note: the carry equation is the same as the Maj-3 equation, as previously mentioned in Eq. 1. Therefore, the full

-1.000

Transactions on Electrical and Electronic Materials (2020) 21:198-207

-1.000

Input cell

• • • •

Clock zone 0

Clock zone 1 Clock zone 2 Clock zone 3

Fig. 12 Full adder logic diagram

adder circuit can be implemented as shown in Fig. 13. Another form of full adder logical representation that utilizes multi-input majority function and its reliability is studied in [42].

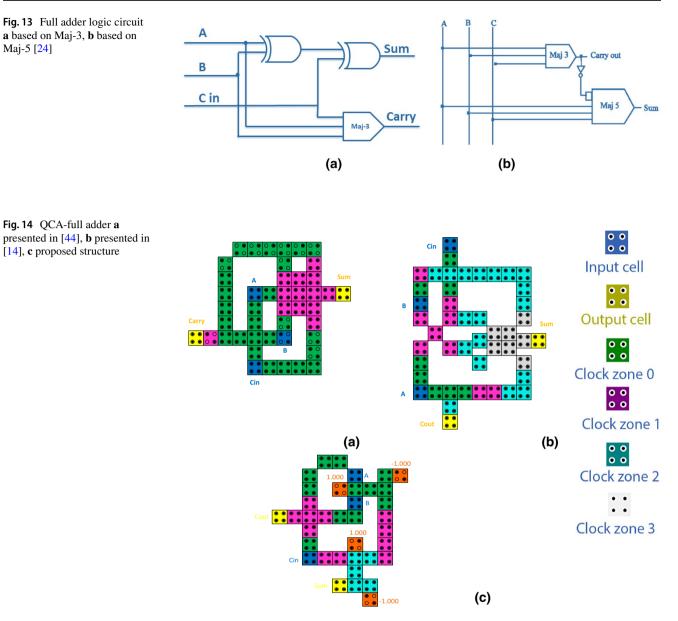

The full adder design approach illustrated in Fig. 13b is adopted in most of previous literatures because it produces more efficient circuit with less complexity (number of cells and circuit layout area) and latency (number of required clock phases to produce output) as the circuits reported in [14, 43, 44] as shown in Fig. 14a, b. On the other hand, the design approach shown in Fig. 13a is not commonly used in QCA circuitry due to the high complexity of the produced circuit and the designs reported in [26, 45]. The proposed XOR in this work solve this issue. It was used to design full adder circuit with QCA technology as shown in Fig. 14c. Maj-5 [24]

# **5** Simulation Results

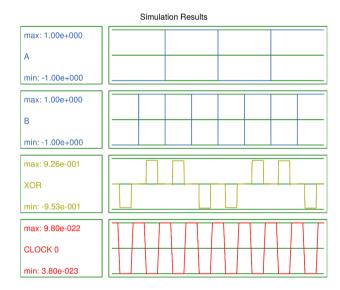

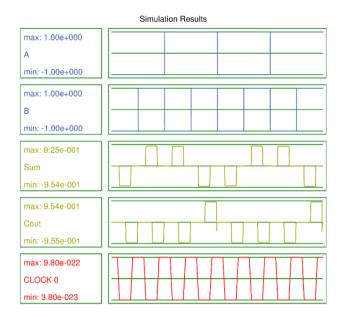

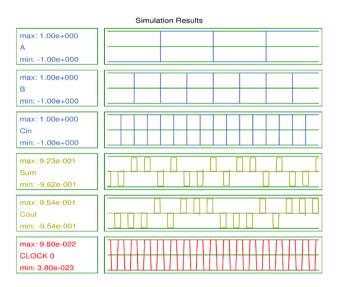

In this work, QCADesigner tool V 2.0.3 [46] is used to simulate the proposed circuits with the simulation parameters shown in Fig. 15. The proposed XOR in Fig. 7c produces the output waveform shown in Fig. 16 and it is clear from the output that the proposed gate shows error-free operation for all input possibilities. From noticing the polarization of the output waveform, it can be concluded that the proposed gate has acceptable robustness. The proposed half adder and full adder circuits are simulated under the same conditions and produced the output waveforms shown in Figs. 17 and 18 respectively. In both circuits, the output was correct for all input states.

The proposed gate is superior in terms of area, number of cells, latency when compared with previous reported designs. Table 3 gives the comparison results. Furthermore, the proposed gate makes a reduction in delay time to 50% compared to best previously reported; where it can be implemented in a <sup>1</sup>/<sub>4</sub> clock cycle of the clock signal defined in Fig. 5. The proposed design requires only 9 cells; while the best previous design required 14 cells. Another important aspect of the proposed design is that it does not require wire crossover.

The results of the comparison for the proposed half adder, with existing designs, are shown in Table 4. From this table, it is obvious that the proposed structure is an optimal design in comparison with previously counterparts. The proposed

| 🔄 Bistable Options                 | – 🗆 X         |  |  |  |  |

|------------------------------------|---------------|--|--|--|--|

| Number Of Samples:                 | 12800         |  |  |  |  |

| Convergence Tolerance:             | 0.001000      |  |  |  |  |

| Radius of Effect [nm]:             | 65.000000     |  |  |  |  |

| Relative Permittivity:             | 12.900000     |  |  |  |  |

| Clock High:                        | 9.800000e-022 |  |  |  |  |

| Clock Low:                         | 3.800000e-023 |  |  |  |  |

| Clock Shift:                       | 0.000000e+000 |  |  |  |  |

| Clock Amplitude Factor:            | 2.000000      |  |  |  |  |

| Layer Separation:                  | 11.500000     |  |  |  |  |

| Maximum Iterations Per Sample: 100 |               |  |  |  |  |

| Randomize Simulation Order         |               |  |  |  |  |

| Animate                            |               |  |  |  |  |

| 💥 <u>C</u> ancel                   |               |  |  |  |  |

Fig. 15 QCADesigner simulation parameters

Fig. 16 Proposed XOR simulation result

half adder is crossover free, with minimum cell number and area. Table 5 details the comparison results of the full adder with existing structures. It is clear from this table that the proposed full adder is distinguished in terms of complexity; where it was implemented using only 39 cells, by improving 15% from the nearest competitor structure presented in [43].

Fig. 17 Proposed half adder simulation result

Fig. 18 Proposed full adder simulation result

# 6 Conclusions

In this paper, a new single layer Exclusive-OR gate design is introduced with QCA technology. The proposed design has a 50% speed improvement and a 35% reduction in the number of cells needed over the best reported XOR. The presented gate is used to design superior half and full adders with a very noticeable reduction in the circuit layout area and number of cells. The proposed XOR gate shows a noticeable reduction in the power dissipation compared to

| Table 3 | Comparison of | proposed XOR with | existing structures |

|---------|---------------|-------------------|---------------------|

|---------|---------------|-------------------|---------------------|

| XOR                          | Area (µm <sup>2</sup> ) | No. of cells | Crossover type | Latency |

|------------------------------|-------------------------|--------------|----------------|---------|

| [47]                         | 0.22                    | 121          | Coplanar       | 1       |

| [48]                         | 0.07                    | 64           | Multilayer     | 1       |

| [49]                         | 0.06                    | 49           | Multilayer     | 1       |

| [50]                         | 0.06                    | 54           | Not required   | 3/4     |

| [ <b>29</b> ] Fig. 8b        | 0.08                    | 84           | Multilayer     | 1       |

| [ <b>29</b> ] Fig. 8c        | 0.07                    | 64           | Multilayer     | 1       |

| [29] Fig. 9                  | 0.06                    | 34           | Not required   | 1 1/4   |

| [29] Fig. 10                 | 0.07                    | 54           | Not required   | 1 1/4   |

| [29] Fig. 11                 | 0.08                    | 52           | Not required   | 2 1/4   |

| [29] Fig. 12                 | 0.09                    | 52           | Not required   | 2 1/4   |

| [29] Fig. 13                 | 0.06                    | 48           | Not required   | 3/4     |

| [ <b>29</b> ] Fig. 14        | 0.07                    | 54           | Not required   | 1 1/4   |

| [29] Fig. 15                 | 0.05                    | 42           | Not required   | 3/4     |

| [51] Fig. 10                 | 0.09                    | 88           | Multilayer     | 1       |

| [ <mark>51</mark> ] Fig. 11a | 0.07                    | 44           | Not required   | 1       |

| [ <mark>51</mark> ] Fig. 11b | 0.09                    | 55           | Not required   | 2       |

| [51] Fig. 11c                | 0.09                    | 62           | Not required   | 1 1/2   |

| [52]                         | 0.17                    | 115          | Coplanar       | 1 1/2   |

| [53]                         | 0.04                    | 40           | Coplanar       | 3/4     |

| [54]                         | 0.08                    | 51           | Coplanar       | 1 1/4   |

| [ <b>55</b> ] Fig. 9a        | 0.16                    | 51           | Coplanar       | 1 1/4   |

| [ <b>55</b> ] Fig. 9b        | 0.09                    | 30           | Not required   | 1       |

| [30]                         | 0.07                    | 49           | Not required   | 2       |

| [56]                         | 0.05                    | 45           | Coplanar       | 1       |

| [37]                         | 0.05                    | 47           | Coplanar       | 1       |

| [ <b>57</b> ] Fig. 8b        | NA                      | 71           | Not required   | 1 3/4   |

| [ <b>57</b> ] Fig. 9b        | NA                      | 72           | Not required   | 1 1/2   |

| [34]                         | 0.04                    | 32           | Not required   | 3/4     |

| [58]                         | 0.09                    | 60           | Coplanar       | 1 1/2   |

| [59]                         | 0.08                    | 54           | Coplanar       | 1 1/2   |

| [32]                         | 0.03                    | 29           | Not required   | 3/4     |

| [41]                         | 0.02                    | 28           | Not required   | 3/4     |

| [60]                         | 0.01                    | 14           | Not required   | 1/2     |

| Proposed                     | 0.01                    | 9            | Not required   | 1/4     |

Table 4

Comparison of proposed half adder with existing structures

| Half adder | Area (µm <sup>2</sup> ) | No. of cells | Crossover type | Latency |

|------------|-------------------------|--------------|----------------|---------|

| [61]       | 0.08                    | 77           | Multilayer     | 1       |

| [50]       | NA                      | 61           | Not required   | 3⁄4     |

| [54]       | NA                      | 65           | Coplanar       | 1 1⁄4   |

| [30]       | 0.08                    | 62           | Not required   | 2       |

| [34]       | 0.05                    | 34           | Not required   | 3⁄4     |

| [38]       | 0.05                    | 44           | Not required   | 1       |

| Proposed   | 0.02                    | 21           | Not required   | 1/2     |

Table 5

Proposed full adder compared to previously reported structures

| Full adder Area (µm <sup>2</sup> ) |       | No. of cells | Crossover type | Latency |  |

|------------------------------------|-------|--------------|----------------|---------|--|

| [ <mark>61</mark> ] Fig. 11        | 0.2   | 192          | Multilayer     | 2       |  |

| [61] Fig. 13                       | 0.114 | 122          | Coplanar       | 1       |  |

| [61] Fig. 14                       | 0.1   | 98           | Multilayer     | 1       |  |

| [26]                               | 0.15  | 120          | Coplanar       | 2 1/2   |  |

| [47]                               | 0.04  | 124          | Multilayer     | 1       |  |

| [54]                               | 0.28  | 150          | Coplanar       | 2 1⁄4   |  |

| [34]                               | 0.14  | 105          | Not required   | 1 1⁄4   |  |

| [14]                               | 0.04  | 49           | Coplanar       | 1       |  |

| [15]                               | 0.28  | 228          | Not required   | 1 3⁄4   |  |

| [45]                               | 0.37  | 221          | Coplanar       | 2       |  |

| [43]                               | 0.04  | 48           | Not required   | 3⁄4     |  |

| [43]                               | 0.04  | 46           | Not required   | 3⁄4     |  |

| Proposed                           | 0.04  | 37           | Not required   | 3⁄4     |  |

the previous designs. The reduction in the complexity of the proposed designs is very encouraging to adapt it to other circuit designs.

# References

- 1. G.Q. Zhang, A. Roosmalen, *More than Moore: Creating High Value Micro/Nanoelectronics Systems* (Springer, Berlin, 2009)

- E. Alkaldy, A.H. Majeed, Bin Zainal, D. Bin Md Nor, Optimum multiplexer design in quantum-dot cellular automata. Indones. J. Electr. Eng. Comput. Sci. 17, 148–155 (2020)

- B. Sen, M. Dutta, M. Goswami, B.K. Sikdar, Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron. J. 45, 1522–1532 (2014)

- S. Sheikhfaal, K. Navi, S. Angizi, A.H. Navin, Designing high speed sequential circuits by quantum-dot cellular automata: memory cell and counter study. Quantum Matter 4, 190–197 (2015)

- A.H. Majeed, E. Alkaldy, BinZainal, D. BinMdNor, Synchronous counter design using novel level sensitive T-FF in QCA technology. J. Low Power Electron. Appl. 9, 27 (2019)

- A.H. Majeed, E. Alkaldy, M. Zainal, K. Navi, D. Nor, in *Optimal Design of RAM Cell Using Novel 2:1 Multiplexer in QCA Technology*, Circuit World (2019)

- A. Majeed, E. AlKaldy, S. Albermany, An energy-efficient RAM cell based on novel majority gate in QCA technology. SN Appl. Sci. 1, 1–8 (2019)

- K. Navi, R. Farazkish, S. Sayedsalehi, M. RahimiAzghadi, A new quantum-dot cellular automata full-adder. Microelectron. J. 41, 820–826 (2010)

- M. Gladshtein, Design and simulation of novel adder/subtractors on quantum-dot cellular automata: radical departure from Boolean logic circuits. Microelectron. J. 44, 545–552 (2013)

- R. Farazkish, F. Khodaparast, Design and characterization of a new fault-tolerant full-adder for quantum-dot cellular automata. Microprocess. Microsyst. 39, 426–433 (2015)

- S. Hashemi, K. Navi, A novel robust QCA full-adder. Procedia Mater. Sci. 11, 376–380 (2015)

- A. Roohi, R.F. DeMara, N. Khoshavi, Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46, 531–542 (2015)

- M. Mohammadi, M. Mohammadi, S. Gorgin, An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

- T.N. Sasamal, A.K. Singh, A. Mohan, An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik Int. J. Light Electron Opt. **127**, 8576–8591 (2016)

- E. Taherkhani, M.H. Moaiyeri, S. Angizi, Design of an ultraefficient reversible full adder-subtractor in quantum-dot cellular automata. Optik Int. J. Light Electron Opt. 142, 557–563 (2017)

- S. Sayedsalehi, M.H. Moaiyeri, K. Navi, Novel efficient adder circuits for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 8, 1769–1775 (2011)

- G.R.Y.T. Rajinder, S. Preeta, K. Anil, Performance evaluation of counter circuit for reversible ALU using QCA and VERILOG HDL. J. Eng. Sci. Technol. 14, 784–796 (2019)

- M.B. Khosroshahy, M.H. Moaiyeri, K. Navi, N. Bagherzadeh, An energy and cost efficient majority-based RAM cell in quantum-dot cellular automata. Results Phys. 7, 3543–3551 (2017)

- M.A. Tehrani, K. Navi, A. Kia-kojoori, Multi-output majority gate-based design optimization by using evolutionary algorithm. Swarm Evol. Comput. 10, 25–30 (2013)

- R. Zhang, P. Gupta, N.K. Jha, Majority and minority network synthesis with application to QCA-, SET-, and TPL-based nanotechnologies. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 26, 1233–1245 (2007)

- M.R. Bonyadi, S.M.R. Azghadi, N.M. Rad, K. Navi, E. Afjei, Logic optimization for majority gate-based nanoelectronic circuits based on genetic algorithm. Int. Conf. Electr. Eng. 2007, 1–5 (2007)

- 22. M. Bagherian Khosroshahy, M. Hossein Moaiyeri, K. Navi, in Design and Evaluation of a 5-Input Majority Gate-Based Content-Addressable Memory Cell in Quantum-Dot Cellular Automata (2017)

- F. Ahmad, An optimal design of QCA based 2 n:1/1:2 n multiplexer/demultiplexer and its efficient digital logic realization. Microprocess. Microsyst. 56, 64–75 (2018)

- M.R. Azghadi, O. Kavehei, K. Navi, A novel design for quantum-dot cellular automata cells and full adders. J. Appl. Sci. 7, 3460–3468 (2007)

- A.H. Majeed, E. AlKaldy, M.S.B. Zainal, D.B.M.D. Nor, A new 5-input majority gate without adjacent inputs crosstalk effect in QCA technology. Indones. J. Electr. Eng. Comput. Sci. 14, 1159–1164 (2019)

- F. Ahmad, G.M. Bhat, P.Z. Ahmad, Novel adder circuits based on quantum-dot cellular automata (QCA). Circ. Syst. 05, 142– 152 (2014)

- P.Z. Ahmad, S.M.K. Quadri, F. Ahmad, A.N. Bahar, G.M. Wani, S.M. Tantary, A novel reversible logic gate and its systematic approach to implement cost-efficient arithmetic logic circuits using QCA. Data Brief 15, 701–708 (2017)

- A.N. Bahar, M.S. Uddin, M. Abdullah-Al-Shafi, M.M.R. Bhuiyan, K. Ahmed, Designing efficient QCA even parity generator circuits with power dissipation analysis. *Alex. Eng. J.* (2017)

- 29. M.R. Beigh, M. Mustafa, F. Ahmad, Performance evaluation of efficient XOR structures in quantum-dot cellular automata (QCA). Circuits Syst. **04**, 147–156 (2013)

- P.Z. Ahmad, F. Ahmad, H.A. Khan, A new F-shaped XOR gate and its implementations as novel adder circuits based quantumdot cellular Automata (QCA). IOSR J. Comput. Eng. (IOSR-JCE) 16, 201 (2014)

- 31. S. Angizi, E. Alkaldy, N. Bagherzadeh, K. Navi, Novel robust single layer wire crossing approach for exclusive OR sum of

🖉 Springer

products logic design with quantum-dot cellular automata. J. Low Power Electron. **10**, 259–271 (2014)

- A.M. Chabi, S. Sayedsalehi, S. Angizi, K. Navi, Efficient QCA exclusive-or and multiplexer circuits based on a nanoelectroniccompatible designing approach. Int. Sch. Res. Not. 2014, 463967 (2014)

- 33. M.G. Waje, P.K. Dakhole, Design and simulation of new XOR gate and code converters using Quantum Dot Cellular Automata with reduced number of wire crossings, in 2014 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2014], pp. 1245–1250 (2014)

- D. Ajitha, K.V. Ramanaiah, V. Sumalatha, An efficient design of XOR gate and its applications using QCA, *i-manager's*. J. Electron. Eng. 5, 22–29 (2015)

- A.N. Bahar, S. Waheed, N. Hossain, M. Asaduzzaman, A novel 3-input XOR function implementation in quantum dot-cellular automata with energy dissipation analysis, *Alex. Eng. J.* (2017)

- A.M. Chabi, A. Roohi, R.F. DeMara, S. Angizi, K. Navi, H. Khademolhosseini, Cost-efficient QCA reversible combinational circuits based on a new reversible gate, in 2015 18th CSI International Symposium on Computer Architecture and Digital Systems (CADS), pp. 1–6 (2015)

- M. Kianpour, R. Sabbaghi-Nadooshan, K. Navi, A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80, 1404–1414 (2014)

- M. Poorhosseini, A.R. Hejazi, A fault-tolerant and efficient XOR structure for modular design of complex QCA circuits. J. Circ. Syst. Comput. 27, 1850115 (2018)

- S. Sheikhfaal, S. Angizi, S. Sarmadi, M. HosseinMoaiyeri, S. Sayedsalehi, Designing efficient QCA logical circuits with power dissipation analysis. Microelectron. J. 46, 462–471 (2015)

- T.N. Sasamal, A.K. Singh, U. Ghanekar, Design and analysis of ultra-low power QCA parity generator circuit, in *Advances in Power Systems and Energy Management: ETAEERE-2016*, ed. by A. Garg, A.K. Bhoi, P. Sanjeevikumar, K.K. Kamani (Springer, Singapore, 2018), pp. 347–354

- G. Singh, R.K. Sarin, B. Raj, A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis. J. Comput. Electron. 15, 455–465 (2016)

- E. Alkaldy, K. Navi, Reliability study of single stage multi-input majority function for QCA. Int. J. Comput. Appl. 83, 2 (2013)

- 43. M. Sarvaghad-Moghaddam, A.A. Orouji, New symmetric and planar designs of reversible full-adders/subtractors in quantum-dot cellular automata, in *CoRR*, abs/1803.11016,/2018

- 44. D. De, J.C. Das, Design of novel carry save adder using quantum dot-cellular automata. J. Comput. Sci. **22**, 54–68 (2017)

- P. Kumari, A. Sharma, A. Singh, Implementation of adder circuit using quantum-dot cellular automata-based logic gates, in *Intelligent Communication, Control and Devices*, Singapore, pp. 173–185 (2018)

- K. Walus, T.J. Dysart, G.A. Jullien, R.A. Budiman, QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3, 26–31 (2004)

- V.C. Teja, S. Polisetti, S. Kasavajjala, QCA based multiplexing of 16 arithmetic; logical subsystems-A paradigm for nano computing, in 2008 3rd IEEE International Conference on Nano/Micro Engineered and Molecular Systems, pp. 758–763 (2008)

- S.K. Lakshmi, G. Athisha, Efficient design of logical structures and functions using nanotechnology based quantum dot cellular automata design. Int. Comput. Appl. 3, 35–42 (2010)

- A. Shahidinejad, A. Selamat, Design of first adder/subtractor using quantum-dot cellular automata. Adv. Mater. Res. 403–408, 3392–3397 (2011)

- 50. H.S. Jagarlamudi, M. Saha, P.K. Jagarlamudi, Quantum dot cellular automata based effective design of combinational and

sequential logical structures. World Acad. Sci. Eng. Technol. 5, 1523–1529 (2011)

- M. Mustafa, M.R. Beigh, Design and implementation of quantum cellular automata based novel parity generator and checker circuits with minimum complexity and cell count. Indian J. Pure Appl. Phys. 51, 60–66 (2013)

- 52. M.G. Waje, P.K. Dakhole, Design and implementation of 4-bit arithmetic logic unit using quantum dot cellular automata, in 2013 3rd IEEE International Advance Computing Conference (IACC), pp. 1022–1029 (2013)

- M. Goswami, B. Kumar, H. Tibrewal, S. Mazumdar, Efficient realization of digital logic circuit using QCA multiplexer, in 2014 2nd International Conference on Business and Information Management (ICBIM), pp. 165–170 (2014)

- S. Santra, U. Roy, Design and implementation of quantum cellular automata based novel adder circuits. Int. J. Comput. Electr. Autom. Control Inf. Eng. 8, 168–173 (2014)

- S. Santra, U. Roy, Design and optimization of parity generator and parity checker based on quantum-dot cellular automata. Eng. Technol. Int. J. Comput. Inf. Syst. Control Eng. 8, 491–497 (2014)

- M. Kianpour, R. Sabbaghi-Nadooshan, Novel design of n-bit controllable inverter by quantum-dot cellular automata. Int. J. Nanosci. Nanotechnol. 10, 117–126 (2014)

- 57. S.-H. Shin, J.-C. Jeon, K.-Y. Yoo, Design of wire-crossing technique based on difference of cell state in quantum-dot cellular automata. Int. J. Control Autom. **7**, 153–164 (2014)

- 58. M.T. Niemier, P.M. Kogge, *Designing Digital Systems in Quantum Cellular Automata* (Notre Dame, Paris, 2004)

- S. Hashemi, R. Farazkish, K. Navi, New quantum dot cellular automata cell arrangements. J. Comput. Theor. Nanosci. 10, 798– 809 (2013)

- A.M. Chabi, A. Roohi, H. Khademolhosseini, S. Sheikhfaal, S. Angizi, K. Navi et al., Towards ultra-efficient QCA reversible circuits. Microprocess. Microsyst. 49, 127–138 (2017)

- S.K. Lakshmi, G. Athisha, Design and analysis of adders using nanotechnology based quantum dot cellular automata. J. Comput. Sci. 7, 1072–1079 (2011)

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.