## Design and implement of LED drive circuit chip with the controllable constant output current\*

LI Xian-rui(李先锐)1\*\*, WANG Song-lin(王松林)<sup>2</sup>, LAI Xin-quan(来新泉)<sup>1</sup>, and LI Yu-shan(李玉山)<sup>1</sup>

1. Institute of Circuit Design, Xi'an University of Electronic Science and Technology, Xi'an 710071, China.

2. School of Electronic Engineering, Xi'an University of Electronic Science and Technology, Xi'an 710071, China.

(Received 16 February 2009)

Owing to the fact that the LED drive circuit must have constant output current control, we propose a controlled current driver with a high precision for the white light LED. Three discrete constant current settings are available and may be selected at the supply voltage from 2.9 V to 4.4 V, which is up to 1 A. An autozero transconductance amplifier is proposed, which effectively improves the precision, reduces the offset voltage and the noise. The variation in the ratio of the external resistor current to the LED load current is less than 2.3%, when the LED load current changes from 200 mA to 800 mA. **Document code:** A **Article ID:** 1673-1905(2009)03-0186-4

DOI 10.1007/s11801-009-8188-6

In order to lower the influence on the precision of output current, an autozero technique is applied to remove the offset of the amplifier and improve the precision of the output current<sup>[1]</sup>. A serial connection is superior to a parallel connection, because a constant current can be simply supplied to each LED that belongs to an array. However, the total voltage and total current of a serial connection vary, depending on the occurrence of short circuit LED breakdowns. Consequently, the LED drive circuit must have constant output current control and/or constant-luminance control.

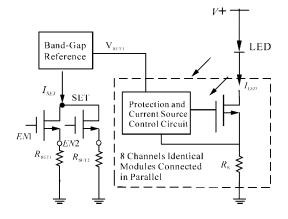

In this paper we use an external resistor to control the output driving current, which has a wide range, and the maximum of 1 A. The circuit structure is shown in Fig.1, which consists of the band-gap reference voltage source, the programmable control current circuit and the current source control output circuit. The programmable control current circuit is composed of external resistors  $R_{\text{SET1}}$  and  $R_{\text{SET2}}$ , which is controlled by enable signals *EN*1 and *EN*2. In the different enable case, the different reference voltages of  $V_{\text{REF1}}$  can be obtained by changing the value of external resistors  $R_{\text{SET1}}$  and  $R_{\text{SET2}}$ . The current source control circuit consists of 8 identical modules connected in parallel.

In Fig.1,  $R_{\rm s}$  is the sampling resistance, and  $I_{\rm LED}$  is the drive current of LEDs and is represented as,

$$V_{\text{REF1}} = K \cdot V_{\text{REF}} \quad , \tag{1}$$

$$I_{\text{LED}} = 8 \cdot \frac{V_{\text{REF1}}}{R_{\text{S}}}.$$

(2)

From eq.(1) and eq.(2), it can be seen that  $I_{\text{LED}}$  is dependent on the gain *K*, the reference voltage  $V_{\text{REF}}$  and  $R_{\text{s}}$ . But the gain *K* is associated with the external resistors. Therefore, if  $V_{\text{REF}}$  is given, the output current is controlled by the external resistor.

Fig.1 Schematic diagram of constant current driver

Fig.2 shows the complete circuit schematics in the design. The current source control circuit and the complete bandgap reference consist of four circuit blocks: the bias circuit,

<sup>\*</sup> This work has been supported by the National Natural Science Foundation of China(No. 60876023)

<sup>\*\*</sup> E-mail: lixianrui4213@126.com

(3)

the startup circuit, the core reference and the controlled reference. There are two state equilibrium points in the bias circuit. One is a designed operating point that we need (which can be referred to as a non-zero state equilibrium point), that is to say, current mirrors formed by M1-M4 that enforce branch currents equal to a proportional-to-absolute-temperature(PTAT)I, which is generated by Q1,Q2 and R1.

The emitter area of Q1 is eight times of Q1 in the bias circuit. So M1-M4 respectively has the same current that is shown in the eq.(3).The bias current of the other circuits can be supplied by  $I_1$  mirroring.

(PTAT) I, which is generated by

$$Q_1, Q_2$$

and  $R_1$ .

$M_1 \rightarrow M_2 \rightarrow M_3 \rightarrow M_1 \rightarrow M_1$

$I_{1,i} = \frac{k \ln 8}{2} T$

Fig.2 Schematic of the band-gap reference and the controlled current

Another state equilibrium point of the bias circuit is the state that M1-M4 is turned off (which can be referred to as a zero state equilibrium point) and  $I_1-I_4$  is zero. A startup circuit is required to make sure that enough current flows to force operation at the designed operating point.

The startup circuit used in the design is constituted by M5-M8. When the supply is turned on and the gate of M8 is pulled high and the drain of M8 is pulled low, consequently the gates of M6-M7 are pulled low which inject current to the bias circuit. Once the currents flow through the bias circuit, the drain of M4 becomes high and this pulls the gates of M3-M4 high which pulls the gate of M5 down, as a consequence, the gates of M6-M7 are pulled high leaving this transistor in cut off and eventually making the startup circuit idle.

The reference core circuit consists of R3-R5, Q3-Q4 and the operation amplifier. The operation amplifier enforces the invert and non-invert ports to have the same potential, and due to R3 = R4, currents flowing through R3 and R4 are equal as consequence currents flowing through Q3 and Q4 are equal. Considering that the ratio emitter area of Q3 and Q4 is 8:1, the output voltage of the reference can be expressed as follows,

$$V_{\text{REF}} = V_{BE4} + \frac{2R_2 + R_4}{R5} \frac{k \ln 8}{q} T, \qquad (4)$$

The controlled reference circuit consists of R6, M11-M12

and the operation amplifier A1. The voltage follower formed by A1 and M11 enforces the voltage of node SET following the output voltage of the reference. The gain of the current mirror formed by M11 and M12 is N, which amplifies the current of  $I_{\text{SET}}$ . The output voltage of the controlled reference is controlled by external resistors and the enabling port (*EN*1 and *EN*2).

$$V_{\text{REF1}} = N \cdot \frac{V_{\text{REF}}}{R_{\text{SETX}}} \cdot R_6 \quad . \tag{5}$$

The current source control circuit is formed by an operation amplifier A2, M13 and the sampling resistance  $R_{\rm s}$ . When the output driving current is under the value  $V_{\rm REF1}/R_{\rm s}$ , the drop voltage of  $R_{\rm s}$  is smaller than the voltage of  $V_{\rm REF1}$ , and therefore, the output of the operation amplifier is pulled high which increases the output current. In the balance state, the drop voltage of  $R_{\rm s}$  can be clamped to the value of  $V_{\rm REF1}$ . In order to enhance the driving capability, there are 8 identical current source control circuits in parallel to drive the LEDs. Considering the offset voltage of the operation amplifier, the eq.(2) is modified, and we get the eq.(6),

$$I_{\text{LED}} = 8 \cdot \frac{V_{\text{REF1}} + V_{\text{OS}}}{R_{\text{S}}} \qquad . \tag{6}$$

The eq.(6) tells us that the offset voltage of the operation

amplifier has great influence on the precision of the output current, so an autozero technique is applied to reduce the offset voltage of the operation amplifier.

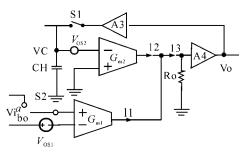

The basic schematic of the autozero technique (AZT) operation amplifier<sup>[5,6]</sup> is shown in Fig.3, which includes the base amplifier  $G_{m1}$ , the compensating amplifier  $G_{m2}$ , the second stage amplifier  $A_4$ , the feedback amplifier  $A_3$ , the holdcapacitor  $C_h$  and two switches  $S_1$  and  $S_2$ .  $R_o$  is the output impedance of  $G_{m1}$  and  $G_{m2}$ .

Fig.3 AZT amplifier principle schematic

1) During the sampling phase, the  $S_2$  switch is connected with the point b, so that it connects the  $G_{m1}$  stage inputs together, so  $G_{m1}$  has only its own offset voltage applied at the input. As a result, it generates an output offset current,

$$I_1 = G_{m1} \cdot V_{os1} \quad . \tag{7}$$

The  $S_1$  switch is also on and  $A_3$  amplifier feedbacks the output voltage to the  $G_{m2}$  inverting input.  $G_{m2}$  outputs current,  $I_2$  is given by

$$I_2 = -G_{m2} \cdot (A_3 V_o - V_{os2}) \quad , \tag{8}$$

$$V_{a} = R_{a}(I_{1} + I_{2})A_{4} \quad , \tag{9}$$

where  $V_{os2}$  is the input offset voltage of  $G_{m2}$ , and  $V_o$  is output voltage. This current tries to compensate the base amplifier offset current, so it has an opposite direction and is proportional to the output offset voltage.

With eqs. (7) and (8), we can get the offset voltage  $V_{\rm C}$

$$V_{C} = A_{3}V_{o} = A_{3}A_{4} \frac{G_{m1}R_{o}V_{os1} + G_{m2}R_{o}V_{os2}}{1 + A_{4}A_{3}R_{o}G_{m2}} .$$

(10)

2) During the signal processing phase, the  $S_2$  switch is connected with the point a, and it causes that the base amplifier  $G_{\rm m1}$  is connected to the signal path. The feedback loop is disconnected ( $S_1$  is off). At this time,  $V_{\rm C}$  is stored in  $C_{\rm h}$ . Because the switches are implemented by MOS transistors in CMOS circuit, the AZT operation analysis must include the charge injection effects that take place during the transition among phases<sup>[7]</sup>.

When the switch  $S_1$  is turned off, the part of the channel charge is injected in the  $V_c$  node, changing the voltage stored on  $C_b$ . The variation of the voltage is,

$$\Delta V_c = q_{inj} / C_h \quad . \tag{11}$$

The total output voltage is,

$$V_{o} = G_{m1}R_{o}A_{4}V_{i} + A_{4}\frac{G_{m1}R_{o}V_{os1}}{1 + G_{m2}R_{o}A_{3}A_{4}} + A_{4}\frac{G_{m2}R_{o}V_{os2}}{1 + G_{m2}R_{o}A_{3}A_{4}} - A_{4}G_{m2}R_{o}\frac{q_{inj}}{C_{h}} , \qquad (12)$$

where  $V_i$  is the input signal, and the residual offset voltage  $V_{OSres}$  is an output voltage for a zero differential input, divided by the differential voltage gain.

$$V_{OSres} = \frac{V_o |_{Vi=0}}{G_{m1}R_o A_4} = \frac{V_{OS1}}{G_{m2}R_o A_3 A_4} + \frac{V_{OS2}}{G_{m1}R_o A_3 A_4} - \frac{G_{m2}}{G_{m1}}\frac{q_{inj}}{C_h} \quad .$$

(13)

From the equation (13), we can know that the offset voltage of  $G_{m1}$  is divided to the  $G_{m1}R_{0}A_{3}A_{4}$  ratio, and the offset voltage of  $G_{m2}$  is reduced by  $G_{m2}R_{0}A_{3}A_{4}$  ratio.

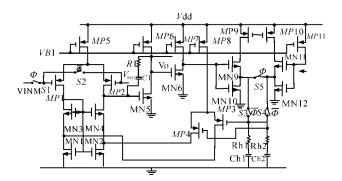

The AZT amplifier complete schematic is presented in Fig.4. There are five switches in the circuit. During the sampling phase,  $S_2$ ,  $S_3$  and  $S_4$  are short connected, and  $S_1$  and  $S_5$  are turned off. The two transconductance stages,  $G_{m1}$  and  $G_{m2}$  are respectively composed of two differential pairs. $G_{m1}$  is implemented by MP1 and MP2.  $G_{m2}$  consists of the fold-cascode parts MP3, MP4 and MN3, MN4. Amplified by three stages, the offset voltage is stored in  $C_{h1}$  by the follower MN9.

Fig.4 AZT amplifier implementation

During the signal processing phase,  $S_2$ ,  $S_3$  and  $S_4$  are turned off, but  $S_1$  and  $S_5$  are short connected, so it makes the offset voltage subtracted from the input signal. The bias circuit is composed of *MP5-MP16*. *VB1* and *VB2* are external bias signals.  $R_1$  and  $C_1$  form the miller compensation circuit.

Based on the Hynix 0.6 µm CMOS process, the circuit is

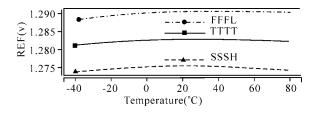

simulated using Hspice. Fig.5 shows the temperature response of the corners when the supply voltage is 3 V. We observe that the output variation of the band-gap reference in the temperature range from -40 °C to 85 °C is 1 mV, and the difference is smaller than 15 mV at all three process corners.

Fig.5 The reference voltage under three process corners

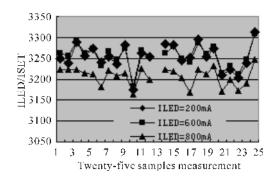

The twenty-five samples measurement results of the output current  $I_{\text{LED}}$  and  $I_{\text{LED}}/I_{\text{SET}}$  are shown in Fig.6. The value of  $I_{\text{LED}}/I_{\text{SET}}$  is between 3314 to 3165. The current precision is 2.3%.

Fig.6 The measurement result of the output current  $I_{\text{LED}}$  and  $I_{\text{LED}}/I_{\text{SET}}$

Tab.1 shows the electrical characteristics of the chip with the constant current driving circuit. We observe that the leakage voltage of  $I_{LED}$  will increase with the increase of the driving current, and the leakage voltage is 115 mV when the driving current is 200 mA. The overcurrent detection current  $I_{SET}$ should not exceed 330 µA. When it is above 330 µA, the overcurrent protection will make the driving output current zero.

Tab.1 Electrical characteristics of the chip with constant current driver

| $V_{\rm IN}$ =3.6 V, $T_{\rm A}$ = 25 °C         | ( LED is externally connected with 5V)            |      |      |      |

|--------------------------------------------------|---------------------------------------------------|------|------|------|

| Parameter                                        | Test conditions                                   | Min  | Тур. | Max. |

| Current Ratio( $I_{\text{LED}}/I_{\text{SET}}$ ) | $I_{\rm LED} = 200 \text{ mA to } 800 \text{ mA}$ | 3165 | 3243 | 3314 |

| $I_{\text{LED}}$ dropout voltage (mV)            | $I_{\text{LED}} = 200 \text{ mA}$                 |      | 115  |      |

| $I_{\text{SET}}$ overcurrent current ( $\mu$ A)  |                                                   |      |      | 330  |

| Overtemperature protection (°C)                  |                                                   | 140  |      | 160  |

In summay, this paper refers a high precision constant current driving circuit that can be applied in LED chargepump DC-DC chip. With an autozero technique, the internal circuit can reduce the offset voltage of the operation amplifier and improve the precision of the output current greatly. By regulating the value of the external resistors, different constant driving current can be provided, which is up to 1A. When the driving current varies from 200 mA to 800 mA, the variation of  $I_{\text{LED}}/I_{\text{SET}}$  is less than 2.3%. This circuit also can be applied to drive large LED array.

## References

- PIAO Yan, WANG Rui-guang, and DING Tie-fu. Journal of Optoelectronics • Laser, 19 (2008), 125 (in Chinese)

- [2] ZHAO Huan, XU Wen-hai, and LU Yong-jun, Journal of Optoelectronics • Laser, 18 (2007), 1314 (in Chinese)

- [3] WANG Hui, WANG Song-lin, and LAI Xia-quan, Journal of Xi'an University, 35 (2008), 272 (in Chinese)

- [4] WANG Hongyi, WANG Songlin, and LAI Xinquan, Microeletronics, 35 (2003), 415.

- [5] C. Enz, and G. Temes, Proceedings of the IEEE, 1996.

- [6] Danchiv, M. Bodea, and C. Dan, International Semiconductor Conference, 2 (2006), 409.

- [7] Razavi B. Design of analog CMOS integrated Circuit. Translated by Chen Guican, Cheg Jun, and Zhang Ruizhi, Xi'an Jiaotong University Press, 2003.