# Effect of Thickness and Thermal Treatment on the Electrical Performance of 2D MoS<sub>2</sub> Monolayer and Multilayer Field-Effect Transistors

B. A. Muñiz Martínez<sup>1</sup> · Mario Flores Salazar<sup>2</sup> · M. G. Syamala Rao<sup>2</sup> · Andrés de Luna Bugallo<sup>2</sup> · R. Ramirez-Bon<sup>1</sup>

Received: 22 September 2023 / Accepted: 28 December 2023 / Published online: 25 January 2024 © The Author(s) 2024

#### Abstract

We deposited high-quality molybdenum disulfide (MoS<sub>2</sub>) monolayer and multilayer crystals on SiO<sub>2</sub>/Si substrates, by means of a chemical vapor deposition (CVD) process at atmospheric pressure. Notably, NaCl salt was used as component of the precursors to assist the growth of  $MoS_2$  crystals, which were intended for use as the active channel layer in the fabrication of field-effect transistors (FETs). The resulting MoS<sub>2</sub> crystals from this CVD process were analyzed by optical, scanning electron, and atomic force microscopies, and by Raman and photoluminescence spectroscopies. The optical images and the micrographs obtained by SEM revealed the formation of dispersed  $MoS_2$  crystals with a triangular shape all over the SiO<sub>2</sub> surface. The thickness of the MoS<sub>2</sub> crystals, analyzed by atomic force microscopy, showed minimum values of around 0.7 nm, confirming the formation of monolayers. Additionally, multilayers with larger thickness were also identified. The Raman and photoluminescence spectra of the  $MoS_2$  crystals corroborated the formation of single and multiple layers. The fabrication of the FET back-SiO<sub>2</sub> -gate configuration was made by depositing patterned source and drain Ti contacts on the dispersed  $MoS_2$  crystals to achieve the Ti/MoS<sub>2</sub>/SiO<sub>2</sub>/Si layer stacks.  $MoS_2$ -based FETs with one and three layers were assembled and their electrical response analyzed by I-V output and transfer curves showing the typical characteristics of an *n*-type semiconductor channel operating in depletion mode. The electrical performance parameters of the devices, such as mobility and threshold voltage, were also determined from this analysis. Finally, to enhance their electrical response, the MoS<sub>2</sub>-based devices were thermally annealed at 200 °C for 30 min in Ar atmosphere. The increase in the mobility of the device was 176% compared to the device before the treatment.

Keywords Chemical vapor deposition  $\cdot$  2D materials  $\cdot$  FETs  $\cdot$  MoS<sub>2</sub>

# Introduction

Two-dimensional (2D) layered semiconductor materials, specifically transition metal dichalcogenides (TMDs), have garnered significant interest for their potential applications in numerous electronic and optoelectronic devices.<sup>1,2</sup> These materials possess unique properties, including atomic thinness, a surface free of dangling bonds, a direct energy band

in monolayer form, and relatively high carrier mobility.<sup>3–5</sup> Among 2D TMDs, layered molybdenum disulfide  $(MoS_2)$ has recently been considered of special importance, and it has emerged as a promising semiconductor material in the application of next-generation electronic devices due to its unique electrical and optical properties.<sup>6,7</sup> For example, 2D MoS<sub>2</sub> field-effect transistors (FETs) have attracted considerable attention as potential building blocks for high-performance, low-power, next-generation electronics devices, and a variety of potential applications in the field of sensors and RF switching devices have been explored.<sup>8–11</sup> The understanding of the electrical response and performance characteristics of 2D MoS<sub>2</sub>-based FETs is crucial for their successful integration into practical applications. Several techniques have been employed to achieve the 2D MoS<sub>2</sub> semiconductor layers in FETs, CVD being one of the most convenient for this purpose.<sup>12-14</sup> Other techniques, such as atomic layer

R. Ramirez-Bon rrbon@cinvestav.mx

<sup>&</sup>lt;sup>1</sup> Centro de Investigación y de Estudios Avanzados del IPN, Unidad Querétaro Apdo, Postal 1-798, 76001 Querétaro, Querétaro, México

<sup>&</sup>lt;sup>2</sup> Centro de Física Aplicada y Tecnología Avanzada, Universidad Nacional Autónoma de México, Campus Juriquilla, C.P. 76230 Querétaro, Qro, Mexico

deposition,<sup>15</sup> mechanical exfoliation,<sup>16</sup> and liquid-phase exfoliation<sup>17</sup> have also been widely explored to obtain 2D MoS<sub>2</sub> layers with controlled thickness and quality. However, mechanical exfoliation or layer transfer methods are not ideal for large-scale manufacturing due to their complex processes and uncertain control over size and layer number of the 2D layers. Chemical vapor deposition (CVD) has emerged as a reliable and promising synthesis method for 2D TMDs, enabling the deposition of monolayers, discrete triangular islands, and continuous thin-to-thick-layer films, offering precise control over film thickness and interface quality.<sup>18</sup> This is why CVD is a widely adopted technique for the growing of high-quality 2D TMDs, including MoS<sub>2</sub>. Recently, it has been demonstrated that assisted synthesis using alkali metal halides (AMH), like NaCl, KBr, KCl, etc., plays a crucial role in the growth of different TMDs.<sup>19,20</sup> This process induces the formation of volatile compounds that interact more effectively with the sources of the transition metal and chalcogen, thereby enhancing the characteristics of the deposit, such as size and crystalline quality. It even influences the growth of specific TMDs like ReS<sub>2</sub>, MoSe<sub>2</sub>, and WSe<sub>2</sub>.

2D MoS<sub>2</sub>-based FETs have shown several advantages such as good thermal stability, high carrier mobility, excellent on/off ratio, and great compatibility with flexible substrates.<sup>21,22</sup> Therefore, the research in this topic is of current interest, including the efforts to advance in fabrication techniques, design of device structures, and the analysis of the performance characteristics. These devices are promising for a wide range of applications. They can be utilized in integrated circuits for digital and analogic electronics, as well as in flexible and wearable devices due to their mechanical flexibility.<sup>23,24</sup> Furthermore, the strong light-matter interaction of 2D MoS<sub>2</sub> due to its direct energy band gap is excellent for potential application in optoelectronic devices, including photodetectors and light-emitting transistors.<sup>25–28</sup> The typical device structure consists of a back-gated structure, where the 2D MoS<sub>2</sub> layer deposited on the dielectric gate material is the semiconductor channel. The selection of the dielectric gate material is critical because it has a great influence on the device performance parameters, such as carrier mobility, threshold voltage, and on/off ratio. Some commonly reported dielectric gate materials employed to assemble 2D MoS<sub>2</sub>-based FETs are SiO<sub>2</sub>, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>.<sup>29-32</sup>

In this paper, we report the synthesis of 2D  $MoS_2$  semiconductor crystals by an atmospheric pressure CVD (APCVD) AMH assisted method, using NaCl as growth promoter, and its application as active layers in FETs with a SiO<sub>2</sub> dielectric gate. To assemble the FETs with a back-gate configuration, the 2D  $MoS_2$  crystals were deposited on Si/SiO<sub>2</sub> wafers and, by means of a lift-off photolithography

process, source and drain Ti contacts were evaporated on some of these dispersed crystals to complete the devices. This procedure enables the fabrication of FETs with either single or multiple layers of 2D  $MoS_2$ . The aim of the paper is to determine the effect of the MoS<sub>2</sub> active layer thickness on the electrical response of the assembled FETs, as well as the impact of post-deposition thermal annealing treatment. For this, we include here the description of the APCVD process and the analysis of the main characteristics of the 2D MoS<sub>2</sub> crystals by spectroscopic and microscopic techniques. Moreover, the electrical responses of two types of 2D MoS<sub>2</sub>-based FETs have been investigated, with the semiconductor active layer consisting of a single layer and three layers of 2D MoS<sub>2</sub> crystals, respectively. The fabricated devices exhibited typical characteristics of an *n*-type channel working in the depletion mode. Finally, to enhance the performance of the 2D MoS<sub>2</sub>-based FETs, a heat treatment at 200 °C for 30 min was conducted, which resulted in an increase of the drain current and enhanced mobility with lowering of the threshold voltage for both types of devices.

## Experimental

## 2D MoS<sub>2</sub> CVD Growth

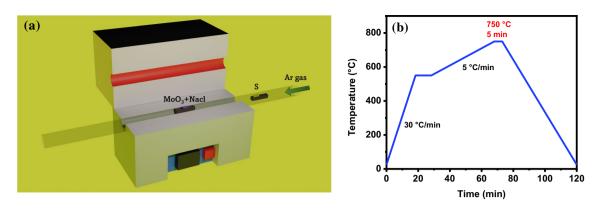

Monolayers and multilayers of MoS<sub>2</sub> were synthesized using the APCVD method. The 2D MoS<sub>2</sub> crystals were deposited on  $25 \times 15 \text{ mm}^2$  pieces of SiO<sub>2</sub>(300 nm)/Si substrates (p-type, B-doped, orientation 100, 1–10 Ohm cm). Prior to the deposition, the organic and inorganic residuals on the substrates were removed through sequential ultrasonic baths in acetone and isopropyl alcohol. Figure 1a displays the experimental setup and Fig. 2b the temperature ramp of the CVD process for MoS<sub>2</sub> growth. An alumina boat loaded with the blend of 30 mg of molybdenum dioxide (MoO<sub>2</sub>; 99.0%; Sigma Aldrich) precursor powder with 1 mg of NaCl (99.0%; Sigma Aldrich) was placed in the center of a tube furnace. The Si/SiO<sub>2</sub> substrate was positioned in the center of the boat with the polished side facing down. Another alumina boat with 150 mg of S (99.5%; Alfa Aesar) was placed upstream at the edge of the furnace. The distance between these two boats was optimized to approximately 19 cm. At the beginning of the heating process, 80 sccm of Ar was introduced into the system as a carrier gas and remained throughout the process. As shown in Fig. 1b, the temperature was gradually increased from room temperature up to 550 °C at a rate of 30 °C/min, and then, after 5 min, increased again up to 750 °C at 5 °C/min. This temperature, 750 °C, was kept for 5 min, and, finally, the furnace is naturally cooled to room temperature.

Fig. 1 (a) Schematic of the setup of the CVD process, and (b) variation of the furnace temperature during the MoS<sub>2</sub> growth CVD process.

#### **MoS<sub>2</sub> Device Fabrication**

The FETs were fabricated by covering the  $MoS_2$  crystals deposited on the SiO<sub>2</sub> dielectric surface by the CVD process with a patterning of source and drain Ti contacts. For the patterning, a lift-off layer (500 nm) (LOR 5A; Micro Chemical) and a 1.9- $\mu$ m-thick photoresist layer (Microposittm S1818TM) were initially spin-coated at 1000 rpm for 10 s (step 1) and 4000 rpm for 40 s (step 2). Subsequently, the lift-off layer and the photoresist were baked on a hot plate at 170 °C and 110 °C, respectively, for 2 min. After annealing, UV light was exposed for 13 s using a photomask aligner (Mask Aligner and UV Exposure System 83210), and the photoresist layer was developed for 30 s. Then, the source (S) and drain (D) Ti (100 nm) ohmic contact electrodes were deposited using a DC magnetron sputtering system. Finally, the lift-off process removed the photoresist layers.

#### Materials and Devices Characterization

Scanning electron microscope (SEM; JXA-8530F; JEOL) was utilized for capturing images to determine the shape of the  $MoS_2$  crystals. The surface morphology and thickness (number of layers) of the 2D  $MoS_2$  crystals on the SiO<sub>2</sub> surface were examined by using an atomic force microscope (AFM; INNOVA; Bruker). The optical characteristics of the CVDgrown  $MoS_2$  were evaluated through Raman spectroscopy and photoluminescence (PL) spectroscopy (Labram HR Evolution; HORIBA Scientific). The electrical response of the 2D  $MoS_2$ -based FETs was analyzed from current–voltage measurements in a dark environment at room temperature performed with a semiconductor parameter analyzer (Keithley 4200).

#### **Results and Discussion**

#### 2D MoS<sub>2</sub> Single and Multilayers

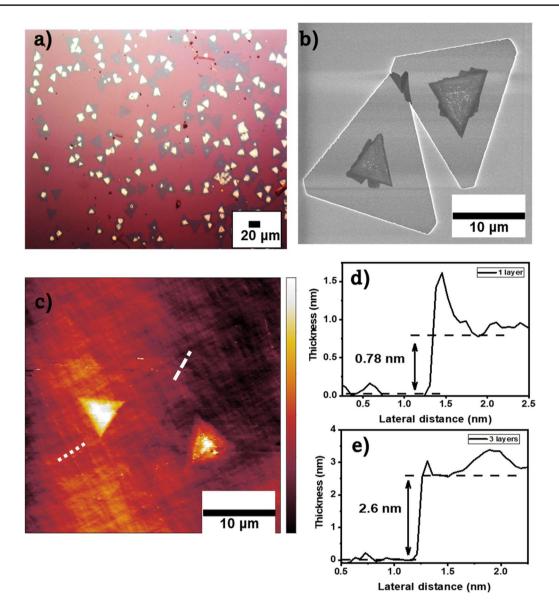

Figure 2a shows an optical image of the deposited  $MoS_2$ on the SiO<sub>2</sub> surface, from which it can be seen that there is a typical random distribution of triangular-shaped MoS<sub>2</sub> crystals dispersed throughout the substrate surface. The different dark and bright colors of the MoS<sub>2</sub> crystals in this image are directly related to the presence of monolayers and multilayers.<sup>33</sup> These features are characteristics of the CVD growth of 2D MoS<sub>2</sub> crystals. The SEM image in Fig. 2b is a higher-amplification image of these crystals, where two triangular MoS<sub>2</sub> crystals are observed. The triangles have a size of around 20  $\mu$ m and not sharp corners but truncated, which is attributed to the Mo:S atomic ratio reacting on the substrate.<sup>34</sup> In addition, smaller triangular MoS<sub>2</sub> crystals with sharp corners grew on the center of both truncated triangles, evidencing the formation of multilayers in a partial area. In both cases, several triangles stack at the center of the larger triangle. A topography analysis, performed by AFM and shown in Fig. 1a, corroborated the coexistence of monolayers and multilayers among the MoS<sub>2</sub> crystals. The AFM image in Fig. 2c displays a large triangular MoS<sub>2</sub> crystal, in which two straight dotted lines are drawn, one at the center of one of the triangle sides and the other one around one corner, respectively. The height profiles along these lines are shown in Fig. 2d and e for the line at the center of the side and the corner, respectively. These profiles reveal that the height steps between the MoS<sub>2</sub> crystal and the SiO<sub>2</sub> substrate at these points are 0.78 and 2.6 nm, respectively. The height of the step at the center of the triangle of the MoS<sub>2</sub> crystal coincides with the reported value for the thickness of a MoS<sub>2</sub> monolayer.9,10,13,35 Meanwhile, the height step around the corner, 2.6 nm, suggests the formation of a stack of three

**Fig.2** (a) Optical and (b) SEM images of  $MoS_2$  crystals grown by CVD on  $SiO_2/Si$  at 750 °C for 5 min. (c) AFM image of the  $MoS_2$  crystals on the  $SiO_2/Si$  substrate. Height profile of a  $MoS_2$  (d) monolayer (*dotted line* AFM image) and (e) trilayer (*dashed line* AFM image).

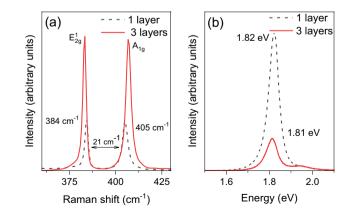

$MoS_2$  monolayers (trilayer) in this zone. The monolayer and trilayer of  $MoS_2$ , as identified in Fig. 2c, were further analyzed by Raman and photoluminescence spectroscopy. The Raman spectra of crystals display two characteristic Raman peaks ,as shown in Fig. 3a. For the monolayer,<sup>36</sup> the peak related to the out-of-plane vibrations of S atoms ( $A_{1g}$ ) is observed at ~ 405 cm<sup>-1</sup>, and for the in-plane vibrations of S and Mo atoms ( $E_{12g}$ ) at ~ 384 cm<sup>-1</sup>. The difference between the positions of the  $A_{1g}$  and  $E_{12g}$  Raman peaks is related to the thickness of the MoS<sub>2</sub> crystals. In our case, this difference is ~ 21 cm<sup>-1</sup>; this value has been reported for single layers of MoS<sub>2</sub> crystals, corroborating that it is a monolayer.<sup>37</sup> As observed in Fig. 3a, in the trilayer MoS<sub>2</sub> spectrum, the  $A_{1g}$  Raman peak shifts towards higher energy

Fig. 3 (a) Raman and (b) PL spectra of the monolayer and the trilayer of  $MoS_2$  crystals shown in Fig. 2c.

values. This is because it is associated with the out-of-plane vibration of S atoms, and the vibrational energy of the lattice decreases as the underlying layer feels the electric potential of the  $MoS_2$  layers above. For the  $E_{12g}$  mode, the Raman peak shifts towards lower energy values, as it is associated with the in-plane vibration of the atoms. With an increasing number of layers, the electrostatic repulsion force between the atoms increases, resulting in a lower vibrational energy of the mode. As a result, the difference between the  $A_{1\sigma}$ and  $E_{12g}$  Raman peaks increases with the number of layers of the MoS<sub>2</sub> crystals; for the trilayer, the measured value is 23 cm<sup>-1</sup>.<sup>38</sup> The photoluminescence spectra of MoS<sub>2</sub> crystals also exhibit a strong dependence on the number of layers. Due to the two-dimensional confinement, monolayers of MoS<sub>2</sub> have a direct band gap of 1.82 eV, which enables a strong photoluminescence emission. On the other hand, MoS<sub>2</sub> in multilayers has an indirect band gap that is smaller than 1.81 eV, resulting in a much weaker emission intensity<sup>39</sup>. Figure 3b shows the photoluminescence spectra acquired at room temperature in the same points where the Raman measurements were performed for the monolayer and trilayer of MoS<sub>2</sub>. Both spectra display an emission band at 1.82 eV related to exciton A.<sup>40</sup> As expected, the emission intensity of the monolayer is much higher than that of the trilayer in these spectra. The transition of  $MoS_2$  from direct band gap to an indirect band gap material by the increasing the number of layers also produces a red shift of the emission band,<sup>41</sup> which is observed in these photoluminescence spectra. Furthermore, a second contribution to the emission can be observed at higher energies due to the spin–orbit coupling present in these semiconductors. There is a degeneracy in the valence band, allowing for another transition at the same high-symmetry point near the valence band but with higher energy. This transition is referred to as exciton B.<sup>42,43</sup>

#### 2D MoS<sub>2</sub> thin film transistors

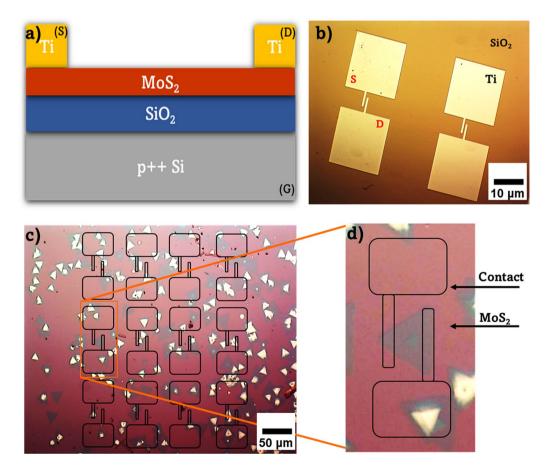

As described in the previous section, the CVD process resulted in the growth of  $MoS_2$  crystals with different number of layers randomly dispersed on the SiO<sub>2</sub>/Si substrates. The  $MoS_2$  crystals were used as semiconductor active layers in FETs with the back-gate configuration shown in Fig. 4a, where the moderately doped *p*-type Si substrate is the gate electrode, and the SiO<sub>2</sub> layer is the dielectric gate.

**Fig.4** (a) Schematic of the back-gate configuration of the  $MoS_2$ -based FET; *S* source, *D* drain, *G* gate. (b) Optical image of the source and drain Ti contacts. (c) Optical image of the shadow mask pattern on the  $MoS_2$  crystals. (d) Amplified image of a complete layer stack of the FET.

The devices were completed by the patterning of source and drain Ti contacts by the lift-off photolithography process described in the experimental section.

Figure 4b shows two pairs of the Ti contacts after the lift-off process. Since the growth of the  $MoS_2$  crystals is random on the  $SiO_2$  surface, the alignment of the source and drain contacts, defined by the mask employed for the patterning to achieve the stack configuration in Fig. 4a, necessarily requires a successful coincidence. This situation can be seen in Fig. 4c where the patterned source and drain Ti contacts can be seen deposited mostly on the  $SiO_2$  surface, or partially over the  $SiO_2$  crystals. However, in some regions, like the one shown in Fig. 4d, there is a successful coincidence of both Ti contacts on a triangular  $MoS_2$  crystal, defining a device with the stack layer in Fig. 4a. This way, we could find in different regions several complete devices with  $MoS_2$  crystals with different number of layers as the semiconductor active layer.

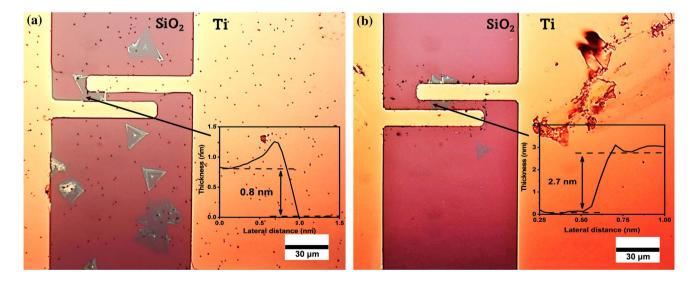

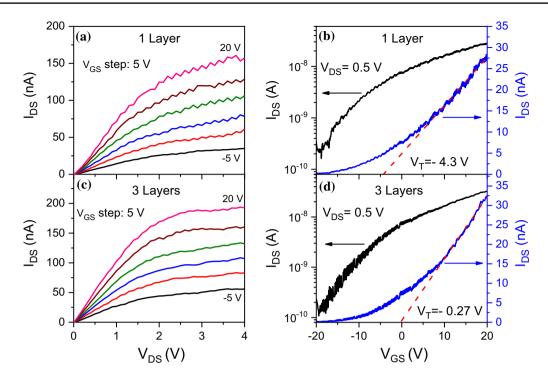

The electrical response was analyzed on two types of FETs with one and three  $MoS_2$  layers. These devices are shown in Fig. 5a and b, respectively, which include the height profiles of the  $MoS_2$  crystals corroborating the number of  $MoS_2$  layers in each case. The average thickness of the single- and three-layer  $MoS_2$  crystals, measured along the gate, were  $0.94 \pm 0.12$  nm and  $2.3 \pm 0.26$  nm, respectively. In these devices, the length of the channel, L, is 7  $\mu$ m, while, based on these images, the width, W, of the channel is 16 and 14  $\mu$ m, respectively. Figure 6a and c shows the output drain current versus drain voltage ( $I_{DS}$ - $V_{DS}$ ) curves at different source-gate voltage ( $V_{GS}$ ) values from -5 V to 20 V in steps of 5 V, for the devices with  $MoS_2$  single layer and three layers, respectively.

The output curves of both devices reveal the typical transistor response for an *n*-type semiconductor channel with drain current linear behavior at low drain voltages and saturation at higher voltages. The drain current saturation is achieved at rather low drain voltage, around 2-3 V, in both devices. The maximum values of the drain current at the different values of V<sub>GS</sub> are higher for the device with three layers of MoS<sub>2</sub>. On the other hand, the transfer drain current versus source-gate voltage  $(I_{DS}-V_{GS})$  curves measured at 0.5 V of the source-drain voltage are shown in Fig. 6b and d for the devices with MoS<sub>2</sub> single layer and three layers, respectively. As can be seen, the lowest values of the drain current in both devices are of the order of  $10^{-10}$  A which increases to values of the order of  $10^{-8}$  A with source-gate voltage. From this, both devices have an  $I_{on}/I_{off}$  current ratio of  $10^2$ . The field effect mobility in the linear region,  $\mu$ , and threshold voltage, V<sub>T</sub>, can be also determined from the transfer characteristics of the devices using:

$$\mu = \frac{L}{WC_{G}} \left( \frac{dI_{DS}}{dV_{GS}} \right) \frac{1}{V_{DS}}$$

(1)

where L and W are the length and width of the channel, respectively,  $(dI_{DS})/(dV_{GS})$  is the slope of the transfer curve of the device,  $V_{DS}$  is the applied drain voltage, and  $C_G$  is the gate capacitance, which for SiO<sub>2</sub> is ~ 115  $\mu$ F m<sup>-2</sup>. The value of  $(dI_{DS})/(dV_{GS})$  is obtained by fitting the linear region of the transfer curves, as shown in the right-axis plots of Fig. 6b and d. The drain current in these transfer curves is plotted in linear scale, unlike the left-axis drain current where the scale is logarithmic. The best linear fitting to Eq. (1) is depicted by the red dashed line in both transfer curves. In addition, the threshold voltage of the devices is determined from the

Fig. 5 Optical image of the (a) single- and (b) three-layer  $MoS_2$ -based FETs. The height profile corroborating the number of  $MoS_2$  layers in the device is included as an *inset* in each case.

Fig.6 (a) Output and (b) transfer curves of the single-layer  $MoS_2$ -based FET, and (c) output and (d) transfer curves of the three-layer  $MoS_2$ -based FET (Color figure online).

Table I Dimensions and electrical performance parameters of the  ${\rm MoS}_2$  -based FETs with single and three layers, before and after thermal annealing

|                  | L, µm | W, μm | $\mu$ , cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | $V_{\rm T}$ , V | $I_{\rm ON}/I_{\rm OFF}$ |

|------------------|-------|-------|---------------------------------------------------------|-----------------|--------------------------|

| 1 layer          | 7     | 10    | 0.13                                                    | - 4.3           | 10 <sup>2</sup>          |

| 3 layers         | 7     | 12    | 0.16                                                    | - 0.27          | $10^{2}$                 |

| 1 layer 200, °C  | 7     | 10    | 0.36                                                    | 0.53            | 10 <sup>2</sup>          |

| 3 layers 200, °C | 7     | 12    | 0.38                                                    | - 1.86          | 10 <sup>3</sup>          |

interception of this straight line with the V<sub>GS</sub> axis. The electrical performance parameters for both types of MoS<sub>2</sub>-based FETs are summarized in Table I. The mobility, 0.38 cm<sup>2</sup>/Vs, and threshold voltage, -1.86 V, of the MoS<sub>2</sub> trilayer device are slightly better values than those corresponding to the MoS<sub>2</sub> monolayer device, 0.36 cm<sup>2</sup>/Vs and 0.53 V. This difference, attributed to the number of layers of MoS<sub>2</sub>, can be due to Coulomb scattering. The higher susceptibility of the monolayer to acquire impurities from the environment, such as water or oxygen molecules, form adsorbates on its surface causing a decrease in the mobility of the device.<sup>44,45</sup> In the same way, since it is a single layer, the roughness can be another important factor in the decrease of this parameter.<sup>46</sup>

To enhance the electrical performance parameters of the  $MoS_2$ -based FETs, they were thermally annealed at 200 °C

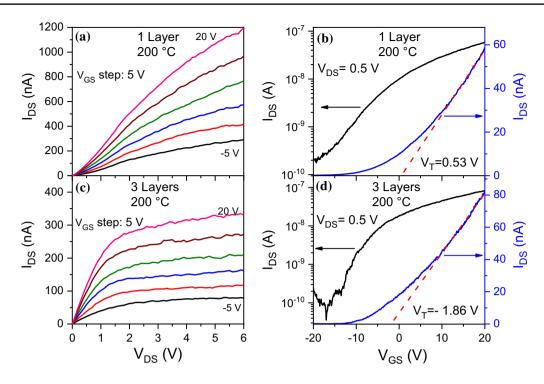

in an Ar atmosphere during 30 min. It is known that the heat treatments improve the electronic transport reducing the resistance of the metal contacts and removing contaminants such as resin residues from the manufacturing process.<sup>47</sup> Likewise, it has been reported that heat treatment induces a structural rearrangement, thus affecting the electrical properties of the MoS<sub>2</sub> semiconductor.<sup>48</sup> Thermal annealing produces the removal of defects and impurities in the MoS<sub>2</sub> crystals, leading to the reduction of charge trapping and improving the charge carrier mobility. This is particularly important in CVD-grown MoS<sub>2</sub> crystals, which may contain a higher density of defects compared to highly crystalline material.<sup>48–50</sup> Because the devices can be damaged by the high temperature,<sup>51</sup> the treatment temperature was chosen as 200 °C. The electrical response of both types of devices after the heat treatment is shown in Fig. 7, where a and c correspond to the output curves and b and d to the transfer ones. The output curves of the annealed devices show the transistor behavior with increased drain current compared to the corresponding curves before annealing. The observed increase of the drain current is higher for the single-layer device, where the current saturation shifts to higher voltage, while the current saturation in the trilayer device is much better at still a low voltage. The observed slope of the output curves in the saturation region of the single-layer device can also be a consequence of the more conductive channel after thermal annealing. The drain current increases, producing

Fig.7 (a) Output and (b) transfer curves of the single-layer  $MoS_2$ -based FET, and (c) output and (d) transfer curves of the three-layer  $MoS_2$ -based FET.

the observed slope in the curve, indicating that the polarization of the dielectric gate is not enough to modulate the drain current. The transfer curves also show the increase of the drain current in the annealed device keeping the current level of the off-state of the device. Therefore, the annealing of the devices produces an increase of their  $I_{on}/I_{off}$  current ratio, which in the case of the trilayer device is now  $10^3$ . These curves were also fitted to Eq. (1) to determine the mobility and threshold voltage of the annealed devices, and the results are summarized in Table I. These results show that the heat treatment increased by about ~ 1.25 times the mobility of the single-layer and trilayer devices. Meanwhile, the threshold voltage of the single-layer device reduced and even became positive. The negative values of the threshold voltages of *n*-type FETs indicate their depletion operation mode, where at zero gate voltage they are turned on. Therefore, the single-layer device, with very low positive threshold voltage, 0.53 V, changed to enhancement operation mode after thermal annealing, where the device is turned off at zero gate voltage. These results demonstrate the enhancement of the electrical response of the MoS<sub>2</sub>-based FETs produced by the thermal treatment at 200 °C.

The values of the mobility and  $I_{\rm on}/I_{\rm off}$  current ratio of our FETs can be fairly compared with similar CVD-MoS<sub>2</sub> monolayers and multilayer-based FETs with a SiO<sub>2</sub> dielectric gate. For these devices reported in the literature, the values of mobility and  $I_{\rm on}/I_{\rm off}$  current ratio also depend on the number of layers and are in the ranges from 0.003 cm<sup>2</sup>/Vs to 45 cm<sup>2</sup>/Vs and from 10<sup>3</sup> to 10<sup>7</sup>, respectively.<sup>37,52,53</sup> The large difference between these values is mainly due to the CVD-MoS<sub>2</sub>-based FETs fabrication processes. Better FET performance parameters are achieved when e-beam lithography is employed in their fabrication, while the photolithography process, like in our case, produces devices with lower values of mobility and  $I_{off}$  current ratio.

#### Conclusions

We have reported the electrical behavior of 2D  $MoS_2$  layers, obtained from an AMH assisted APCVD process, as the active semiconductor layer in FETs with back-SiO<sub>2</sub>-gate configuration. The detailed microscopic and spectroscopic analysis of the 2D  $MoS_2$  deposit on the SiO<sub>2</sub> surface corroborated the formation of single and multiple layers of  $MoS_2$  crystals with a triangular shape. The size of the crystals was a few microns, and the thickness of the single layer was 0.78 nm. The assembling process of the FETs was carried out by depositing a patterning of source and drain Ti contacts on the randomly dispersed  $MoS_2$  crystals, and selecting those where the layer stack configuration of the device was complete. This way, two types of 2D  $MoS_2$ -based devices with one and three layers were assembled and analyzed. These devices exhibited *n*-type electrical behavior operating in the depletion mode, where the trilayer device showed slightly higher mobility. 0.16 cm<sup>2</sup>/Vs, with very low threshold voltage, -0.27 V, than the single-layer device, 0.13 cm<sup>2</sup>/Vs and – 4.3 V, respectively. Furthermore, the 2D MoS<sub>2</sub>-based FETs were thermally annealed at 200 °C for 30 min to improve their electrical response. This thermal treatment led to a improvement in the drain current for both devices, resulting in a ~ 1.25 times increase in mobility. Specifically, the mobility values increased to 0.36 and 0.38  $\text{cm}^2$ / Vs for the single-layer and three-layer devices, respectively. An interesting observation was a change in the threshold voltage of from - 4.3 V to 0.53 V for the single-layer device after thermal annealing, indicating a transition from depletion to enhanced operation mode due to thermal annealing. Furthermore, the  $I_{on}/I_{off}$  current ratio of the three-layer device increased to  $10^3$  after thermal annealing, suggesting an improvement in the device's performance and its potential for practical applications.

Acknowledgments The technical assistance of C.A. Avila-Herrera is acknowledged.

Author contributions All authors contributed to the study conception and design. Material preparation, data collection and analysis were performed by BAMM. The first draft of the manuscript was written by BAMM and RRB. All authors commented on previous versions of the manuscript. All authors read an approved the final manuscript.

**Funding** The authors declare that no funds, grants, or other support were received during the preparation of this manuscript. The authors have no relevant financial or non-financial interests to disclose.

## Declarations

**Conflict of interest** On behalf of all authors, the corresponding author states that there is no conflict of interest.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

## References.

- K.F. Mak and J. Shan, Photonics and optoelectronics of 2D semiconductor transition metal dichalcogenides. *Nat. Photonics* 10, 216–226 (2016). https://doi.org/10.1038/nphoton.2015.282.

- X. Yin, C.S. Tang, Y. Zheng, J. Gao, J. Wu, H. Zhang, M. Chhowalla, W. Chen, and A.T.S. Wee, Recent developments in 2D transition metal dichalcogenides: phase transition and applications of

the (quasi-)metallic phases. *Chem. Soc. Rev.* 50, 10087–10115 (2021). https://doi.org/10.1039/D1CS00236H.

- H. Wang, H. Yuan, S. Sae Hong, Y. Li, and Y. Cui, Physical and chemical tuning of two-dimensional transition metal dichalcogenides. *Chem. Soc. Rev.* 44, 2664–2680 (2015). https://doi.org/10. 1039/C4CS00287C.

- S.A. Han, R. Bhatia, and S.-W. Kim, Synthesis, properties and potential applications of two-dimensional transition metal dichalcogenides. *Nano Converg.* 2, 17 (2015). https://doi.org/10.1186/ s40580-015-0048-4.

- D. Voiry, A. Mohite, and M. Chhowalla, Phase engineering of transition metal dichalcogenides. *Chem. Soc. Rev.* 44, 2702– 2712 (2015). https://doi.org/10.1039/C5CS00151J.

- S. Wang, H. Tian, C. Ren, J. Yu, and M. Sun, Electronic and optical properties of heterostructures based on transition metal dichalcogenides and graphene-like zinc oxide. *Sci. Rep.* 8, 12009 (2018). https://doi.org/10.1038/s41598-018-30614-3.

- Z. Cui, K. Ren, Y. Zhao, X. Wang, H. Shu, J. Yu, W. Tang, and M. Sun, Electronic and optical properties of van der Waals heterostructures of g-GaN and transition metal dichalcogenides. *Appl. Surf. Sci.* 492, 513–519 (2019). https://doi.org/10.1016/j. apsusc.2019.06.207.

- J. Jang, J.-K. Kim, J. Shin, J. Kim, K.-Y. Baek, J. Park, S. Park, Y.D. Kim, S.S.P. Parkin, K. Kang, K. Cho, and T. Lee, Reduced dopant-induced scattering in remote charge-transfer-doped MoS<sub>2</sub> field-effect transistors. *Sci. Adv.* 8, eabn3181 (2023). https://doi.org/10.1126/sciadv.abn3181.

- N. Divya Bharathi and K. Sivasankaran, Research progress and challenges of two dimensional MoS<sub>2</sub> field effect transistors. J. Semicond. 39, 104002 (2018). https://doi.org/10.1088/1674-4926/39/10/104002.

- S. Ghatak, A.N. Pal, and A. Ghosh, Nature of electronic states in atomically thin MoS<sub>2</sub> field-effect transistors. ACS Nano 5, 7707–7712 (2011). https://doi.org/10.1021/nn202852j.

- Z. Yu, Z.-Y. Ong, S. Li, J.-B. Xu, G. Zhang, Y.-W. Zhang, Y. Shi, and X. Wang, Analyzing the carrier mobility in transitionmetal dichalcogenide MoS<sub>2</sub> field-effect transistors. *Adv. Funct. Mater.* 27, 1604093 (2017). https://doi.org/10.1002/adfm.20160 4093.

- Y. Zhang, Y. Yao, M.G. Sendeku, L. Yin, X. Zhan, F. Wang, Z. Wang, and J. He, Recent progress in CVD growth of 2D transition metal dichalcogenides and related heterostructures. *Adv. Mater.* 31, 1901694 (2019). https://doi.org/10.1002/adma.201901694.

- V. Kranthi Kumar, S. Dhar, T.H. Choudhury, S.A. Shivashankar, and S. Raghavan, A predictive approach to CVD of crystalline layers of TMDs: the case of MoS<sub>2</sub>. *Nanoscale* 7, 7802–7810 (2015). https://doi.org/10.1039/C4NR07080A.

- J. You, M.D. Hossain, and Z. Luo, Synthesis of 2D transition metal dichalcogenides by chemical vapor deposition with controlled layer number and morphology. *Nano Converg.* 5, 26 (2018). https://doi.org/10.1186/s40580-018-0158-x.

- Y. Shi, H. Li, and L.-J. Li, Recent advances in controlled synthesis of two-dimensional transition metal dichalcogenides via vapour deposition techniques. *Chem. Soc. Rev.* 44, 2744–2756 (2015). https://doi.org/10.1039/C4CS00256C.

- H. Li, J. Wu, Z. Yin, and H. Zhang, Preparation and applications of mechanically exfoliated single-layer and multilayer MoS<sub>2</sub> and WSe<sub>2</sub> nanosheets. *Acc. Chem. Res.* 47, 1067–1075 (2014). https:// doi.org/10.1021/ar4002312.

- B. Adilbekova, Y. Lin, E. Yengel, H. Faber, G. Harrison, Y. Firdaus, A. El-Labban, D.H. Anjum, V. Tung, and T.D. Anthopoulos, Liquid phase exfoliation of MoS<sub>2</sub> and WS<sub>2</sub> in aqueous ammonia and their application in highly efficient organic solar cells. *J. Mater. Chem. C Mater.* 8, 5259–5264 (2020). https://doi.org/10. 1039/D0TC00659A.

- P.-C. Shen, Y. Lin, H. Wang, J.-H. Park, W.S. Leong, A.-Y. Lu, T. Palacios, and J. Kong, CVD technology for 2-D materials. *IEEE Trans. Electron Devices* 65, 4040–4052 (2018). https://doi.org/10. 1109/TED.2018.2866390.

- J. Lei, Y. Xie, A. Kutana, K.V. Bets, and B.I. Yakobson, Saltassisted MoS<sub>2</sub> growth: molecular mechanisms from the first principles. J. Am. Chem. Soc. 144, 7497–7503 (2022). https://doi.org/ 10.1021/jacs.2c02497.

- F.G. Aras, A. Yilmaz, H.G. Tasdelen, A. Ozden, F. Ay, N.K. Perkgoz, and A. Yeltik, A review on recent advances of chemical vapor deposition technique for monolayer transition metal dichalcogenides (MX2: Mo, W; S, Se, Te). *Mater. Sci. Semicond. Process.* 148, 106829 (2022). https://doi.org/10.1016/j. mssp.2022.106829.

- G.-H. Lee, Y.-J. Yu, X. Cui, N. Petrone, C.-H. Lee, M.S. Choi, D.-Y. Lee, C. Lee, W.J. Yoo, K. Watanabe, T. Taniguchi, C. Nuckolls, P. Kim, and J. Hone, Flexible and transparent MoS<sub>2</sub> field-effect transistors on hexagonal boron nitride-graphene heterostructures. ACS Nano 7, 7931–7936 (2013). https://doi.org/ 10.1021/nn402954e.

- N. Li, Q. Wang, C. Shen, Z. Wei, H. Yu, J. Zhao, X. Lu, G. Wang, C. He, L. Xie, J. Zhu, L. Du, R. Yang, D. Shi, and G. Zhang, Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. *Nat. Electron.* 3, 711–717 (2020). https://doi.org/10.1038/s41928-020-00475-8.

- E. Reato, P. Palacios, B. Uzlu, M. Saeed, A. Grundmann, Z. Wang, D.S. Schneider, Z. Wang, M. Heuken, H. Kalisch, A. Vescan, A. Radenovic, A. Kis, D. Neumaier, R. Negra, and M.C. Lemme, Zero-bias power-detector circuits based on MoS<sub>2</sub> field-effect transistors on wafer-scale flexible substrates. *Adv. Mater.* 34, 2108469 (2022). https://doi.org/10.1002/adma.202108469.

- M.-Y. Tsai, A. Tarasov, Z.R. Hesabi, H. Taghinejad, P.M. Campbell, C.A. Joiner, A. Adibi, and E.M. Vogel, Flexible MoS<sub>2</sub> field-effect transistors for gate-tunable piezoresistive strain sensors. *ACS Appl. Mater. Interfaces* 7, 12850–12855 (2015). https://doi.org/10.1021/acsami.5b02336.

- Y. Woo, W. Hong, S.Y. Yang, H.J. Kim, J.-H. Cha, J.E. Lee, K.J. Lee, T. Kang, and S.-Y. Choi, Large-area CVD-grown MoS<sub>2</sub> driver circuit array for flexible organic light-emitting diode display. *Adv. Electron. Mater.* 4, 1800251 (2018). https://doi.org/10. 1002/aelm.201800251.

- Y. Xie, B. Zhang, S. Wang, D. Wang, A. Wang, Z. Wang, H. Yu, H. Zhang, Y. Chen, M. Zhao, B. Huang, L. Mei, and J. Wang, Ultrabroadband MoS<sub>2</sub> photodetector with spectral response from 445 to 2717 nm. *Adv. Mater.* 29, 1605972 (2017). https://doi.org/ 10.1002/adma.201605972.

- Z. Huang, T. Zhang, J. Liu, L. Zhang, Y. Jin, J. Wang, K. Jiang, S. Fan, and Q. Li, Amorphous MoS<sub>2</sub> photodetector with ultrabroadband response. *ACS Appl. Electron. Mater.* 1, 1314–1321 (2019). https://doi.org/10.1021/acsaelm.9b00247.

- M. Choi, Y.J. Park, B.K. Sharma, S.-R. Bae, S.Y. Kim, and J.-H. Ahn, Flexible active-matrix organic light-emitting diode display enabled by MoS<sub>2</sub> thin-film transistor. *Sci. Adv.* 4, 8721 (2023). https://doi.org/10.1126/sciadv.aas8721.

- P. Xia, X. Feng, R.J. Ng, S. Wang, D. Chi, C. Li, Z. He, X. Liu, and K.-W. Ang, Impact and origin of interface states in MOS capacitor with monolayer MoS<sub>2</sub> and HfO<sub>2</sub> high-k dielectric. *Sci. Rep.* 7, 40669 (2017). https://doi.org/10.1038/srep40669.

- T. Kawanago, T. Oba, and S. Oda, Transfer printing of Al<sub>2</sub>O<sub>3</sub> gate dielectric for fabrication of top-gate MoS<sub>2</sub> FET. *Appl. Phys. Express* 12, 026501 (2019). https://doi.org/10.7567/1882-0786/ aaf995.

- Md.S. Islam, S. Sadman, A.S.M.J. Islam, and J. Park, HfO<sub>2</sub>/TiO<sub>2</sub>/ HfO<sub>2</sub> tri-layer high-K gate oxide based MoS<sub>2</sub> negative capacitance

FET with steep subtreshold swing. *AIP Adv.* 10, 035202 (2020). https://doi.org/10.1063/1.5143939.

- 32. L. Zhang, H. Xing, M. Yang, Q. Dong, H. Li, and S. Liu, Advances in atomic layer deposited high-κ inorganic materials for gate dielectrics engineering of two-dimensional MoS<sub>2</sub> field effect transistors. *Carbon Lett.* 32, 1247–1264 (2022). https://doi. org/10.1007/s42823-022-00367-1.

- T. Zou and Y.-Y. Noh, Solution-processed 2D transition metal dichalcogenides: materials to CMOS electronics. Acc. Mater. Res. 4, 548–559 (2023). https://doi.org/10.1021/accountsmr.3c00032.

- 34. S. Wang, Y. Rong, Y. Fan, M. Pacios, H. Bhaskaran, K. He, and J.H. Warner, Shape evolution of monolayer MoS<sub>2</sub> crystals grown by chemical vapor deposition. *Chem. Mater.* 26, 6371–6379 (2014). https://doi.org/10.1021/cm5025662.

- J. Jeon, S.K. Jang, S.M. Jeon, G. Yoo, Y.H. Jang, J.-H. Park, and S. Lee, Layer-controlled CVD growth of large-area two-dimensional MoS<sub>2</sub> films. *Nanoscale* 7, 1688–1695 (2015). https://doi.org/10. 1039/C4NR04532G.

- C. Lee, H. Yan, L.E. Brus, T.F. Heinz, J. Hone, and S. Ryu, Anomalous lattice vibrations of single- and few-layer MoS<sub>2</sub>. ACS Nano 4, 2695–2700 (2010). https://doi.org/10.1021/nn1003937.

- H. Schmidt, S. Wang, L. Chu, M. Toh, R. Kumar, W. Zhao, A.H. Castro Neto, J. Martin, S. Adam, B. Özyilmaz, and G. Eda, Transport properties of monolayer MoS<sub>2</sub> grown by chemical vapor deposition. *Nano Lett.* 14, 1909–1913 (2014). https://doi.org/10. 1021/nl4046922.

- A. Singh, B.P. Majee, J.D. Gupta, and A.K. Mishra, Layer dependence of thermally induced quantum confinement and higher order phonon scattering for thermal transport in CVD-grown triangular MoS<sub>2</sub>. J. Phys. Chem. C 127, 3787–3799 (2023). https://doi.org/10.1021/acs.jpcc.2c08389.

- Z. Li, G. Ezhilarasu, I. Chatzakis, R. Dhall, C.-C. Chen, and S.B. Cronin, Indirect band gap emission by hot electron injection in metal/MoS<sub>2</sub> and metal/WSe<sub>2</sub> heterojunctions. *Nano Lett.* 15, 3977–3982 (2015). https://doi.org/10.1021/acs.nanolett.5b00885.

- H. Li, X. Zhu, Z.K. Tang, and X.H. Zhang, Low-temperature photoluminescence emission of monolayer MoS<sub>2</sub> on diverse substrates grown by CVD. J. Lumin. 199, 210–215 (2018). https:// doi.org/10.1016/j.jlumin.2018.03.052.

- J. Pak, Y. Jang, J. Byun, K. Cho, T.-Y. Kim, J.-K. Kim, B.Y. Choi, J. Shin, Y. Hong, S. Chung, and T. Lee, Two-dimensional thickness-dependent avalanche breakdown phenomena in MoS<sub>2</sub> field-effect transistors under high electric fields. *ACS Nano* 12, 7109–7116 (2018). https://doi.org/10.1021/acsnano.8b02925.

- V. Senthilkumar, L.C. Tam, Y.S. Kim, Y. Sim, M.-J. Seong, and J.I. Jang, Direct vapor phase growth process and robust photoluminescence properties of large area MoS<sub>2</sub> layers. *Nano Res.* 7, 1759–1768 (2014). https://doi.org/10.1007/s12274-014-0535-7.

- C. Ataca, H. Şahin, and S. Ciraci, Stable, single-layer MX<sub>2</sub> transition-metal oxides and dichalcogenides in a honeycomb-like structure. *J. Phys. Chem. C* 116, 8983–8999 (2012). https://doi.org/10.1021/jp212558p.

- J. Park, H. Woo, and S. Jeon, Impact of fast transient charging and ambient on mobility of WS<sub>2</sub> field-effect transistor. *J. Vac. Sci. Technol.*, B 35, 050601 (2017). https://doi.org/10.1116/1.4989781.

- K. Kaasbjerg, K.S. Thygesen, and K.W. Jacobsen, Phonon-limited mobility in *n*-type single-layer MoS<sub>2</sub> from first principles. *Phys. Rev. B* 85, 115317 (2012). https://doi.org/10.1103/PhysRevB.85. 115317.

- 46. Q. Yang, J. Fang, G. Zhang, and Q. Wang, Effect of substrate and temperature on the electronic properties of monolayer molybdenum disulfide field-effect transistors. *Phys Lett A*. 382, 697–703 (2018). https://doi.org/10.1016/j.physleta.2017.12.052.

- 47. P. Zhao, A. Azcatl, P. Bolshakov, J. Moon, C.L. Hinkle, P.K. Hurley, R.M. Wallace, and C.D. Young, Effects of annealing on

top-gated MoS<sub>2</sub> transistors with HfO<sub>2</sub> dielectric. *J. Vac. Sci. Technol.*, *B* 35, 01A118 (2017). https://doi.org/10.1116/1.4974220.

- S.D. Namgung, S. Yang, K. Park, A.-J. Cho, H. Kim, and J.-Y. Kwon, Influence of post-annealing on the off current of MoS<sub>2</sub> field-effect transistors. *Nanoscale Res. Lett.* 10, 62 (2015). https:// doi.org/10.1186/s11671-015-0773-y.

- Ansh, J. Kumar, G. Sheoran, and M. Shrivastava, Electrothermal transport induced material reconfiguration and performance degradation of CVD-grown monolayer MoS<sub>2</sub> transistors. *Mater. Appl.* 4, 37 (2020). https://doi.org/10.1038/s41699-020-00171-3.

- M.H. Johari, M.S. Sirat, M.A. Mohamed, Y. Wakayama, and A.R. Mohmad, Effects of post-annealing on MoS<sub>2</sub> thin films synthesized by multi-step chemical vapor deposition. *Nanomater. Nanotechnol.* 11, 1847980420981537 (2021). https://doi.org/10.1177/ 1847980420981537.

- 51. F. Wang, P. Stepanov, M. Gray, and C. Ning Lau, Annealing and transport studies of suspended molybdenum disulfide devices.

Nanotechnology 26, 105709 (2015). https://doi.org/10.1088/0957-4484/26/10/105709.

- 52. Y.-H. Lee, L. Yu, H. Wang, W. Fang, X. Ling, Y. Shi, C.-T. Lin, J.-K. Huang, M.-T. Chang, C.-S. Chang, M. Dresselhaus, T. Palacios, L.-J. Li, and J. Kong, Synthesis and transfer of single-layer transition metal disulfides on diverse surfaces. *Nano Lett.* 13, 1852–1857 (2013). https://doi.org/10.1021/nl400687n.

- Y. Yu, C. Li, Y. Liu, L. Su, Y. Zhang, and L. Cao, controlled scalable synthesis of uniform, high-quality monolayer and few-layer MoS<sub>2</sub> films. *Sci. Rep.* 3, 1866 (2013). https://doi.org/10.1038/ srep01866.

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.