# Multiobjective Optimization of Design of 4H-SiC Power MOSFETs for Specific Applications

H. BENCHERIF,<sup>1,2</sup> L. DEHIMI,<sup>1</sup> F. PEZZIMENTI ,<sup>3,4</sup> G. DE MARTINO,<sup>3</sup> and F.G. DELLA CORTE<sup>3</sup>

1.—Laboratory of Metallic and Semiconductor Materials, University of Biskra, Biskra, Algeria. 2.—LAAAS, Department of Electronics, University Mostefa Benboulaid, Batna 2, Algeria. 3.—DIIES, Mediterranea University of Reggio Calabria, Reggio Calabria, Italy. 4.—e-mail: fortunato.pezzimenti@unirc.it

The electrical characteristics of a 4H silicon carbide (4H-SiC) metal–oxidesemiconductor field-effect transistor (MOSFET) have been investigated by using a multiobjective genetic algorithm (MOGA) to overcome the existing tradeoff between main device figures of merit such as the breakdown voltage, drain current, and ON-state resistance. The aim of this work is to achieve an optimized device for a specific application. In particular, without loss of generality, we refer to a dual-implanted MOSFET (DMOSFET) dimensioned for use as a low-power transistor in direct current (DC)–DC converters for solar power optimizers. Typical blocking voltages for these transistors are around 150 V. In this investigation, both analytical and numerical models are used as objective functions in MOGA to determine a set of optimized physical and geometrical device parameters that meet the application constraints while minimizing the ON-state resistance ( $R_{ON}$ ). The optimized DMOSFET exhibits an  $R_{ON}$  value of a few hundred k $\Omega \times \mu m^2$  for different breakdown voltages in the range from 150 V to 800 V.

**Key words:** 4H-SiC MOSFET, power device, design optimization, ON-state resistance, blocking voltage

# **INTRODUCTION**

During the last decade, use of 4H silicon carbide (4H-SiC)-based metal-oxide-semiconductor field-effect transistors (MOSFETs) for high-power, high-temperature, and switching applications has been widely proposed.<sup>1-5</sup> Thanks to its outstanding physical and electronic properties (i.e., mechanical strength, thermal conductivity, and critical electric field),<sup>6,7</sup> silicon carbide has been recognized worldwide as a promising material to improve device performance in terms of ON-state resistance, breakdown voltage, and switching capabilities. In particular, SiC MOSFETs are widely used as power devices in onboard DC-DC converters for use in specific modules; For example, in Ref. 8, a boost-

based converter was proposed, describing the design of a zero-voltage zero-current switch (ZVZCS) suitable for high duty cycle and wide load currents; in Ref. 9, dual-SiC MOSFET modules were designed for use in the electric traction context; in Ref. 10, a dual active bridge (DAB) converter was implemented using 10-kV SiC MOSFETs; in Ref. 11 a high-frequency, 1-kW, 800 V output voltage boost DC-DC converter was developed.

To meet the specific constraints related to modern power electronics, the design of 4H-SiC MOSFETs requires deployment of intensive modeling effort based in turn on numerical, analytical, and empirical calculations, carefully taking into account the different geometrical and physical parameters that affect device performance.<sup>12-15</sup>

Although several studies have dealt with the tradeoff between the electrical characteristics of a MOSFET in 4H-SiC,<sup>15–18</sup> to the best of the authors' knowledge, no investigations on global performance

<sup>(</sup>Received April 17, 2018; accepted March 14, 2019; published online March 25, 2019)

optimization based on evolutionary algorithms have been carried out. Such tools are very useful for optimization problems where various objective functions must be treated simultaneously, offering low complexity and reasonable computational time.

To achieve this aim, in the work presented herein, we investigated optimized design of a 4H-SiC dualimplanted MOSFET (DMOSFET) well suited for a specific application by means of a multiobjective genetic algorithm (MOGA).<sup>19</sup> In more detail, starting from combined analytical and numerical analysis of the device current-voltage  $(I_{\rm D}-V_{\rm DS})$ characteristic, both analytical and numerical models are used as objective functions in MOGA to determine fundamental design parameters that minimize the ON-state resistance of a device dimensioned for a blocking voltage  $(BV_{DS})$  in the range from 150 V to 800 V. Although typical 4H-SiC MOSFETs are designed to support high breakdown voltages ranging from 600 V to 1700 V,<sup>20-22</sup> recent papers have also investigated low-power transistors (in the 100 V to 200 V class) to be used, for example, for photovoltaic module-level applications, enabling operation in harsh conditions with considerable lifetime.  $^{23-28}$  In fact, smart maximum-power-point tracking converters for photovoltaics should be characterized by  $BV_{DS}$  values close to 150 V or less and  $R_{\rm ON}$  in the limit of a few hundred k $\Omega \times \mu m^2$ . In particular, in Ref. 23, the authors underlined the need to overcome the existing tradeoff between  $BV_{DS}$ ,  $I_D$ , and  $R_{ON}$  to design low-voltage 4H-SiC MOSFETs with optimized performance. As mentioned above, without loss of generality, we adopt a genetic algorithm framework to search for the commonly called Pareto-optimal (i.e., nondominated) solution for several physical and geometrical device parameters. The results obtained in terms of  $R_{\rm ON}$  are compared with those reported in Ref. 23.

# **DMOSFET STRUCTURE**

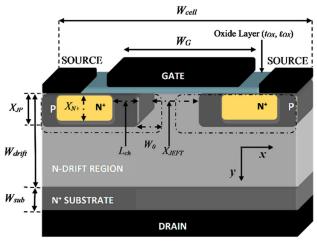

A schematic cross-sectional view of the single-cell n-channel 4H-SiC DMOSFET considered herein is shown in Fig. 1, along with the notation adopted to describe the geometry of the different device regions. In particular,  $W_{cell}$  is the cell width,  $L_{ch}$  is the device channel length,  $X_{JFET}$  is the distance between the base regions,  $W_{drift}$  is the thickness of the n-drift region, and  $X_{JP}$  and  $X_{N+}$  are the p-base and n-source depths, respectively.

The source contact shorts the source and the base regions to prevent the switch-on of the parasitic substrate  $(n^+)$ -epilayer (n)-base (p)-source  $(n^+)$  bipolar junction transistor. Finally, a silicon oxide layer is used to insulate the actual MOS structure.

#### **COMPUTATION METHODOLOGY**

Detailed analytical and numerical models are first used to investigate the current-voltage behavior of the DMOSFET. These models are then assumed as objective functions in MOGA to

Fig. 1. Cross-sectional view of single-cell *n*-channel 4H-SiC DMOSFET (drawing not to scale).

determine the optimized physical and geometrical device parameters for a specific application. The fundamental simulation models are briefly recalled in the following subsections.

#### **Analytical Models**

#### Breakdown Voltage

The breakdown or blocking voltage (BV<sub>DS</sub>) characteristics of a DMOSFET can be calculated when the device is in a firm OFF-state, i.e.,  $V_{\rm G} = 0$  V with grounded source. The BV<sub>DS</sub> value is related to the onset of breakdown within the base-drain *p*-i-*n* structure as the bias voltage  $V_{\rm DS}$  is increased. Assuming that the drift region is in a punchthrough condition, namely totally depleted before breakdown occurs, a first estimate of BV<sub>DS</sub> is given by<sup>7</sup>

$$\mathrm{BV}_{\mathrm{DS}} = E_{pn}^{\mathrm{crit}} W_{\mathrm{drift}} - rac{q N_{\mathrm{drift}} W_{\mathrm{drift}}^2}{2 arepsilon_{\mathrm{sc}}},$$

(1)

where  $E_{pn}^{\rm crit}$  is the critical electric field that appears somewhere along the border of the *p*-base/*n*-drift junction,  $\varepsilon_{\rm sc}$  is the material permittivity, and  $N_{\rm drift}$  is the doping concentration in the drift region. This expression is valid for  $W_{\rm drift} \leq \varepsilon_{\rm sc} E_{pn}^{\rm crit} q^{-1} N_{\rm drift}^{-1}$ ; For example, considering typical values for the permittivity of 4H-SiC and a critical electric field of 2 MV/ cm, the width of the *n*-type drift region must be in the limit of 10  $\mu$ m for  $N_{\rm drift} = 1 \times 10^{16}$  cm<sup>-3.7</sup> This result was also calculated in Refs. 29,30 for similar *p*-i-*n* structures. The dependence of the electric field on  $N_{\rm drift}$  is in the form<sup>31</sup>

$$E_{pn} = 2.49 \times 10^6 (5 - 0.25 \log N_{\rm drift}).$$

(2)

#### **ON-State** Resistance

The total ON-state resistance in the device current path is the sum of different terms as follows:

$$R_{\rm ON} = R_{\rm N+} + R_{\rm ch} + R_{\rm acc} + R_{\rm JFET} + R_{\rm drift} + R_{\rm sub}, ~(3)$$

where  $R_{\rm N+}$  is the source resistance,  $R_{\rm ch}$  is the channel region resistance,  $R_{\rm acc}$  is the accumulation region resistance relative to the distance  $X_{\rm JFET}$  next to the channel (Fig. 1),  $R_{\rm JFET}$  refers to the JFET channel portion,  $R_{\rm drift}$  is the resistance of the drift region, and  $R_{\rm sub}$  is the substrate contribution. In accordance with Fig. 1, appropriate expressions for these terms can be written as<sup>7</sup>

$$R_{\rm ch} = \frac{L_{\rm ch} W_{\rm cell}}{2\mu_{\rm ch} C_{\rm OX} (V_{\rm GS} - V_{\rm TH})}, \qquad (4)$$

$$R_{\rm acc} = \frac{X_{\rm JFET} W_{\rm cell}}{4\mu_{\rm acc} C_{\rm OX} (V_{\rm GS} - V_{\rm TH})}, \qquad (5)$$

$$R_{\rm JFET} = \frac{\rho_{\rm JFET} X_{\rm JP} W_{\rm cell}}{W_{\rm G} - 2X_{\rm JP} - 2W_0},\tag{6}$$

$$R_{\rm drift} = \frac{\rho_{\rm drift} W_{\rm drift} W_{\rm cell}}{W_{\rm cell} - W_{\rm G} + 2X_{\rm JP} + 2W_0} \ln\left(\frac{W_{\rm cell}}{W_{\rm G} - 2X_{\rm JP} - 2W_0}\right).$$

(7)

Here, in particular,  $R_{\rm acc}$  is the gate oxide capacitance,  $\mu_{\rm ch}$  and  $\mu_{\rm acc}$  are the doping-dependent carrier mobility in the inversion and accumulation layer, respectively,  $\rho_{\rm JFET}$  is the resistivity of the JFET region, and  $W_0$  is the zero-bias depletion width in the JFET region computed as

$$W_0 = \sqrt{\frac{2\varepsilon_{\rm SC}N_{\rm A}V_{\rm bi}}{qN_{\rm JFET}(N_{\rm A} + N_{\rm JFET})}},\tag{8}$$

where  $N_{\rm A}$  and  $N_{\rm JFET}$  are the doping concentration in the *p*-base and JFET region, respectively, and  $V_{\rm bi}$  is the built-in potential in the form

$$V_{\rm bi} = \frac{kT}{q} \ln\left(\frac{N_{\rm A}N_{\rm JFET}}{n_{\rm i}^2}\right). \tag{9}$$

Note that, for the sake of simplicity, the resistance contributions  $R_{\rm N+}$  and  $R_{\rm sub}$  are considered to be negligible in these calculations, because they are relative to heavily doped regions.

#### Threshold Voltage and Drain Current

The MOSFET threshold voltage  $(V_{\rm TH})$  is defined as the gate bias voltage that ensures the strong inversion regime in the channel region. Its value depends on the doping concentration in the *p*-base and increases linearly with the gate oxide thickness. A typical expression for  $V_{\rm TH}$  is<sup>7</sup>

$$V_{\rm TH} = \frac{t_{\rm OX}}{\varepsilon_{\rm OX}} \sqrt{4\varepsilon_{\rm SC} k T N_{\rm A} \ln\left(\frac{N_{\rm A}}{n_{\rm i}}\right) + \frac{2kT}{q} \ln\left(\frac{N_{\rm A}}{n_{\rm i}}\right)}.$$

(10)

By neglecting the subthreshold current (i.e.,  $I_{\rm D} = 0$  for  $V_{\rm GS} < V_{\rm TH}$ ) and assuming a MOSFET operating point in the triode region (i.e.,  $V_{\rm DS} \leq V_{\rm GS} - V_{\rm TH}$ ), the drain current can be calculated as<sup>10</sup>

$$I_{\rm D} = \mu_{ni} C_{\rm OX} \frac{W_{\rm cell}}{L_{\rm ch}} \Big[ 2(V_{\rm GS} - V_{\rm TH}) (V_{\rm DS} - I_{\rm D} R_{\rm ON}) - (V_{\rm DS} - I_{\rm D} R_{\rm ON})^2 \Big],$$

(11)

where the term  $V_{\rm DS} - I_{\rm D}R_{\rm ON}$  is the drain internal voltage, differing from the terminal voltage by the ohmic contribution.

Finally, for  $V_{\rm DS} > V_{\rm GS} - V_{\rm TH}$ , we use

$$I_{\rm D} = \mu_{\rm ni} C_{\rm OX} \frac{W_{\rm cell}}{2L_{\rm ch}} (V_{\rm GS} - V_{\rm TH})^2 [1 + \lambda (V_{\rm DS} - I_{\rm D} R_{\rm ON})],$$

(12)

where  $\lambda$  is an appropriate channel modulation coefficient.

#### **Numerical Framework**

Numerical simulations of the DMOSFET were performed by using a commercial two-dimensional (2D) technology computer-aided design (TCAD) physical simulator that provides the solution of Poisson's equation and carrier continuity equations.<sup>32</sup> The physical models and reference parameters included at T = 300 K are summarized in Table I.

They include Shockley–Read–Hall recombination  $(R_{\text{SRH}})$ ,<sup>33</sup> Auger recombination  $(R_{\text{Auger}})$ ,<sup>34</sup> incomplete ionization of impurities  $(N_{A,D}^{-+})$ ,<sup>35–37</sup> apparent bandgap narrowing  $(\Delta E_{gp,n})$ ,<sup>38</sup> doping-dependent carrier lifetime  $(\tau_{n,p})$ ,<sup>39,40</sup> impact ionization rate  $(\alpha_{n,p})$ ,<sup>41</sup> and low- and high-field carrier mobility  $(\mu_{n,p})$ .<sup>42–44</sup> The simulation setup assumed in this work has

The simulation setup assumed in this work has been used in other recent works of ours,  $^{45-48}$  where it is also supported by comparison with experimental results obtained on both  $p^+$ -i-n and Schottky structures over wide ranges of current and temperature.  $^{49-52}$

### SIMULATION ANALYSIS

In this section, we develop the background for the MOGA optimization. In particular, the impact of the fundamental design parameters on the main figures of merit of the DMOSFET is investigated by using the reference values listed in Table II as initial entry data for modeling.

## **Blocking Voltage Characteristics**

The device  $BV_{DS}$  value is strictly dependent on the *n*-drift thickness, which determines the distance between the base junction and substrate, namely the difference  $W_{drift} - X_{JP}$  in Fig. 1.

In the numerical analysis,  $BV_{DS}$  is calculated by considering the device in the OFF-state and gradually raising  $V_{DS}$  until the electric field reaches the

# Table I. Physical models and reference parameters

| $R_{\mathrm{SRH}} = rac{pn-n_{\mathrm{i}}^2}{	au_p \left(n+n_{\mathrm{i}}\exp\left(rac{\mathcal{E}_{\mathrm{trap}}}{kT} ight) ight) + 	au_n \left(p+n_{\mathrm{i}}\exp\left(-rac{\mathcal{E}_{\mathrm{trap}}}{kT} ight) ight)}$                                                                                  | $n_i = 6.7 \times 10^{-11} \text{ cm}^{-3}$<br>$C_{An} = 5 \times 10^{-31} \text{ cm}^6/\text{s}$<br>$C_{Ap} = 2 \times 10^{-31} \text{ cm}^6/\text{s}$                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $egin{aligned} R_{	ext{Auger}} &= (C_{	ext{Ap}}p + C_{	ext{An}}n)(np - n_{	ext{i}}^2) \ && & & & & & & & & & & & & & & & & &$                                                                                                                                                                                       | $	au_{0n} = 500 \text{ ns}$<br>$	au_{0p} = 100 \text{ ns}$<br>$N_{n,p}^{\text{SRH}} = 1 \times 10^{30} \text{ cm}^{-3}$                                                                                                                                                                    |

| $\tau_{n,p} = \frac{\tau_{n,p}}{1 + \left(\frac{N}{N_{n,p}^{\text{SRH}}}\right)} \left( -\frac{1 + 4 \sqrt{1 + 4 \sigma_{n-1} - \frac{N_{\text{A,D}}}{kT}}}{1 + 4 \sigma_{n-1} - \frac{N_{\text{A,D}}}{kT}} \right)$                                                                                                | $N_{ m C}^{n,p}$ = 3.29 × 10 <sup>19</sup> cm <sup>-3</sup><br>$N_{ m C}$ = 1.66 × 10 <sup>19</sup> cm <sup>-3</sup><br>$g_{ m v}$ = 4, $g_{ m c}$ = 2<br>$\Delta E_{ m A}$ = 190 meV                                                                                                      |

| $N_{\rm A}^{-}, { m }_{ m D}^{+} = N_{ m A,D} \left( rac{-1 + \sqrt{1 + 4 g_{ m v,c} rac{N_{ m A,D}}{N_{ m V,C}(T)} e^{rac{\Delta E_{ m A,D}}{kT}}}}{2 g_{ m v,c} rac{N_{ m A,D}}{N_{ m V,C}(T)} e^{rac{\Delta E_{ m A,D}}{kT}}}}  ight)$                                                                      | $\Delta E_{ m D}$ = 70 meV<br>$a_{0n}$ = 2.5 × 10 <sup>5</sup> cm <sup>-1</sup><br>$a_{0n}$ = 3.25 × 10 <sup>6</sup> cm <sup>-1</sup>                                                                                                                                                      |

| $egin{aligned} lpha_{n,p} &= a_{0n,p} \exp igg( - rac{b_{0n,p}}{E} igg) \ \Delta E_{	ext{gp},n} &= A_{p,n} igg( rac{N^{-++}_{A 	o D}}{10^{18}} igg)^{rac{1}{2}} + B_{p,n} igg( rac{N^{-++}_{A 	o D}}{10^{18}} igg)^{rac{1}{3}} + C_{p,n} igg( rac{N^{-++}_{A 	o D}}{10^{18}} igg)^{rac{1}{4}} \end{aligned}$ | $b_{0n}^{0,p} = 1.84 \times 10^7 \text{ V/cm}$<br>$b_{0p} = 1.71 \times 10^7 \text{ V/cm}$<br>$A_p = 1.54 \times 10^{-3}$<br>$B_p = 1.3 \times 10^{-2}$                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                     | $C_p^{ P} = 1.57 	imes 10^{-2} \ A_n = 1.17 	imes 10^{-2} \ B_n = 1.5 	imes 10^{-2} \ C_n = 1.9 	imes 10^{-2}$                                                                                                                                                                             |

| $\mu_{n,p}=\mu_{0n,p}^{\min}+rac{\mu_{0n,p}^{\max}-\mu_{n,p}^{\min}}{1+\left(rac{N}{N_{n,p}^{\mathrm{errit}}} ight)^{\delta_{n,p}}},$                                                                                                                                                                             | $\mu_{0p}^{\min} = 40 \text{ cm}^2/\text{V s}$ $\mu_{0p}^{\min} = 15.9 \text{ cm}^2/\text{V s}$ $\mu_{0n}^{\max} = 950 \text{ cm}^2/\text{V s}$ $\mu_{0p}^{\max} = 125 \text{ cm}^2/\text{V s}$ $N_{cn}^{\text{cnt}} = 2 \times 10^{17} \text{ cm}^{-3}$                                   |

| $\mu_{n,p}(E) = rac{\mu_{n,p}}{\left[1 + \left(E^{u_{n,p}}_{v_{	ext{sat}}} ight)^{\kappa_{n,p}} ight]^{rac{1}{k_{n,p}}}}$                                                                                                                                                                                         | $\mu_{0p}^{\text{mm}} = 125 \text{ cm}^{-7}/\text{V s}$ $N_{cnt}^{\text{ent}} = 2 \times 10^{17} \text{ cm}^{-3}$ $N_{p}^{\text{ent}} = 1.76 \times 10^{19} \text{ cm}^{-3}$ $\delta_{n} = 0.76, \delta_{p} = 0.34$ $k_{n} = 2, k_{p} = 1$ $v_{\text{sat}} = 2 \times 10^{7} \text{ cm/s}$ |

#### Table II. DMOSFET reference parameters (Fig. 1)

| Silicon oxide thickness, $t_{ox}$ ( $\mu$ m)                   | 0.08                |

|----------------------------------------------------------------|---------------------|

| Source thickness, $X_{N+}$ ( $\mu$ m)                          | 0.5                 |

| Channel length, $L_{ch}$ ( $\mu$ m)                            | 1                   |

| Base junction depth, $X_{JP}(\mu m)$                           | 1.5                 |

| Base-to-base distance, $X_{\text{JFET}}$ ( $\mu$ m)            | 7                   |

| Epilayer thickness, $W_{\text{drift}}(\mu m)$                  | 10                  |

| Substrate thickness, $W_{sub}$ ( $\mu m$ )                     | 100                 |

| Gate width, $W_{\rm G}$ ( $\mu$ m)                             | 9.4                 |

| Cell width, $W_{\text{cell}}(\mu \text{m})$                    | 15                  |

| Device footprint area $(\mu m^2)$                              | 15                  |

| $n^+$ -Source doping, $N_{\rm D}~({\rm cm}^{-3})$              | $1	imes 10^{18}$    |

| <i>p</i> -Base doping, $N_{\rm A}$ (cm <sup>-3</sup> )         | $1.5 	imes 10^{17}$ |

| <i>n</i> -Drift doping, $N_{\text{drift}}$ (cm <sup>-3</sup> ) | $1	imes 10^{16}$    |

| $n^+$ -Substrate doping, $N_{ m sub} \ ( m cm^{-3})$           | $1	imes 10^{19}$    |

threshold of 1.9 MV/cm. The increase of  $V_{\rm DS}$ , in fact, is responsible for the expansion of the depletion region to the low-doped side of the p-base/n-drift junction, and the more the depletion region expands, the greater the increase in the electric field. The drain leakage current density,  $J_{\rm D}$ , was kept below 10 mA/cm<sup>2</sup>.

Table III. DMOSFET breakdown voltage versus ndrift thickness assuming an electric field threshold of 1.9 MV/cm and  $N_{drift} = 1 \times 10^{16} \text{ cm}^{-3}$

| $W_{\rm drift}$ ( $\mu m$ ) | BV <sub>DS</sub> (V) |  |

|-----------------------------|----------------------|--|

| 10                          | 900                  |  |

| 8                           | 800                  |  |

| 6                           | 700                  |  |

| 4                           | 500                  |  |

| 3 2                         | 350                  |  |

| 2                           | 200                  |  |

| 1.8                         | 150                  |  |

For the device described in Table II, we calculate a  $BV_{DS}$  of about 900 V. Then,  $W_{drift}$  is reduced to 1.8  $\mu$ m to meet the constraint of a BV<sub>DS</sub> close to 150 V. Different values of  $BV_{\rm DS}$  as a function of  $W_{\rm drift}$  are summarized in Table III.

The influence of the n-drift doping concentration on BV<sub>DS</sub> is also evaluated. In particular, on decreasing the doping concentration  $N_{\rm drift}$  from  $1 \times 10^{16} {\rm ~cm^{-3}}$  to  $1 \times 10^{15} {\rm ~cm^{-3}}$ , a decrease in the critical electric field with a maximum reduction of

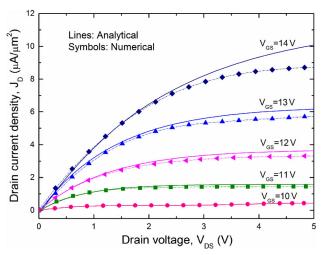

Fig. 2. DMOSFET forward  $J_{\rm D}-V_{\rm DS}$  characteristics at T = 300 K for  $W_{\rm drift} = 1.8~\mu{\rm m}$  and  $N_{\rm drift} = 3 \times 10^{15}~{\rm cm}^{-3}$  with other geometrical and electrical parameters as listed in Table II.

$BV_{DS}$  on the order of 10% is calculated for the same drain leakage current level assumed previously; For example, for the device in Table II, the simulation gives  $BV_{DS} = 850$  V for  $N_{drift} = 3 \times 10^{15}$  cm<sup>-3</sup>, as in Ref. 23. However,  $N_{drift}$  has only a limited effect on the device  $BV_{DS}$  characteristic considering the thinner  $W_{drift}$  (i.e.,  $W_{drift} \leq 3 \mu m$  in Table III).<sup>7</sup>

# **ON-State Characteristics and Temperature** Effect

The  $I_{\rm D}-V_{\rm DS}$  curves of a DMOSFET with  $W_{\rm drift} = 1.8 \ \mu m$  and  $N_{\rm drift} = 3 \times 10^{15} \ {\rm cm}^{-3}$  are shown in Fig. 2 for  $V_{\rm GS}$  from 10 V to 14 V. These simulation results indicate that the device is truly in ON-state for  $V_{\rm GS} > 8$  V at room temperature.

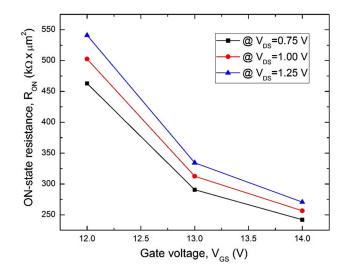

The numerical simulations and analytical results are in good agreement, especially when assuming the device operates in the deep triode region ( $V_{\rm DS} \leq 2$  V). For  $V_{\rm DS} = 1$  V and  $V_{\rm GS} = 14$  V, the drain current is close to 3.9  $\mu$ A/ $\mu$ m<sup>2</sup>, corresponding to an ON-state resistance  $R_{\rm ON}$  of about 255 k $\Omega \times \mu$ m<sup>2</sup>. From Fig. 2, the  $R_{\rm ON}$  values calculated for different  $V_{\rm DS}$  as a function of  $V_{\rm GS}$  are plotted in Fig. 3.

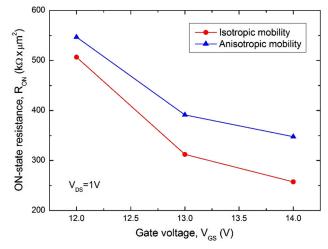

It is worth noting that, although for comparison purposes with the results reported in Ref. 23 isotropic mobility behavior was assumed by default, during the simulations the impact of an anisotropic model in determining the device  $R_{\rm ON}$  was also evaluated. In particular, the anisotropic mobility model was defined using different parameter values along the x- and y-direction in Fig. 1, which we can suppose applies to the <1100> and <0001> planes<sup>32</sup> within the 4H-SiC structure, respectively. In other words, the MOS channel lies in the highmobility <1100> plane, whilst the perpendicular <0001> plane is characterized by a longer resistive path along which the drain current flows. Assuming the parameters in Table I for the Caughey–Thomas

Fig. 3.  $R_{ON}$  as function of  $V_{GS}$  for different  $V_{DS}$  at T = 300 K.

Fig. 4.  $R_{ON}$  as function of  $V_{GS}$  for different mobility behaviors at T = 300 K.

mobility model, with a perpendicular to parallel ratio of 0.83 as suggested in Ref. 53, the variation of  $R_{\rm ON}$  for different mobility behaviors is shown in Fig. 4.

By accounting for the current degradation in the <0001> plane due to the thickness and doping concentration of the drift region, the anisotropic mobility gives higher values of  $R_{\rm ON}$  while the isotropic model underestimates  $R_{\rm ON}$  by the order of 25% on average in the considered voltage range.

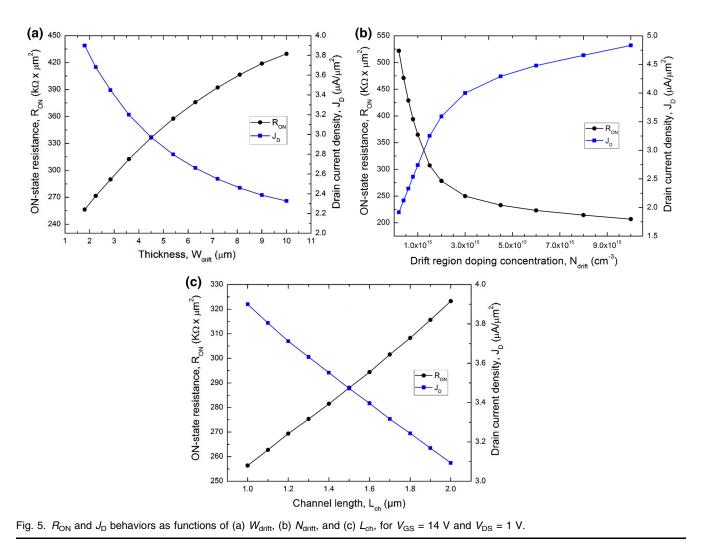

The drift region thickness  $W_{\text{drift}}$  and doping concentration  $N_{\text{drift}}$ , as well as the channel length  $L_{\text{ch}}$ , are critical parameters affecting  $R_{\text{ON}}$ , as shown in Fig. 5 for  $V_{\text{GS}} = 14$  V and  $V_{\text{DS}} = 1$  V.

From Fig. 5a, b, the drain current increases with decreasing  $W_{\rm drift}$  and increasing  $N_{\rm drift}$  as a result of the decreasing  $R_{\rm ON}$  due to a reduction of its  $R_{\rm drift}$  component. On the other hand, from Fig. 5c, increasing the channel length tends to increase

$R_{\rm ON}$  via the  $R_{\rm ch}$  component in a rather linear manner.

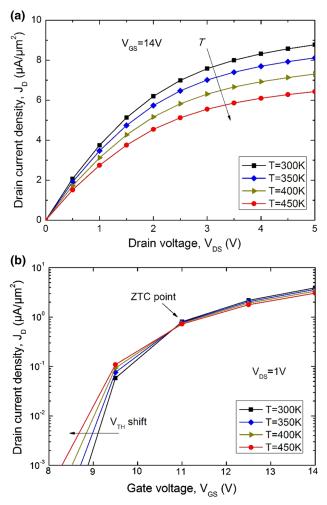

The effect of temperature on the device current capabilities is shown in Fig. 6a, b.

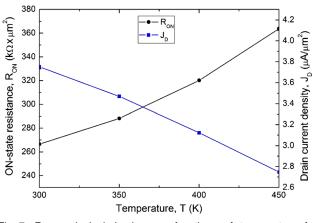

As expected,  $J_{\rm D}$  decreases with increasing temperature in Fig. 6a. This effect is due to the temperature dependence of the carrier mobility and the overall increase of  $R_{\rm ON}$ , as shown in Fig. 7. In particular, the increased temperature limits the current components which originate in the inversion layer and drift region.<sup>7</sup> At the same time, linked to the increase of the intrinsic carrier concentration in 4H-SiC, Fig. 6b shows that the threshold voltage of the DMOSFET tends to decrease, leading to a zero temperature coefficient (ZTC) point close to  $V_{\rm GS} = 11$  V.

Finally, for fixed base depth and distance between the base regions, we simulate the  $R_{\rm ON}$  behavior for different doping concentrations in the JFET region under the gate oxide ( $N_{\rm JFET}$ ). In the adopted  $N_{\rm JFET}$ doping range (3 × 10<sup>15</sup> cm<sup>-3</sup> to 3 × 10<sup>16</sup> cm<sup>-3</sup>), the results show that this parameter has only limited impact on  $R_{\rm ON}$  at different temperatures, making the device ON-state current capability only weakly dependent on the majority carrier concentration in the JFET region where the inversion layer is formed.

#### THEORETICAL BASIS FOR MOGA

In recent years, MOGA-based techniques have gained great popularity in the scientific community in many research areas, focused on the optimal solution of multidimensional and nonlinear problems.<sup>54–57</sup> Distinctive characteristics of the MOGA approach are its universality and simple implementation. It is well known that the majority of optimization procedures provide a single solution. In contrast, MOGA-based techniques permit the identification of a set of optimized solutions, commonly called a "Pareto front," which allows the selection of an appropriate combination of results according to the application field.

The background in this scenario is to establish many proper arguments, namely a set of objective functions, different constraints, and design parameters. Then, the multiobjective optimization

Fig. 6. (a)  $J_{\rm D}-V_{\rm DS}$  and (b)  $J_{\rm D}-V_{\rm GS}$  curves in the temperature range from 300 K to 450 K with  $W_{\rm drift}$  = 1.8  $\mu$ m and  $N_{\rm drift}$  = 3 × 10<sup>15</sup> cm<sup>-3</sup>.

Fig. 7.  $R_{\rm ON}$  and  $J_{\rm D}$  behaviors as functions of temperature for  $V_{\rm GS}$  = 14 V and  $V_{\rm DS}$  = 1 V.

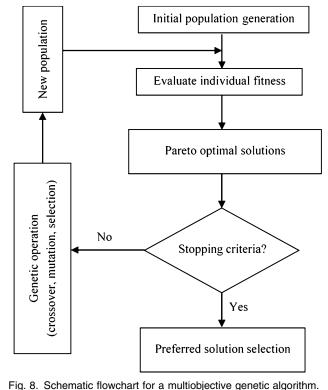

A simplified schematic flowchart for a multiobjective genetic algorithm is shown in Fig. 8. As seen, it is based on the application of selection, crossover, and mutation operations on a certain generation. Starting from an initial population, these operations allow the algorithm to evolve through different generations until a required criterion is reached. Otherwise, the constraint on the maximum number of iterations determines its termination.

In MOGA terminology, a population is a set of chromosomes generated randomly, where each chromosome is made of numbered units called genes. The genes correspond to the design physical and geometrical fitting parameters (e.g., drift region thickness and doping, channel length, etc.). The initial population is made of two chromosomes (parents), and the crossover operation consists in combining them to obtain a new chromosome called offspring. This process is repeated for all the chromosomes to yield the best offspring. At the same time, mutation occurs at the genetic level to ensure the exploration of all the considered parameters. Finally, the selection operation permits the choice of the best offspring to create the next population.

### **Optimized 4H-SiC DMOSFET Design**

In this section, the MOGA-based technique is used to support the numerical and analytical simulation results in order to design an optimized 4H-SiC DMOSFET in terms of breakdown voltage and ON-state resistance. In other words, we deal with

| Table IV. ConfigurationMOGA-based optimization |                   |  |  |

|------------------------------------------------|-------------------|--|--|

|                                                |                   |  |  |

| Number of variables                            | 10                |  |  |

| Population size                                | 1000              |  |  |

| Maximum number of genera-<br>tions             | 100               |  |  |

| Selection                                      | Tournament        |  |  |

| Crossover                                      | Scattered         |  |  |

| Mutation                                       | Adaptive feasible |  |  |

|                                                | migration         |  |  |

| Crossover fraction                             | <b>0</b> .8       |  |  |

| Migration fraction                             | 0.2               |  |  |

| Pareto front population<br>fraction            | 0.5               |  |  |

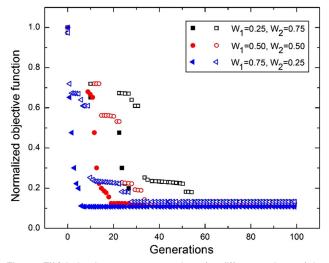

Fig. 9. F(Y) behavior versus generations for different values of the weighting factors  $w_1$  and  $w_2$  when using both numerical (filled symbols) and analytical (empty symbols) models as fitness functions.

two objective functions, considered in the form  $BV_{DS}(Y)$  and  $R_{ON}(Y)$ , where  $Y = \{t_{ox}, W_G, L_{ch}, W_{drift}, X_{JP}, X_{N+}, X_{JFET}, N_A, N_D, N_{drift}\}$  is a vector of device parameters.

The design optimization is evaluated according to the following aim: minimize the ON-state resistance while maximizing the breakdown voltage for a fixed drain-source voltage range. Proper constraints on the physical and geometrical parameters in Y with respect to realistic values are defined during the computations. Also, tournament selection and scattered crossover techniques are employed to generate random vectors, and each combination of Y is binary-coded using biomimicry considerations.

A full set of configuration parameters assumed for the MOGA-based optimization is summarized in Table IV.<sup>58,59</sup>

It is noteworthy that a MOGA-based technique can use either analytical or numerical models indifferently as fitness functions. However, the complexity of the DMOSFET design, which

Fig. 10. Pareto-optimal solutions for the DMOSFET design.

involves different interrelated parameters, suggests that the computational time required by the algorithm should be compared when using numerical or analytical approaches. Moreover, as shown above, the output  $I_{\rm D}-V_{\rm DS}$  characteristics of both models are in good agreement within the device triode region.

To achieve such a comparison of computational time, the weighted sum approach is used to incorporate the two objective functions defined above into a single one, expressed as

$$F(Y) = w_1(1/BV_{DS}) + w_2R_{ON},$$

(13)

where the optimal solution varies according to the values of the weighting factors  $w_1$  and  $w_2$ . In particular, we consider three cases, namely (a)  $w_1 = 0.25$ ,  $w_2 = 0.75$ ; (b)  $w_1 = w_2 = 0.5$ ; (c)  $w_1 = 0.75$ ,  $w_2 = 0.25$ . The behavior of F(Y) as a function of the evolving generations can be be plotted to determine the convergence of the algorithm in each case (Fig. 9).

As shown by this figure, for a single-objective function F(Y) based on a numerical fitness function, convergence occurs within 28 (a), 18 (b), and 5 (c) generations, respectively. In contrast, it occurs within 55 (a), 35 (b), and 28 (c) generations for the analytical function. In addition, the latter optimization procedures require much longer computational time (about twice), amounting to about 10 min to 15 min on a modern personal computer (PC). For the sake of brevity, in what follows only the numerical model is thus considered.

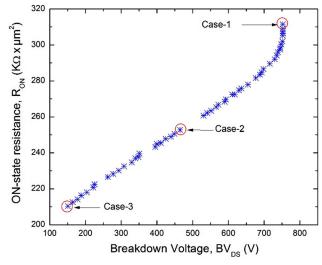

The Pareto front with the assumed objective functions  $R_{ON}(Y)$  and  $BV_{DS}(Y)$  is depicted in Fig. 10. Each pair of solutions ( $R_{ON}$ ,  $BV_{DS}$ ) corresponds to a specific combination of the vector Y.

As shown in Fig. 10, we choose three pairs of solutions to assess the accuracy of the proposed optimization of the design of a device rated for  $BV_{DS}$

and antimization of AU SiC DMOSFET d

|                                                                | Case 1             | Case 2             | Case 3             | <b>Ref. 23</b>      |

|----------------------------------------------------------------|--------------------|--------------------|--------------------|---------------------|

| Design Parameter                                               |                    |                    |                    |                     |

| Silicon oxide thickness, $t_{ox}$ (µm)                         | 0.085              | 0.085              | 0.085              | 0.08                |

| Source thickness, $X_{N+}$ ( $\mu$ m)                          | 0.5                | 0.5                | 0.5                | 0.5                 |

| Channel length, $L_{ch}$ ( $\mu$ m)                            | 1.06               | 1.14               | 1.0                | 1.0                 |

| Base junction depth, $X_{JP}$ ( $\mu$ m)                       | 2.0                | 2.0                | 1.65               | 1.5                 |

| Base-to-base distance, $X_{\text{JFET}}$ ( $\mu$ m)            | 6.13               | 6.72               | 7.6                | 7.0                 |

| Epilayer thickness, $W_{\text{drift}}$ ( $\mu$ m)              | 10                 | 3.75               | 1.8                | 1.8                 |

| Gate width, $W_{\rm G}$ ( $\mu$ m)                             | 8.65               | 9.4                | 10                 | 9.4                 |

| $n^+$ -Source doping, $N_{\rm D}$ (cm <sup>-3</sup> )          | $1	imes 10^{18}$   | $1	imes 10^{18}$   | $1	imes 10^{18}$   | $1	imes 10^{18}$    |

| p-Base doping, $N_{\rm A}$ (cm <sup>-3</sup> )                 | $1	imes 10^{17}$   | $1	imes 10^{17}$   | $1.25	imes10^{17}$ | $1.5 	imes 10^{17}$ |

| <i>n</i> -Drift doping, $N_{\text{drift}}$ (cm <sup>-3</sup> ) | $2.88	imes10^{15}$ | $2.89	imes10^{15}$ | $2.89	imes10^{15}$ | $3	imes 10^{15}$    |

| Objective functions                                            |                    |                    |                    |                     |

| ON-state resistance, $R_{\rm on}$ (k $\Omega \times \mu m^2$ ) | 315                | 250                | 210                | 260                 |

| Breakdown voltage, BV <sub>DS</sub> (V)                        | 800                | 450                | 150                | 150                 |

Table V MOCA be

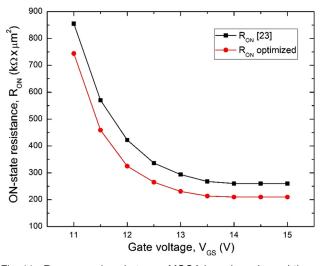

Fig. 11.  $R_{\rm ON}$  comparison between MOGA-based results and those reported in Ref. 23.

of 150 V (case 1), 450 V (case 2), or 800 V (case 3), respectively. The relevant geometrical and physical parameters are summarized in Table V. Here, the fundamental device parameters reported in Ref. 23, which refer to a 4H-SiC DMOSFET with the same device footprint area (15  $\mu$ m<sup>2</sup>) and dimensioned for BV<sub>DS</sub> = 150 V, are also listed for comparison. The  $R_{\rm ON}$  values are calculated for  $V_{\rm GS}$  = 14 V and  $V_{\rm DS}$  = 1 V.

To highlight the efficiency of the proposed design strategy, a comparison with the  $R_{\rm ON}$  results calculated in Ref. <sup>23</sup> for  $V_{\rm GS}$  in the range from 11 V to 15 V and  $V_{\rm DS}$  = 1 V is shown in Fig. 11.

It can be clearly seen that, for a device with the same  $BV_{DS}$  value, the MOGA-based optimization achieves lower  $R_{ON}$  over the whole explored  $V_{GS}$  range. In the full ON-state condition,  $R_{ON}$  is decreased by a factor of up to 20%.

# CONCLUSIONS

An optimized design for a 4H-SiC DMOSFET for a specific application was obtained using a multiobjective genetic algorithm. The electrical characteristics of the device were investigated in terms of the ON-state resistance and breakdown voltage using both analytical and numerical models, revealing good agreement in the considered voltage range. To evaluate the effective device performance, the temperature effect and drain current degradation due to the anisotropic carrier mobility behavior were also introduced. The simulation models were then used as fitness functions for a MOGA-based design with the aim of determining optimal values of the geometrical and physical parameters to minimize the ON-state resistance value for devices with different breakdown voltages in the range from 150 V to 800 V. The analytical and numerical results were also used to evaluate the effectiveness of the MOGA analysis. With respect to a low-voltage DMOSFET dimensioned for  $BV_{DS} = 150$  V, the optimized device achieved an  $R_{ON}$  value close to 210 k $\Omega \times \mu m^2$ , decreased by a factor of 20% with respect to that reported in previous work.

# REFERENCES

- 1. K. Han, B.J. Baliga, and W. Sung, *IEEE Electron Dev. Lett.* 39, 248 (2018).

- S. Mori, M. Aketa, T. Sakaguchi, Y. Nanen, H. Asahara, T. Nakamura, and T. Kimoto, *IEEE Trans. Electron Devices* 64, 4167 (2017).

- D. Bharti and A. Islam, *IEEE Trans. Electron Devices* 65, 615 (2018).

- K. Han, B.J. Baliga, and W. Sung, *IEEE Electron Device* Lett. 38, 1437 (2017).

- Y. Mikamura, K. Hiratsuka, T. Tsuno, H. Michikoshi, S. Tanaka, T. Masuda, K. Wada, T. Horii, J. Genba, T. Hiyoshi, and T. Sekiguchi, *IEEE Trans. Electron Devices* 62, 382 (2015).

- B.J. Baliga, Silicon Carbide Power Devices (Singapore: World Scientific, 2005).

- 7. B.J. Baliga, Fundamentals of Power Semiconductor Devices (New York: Springer, 2008).

- 8. B.H. Choi, S.W. Lee, V.X. Thai, and C.T. Rim, *IEEE Trans.* Power Electron. 29, 5181 (2014).

- 9. J. Fabre, P. Ladoux, and M. Piton, *IEEE Trans. Power Electron.* 30, 4079 (2015).

- A.K. Tripathi, K. Mainali, S. Madhusoodhanan, A. Kadavelugu, K. Vechalapu, D.C. Patel, S. Hazra, S. Bhattacharya, and K. Hatua, *IEEE Trans. Power Electron.* 32, 4231 (2017).

- 11. X. Zhong, X. Wu, W. Zhou, and K. Sheng, *IEEE Trans.* Power Electron. 29, 5091 (2014).

- C.C. Hung, Y.S. Chen, C.T. Yen, C.Y. Lee, L.S. Lee, and M.J. Tsai, *Mater. Sci. Forum* 740, 711 (2013).

- A. Saha and J.A. Cooper, *IEEE Trans. Electron Devices* 54, 2786 (2007).

- G.D. Licciardo, S. Bellone, and L. Di Benedetto, *IEEE Trans. Power Electron.* 30, 5800 (2014).

- 15. A. Merkert, T. Krone, and A. Mertens, *IEEE Trans. Power Electron.* 29, 2238 (2014).

- 16. L. Di Benedetto, G.D. Licciardo, T. Erlbacher, A.J. Bauer,

- and A. Rubino, *IEEE Electron Device Lett.* 37, 1454 (2016).

17. K. Hamada, S. Hino, and T. Kitani, *Mitsubishi Electr. Adv.* 149, 14 (2015).

- A. Bolotnikov, P. Losee, K. Matocha, J. Glaser, J. Nasadoski, and L. Wang, Y. Sui, in *Proc. Int. Symp. Power Semiconductor Devices and ICs-ISPS* (2012), pp. 389–392.

- S. Bechikh, R. Datta, and A. Gupta, *Recent Advances in Evolutionary Multi-objective Optimization* (Switzerland: Springer, 2017).

- ROHM Model SCT2H12NZ (1700 V), http://www.rohm.com/ web/eu/products/-/product/SCT2H12NZ. Accessed 10 Jan 2019.

- CREE Model C3M0280090D (900 V), http://www.wolfspee d.com/c3m0280090d. Accessed 10 Jan 2019.

- ROHM Model SCT3017AL (650 V), http://www.rohm.com/ web/eu/products/-/product/SCT3017AL. Accessed 10 Jan 2019.

- G. De Martino, F. Pezzimenti, F.G. Della Corte, G. Adinolfi, and G. Graditi, in Proc. IEEE Int. Conf. Ph. D. Research in Microelectronics and Electronics-PRIME (2017), pp. 221– 224.

- O. Khan, W. Xiao, and M. Shawky El Moursi, *IEEE Trans.* Power Electron. 32, 3278 (2017).

- H. Zhou, J. Zhao, and Y. Han, *IEEE Trans. Power Electron*. 30, 3479 (2015).

- F.G. Della Corte, G. De Martino, F. Pezzimenti, G. Adinolfi, and G. Graditi, *IEEE Trans. Electron Devices* 65, 3352 (2018).

- G. Graditi, G. Adinolfi, and G.M. Tina, *Appl. Energy* 115, 140 (2014).

- Y. Shi, R. Li, Y. Xue, and H. Li, *IEEE Trans. Power Electron.* 31, 328 (2016).

- 29. F. Pezzimenti, *IEEE Trans. Electron Devices* 60, 1404 (2013).

- F. Pezzimenti, and F.G. Della Corte, in Proc. Mediterranean Electrotechnical Conf.-MELECON (2010), pp. 1129–1134.

- A.O. Konstantinov, Q. Wahab, N. Nordell, and U. Lindefelt, Appl. Phys. Lett. 71, 90 (1997).

- Silvaco Int., Atlas User's Manual, Device Simulator Software (2016).

- S. Selberherr, Analysis and Simulation of Semiconductor Devices (Wien: Springer, 1984).

- A. Galeckas, J. Linnros, V. Grivickas, U. Lindefelf, and C. Hallin, *Appl. Phys. Lett.* 71, 3269 (1997).

- M. Ruff, H. Mitlehner, and R. Helbig, *IEEE Trans. Electron Devices* 41, 1040 (1994).

- T. Ayalew, T. Grasser, H. Kosina, and S. Selberherr, *Mater. Sci. Forum* 483, 845 (2005).

- T. Troffer, M. Schadt, T. Frank, H. Itoh, G. Pensl, J. Heindl, H.P. Strunk, and M. Maier, *Phys. Status Solidi* (a) 162, 277 (1997).

- 38. U. Lindefelt, J. Appl. Phys. 84, 2628 (1998).

- P.T. Landsberg and G.S. Kousik, J. Appl. Phys. 56, 1696 (1984).

- M. Bakowski, U. Gustafsson, and U. Lindefelt, *Phys. Status Solidi (a)* 162, 421 (1997).

- 41. R. Raghunathan and B.J. Baliga, in Proc. IEEE ISPSD (1997), pp. 173–176.

- D.M. Caughey and R.E. Thomas, *Proc. IEEE* 55, 2192–2193 (1967).

- M. Roschke and F. Schwierz, *IEEE Trans. Electron Devices* 48, 1442 (2001).

- X. Li, Y. Luo, L. Fursin, J.H. Zhao, M. Pan, P. Alexandrov, and M. Weiner, *Solid State Electron*. 47, 233 (2003).

- M.L. Megherbi, F. Pezzimenti, L. Dehimi, M.A. Saadoune, and F.G. Della Corte, *IEEE Trans. Electron Devices* 65, 3371 (2018).

- Y. Marouf, L. Dehimi, F. Bouzid, F. Pezzimenti, and F.G. Della Corte, *Optik* 163, 22 (2018).

- F. Bouzid, L. Dehimi, and F. Pezzimenti, J. Electron. Mater. 46, 6563 (2017).

- F. Bouzid, F. Pezzimenti, L. Dehimi, M.L. Megherbi, and F.G. Della Corte, Jpn. J. Appl. Phys. 56, 094301 (2017).

- M.L. Megherbi, F. Pezzimenti, L. Dehimi, A. Saadoune, and F.G. Della Corte, J. Electron. Mater. 47, 1414 (2018).

- K. Zeghdar, L. Dehimi, F. Pezzimenti, S. Rao, and F.G. Della Corte, Jpn. J. Appl. Phys. 58, 014002 (2019).

- F.G. Della Corte, F. Pezzimenti, S. Bellone, and R. Nipoti, Mater. Sci. Forum 679, 621 (2011).

- F. Pezzimenti, L.F. Albanese, S. Bellone, and F.G. Della Corte, in Proc. IEEE Conf. on Bipolar/BiCMOS Circuits and Technology Meeting-BCTM (2009), pp. 214–217.

- W.J. Schaffer, G.H. Negley, K.G. Irvine, and J.W. Palmour, Mater. Res. Soc. Symp. 339, 595 (1994).

- J. Fang, Y. Gao, G. Sun, C. Xu, and Q. Li, *Reliab. Eng. Syst.* Saf. 135, 1 (2015).

- T. Nguyen, S. Nahavandi, D. Creighton, and A. Khosravi, FEBS Lett. 589, 3879 (2015).

- Z. Jin, L. Gao, Q. Zhou, and J. Wang, Sci. Rep. 4, 4268 (2014).

- P.C. Chang, J.C. Hsieh, and C.Y. Wang, *Appl. Soft Comput.* 7, 800 (2007).

- A. Konak, D.W. Coit, and A.E. Smith, *Reliab. Eng. Syst. Saf.* 91, 992 (2006).

- Q. Long, C. Wu, T. Huang, and X. Wang, Swarm Evol. Comput. 22, 1 (2015).

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.