December 2016 Vol. 59 No. 12: 127331 doi: 10.1007/s11433-016-0394-5

## **Recent research development of FinFETs**

Qian Xie<sup>1</sup>, and Jun Xu<sup>2\*</sup>

<sup>1</sup> School of Microelectronics and Solid-State Electronics, University of Electronic Science and Technology of China, Chengdu 610054, China; <sup>2</sup> Tsinghua National Laboratory for Information Science and Technology, Institute of Microelectronics, Tsinghua University, Beijing 100084, China

Received October 8, 2016; accepted October 12, 2016; published online October 24, 2016

Citation: Q. Xie, and J. Xu, Recent research development of FinFETs, Sci. China-Phys. Mech. Astron. 59, 127331 (2016), doi: 10.1007/s11433-016-0394-5

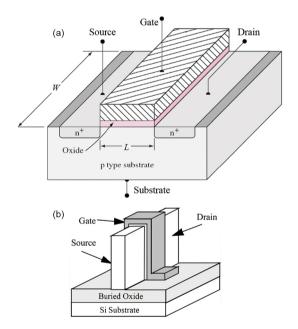

The rapid development of CMOS technology is driven by the device scaling down. Classical MOS devices have encountered difficulties and challenges as scaling down to nanoscale [1], which seriously affects the device performance and limits the further development of CMOS technology. Because of the excellent control over short-channel effects and high current drive capability, novel multi-gate MOS devices have been regarded for years as the most attractive devices to continue the CMOS technology development following "Moore's law" [2]. Among which FinFET, mainly proposed by Hisamoto et al. [3], has attracted considerable scholarly attention [4-7] and has been adopted as the basic device of VLSI by industry. Figure 1 shows the schematic view comparison between classical planar bulk n-channel MOSFET and that of FinFET. Intel is the first company who released the production of 22 nm FinFET technology in 2011. To the authors' knowledge, there are mainly three companies in industry having stepped into FinFET Techonlogy. Samsung plans to ship 10 nm FinFET technology by the end of 2016. Intel will move into 10 nm production by mid-2017, with 7 nm slated for 2018 or 2019. TSMC will move into 10 nm production in early 2017, with 7 nm slated to ship in 2018. Meanwhile, in addition to the three companies, GlobalFoundries will be in the mix at 7 nm. This paper will briefly introduce the recent research development of FinFET, including the experimental research progress and the analytical model research progress.

**Figure 1** (Color online) Schematic view of classical planar bulk *n*-channel MOSFET (a) and FinFET (b).

## (1) Experimental demonstration

**FinFET with Si channel.** Silicon is the main channel material in semiconductor industry. Intel, the company who first released the production of FinFET technology, published a 14 nm logic technology featuring 2nd-Generation FinFET with strained Si channel [8].  $L_{gate}$  scaled from 26 nm in the 22 nm node to 20 nm in the 14 nm node. It is enabled by fin profile optimization and a novel subfin doping. At 0.7 V

• News & Views •

<sup>\*</sup>Corresponding author (email: junxu@tsinghua.edu.cn)

<sup>©</sup> Science China Press and Springer-Verlag Berlin Heidelberg 2016

$V_{dd}$ , off current is 10 nA/µm, and saturated drive currents are 1.04 mA/µm for both NMOS and PMOS. Sub-threshold slope is ~65 mV/decade. DIBL is ~60 mV/V and ~75 mV/V for NMOS and PMOS, respectively. High-density SRAM featuring 0.0588 µm<sup>2</sup> cell size are fabricated usi ng all 14 nm process features.

FinFET with high mobility material channel. III-V materials attract much interest to be adopted as the channel material since they have potential advantages as high mobility, high injection velocity (small *m*\*), and near-ballistic performance. Lu et al. [9] demonstrated and published the first In-GaSb p-channel FinFET. They developed a fin dry-etch technology which yields fins as narrow as 15 nm with vertical sidewalls and realized Si-compatible ohmic contacts with ultra-low contact resistivity of  $3.5 \times 10^{-8} \Omega \cdot \text{cm}^2$ . Gate oxide is Al<sub>2</sub>O<sub>3</sub> with an EOT of 1.8 nm.  $g_{\rm m}$  of 122 µS/µm is obtained in devices of  $W_{\rm f}$ = 100 nm and  $L_{\rm g}$ = 100 nm, while  $g_{\rm m}$  of 78 µS/µm is achieved in the smallest devices with  $W_{\rm f}$  = 30 nm and  $L_{\rm g}$  = 100 nm.

**FinFET with TMD channel.** At ultra-thin body thickness, novel two-dimensional transition-metal dichalcogenide (TMD) is a very attracting channel material for its unique sub-nm monolayer ultra-thin body potential and good transport property at nanometer thinness. For the first time, Chen et al. [10] proposed and demonstrated a 4 nm thin transition-metal dichalcogenide (TMD) body FinFET with back gate control. Two key processes in the demonstration of TMD Fin-FET are CMOS-compatible CVD conformal MoS<sub>2</sub> growth and Hydrogen plasma treatment of MoS<sub>2</sub> for low contact resistance. The front gate MoS<sub>2</sub> FinFET device has on/off current ratio larger than 10<sup>5</sup>. *I*<sub>on</sub> for 1 V *V*<sub>dd</sub> is 200  $\mu$ A/ $\mu$ m.

(2) Analytical model

Long channel *I-V* model. Analytical model is of great importance in depicting the physical insight of device, serving as the guideline for device design and circuit analysis, predicting the future trend of device development, and serving in the circuit simulator. Long channel model is the core model depicting the basic operating behavior of device. Depending on the thickness of top gate insulator compared to that of the side gates, FinFET includes double-gate (DG) and triple-gate (TG) structure. Taur et al. [11] presented a continuous analytical I-V model for DG MOSFETs, which is derived from closed-form solutions of Poisson's equation, and current continuity equation without the charge-sheet approximation. A complete compact model of FinFETs with the DG MOSFET model has been implemented in SPICE. With cylindrical symmetry, the long channel model of surrounding-gate (SG) can be built based on solving 1-D Poisson's equation. Quadruple-gate (QG) MOSFETs resemble SG MOSFET in many aspects. The I-V analytical model of TG FinFETs can be derived based on DG and QG I-V model [12].

Short channel effects model. Short channel effects

(SCEs) have become a significant issue with the continuous scaling of CMOS technology [13]. Xie et al. [14] published a three-dimensional (3-D) analytical model for SCEs in the nanoscale TG FinFET based on solving a boundary value problem using the 3-D Poisson's equation. This SCEs model can be used to predict the minimum channel length ( $L_{min}$ ) of a device under the requirement of keeping SCEs at a tolerable level. Based on the analytical model, the insights into the physics of SCEs in nanoscale TG FinFET are discussed, and design considerations are investigated.

**GER and FER model.** Gate edge roughness (GER) and Fin edge roughness (FER) are two key variability sources in FinFET technology. Jiang et al. [15] proposed a predictive model of GER and FER for the first time. This work well captures the inherent correlations between the variations of device electrical parameters, efficiently predicts that the impacts of GER and FER on circuits are for 16/14 nm node and beyond, and provides helpful guidelines for variationaware design and technology process development. The GER and FER model has been incorporated into industry standard BSIM-CMG core model.

FinFETs have attracted considerable scholarly attention since proposed around 2000. FinFETs with silicon as the channel material have been adopted by industry, and have achieved high transistor performance and density, which marked the semiconductor industry stepping from conventional 2-D planer world into novel 3-D world. The performance of FinFETs can be increased by adopting novel channel materials. FinFETs with III-V high mobility material and TMD as channel materials have been proposed Besides experimental demonstration, and demonstrated. analytical model plays an important role in the aspects of depicting the physical insight of device and predicting the future device development trend. Completed compact model of FinFETs with the DG MOSFET model including short-channel and quantum mechanical effects has been implemented in SPICE, and the GER and FER model has been integrated into industry standard BSIM-CMG core model.

This work was supported in part by the State Key Development Program for Basic Research of China (Grant No. 2016YFA0200404).

- 1 M. Li, Sci. China-Phys. Mech. Astron. 55, 2316 (2012).

- 2 I. Ferain, C. A. Colinge, and J. P. Colinge, Nature 479, 310 (2011).

- 3 D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. J. King, J. Bokor, and C. M. Hu, IEEE Trans. Electron Devices 47, 2320 (2000).

- 4 K. Liao, X. X. Cui, N. Liao, K. S. Ma, D. Wu, W. Wei, R. Li, and D. S. Yu, Sci. China Inf. Sci. 57, 042408 (2014).

- 5 K. S. Ma, X. X. Cui, K. Liao, N. Liao, D. Wu, and D. S. Yu, Sci. China Inf. Sci. 58, 042403 (2015).

- 6 N. Liao, X. X. Cui, K. Liao, K. S. Ma, D. Wu, W. Wei, R. Li, and D. S. Yu, Sci. China Inf. Sci. 57, 022402 (2014).

- 7 K. L. Wei, J. Egley, X. Y. Liu, and G. Du, Sci. China Inf. Sci. 57, 022403 (2014).

- 8 S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang, and K. Zhang, A 14 nm Logic Technology Featuring 2nd-Generation FinFET Transistors, Air-Gapped Interconnects, Self-Aligned Double Patterning and a 0.0588 µm<sup>2</sup> SRAM cell size, in Proceedings of 2014 IEEE International Electron Devices Meeting (IEDM) (IEEE, San Francisco, 2014).

- 9 W. Lu, J. K. Kim, J. F. Kelm, S. D. Hawkins, and J. A. del Alamo, An InGaSb p-Channel FinFET, in Proceeding of 2015 IEEE International Electron Devices Meeting (IEDM) (IEEE, Washington D C, 2015).

- 10 M. C. Chen, K. S. Li, L. J. Li, A. Y. Lu, M. Y. Li, Y. H. Chang,

C. H. Lin, Y. J. Chen, Y. F. Hou, C. Chen, B. Wu, C. Wu, I. Yang, Y. Lee, J. M. Shieh, W. Yeh, J. Shih, P. Su, A. B. Sachid, T. Wang, F. Yang, and C. Hu, *TMD FinFET with 4 nm Thin Body and Back Gate Control for Future Low Power Technology*, in *Proceedings of* 2015 IEEE International Electron Devices Meeting (IEDM) (IEEE, Washington D C, 2015).

- 11 Y. Taur, X. Liang, W. Wang, and H. Lu, IEEE Electron Device Lett. 25, 107 (2004).

- 12 B. Yu, J. Song, Y. Yuan, W. Y. Lu, and Y. Taur, IEEE Trans. Electron Devices 55, 2157 (2008).

- 13 R. S. Wang, T. Yu, R. Huang, and Y. Y. Wang, Sci. China Inf. Sci. 56, 062403 (2013).

- 14 Q. Xie, R. R. Liang, J. Wang, L. B. Liu, and J. Xu, Sci. China Inf. Sci. 57, 042404 (2014).

- 15 X. B. Jiang, X. S. Wang, R. S. Wang, B. J. Cheng, A. Asenov, and R. Huang, Predictive Compact Modeling of Random Variations in Fin-FET Technology for 16/14nm Node and Beyond, in Proceedings of 2015 IEEE International Electron Devices Meeting (IEDM) (IEEE, Washington D C, 2015).