# Dark and illuminated electrical characteristics of Si-based photodiode interlayered with CuCo<sub>5</sub>S<sub>8</sub> nanocrystals

D. E. Yildiz<sup>1</sup> · H. H. Gullu<sup>2</sup> · A. Sarilmaz<sup>3</sup> · F. Ozel<sup>3,4</sup> · A. Kocyigit<sup>5</sup> · M. Yildirim<sup>6</sup>

Received: 28 September 2019 / Accepted: 14 November 2019 / Published online: 23 November 2019 © Springer Science+Business Media, LLC, part of Springer Nature 2019

#### Abstract

Derived from the traditional dichalcogenide CuS structure, ternary transition metal chalcogenide nanoparticles in the form of  $CuCo_5S_8$  are investigated under the aim of photodiode application. In addition to the detailed analysis on material characteristics of  $CuCo_5S_8$  thin-film layer, the work is focused on the electrical characteristics of  $Au/CuCo_5S_8/Si$  diode to investigate its current–voltage, capacitance–voltage, and conductance–voltage characteristics under dark and illuminated conditions.  $CuCo_5S_8$  nanocrystals with an average size of 5 nm are obtained using hot-injection method, and they are used to form thin-film interfacial layer between metal (Au) and semiconductor (Si). Under dark conditions, the diodes show about four orders in magnitude rectification rate and diode illumination results in efficient rectification with increase in intensity. The analysis of current–voltage curve results in non-ideal diode characteristics according to the thermionic emission model due to the existence of series resistances and interface states with interface layer. The measured current–voltage values are used to extract the main diode parameters under dark and illumination conditions. Under illumination, photogenerated carriers contribute to the current flow and linear photoconductivity behavior in photocurrent measurements with illumination shows the possible use of  $CuCo_5S_8$  layer in Si-based photodiodes. This characteristic is also observed from the typical on/off illumination switching behavior for the photodiodes in transient photocurrent, photocapacitance, and photoconductance measurements with a quick response to the illumination. The deviations from ideality are also discussed by means of distribution of interface states and series resistance depending on the applied frequency and bias voltage.

- ☑ D. E. Yildiz desrayildiz@hitit.edu.tr

- Department of Physics, Hitit University, 19030 Corum, Turkey

- Department of Electrical and Electronics Engineering, Atilim University, 06836 Ankara, Turkey

- Department of Metallurgical and Materials Engineering, Karamanoglu Mehmetbey University, 70200 Karaman, Turkey

- Scientific and Technological Research & Application Center, Karamanoglu Mehmetbey University, 70200 Karaman, Turkey

- Department of Electrical and Electronics Engineering, Igdir University, 76000 Igdir, Turkey

- Department of Biotechnology, Selcuk University, 42130 Konya, Turkey

#### 1 Introduction

Chalcogenides are an extraordinarily interesting group of semiconductor compounds in a wide variety of electronic and optoelectronic applications [1, 2]. In the photovoltaic area, thin-film technologies based on this type of compounds have been grown faster in competition with the conventional wafer-based solar cells [3]. It is mostly related to the economical point of view where the use of these compounds can offer less requirement of source material and also simpler fabrication processes with respect to the traditional solar cell technologies. Together with the ternary compound chalcogenide CuInSe<sub>2</sub> as a pioneer in this field, ternary and quaternary Cu chalcogenides have gained great interest for various applications, especially in photovoltaics due to their promising material properties for thin-film devices under solar radiation [4–6]. On the other hand, recent development in the photovoltaic area has been directed to new and better technologies with increasing demand for cheap device applications. In order to fulfill the future demand of solar cells, non-toxic, earth-abundant, and low-cost elements attract

significant interest as an alternative material for the rare elements in the well-known chalcogenide structures [6–8]. Similar to the process in these p-n junction photovoltaic devices, photodiodes have also a potential to be used in solar light conversion to current with having a depletion region to separate photogenerated carriers in a high electric field. Therefore, in place of semiconductor/semiconductor heterojunctions, metal/semiconductor (Schottky) junctions are also used with interfacial layers to gain superior properties for many applications. Metal-semiconductor type diodes are used in many electronic devices, and their electrical properties can be tuned for specific applications by a native insulator layer at the interface and/or an extrinsic interfacial layer stacked between metal and semiconductor [9, 10]. Performance and reliability of these Schottky-type diodes depend on the formation of an interfacial layer and its effects on the diode as the interface states distribution at the interfacial layer and the semiconductor, and inhomogeneous barrier heights together with parasitic resistances. In this approach, in addition to the novel material of SiO2, insulator layer of semiconductor substrates, especially low-dielectric insulator layers such as SnO<sub>2</sub>, TiO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub>, gain importance as potential materials in such applications [11–17]. Due to the open problems in passivation of the active dangling bonds at the semiconductor surface, several inorganic and organic interfacial layers have been employed to improve and also tune their electronic characteristics of these devices [16–18]. In this field, chalcogenide nanocrystals present new developments with material engineering on their optical and electrical properties with size and shape variations that cannot be achieved with changing composition and surface characteristics of their thin-film counterparts [19–21]. Potential optical characteristics in solar light absorption and high charge carrier functionalities in optoelectrical applications make Cu chalcogenide nanocrystals particularly suitable materials for photodiodes [21].

Ternary transition metal chalcogenides offer great potential in a variety of applications including photovoltaic devices and photodetectors, and their nanocrystals gain high level of interest due to superior electrical and optical properties [21–23]. Under the aim of future applications, these materials have presented many research opportunities in low-cost and large-area compatibilities together with preferable energy conversion efficiency and device stability [23]. There are several methods to synthesize these nanocrystals such as solvothermal, hydrothermal, and hot-injection methods [22, 24, 25]. On the other hand, they can be deposited in monolayer form using several techniques such as atomic layer deposition and atomic layer chemical vapor deposition [21, 26, 27]. They are generally used in the diodes as a thin-film layer at the interface, and in this process, several methods such as vacuum evaporation, chemical vapor deposition, and solution-based techniques are used [21]. Among

In this study, the electrical characteristics of the metal (Au)/semiconductor (Si) diode with Cu-based nanocrystal interfacial layer were investigated. This layer was deposited using CuCo<sub>5</sub>S<sub>8</sub> nanocrystals synthesized by hot-injection method with the advantages of easy processing and control in order to obtain high-quality and low-cost materials. These nanocrystals were adopted to the diode as an interfacial layer in the thin-film form deposited on Si surface by spin-coating technique. Derived from the dichalcogenide CuS structure, ternary transition metal chalcogenide nanoparticles in the form of CuX<sub>2</sub>S<sub>4</sub> and their alternatives in different elemental ratios have gained research interest with their effective optical and electronic characteristics [28, 29, 31–33]. In this case, the development in this area has been concentrated on the use of transition metals such as Co, W, and Ni in these compounds to improve the charge storage characteristics of the diodes [33-35]. Therefore, as a member of this family, the work was focused on the diode characteristics of Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode to investigate its current–voltage (I-V), capacitance-voltage (C-V), and conductance-voltage  $(G/\omega - V)$  characteristics under dark and illuminated conditions.

## 2 Experimental details

The synthesis of  $\text{CuCo}_5S_8$  nanocrystals was carried out in 1-octadecene (ODE, 90% tech) by the hot-injection method. To synthesize nanocrystals,  $(\text{Cu}(\text{CO}_2\text{CH}_3)_2 \text{ and } \text{Co}(\text{CO}_2\text{CH}_3)_2 \text{ chemicals with different purities, } 99.995\%$  and 99.99%, were used in 0.2 mmol and 1 mmol, respectively. This solution of  $\text{Co}(\text{Ac})_2$  was mixed with 10 ml ODE in a 25-mL two-necked, round-bottomed flask and heated to 210 °C with magnetic stirring under argon flow. When the reaction medium was reached to 120 °C, freshly prepared S-precursor solution (0,125 mL 1-dodecanethiol (DDT, 98%)) and 0.875 ml tert-dodecanethiol (t-DDT, 98%)) were rapidly injected into the hot reaction mixture under vigorous stirring. Under these conditions, the reaction was continued for 30 min and cooled down to room temperature. Finally,

the nanorods were precipitated adding a mixture of ethanol and toluene (99%) and centrifuged at the rate of 3000 r/min for 1 min.

The cleaning procedure of (100) p-type Si wafer was carried out by shaking it in acetone and propanol by an ultrasonic cleaner, separately. After that, Si wafer was immersed in HF/  $\rm H_2O$  (1:1) solution to remove impurities and native oxide layer from its surface. A 100-nm-thick Al layer was thermally evaporated to the back surface of the wafer as an ohmic contact, and it was annealed for 5 min in  $\rm N_2$  atmosphere at 500 °C to enhance its ohmic contact behavior. The synthesized  $\rm CuCo_5S_8$  solution was deposited on the front surface of the semiconductor substrate as in 180-nm thin-film form by a spin coater. In order to complete the diode structure, Au rectifying contact was thermally deposited on the front surface of  $\rm CuCo_5S_8/p$ -Si using Au trace metals (99.99%).

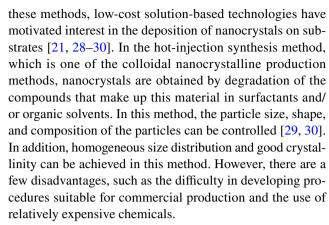

Figure 1a, b shows transmission electron microscope (TEM) images of the as-synthesized nanocrystals. Figure 1a, b clearly shows that the nanocrystals have non-homogeneous size and shape distribution. The average sizes of the  ${\rm CuCo_5S_8}$  nanocrystals are about 5 nm with a standard deviation of 1.5 nm. In addition, high-resolution TEM (HR-TEM) analysis was performed to further confirm the crystallinity and structure of the nanocrystals. Figure 1c shows HR-TEM images of

the nanoparticles, and the lattice fingers of the nanocrystals reveal their highly crystalline nature. The interplanar spacing of CuCo<sub>5</sub>S<sub>8</sub> was measured and found to be 2.36 Å. These can be attributed to the (400) crystallographic planes. The selected area electron diffraction (SAED) patterns agree well with the structure of the CuCo<sub>5</sub>S<sub>8</sub> as shown in Fig. 1d. The polycrystalline SAEDs are indexed with rings to (511), (551), and (822). As shown in this figure, the diffraction rings are discontinuous and consist of sharp spots, which indicate that the nanocrystals are well crystallized. Figure 1e, f shows the typical field emission scanning electron microscope (FE-SEM) images of these nanoparticles. As shown in these images, the nanocrystals exhibit agglomerated morphology. Figure 1g displays the elemental mapping images for the CuCo<sub>5</sub>S<sub>8</sub> structures. As revealed by Fig. 1g, the distributions of the transition metals (Co and Cu) and S in the CuCo<sub>5</sub>S<sub>8</sub> are well in accordance with the element profiles. These results clearly emphasize that highly homogeneous CuCo<sub>5</sub>S<sub>8</sub> structures are achieved by the use of hot-injection method.

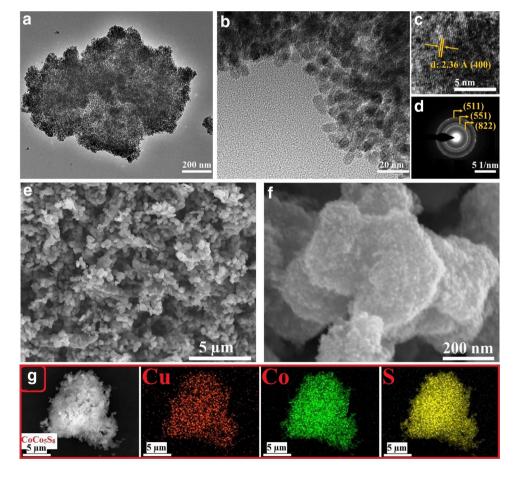

Powder X-ray diffraction (XRD) analysis was employed to investigate the crystallographic structure of the  $CuCo_5S_8$  nanocrystals. Figure 2a displays the XRD pattern of the synthesized nanocrystals. The pronounced peaks at 26.6, 31.3, 38.0, 47, 50, and 54.8 correspond to the (022), (113), (004),

Fig. 1 a, b TEM, c HR-TEM, and d SAED, e, f SEM, and g elemental mapping images of the CuCo<sub>5</sub>S<sub>8</sub> nanocrystals

Fig. 2 a X-ray diffraction pattern, b EDX pattern, and corresponding crystal structure of the CuCo<sub>5</sub>S<sub>8</sub> nanocrystals

(224), (115), and (044) planes of the Cu–Co–S structure, respectively. All diffraction peaks match well with the cubic structured Cu–Co–S (JSPDS No. 00.77-7463). The XRD result was also used to estimate the nanoparticle diameter, using the Scherrer's equation analysis of the strongest XRD peak at 55° revealed an average diameter of 5 nm, in reasonable agreement with that obtained from SEM and TEM measurements [36]. In addition, the energy-dispersive X-ray spectroscopy (EDS) spectrum includes all constituent elements of the final structure, and it confirms the stoichiometry of  $CuCo_5S_8$  (Fig. 2b).

The I-V characteristics of fabricated photodiodes were measured using a FYTRONIX 7000 solar simulator which adjusts the light intensity automatically from 20 to 100 mW/cm<sup>2</sup> under cold light lamp. The C-V and  $G/\omega-V$  measurements were performed by a computer-controlled Keithley 4200 semiconductor characterization system.

## 3 Results and discussion

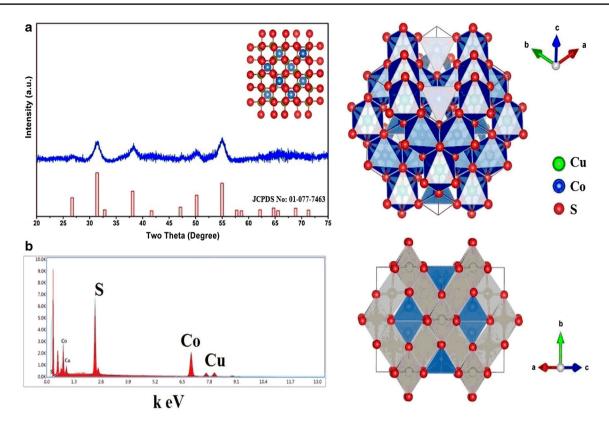

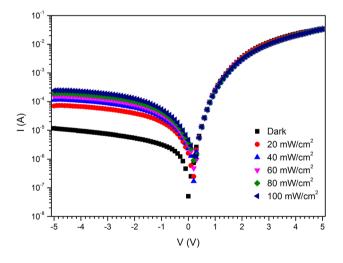

Diode characteristics of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode are investigated by room-temperature *I–V* measurements under dark and different solar illumination intensities in the range of 20–100 mW/cm<sup>2</sup>. In Fig. 3, diode shows a rectifying

Fig. 3 I-V characteristics of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode under dark and illumination with different illumination intensities

behavior where current can flow in the forward-bias region; however, the diode blocks the reverse current transport. It is the indication of good rectifying behavior with four orders of magnitude rectification rate of forward- and reverse-biased currents (RR). On the other hand, there is no remarkable change in forward current value under solar illumination. RR

of the diode decreases with an increase in light intensity due to the increase in the reverse-bias current values, and it can be occurred due to the possible contribution of photogenerated charge carriers to the dark current under illumination [37]. The increase in the carrier concentration because of the generation of electron-hole pairs at the interface is the indication of the photoconducting behavior of the diode, and this light response with good rectifying behavior can be used in the photodiode applications [38, 39]. The sensitivity to light is comparable with previous works on different photodiodes based on Au/Si in terms of change in the current values, especially in reverse-bias region [29, 40]. Although this response is the indication of capacity to be used in photodiode applications, the barrier occurred at the interface to the current flow, and photoinduced carriers from the localized trap states possibly in the interface layer that contribute to the flow can be the reason of the low response in the forward region. The observed *I–V* characteristics under illumination is directly related to the Schottky diode barrier between the rectifying Au contact and the semiconductor Si layer, and also the possible effects of CuCo<sub>5</sub>S<sub>8</sub> layer at the interface. The low response at the forward-bias region can be attributed to the interface layer characteristics where the existence of it at the interface change the junction barrier together with its bulk resistance, structural defects, and interface states, whereas these states can increase the tunneling current at the reverse-bias region [41, 42]. In addition, the weak absorption characteristics of the interface layer can be attributed to this low response compared to the diodes including semiconducting interface film layers [40, 42].

According to the thermionic emission (TE) model, the forward-biased I–V behavior of the diode can be expressed as:

$$I = I_0 \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] \tag{1}$$

where the variations on the TE currents (I) flowing from the metal to semiconductor at barrier depletion are neglected [9, 10]. Based on the rectifying behavior of the diode, the electrical parameters as saturation current  $(I_0)$ , ideality factor (n), and barrier height ( $\Phi_{\rm b}$ ) can be extracted using this relation. The other parameters in Eq. (1) are electronic charge q, Boltzmann constant k, and absolute temperature T in Kelvin unit. In this relation, n is named as the ideality factor for an ideal Schottky barrier, and it is assumed to be independent of V [12, 43]. Therefore, pure TE indicates that I flows only due to TE of carriers with the case of n = 1. In the ideal Schottky diodes, this mechanism can be assumed with defect-free interface between metal and semiconductor, and the deviation from linearity in logarithmic *I–V* curve can only be attributed to series resistance  $(R_s)$ . As a common evaluation, this transport method can be applied to the ohmic

region where the measured current values are in expected linear behavior. This characteristic can also be observed as an experimental result for the Au/n-Si/Al Schottky diodes where I-V data conform with ideal TE as a dominant transport mechanism [44]. Although it can be expected as a dominant factor in the transport mechanism of the diodes with weak deviations from the ideal case neglecting the other contributions by the different mechanisms, I-V characteristics can be found in different transport mechanisms in the conduction with larger n values [9, 43]. Considering the ideal interface-free diode structure, the possible shift in the work function of the rectifying metal and also in the electron affinity of the active semiconductor layer under the effect of interfacial layer formation at the metal-semiconductor interface can be resulted in such deviations [45, 46]. Considering the limit of V, where V > 2kT/q in order to eliminate possible effects of reverse current contribution, Eq. (1) is modified as [43]:

$$I = I_0 \exp\left(\frac{qV}{nkT}\right) \tag{2}$$

According to Eq. (2), linearity in the forward-bias I-V relation (Fig. 3), where TE of majority carriers in the diode is dominant in the carrier diffusion, can be used to extract the main diode parameters [9, 44]. From the intercept of this straight line in the  $\ln(I)$  versus V graph (Fig. 3) at zerobias point, the  $I_0$  value is found as  $2.62 \times 10^{-7}$  A and listed in Table 1. It is the parameter related to the reverse current occurring by the diffusion of the minority charge carriers. This behavior is formulated in the Schottky-type diodes as:

$$I_0 = AA^*T^2 \exp\left(-\frac{q\Phi_b}{kT}\right),\tag{3}$$

where  $I_0$  is expected to be almost independent of the reverse-bias voltage, and the parameters A is the active diode area defined by the Au–metal contact region on top of the CuCo<sub>5</sub>S<sub>8</sub> layer (3.14×10<sup>-2</sup> cm<sup>2</sup>), and  $A^*$  is the effective Richardson constant of the active semiconducting layer with the assumption of uniform barrier height formation

Table 1 Diode parameters under dark and illumination conditions

| Condition              | $I_0 (\times 10^{-7} \text{ A})$ | n    | $\Phi_{\rm b} \left( I \! - \! V \right) \left( { m eV} \right)$ | $ \Phi_{\rm b} $ (Cheung) (eV) |

|------------------------|----------------------------------|------|------------------------------------------------------------------|--------------------------------|

| Dark                   | 2.62                             | 6.72 | 0.687                                                            | 0.670                          |

| 20 mw/cm <sup>2</sup>  | 1.79                             | 5.70 | 0.697                                                            | 0.684                          |

| 40 mw/cm <sup>2</sup>  | 1.39                             | 5.42 | 0.704                                                            | 0.701                          |

| 60 mw/cm <sup>2</sup>  | 1.05                             | 4.74 | 0.711                                                            | 0.717                          |

| 80 mw/cm <sup>2</sup>  | 0.79                             | 4.25 | 0.719                                                            | 0.721                          |

| 100 mw/cm <sup>2</sup> | 0.75                             | 3.82 | 0.720                                                            | 0.732                          |

(32 A/cm<sup>2</sup>K<sup>2</sup> for the p-Si) [9, 47]. Introducing the obtained  $I_0$  to Eq. (3), apparent  $\Phi_b$  value at zero bias is calculated as 0.69 eV. Compared to the literature works on Au/p-Si Schottky diodes, it is higher than the reported values of 0.33 eV [43] and 0.34 eV [48] where difference in deposition methods and/or deposition conditions may cause this small difference between these values. It was also studied in Au/n-Si form; however, the obtained values are higher than the ones found using p-Si [13, 44]. This occurred because barriers on p-type semiconductors are generally lower than those on n-type of the same semiconducting material [48]. Thermal deposition of Au metal on p-Si can also be effective in this barrier formation where the existence of the defects on the Si surface, and its effects to the effective barrier height of Si in the Au/p-Si Schottky barriers can be evaluated as the possible reasons for different barrier heights [49]. In a metal-semiconductor diode, the band gap of the semiconductor is the dominant factor in the formation of the barrier height and the existence of natural and/or deposited interface layer can affect the value of barrier height [44]. At this point, free carrier concentration and better conductivity of the p-Si layer compared to CuCo<sub>5</sub>S<sub>8</sub> layer indicates the dominant effect of p-Si layer on the current flow mechanism in the diode [38, 50]. The value of  $\Phi_{\rm h}$  derived from CuCo<sub>5</sub>S<sub>8</sub> interlayered Au/p-Si diode is in a good correlation with the similar comparisons between Au/p-Si structure with and without oxide/dielectric/insulator interface layer [13, 41, 42, 46]. The increase in  $\Phi_b$  with CuCo<sub>5</sub>S<sub>8</sub> layer can be the result of increasing charge carriers at the interface due to the existence of localized trap states at the semiconductor interface [13]. Additionally, in most of the cases, it is in the range of the reported values for different interface layers such as  $\alpha$ -PbO<sub>2</sub> [40], FePc [41], InP quantum dots [42], and several other organic layers [46, 51]. The observed barrier height between Au metal and Si semiconductor with interface film layer can be also evaluated in the same electrical response of Au/n-Si together with different interface layers such as  $TiO_2$  [14],  $SnO_2$  [52],  $Si_3N_4$  [13], and  $SiO_2$  [53]. On the other hand, as compared to the effect of Cu<sub>2</sub>WSe<sub>4</sub> nanosheet layer, the obtained value is smaller than the reported one as 0.82 eV even if both are in nanostructural form [29].

In addition to  $\Phi_b$ , n is calculated as the main diode parameter from the slope of linear region in the forward-biased semilogarithmic I–V plot (Fig. 3) as:

$$n = \frac{q}{kT} \left( \frac{dV}{d\ln(I)} \right),\tag{4}$$

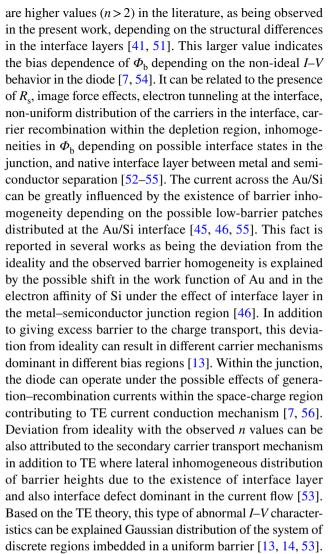

and it is found as to be 6.72, which is greater than unity. It can be evaluated as one of the highest values in Au/p-Si-based Schottky diodes with an intentional interlayer. Although the values are expected to be in the range of 1–2 for the applicability of TE mechanism [40, 42, 46], there

The I–V plots of the diode under different solar illumination intensities from 20 to 100 mW/cm<sup>2</sup> are given in Fig. 3. The increments in the reverse-bias current value with illumination and direct proportionality with the illumination intensity can be attributed to the effects of photogenerated carriers in the interface [29]. In fact, change in the electrical response of the Au/p-Si diode with interface layer, and as a result, barrier height modification due to the effect of localized charge carriers at the interface trap states can be related to this observation in the photoresponse of the diode [40, 42]. In addition to the dark analysis, electrical parameters given in Eq. (2) are extracted for the illumination conditions and the results are tabulated in Table 1. As listed in this table, it is found that there is a decrease in n to 3.82, whereas an increase in  $\Phi_b$  to 0.72 eV was observed. Therefore, the illumination response and carrier transport process across the diode can be explained by the dominant effect of photogenerated carriers together with the decrease in recombination of the electron-hole pairs due to the presence of interface layer [29, 56].

The expression given in Eq. (2) is the case of TE regardless of the effect of  $R_{\rm s}$ ; however, the saturation behavior at high-forward-bias region is related to the dominant effect of  $R_{\rm s}$  in the current flow. Therefore, the general equation in Eq. (1) can be modified by changing the voltage V across the diode in the exponential relation as  $qV - IR_{\rm s}$ , where IR $_{\rm s}$  term is the voltage drop under the effect of  $R_{\rm s}$  according to the Cheung and Cheung method [57]. The method is proposed the saturation region where V > 3kT/q and revised the diode equation as:

$$I = I_0 \left[ \exp\left(\frac{qV - IR_s}{nkT}\right) - 1 \right]$$

(5)

It is an alternate approach to determine  $R_s$  values corresponding to Norde (proposed for n = 1 case) and Sato and Yasumura (for the n > 1 case) in the differential form as [57–59],

$$\frac{dV}{d\ln(I)} = IR_s + n\frac{kT}{q} \tag{6}$$

This relation directs the use of  $dV/d\ln(I)$  versus I plots and the current-dependent junction in the form as,

$$H(I) = V - n \left(\frac{kT}{q}\right) \ln\left(\frac{1}{AA^*T^2}\right) \tag{7}$$

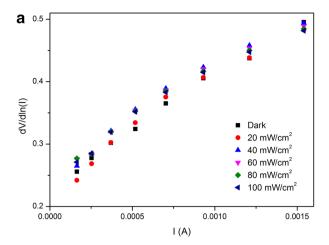

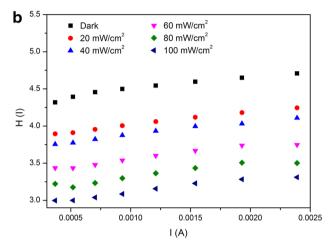

where  $H(I) = IR_s + n\Phi_h$ . The results obtained from the analysis of both  $dV/d\ln(I)$  and H(I) functions are shown in Fig. 4a, b, respectively. The straight lines observed from these plots are modeled by a linear fitting process. As a result, the calculated  $\Phi_{\rm h}$  values are given in Table 1 and also  $R_s$  values obtained from both of the linear plots are shown in Fig. 4c with respect to the dark and illumination conditions. Under dark, the values are about 150–200  $\Omega$  that can be feasible in possible photodiode applications [29], and this value is in the same order of magnitude with the other reported diodes based on Au/p-Si with an insulator/oxide layer [46, 51]. However, in comparison with metal-semiconductor structure, this resistance value is expected to be higher than the value without interface layer [13]. It can be due to the possible natural resistance to the current flow with the existence of interface states and the possible change in current transport mechanism under the effect of a wide distribution of these states [13, 41]. There is a consistency in the  $\Phi_h$  values with TE and Cheung approaches in the change of dark to illumination conditions and the slight difference can be attributed to the working range of bias voltage and also the effect of  $R_{\rm s}$  [60]. On the other hand, use of both the Cheung functions gave consistent values in the same order of magnitude, and they are found to be quite sensitive to illumination intensity. As shown in Fig. 4c, there is a decrease in the  $R_s$  values with increasing illumination intensity under the

**Fig. 4**  $R_s$  values derived from I-V results according to **a**  $dV/d \ln(I) - I$  and **b** H(I) - I analyses for different illumination conditions; **c**  $R_s - P$  plot of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode

effect of photogenerated carriers [61]. This photoresponse of the diode can be detailed with the photocurrent and illumination intensity relation as:

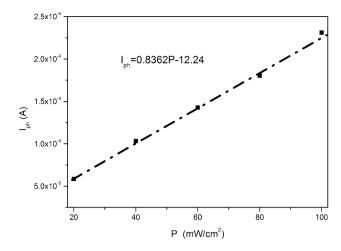

**Fig. 5**  $\ln(I_{\rm ph})$  versus  $\ln(P)$  plot of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode

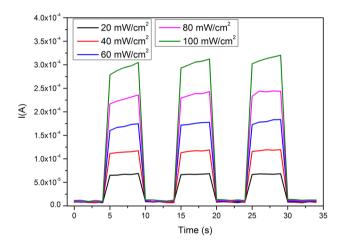

**Fig. 6** I(t) - V plots of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode

$$I_{\rm ph} = BP^m \tag{8}$$

where  $I_{\rm ph}$  is the photocurrent generated by solar light illumination on the diode, P is the applied illumination intensity, m is the illumination coefficient, and B is the proportionality constant [62]. The plot of  $ln(I_{ph})$  versus P is generated, and according to Eq. (8), the expected linear relation is achieved as shown in Fig. 5. The observed straight line behavior indicated the linear photoconductivity behavior, and therefore, photoconduction mechanism in the diode can be explained with the value of m [56, 62]. In this analysis depending on lifetime of the photocarriers, if the monomolecular recombination is dominant, it results in the case of m = 1. On the other hand, the higher values are originated from the lowdensity uninvaded trap levels. From the linear fitting process, this value is found to be 0.84 in 0 < m < 1 interval. As a result, the existence and also continuous distribution of the localized states can be verified in the diode [52, 63].

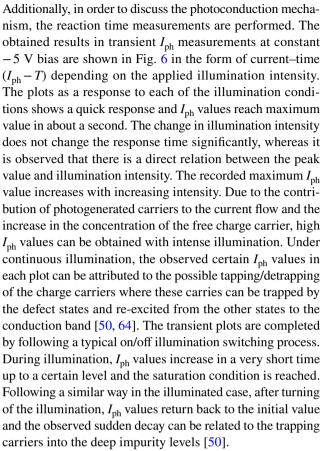

In addition to the I–V analysis, the transient photocapacitance  $(C_{\rm ph})$  and photoconductance  $(G_{\rm ph})$  measurements are performed as a function of time in order to detail the effects of the photogenerated carriers. The corresponding plots at 100 kHz of frequency given in Fig. 7a, b. As in the illuminated I-V behavior, a strong illumination intensity dependence of  $C_{\rm ph}$  and  $G_{\rm ph}$  values is observed. During illumination, both of these values increase up to certain values under a similar approximation for the contribution of generated carriers to the conduction process [56]. Additionally, these values increase with the increase in illumination intensity and the highest values are obtained at the highest illumination intensity condition. After illumination is turned off, the values at maximum point decrease and drop back to their initial values possibly due to trapping of the charge carriers into the deep levels [56, 65].

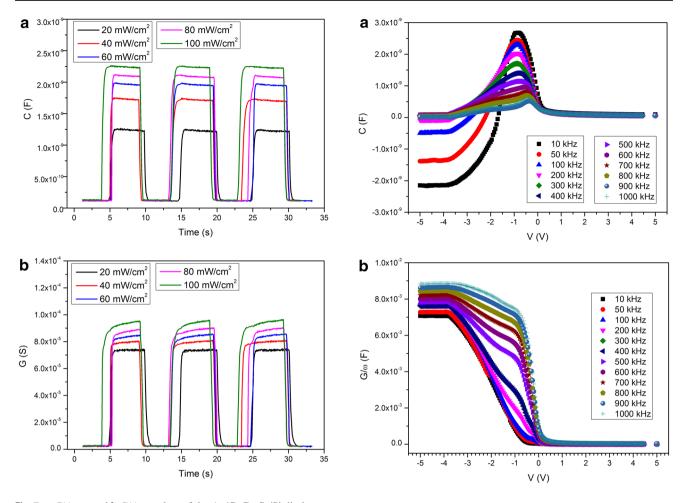

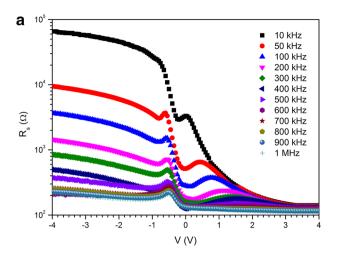

Under dark and room conditions, the frequency-dependent capacitance-voltage (C-V) graph of the diode is shown in Fig. 8a. The data are collected between -4 and +4 V bias voltage and 10 kHz to 1 MHz frequency regions. In this plot, starting from the reverse-bias case, saturation capacitance values are observed in the high-reverse-bias region. With increasing frequency, these values increase and reach a maximum value at low-forward-bias region. On the other hand, increasing bias voltage in the forward-bias region causes a decrease in the capacitance values, and they

**Fig. 7** a C(t) - t and b G(t) - t plots of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode

Fig. 8 Frequency-dependent (a) C-V and (b) G-V plots of the Au/  $CuCo_5S_a/Si$  diode

exhibit saturation behavior around the zero-capacitance point. Under the effect frequency, the values are low in high-reverse-bias region, whereas the magnitude of the peak is obtained at the lowest frequency. This behavior can be explained by the effect of  $R_s$  and also the indication of the existence and response of interface charges to the change in alternating current (AC) [16, 29]. A decrease in the values at each frequency plots at the high-forward- and highreverse-bias regions is related to the effect of  $R_s$  [66]. On the other hand, frequency effects on these measured values are observed strongly at low frequencies. Together with the effects of  $R_s$ , the observed variations mostly in depletion and accumulation zones can be related to the presence of the interface states. At this point, resistance can be related to the bending behavior of these curves in the accumulation region with the contribution of interface traps in the depletion region [16]. The higher capacitance values are obtained at low frequencies where the density of interface states  $(D_{it})$ is in equilibrium with the semiconductor [16, 67]. At these frequencies, under the effect of interfacial space-charge formation, interface state capacitance contributes to the total

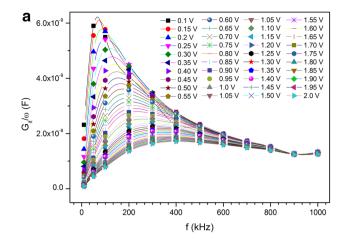

diode capacitance causing observed excess capacitive behavior. In addition, the particularly distributed interface states can follow the applied AC signal and the response to the change in frequency is the case depending on the intrinsic characteristics of the interface states as relaxation time of charges [68]. This behavior can also be attributed to the time-depending response of the diode with the dielectric polarization of the interface layer under the effect of applied electric field [67]. The conductance (G) characteristics of the diode are shown in Fig. 8b in the form of  $G/\omega - V$  plots at different frequencies.  $G/\omega$  values are sensitive in the forward-bias region at low frequencies related to the ability of the interface states to follow the applied AC signal and the contribution of charges to the conductive behavior. Similar to the capacitive behavior, the interlayer variations as  $D_{it}$ and also the existence and possible effects of  $R_s$  depending on the change in frequency limit the conductive behavior. At high frequencies,  $D_{it}$  cannot follow the AC signal, and conductance values decrease with the elimination of charges in these states [69, 70]. These observed frequency-dependent

variations in Fig. 8 can also be expected from metal–semiconductor diode with different interface layers and without them at the Au–Si interface [15, 16, 29]. Although the observed decreasing behavior with increasing frequency can be evaluated as a general behavior, the peak formation generally in C-V curve can be attributed to the existence of  $D_{\rm it}$ in the depletion region due to the interface state [15, 16]. In addition, the single peak observed in this curve can be the indication of localization of these states in one region [16].

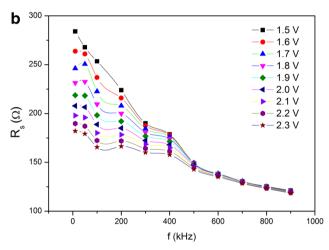

Due to the experimental nature, non-ideality behaviors are observed in these C - V and  $G/\omega - V$  spectra as in the case of I - V characteristics. Therefore, similar to the I - Vanalysis, inhomogeneities in the interfacial layer and barrier height depending on the presence of an interfacial insulator layer on Si surface, interface states between Si and metal Au as  $D_{it}$ , and  $R_s$  can be evaluated based on these data to discuss these deviations [71–73]. At this point of view, the semiconductor/insulator interface and also the effects of  $R_s$ and  $D_{it}$  have become indicative characteristic parameters in the analysis of the origin of these frequency-dependent variations [73]. Although there are several techniques to extract  $R_{\rm s}$ , the method developed by Nicolian presents a theoretical expression generally acclaimed in the literature [71]. At sufficiently high frequencies and in the strong accumulation region,  $R_s$  is expected to be dominant in the current flow. Therefore, these voltage- and frequency-dependent values can be extracted as:

$$R_s = \frac{(G/\omega C)^2}{\left[1 + (G/\omega C)^2\right]G} \tag{9}$$

where  $\omega$  is the angular frequency of the AC signal ( $\omega = 2\pi f$ ) [7]. According to Eq. (9), the  $R_s$  values are calculated with bias voltage dependence at each frequency, and the results are given in Fig. 9a. As seen in this figure, the values are in the same order in magnitude with the obtained values from I-V analysis. The calculated values strongly depend on frequency and decrease with an increase in bias voltage at constant frequency [16, 29]. There are peak points dominant at lower frequencies and the intensity of these peaks decrease together with positional shift toward lower voltages with an increase in the applied frequency. This behavior is observed in all frequency-dependent  $R_s$  profiles, and it can be attributed to the localized interlayer states and possible interface layer formation on Si surface [8, 70]. It is also the fact correlating with the frequency-dependent characteristics of the measured C-V and  $G/\omega - V$  plots [16]. On the other hand, there is a weak response of the  $R_s$  values to the variation in high-frequency region. In addition, these values are presented as a function of frequency under constant bias voltage in Fig. 9b. As shown in Fig. 9, these values change under the dependence of both frequency and voltage. Furthermore, there is a strong response at low bias voltage and

Fig. 9 Variations of  ${\bf a}$  frequency- and  ${\bf b}$  voltage-dependent  $R_{\rm s}$  values of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode

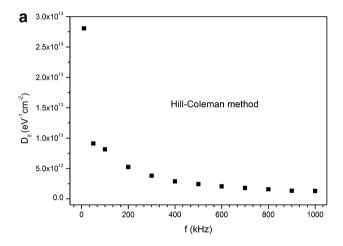

low-frequency region in these plots. In a similar behavior observed in  $R_s$ -V plot,  $R_s$  values decrease with increase in frequency in addition to the decrease with increasing bias voltage. It is the trapped charge effect on  $R_s$  values, and these variations depending on both voltage and frequency changes can be related to the inhomogeneity in the diode interface and the distribution of  $D_{it}$  [70]. In accordance with the interface layer nature, the saturation behavior at the highforward-bias region can be observed due to the its passivation effect [16]; however, the obtained resistance values are expected to be greater than the values in the diode without interface layer depending on the physical barrier of this layer to the current flow. Together with  $R_s$  analysis, the frequency and voltage-dependent  $D_{it}$  characteristics of the diode can be investigated in order to detail the electrical quality of the interface layer. Therefore, the change in  $D_{it}$  under frequency is investigated using Hill-Coleman conductance method as:

$$D_{it} = \frac{2}{qA} \left( \frac{(G/\omega)_{\text{max}}}{\left( (G/\omega)_{\text{max}} C_i \right)^2 + \left( 1 - C_{\text{max}} / C_i \right)^2} \right)$$

(10)

In this expression, C and G are the measured capacitance and conductance values at each frequency where  $(G/\omega)_{\rm max}$  denotes the peak value in the conductance profile (at 1 MHz) and  $C_{\rm max}$  is the value corresponding to this peak point [74]. According to Eq. (10), the possible effects of the interfacial layer can be examined using  $D_{\rm it}-f$  graph where the profile strongly depends on the  $C_{\rm i}$  values in the strong accumulation region.  $C_{\rm i}$  values can be expressed as [75]:

$$C_{\rm i} = C_{\rm max} \left( 1 + \left( \frac{G_{\rm max}}{\omega C_{\rm max}} \right)^2 \right). \tag{11}$$

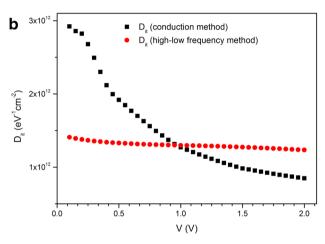

The obtained frequency-dependent distribution profile of  $D_{it}$  is shown in Fig. 10a. As shown in this figure,  $D_{it}$  values decrease with the increment in frequency where the

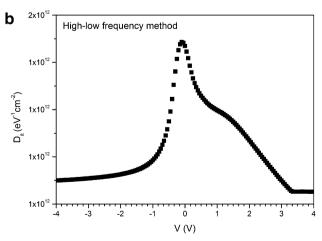

Fig. 10  $D_{it}$  profiles of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode according to a Hill-Coleman and b high-low-frequency methods

parabolic decrease is in a good accordance with the literature and also these values close to a constant value at the higher frequency region [15, 16]. Based on the non-ideal diode characteristics, this fact can be related to the high-frequency response of  $D_{\rm it}$  to the change in the external AC signal [67, 76]. Another way to determine the  $D_{\rm it}$  profile is the high-low-frequency capacitance ( $C_{\rm HF}$ – $C_{\rm LF}$ ) method in the form as:

$$D_{\rm it} = \frac{C_{\rm it}}{qA} = \frac{1}{qA} \left[ \left( \frac{1}{C_{\rm LF}} - \frac{1}{C_{\rm i}} \right)^{-1} - \left( \frac{1}{C_{\rm HF}} - \frac{1}{C_{\rm i}} \right)^{-1} \right]. \tag{12}$$

This expression gives the bias voltage-dependent distribution of  $D_{it}$  values where  $C_{HF}$  and  $C_{LF}$  are the values observed at the highest-frequency capacitance (1 MHz) and lowest-frequency capacitance steps (at 50 kHz), respectively [77]. The voltage-dependent profile with a peak around 0.1 V is shown in Fig. 10b, and the obtained values using both Hill-Coleman and  $C_{HF}$ - $C_{LF}$  methods are in the same order in magnitude. In comparison with the literature, these values are in the same range with the values reported as a result of both I-V and C-V analyses [13. 16, 29, 46]. However, the effect of the interface layer can be observed in the decrease in these values with respect to the diode without this layer formation at the interface [13, 16]. It is due to the interface states originating from this layer and also the remedial effect on the interfacial trapped charges can be occurred at the interface [16]. The peak profile in the  $D_{it}$ -V plot indicates a certain  $D_{it}$  between the metal (Au) and the semiconductor (Si) due to the interruption of the structural periodicity, and therefore, it can be concluded that these traps are uniformly distributed inside the band gap of the semiconductor layer [68, 78]. In order to evaluate the effects of  $D_{it}$ , the conductance of interface states  $(G_{it})$  can be formulated according to the Nicollian and Goetzberg model as:

$$G_{\rm it} = \frac{qI_{\rm dc}}{kTA} \frac{C_{\rm i}(C - C_{\rm HF})}{(G/\omega)^2 + (C - C_{\rm LF})^2},$$

(13)

where  $I_{\rm dc}$  is used to donate the forward-bias current flow in the diode [71]. The obtained  $G_{\rm it}/\omega-f$  plots are presented in Fig. 11a with a peak profile at the low-frequency region. This peak behavior can be ascribed with the existence of interface traps and the profile is strongly dependent on the occupancy of the interface trap levels [78]. In fact, the existence of these maximum  $G_{\rm it}/\omega$  values indicates the uniform distribution of  $D_{\rm it}$  which affects the value of capture cross sections of traps [78, 79]. As seen in Fig. 11a, the peak intensity decreases and the peak position shifts toward higher frequencies with increasing bias voltage. The observed shift can be related to the characteristic time of the interface states to fill and

Fig. 11 a  $G_{\rm it}/\omega-V$  plot of the Au/CuCo<sub>5</sub>S<sub>8</sub>/Si diode and b comparison of the  $D_{\rm it}$  profiles obtained from conductance and high–low-frequency methods

empty with the electrons exchanging by the valence band of the semiconductor [78]. From the peak points observed in Fig. 11a,  $D_{\rm it}$  values can be found as a function of voltage as,

$$D_{it} = (G_{it}/\omega)_{\text{max}/0.402qA}$$

(14)

where  $G_{it}$  values can be related to the time constant of interface states  $(\tau)$  as:

$$G_{it} = \frac{AqD_{it}}{2\tau} ln(1 + \omega^2 \tau^2), \tag{15}$$

and the maximum condition  $\omega \tau = 1.98 \left[ \partial G_{\rm it} / \partial (\omega \tau) = 0 \right]$  is applied to determine  $D_{\rm it} - V$  profile shown in Fig. 11b. Comparing with the experimental results found in Fig. 10a, although there exists an almost continuous distribution of  $D_{\rm it}$  values based on the high–low-frequency method, the values obtained from the conduction method given in Eq. (15)

## 4 Conclusion

In this work, together with the detailed structural and morphological analysis of CuCo<sub>5</sub>S<sub>8</sub> thin-film layer, the electrical characteristics of spin-coated CuCo<sub>5</sub>S<sub>8</sub> film interlayered Al/CuCo<sub>5</sub>S<sub>8</sub>/Si diode are discussed in terms of current and capacitance measurements under dark and solar-illuminated conditions. Dark I-V characteristics show a good rectifying behavior with about  $\Phi_h$  and n of 0.69 eV and 6.72, respectively. Under illumination, the reverse current values increase with the contribution of photogenerated carriers to the current flow, and it results in an increase in  $\Phi_h$  but in a decrease in n values. The saturated regions in the forward-bias region are evaluated with the possible effects of  $R_s$ , and the values are obtained based on Cheung functions. Photoconducting and photocapacitive behaviors of the diode are discussed by transient measurements and the potentials of this diode in several optoelectronic applications are verified. Depending on the applied bias voltage and frequency, capacitance and conductance profiles are evaluated considering the possible effects of  $R_s$  and  $D_{it}$ . The calculated  $R_s$  values show a strong dependency to the change in frequency and voltage. The  $R_s$  profiles exhibit peaks as a response to the frequency change due to the localized states and possible native interface layer formation on Si surface. Because the photoresponse behavior of the diode indicates the existence of these states, the D<sub>it</sub> profiles are discussed according to the high-low-frequency, Hill-Coleman, and conductance methods.

**Acknowledgment** This study was supported by TUBITAK (The Scientific and Technological Research Council of Turkey) under Project Number 217M212.

### References

- R. Scheer, H.W. Schock, Chalcogenide photovoltaics: Physics, technologies, and thin film devices (Wiley, Singapore, 2011)

- 2. G.K. Ahluwalia, Applications of Chalcogenides: S, Se and Te (Springer, Berlin, 2017)

- S.R. Kodigala, Thin Film Solar Cells from Earth Abundant Materials: Growth and Characterization of Cu<sub>2</sub>(ZnSn)(SSe)<sub>4</sub> Thin Films and Their Solar Cells (Elsevier, Amsterdam, 2014)

- H. Matsushita, Y. Tojo, T. Takizawa, J. Phys. Chem. Solids 64, 1825 (2003)

- 5. H.H. Gullu, M. Parlak, J. Electron. Mater. 48, 3096 (2013)

- T. Wada, S. Nakamura, T. Maeda, Prog. Photovolt Res. Appl. 20, 520 (2012)

- M. Terlemezoglu, O. Bayrakli, H.H. Gullu, T. Colakoglu, D.E. Yildiz, M. Parlak, J. Mater. Sci.: Mater. Electron. 29, 5264 (2018)

- H.H. Gullu, D.E. Yildiz, O. Bayrakli Surucu, M. Terlemezoglu, M. Parlak, Bull. Mater. Sci. 42, 45 (2019)

- S.M. Sze, Physics of Semiconductor Devices (Wiley, New York, 1981)

- E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts (Oxford University Press, London, 1988)

- F. Yigiterol, H.H. Gullu, O. Bayrakli, D.E. Yildiz, J. Electron. Mater. 47, 2979 (2018)

- O. Bayrakli Surucu, H.H. Gullu, M. Terlemezoglu, D.E. Yildiz, M. Parlak, Physica B 570, 246 (2019)

- 13. A. Tataroglu, Chin. Phys. B **22**, 068402 (2013)

- H. Altuntas, A. Bengi, T. Asar, U. Aydemir, B. Sarikavak, Y. Ozen, S. Altindal, S. Ozcelik, Surf. Interface Anal. 42, 1257 (2010)

- M. Yildirim, M. Gokcen, Mater. Sci. Semicond. Proc. 15, 406 (2012)

- 16. T. Ataseven, A. Tataroglu, Chin. Phys. B 22, 117310 (2013)

- 17. S. Altindal, O. Sevgili, Y. Azizian-Kalandaragh, J. Mater. Sci.: Mater. Electron. 30, 9273 (2019)

- I. Orak, A. Kocyigit, I. Karteri, S. Urus, J. Mater. Electron. 47, 6691 (2018)

- X. Huang, G. Deng, L. Liao, W. Zhang, G. Guan, F. Zhou, Z. Xiao, R. Zou, O. Wang, J. Hu. Nanoscale 16, 2626 (2019)

- B. Li, F. Yuan, G. He, X. Han, X. Wang, J. Qin, Z.X. Guo, X. Lu, Q. Wang, I.P. Parkin, C. Wu, Adv. Funct. Mater. 27, 1606218 (2017)

- C. Coughan, M. Ibanez, O. Dobrozhan, A. Singh, A. Cabot, K.M. Ryan, Chem. Rev. 117, 5865 (2017)

- D. Aldakov, A. Lefrancois, P. Reiss, J. Mater. Chem. C 1, 3756 (2013)

- 23. H. Fu, S.W. Tsang, Nanoscale 4, 2187 (2012)

- A. Kagkoura, T. Skaltsas, N. Tagmatarchis, Chem. Eur. J. 23, 12967 (2017)

- W. Chen, H. Chen, H. Zhu, Q. Gao, J. Luo, Y. Wang, S. Zhang, K. Zhang, C. Wang, Y. Xiong, Y. Wu, X. Zheng, W. Chu, L. Song, Z. Wu, Small 10, 4637 (2014)

- S. Zheng, L. Sun, T. Yin, A.M. Dubrovkin, F. Liu, Z. Liu, Z.X. Shen, H.J. Fan, Appl. Phys. Lett. 106, 063113 (2015)

- L. Reijnen, B. Meester, A. Goossens, J. Schoonman, Mater. Sci. Eng. C 19, 311 (2002)

- A.M. Wiltrout, C.G. Read, E.M. Spencer, R.E. Schaak, Inorg. Chem. 55, 221 (2016)

- A. Kocyigit, M. Yildirim, A. Sarilmaz, F. Ozel, J. Alloy Compd. 780, 186 (2019)

- M. Yıldırım, A. Sarılmaz, F. Ozel, J. Mater. Sci.: Mater. Electron. 29, 762 (2018)

- I. Bezverkhyy, M. Danot, P. Afanasiev, Inorg. Chem. 42, 1764 (2003)

- C.J. Crossland, P.J. Hickey, J.O.S. Evans, J. Mater. Chem. 15, 3452 (2005)

- M. Chauhan, K. Soni, P.E. Karthik, K.P. Reddy, C.S. Gopinath, S. Deka, J. Mater. Chem. A, Advance Article. (2019). https://doi. org/10.1039/C9TA09896H

- 34. J. Tang, Y. Ge, J. Shen, M. Ye, Chem. Commun. 52, 1509 (2016)

- X. Xu, Y. Liu, P. Dong, P.M. Ajayan, J. Shen, M. Ye, J. Power Sources 400, 96 (2018)

- 36. A. Roth, Vacuum Technology (North Holland, Amsterdam, 1980)

- A. Kocyigit, I. Karteri, I. Orak, S. Urus, M. Caylar, Physica E 103, 452 (2018)

- F. Aslan, H. Esen, F. Yakuphanoglu, J. Alloy Compd. 789, 595 (2019)

- M. Yalcin, D. Ozmen, F. Yakuphanoglu, J. Alloy Compd. 796, 243 (2019)

- M.M. Makhlouf, M.M. el-Nahass, M.H. Zeyada, Mater. Sci. Semicond. Proc. 58, 68 (2017)

- 41. C. Oruc, A. Altindal, Appl. Phys. A 124, 81 (2018)

- N.N. Halder, P. Biswas, S. Kundu, P. Banerji, Sol. Energy Mater. Sol. C 132, 230 (2015)

- 43. B.L. Sharma, Metal-Semicodncutor Schottky Barrier Junctions and Their Applications (Plenum Press, New York, 1984)

- D.K. Schroder, Semiconductor Material and Device Characterization (Wiley, New Jersey, 2005)

- 45. C. Nuhoglu, Y. Gulen, Vacuum **84**, 812 (2010)

- O.F. Yuksel, N. Tugluoglu, H. Safak, M. Kus, J. Appl. Phys. 113, 044507 (2013)

- H.H. Gullu, O. Bayrakli, D.E. Yildiz, M. Parlak, J. Mater. Sci.: Mater. Electron. 28, 17806 (2017)

- 48. B.L. Smith, E.H. Rhoderic, Solid State Electron. 14, 71 (1971)

- 49. X. Zhang, D. Joy, Microsc. Res. Technol. 29, 47 (1994)

- 50. F. Yakuphanoglu, Synth. Met. **157**, 859 (2007)

- O.F. Yuksel, N. Tugluoglu, B. Gulveren, H. Safak, M. Kus, J. Alloy Compd. 577, 30 (2013)

- M. Ozer, D.E. Yildiz, S. Altindal, M.M. Bulbul, Solid State Electron. 51, 941 (2007)

- 53. A. Tataroglu, S. Altindal, J. Alloy Compd. 479, 893 (2009)

- H.H. Gullu, O. Bayrakli Surucu, M. Terlemezoglu, D.E. Yildiz, M. Parlak, J. Mater. Sci.: Mater. Electron. 30, 15371 (2019)

- 55. A. Tataroglu, F.Z. Pur, Phys. Scr. 88, 015801 (2013)

- A. Karabulut, A. Dere, A.G. El-Sehemi, A.A. Al-Ghamdi, F. Yakuphanoglu, J. Electron. Mater. 47, 7159 (2018)

- 57. S.K. Cheung, N.W. Cheungics, Solid State Electron. 49, 85 (1986)

- 58. H. Norde, J. Appl. Phys. **50**, 5052 (1979)

- 59. K. Sato, Yasumura, J. Appl. Phys. **58**, 3655 (1985)

- 60. F. Yakuphanoglu, Sens. Actuators A 141, 383 (2008)

- A. Tataroglu, C. Ahmedova, G. Barim, A.G. Al-Sehemi, A. Karabulut, A.A. Al-Ghamdi, W.A. Farooq, F. Yakuphanoglu, J. Mater. Sci.: Mater. Electron. 29, 12561 (2018)

- 62. F. Yakuphanoglu, Composites B 92, 151 (2016)

- M. Cavas, A.A.M. Farag, Z.A. Alahmed, F. Yakuphanouglu, Electroceramics 31, 298 (2013)

- A.S. Dahlan, A. Tataroglu, A.L. Al-Ghamdi, A.A. Al-Ghamdi, S. Bin-Omran, Y. Al-Turki El-Tantawy, F. Yakuphanoglu, J. Alloy Compd. 646, 1151 (2015)

- A. Dere, M. Soylu, F. Yakuphanoglu, Mater. Sci. Semicond. Proc. 90, 129 (2019)

- 66. P. Chattorpadhyay, Solid State Electron. 36, 605 (1993)

- H.H. Gullu, O. Bayrakli Surucu, M. Terlemezoglu, D.E. Yildiz, M. Parlak, J. Mater. Sci: Mater. Electron. 30, 9814 (2019)

- 68. G. Ersoz, I. Yucedag, Y.A. Kalandaragh, I. Orak, S. Altindal, Trans. Electron Dev. **63**, 2948 (2016)

- H. Tecimer, S.O. Tan, S. Altindal, IEEE Trans. Electron. Dev. 65, 231 (2018)

- I. Tascioglu, S.O. Tan, S. Altindal, J. Mater. Sci.: Mater. Electron. 30, 11536 (2019)

- 71. E.H. Nicollian, J.R. Brews, MOS (Metal Oxide–Semiconductor) Physics and Technology (Wiley, New York, 1982)

- 72. H.C. Card, E.H. Rhoderick, J. Phys. D 4, 1589 (1971)

- 73. D.E. Yildiz, S. Altindal, Microelectron. Eng. 85, 289 (2008)

- Z. Guo, F. Ambrosio, A. Pasquarello, Appl. Phys. Lett. 109, 062903 (2016)

- 75. W.A. Hill, C.C. Coleman, Solid State Electron. 23, 87 (1980)

- S. Aydin, D.E. Yildiz, H. Kanbur Cavus, R. Sahingoz, Bull. Mater. Sci. 37, 1563 (2014)

- 77. R. Castagne, A. Vapaille, Electron. Lett. 6, 691 (1970)

- N. Tugluoglu, F. Yakuphanoglu, S. Karadeniz, Phys. B 393, 56 (2007)

- 79. J.R. Brews, E.H. Nicollian, Solid State Electron. 27, 963 (1984)

- 80. J. Werner, K.H. Ploog, H.J. Queisser, Phys. Rev. Lett. 57, 80 (1986)

- 81. M.M. Bulbul, S. Altindal, F. Parlakturk, A. Tataroglu, Surf. Interface Anal. 43, 1561 (2011)

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.