# **Extensive electrostatic investigation of workfunction-modulated SOI tunnel FETs**

Subhrasmita Panda $^1$  · Sidhartha Dash $^2$  · Guru Prasad Mishra $^1$

Published online: 4 October 2016 © Springer Science+Business Media New York 2016

Abstract An analytical model for the silicon-on-insulator (SOI) tunnel field-effect transistor (FET) with linearly graded workfunction-modulated gate is proposed to improve device performance through subthreshold slope (SS) optimization. The surface potential of the suggested model is analyzed using the two-dimensional (2-D) Poisson equation with imposed channel boundary conditions. Other electrical parameters such as the electric field, drain current, transconductance, and SS are evaluated to examine the performance of the model. Moreover, the performance in terms of the SS and  $I_{60}$  values for the proposed model with downscaling of gate oxide thickness and silicon body thickness are also investigated and the results compared with results for a conventional tunnel FET (TFET) model. The present model exhibits significant reduction in subthreshold slope ( $\sim 14 \, \text{mV/decade}$ ) and improvement in  $I_{60}$  performance. The accuracy of the model is verified against 2-D technology computer-aided design (TCAD) model simulations.

**Keywords** SOI TFET · Workfunction-modulated gate · Subthreshold slope · Drain current

Guru Prasad Mishra gurumishra@soauniversity.ac.in

- <sup>1</sup> Device Simulation Laboratory, Department of Electronics & Instrumentation Engineering, Siksha 'O' Anusandhan University, Khandagiri, Bhubaneswar, India

- <sup>2</sup> Department of Electronics & Communication Engineering, Institute of Technical Education & Research, Siksha 'O' Anusandhan University, Khandagiri, Bhubaneswar, India

## **1** Introduction

Miniaturization of field-effect transistors enables improved functionality and higher packaging density of electronic devices [1-3]. However, the progressive downscaling of complementary metal-oxide-semiconductor (CMOS) technology places certain restrictions on device performance due to the subthreshold slope (SS) limit of 60 mV/decade for MOSFETs [3–6]. Meanwhile, the growing demand for lowpower devices has attracted attention from many researchers. Recently, the tunnel field-effect transistor (TFET) has emerged as a new device of interest, setting the pace in the semiconductor industry [6-9]. A major concern regarding MOSFETs is that the channel shrinkage frequently applied in TFETs results in short-channel effects (SCEs). The TFET employs a band-to-band tunneling (BTBT) mechanism, which reduces the OFF-state current  $(I_{OFF})$ , and thereby the subthreshold slope (SS) to below 60 mV/decade [6-10]. Also, the SOI TFET exhibits better performance in terms of SCEs due to the presence of a tunneling barrier at the source–channel interface [11]. To improve TFET performance, various techniques such as gate engineering [12,13], material engineering [14–16], and dielectric engineering [17, 18] have been proposed to enable improved gate control over the channel. Research has also been carried out on dual- and triple-material gates, resulting in improved device performance by reducing SCEs [14–16].

Recently, such research has been extended to another level through employment of workfunction engineering of the gate metal, resulting in excellent gate control and immunity to SCEs [19–36]. Improved analog performance and reduced SCEs can be realized by introducing linear variation of the mole fraction in the gate metal  $(A_X B_{1-X})$  from the source to drain end. Continuous workfunction variation of nanowire gate metal has already been reported, and fabricated on a sin-

gle substrate by exploiting various methods [37,38]. In this paper, subthreshold slope minimization is considered as one of the key techniques to achieve the objective of low power consumption. Here, a new binary metal alloy with linearly modulated workfunction is applied as the gate electrode to achieve greater gate controllability for the single-gate SOI tunnel FET. The present model reduces the leakage current, which further helps in reducing the subthreshold slope. Here, the electric field is customized to reduce the asymmetric and uneven nature of the surface potential as well as the draininduced barrier lowering (DIBL) effect, thereby reducing SCEs [25]. The improved initial tunneling distance in OFFstate results in SS below 45 mV/decade for the workfunctionmodulated TFET (WM-TFET). The enhanced scalability of the present model is also investigated, and its accuracy validated using the 2-D TCAD Sentaurus device simulator [39].

#### 2 Physical model and electrostatic analysis

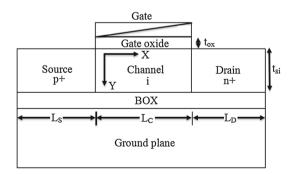

A schematic of the structure of the workfunction-modulated single-gate SOI TFET (WM-TFET) is shown in Fig. 1. The proposed structure is designed with a SOI substrate having channel length  $(L_{\rm C})$  of 40 nm and source/drain length  $(L_{\rm S}/L_{\rm D})$  of 20 nm. The source and drain regions are heavily doped with trivalent and pentavalent impurity concentration  $(p^+/n^+)$  of  $10^{20}$  cm<sup>-3</sup>, respectively. The intrinsic channel region is lightly doped with concentration of N =10<sup>15</sup> cm<sup>-3</sup>. The buried oxide thickness, gate oxide thickness, and silicon body thickness are taken as 2, 2, and 10nm, respectively. The dielectric constant of the silicon and gate oxide are denoted as  $\varepsilon_{Si}$  and  $\varepsilon_{ox}$ , respectively. The present analytical model was developed using a gate metal  $(A_X B_{1-X})$  with spatially modulated workfunction to enhance gate control; the workfunction at the source and drain interface is  $\Phi_{MA} = 4.2 \,\text{eV}$  and  $\Phi_{MB} = 5 \,\text{eV}$ , respectively, while the instantaneous workfunction,  $\Phi_{Mi}(X)$ , of the metal gate contact along the x-axis can be represented as a function of the mole fraction  $(0 \le X \le 1)$  as

**Fig. 1** Schematic cross-sectional view of an *n*-channel workfunctionmodulated TFET (WM-TFET)

$$\Phi_{\rm Mi}(x) = \Phi_{\rm MA} + \frac{(\Phi_{\rm MB} - \Phi_{\rm MA})}{L_{\rm c}} x.$$

(1)

This variation of the workfunction along the *x*-axis is formulated based on the assumption that the two pure metals (A and B) have equivalent density of states [20–22]. The potential profile ( $\Phi(x, y)$ ) in the channel region can be expressed in terms of the two-dimensional (2-D) Poisson equation in the rectangular coordinate system as

$$\frac{\partial^2 \Phi(x, y)}{\partial^2 x} + \frac{\partial^2 \Phi(x, y)}{\partial^2 y} = \frac{qN}{\varepsilon_{\rm Si}}.$$

(2)

Here, the effect of fixed and trapped charges on the surface potential is assumed to be negligible. The solution of Eq. 2 can be found by considering a parabolic approximation [6–8], using the required boundary conditions at the respective interfaces:

$$\Phi_{\rm s}\left(x\right)|_{x=0} = V_{\rm bis} \tag{3}$$

$$\Phi_{\rm s}\left(x\right)|_{x=L_{\rm c}} = V_{\rm bid} + V_{\rm DS} \tag{4}$$

$$E(x, y)|_{y=0} = \left(\frac{\Phi_{s}(x) - V_{GS} + V_{FBi}}{t_{ox}}\right) \frac{\varepsilon_{ox}}{\varepsilon_{Si}}$$

(5)

$$E(x, y)|_{y=t_{\rm Si}} = 0,$$

(6)

where  $V_{\text{bis}}$  and  $V_{\text{bid}}$  represent the built-in potentials at the source–channel and channel–drain interface, respectively. The gate–source voltage ( $V_{\text{GS}}$ ) and drain–source voltage ( $V_{\text{DS}}$ ) are applied at the corresponding gate and drain terminal. Moreover, the instantaneous flat-band voltage ( $V_{\text{FBi}}$ ) can be evaluated using the modulated metal workfunction ( $\Phi_{\text{Mi}}$ ) and silicon workfunction ( $\Phi_{\text{Si}}$ ) as

$$V_{\rm FBi} = \Phi_{\rm Mi} - \Phi_{\rm Si}.$$

(7)

The surface potential along the lateral direction can be evaluated using the solution of Eq. 2

$$\Phi_{\rm s}(x) = A_{\rm m} e^{kx} + B_{\rm m} e^{-kx} - \frac{qN}{\varepsilon_{\rm Si}k^2} + V_{\rm GS} - V_{\rm FBi}, \qquad (8)$$

where k is defined as the natural normalized length, expressed as

$$k = \sqrt{\frac{\varepsilon_{\rm ox}}{t_{\rm Si} t_{\rm ox} \varepsilon_{\rm Si}}}.$$

(9)

The coefficients  $A_m$  and  $B_m$  can be evaluated using the boundary conditions in (3) and (4) as

$$A_{\rm m} = \frac{\left(V_{\rm bid} + V_{\rm DS} + \frac{qN}{\varepsilon_{\rm Si}k^2} - V_{\rm GS} + V_{\rm FBi}\right)e^{kL_{\rm c}} - (V_{\rm bis} + \frac{qN}{\varepsilon_{\rm Si}k^2} - V_{\rm GS} + V_{\rm FBi})}{e^{2kL_{\rm c}} - 1}$$

(10)

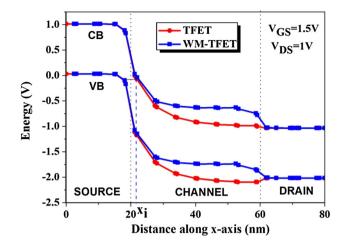

Fig. 2 ON-state energy band diagram of the TFET and WM-TFET models  $% \left( {{{\rm{TFET}}} \right) = 0.025} \right)$

$$B_{\rm m} = \frac{(V_{\rm bis} + \frac{qN}{\varepsilon_{\rm Si}k^2} - V_{\rm GS} + V_{\rm FBi})e^{2kL_{\rm c}} - \left(V_{\rm bid} + V_{\rm DS} + \frac{qN}{\varepsilon_{\rm Si}k^2} - V_{\rm GS} + V_{\rm FBi}\right)e^{kL_{\rm c}}}{e^{2kL_{\rm c}} - 1}.$$

(11)

The electric field along the x-axis has a substantial impact on the driving current capability and subthreshold slope of the device; it is primarily related to the surface potential of the device and can be determined by differentiating the potential w.r.t. the x-axis as

$$E_x(x, y) = -\frac{\partial \Phi_s(x, y)}{\partial x} = k \left( -A_m e^{kx} + B_m e^{-kx} \right).$$

(12)

The drain current of the proposed model can be determined using the tunneling volume in the channel region. In ON-state, charge carriers tunnel from occupied states of the source valence band to unoccupied states of the channel conduction band, thus improving the tunneling volume in the channel. The initial tunneling distance  $(x_i)$  is defined as the shortest distance from the tunneling junction when the source valence band and channel conduction band are lined up [8, 12, 40] as shown in Fig. 2. For lower values of V<sub>GS</sub>, the distance between the source valance band and channel conduction band is high, thus preventing carrier tunneling in OFF-state. As V<sub>GS</sub> is gradually increased, this tunneling distance is progressively reduced, thereby increasing the ONstate current. The initial tunneling distance plays a significant role in determining both the drain current and subthreshold slope of the device. The drain current of the proposed model can be determined by integrating the BTBT generation rate ( $G_{\text{BTBT}}$ ) over a finite volume as

$$I_{\rm D} = q \int A_{\rm c} E_x E_{\rm avg} \exp\left(-\frac{B_{\rm c}}{E_{\rm avg}}\right) \,\mathrm{d}v,\tag{15}$$

where  $E_{\text{avg}} = \frac{E_g}{qx}$  is defined as the average electric field. The magnitude of Kane's tunneling process-dependent parameters  $A_c$  and  $B_c$  are considered as  $9.6615 \times 10^{18} \text{ cm}^{-1} \text{s}^{-1} \text{V}^{-2}$  and  $3 \times 10^7 \text{ V cm}^{-1}$ , respectively [8].

$$I_{\rm D} = q \int_{0}^{t_{\rm Si}} \int_{x_{\rm i}}^{L_{\rm c}} A_{\rm c} E_x \frac{E_{\rm g}}{qx} \exp\left(-\frac{B_{\rm c}q}{E_{\rm g}}x\right) \,\mathrm{d}y \,\mathrm{d}x. \tag{16}$$

Neglecting the minimal effect of the exponential and polynomial terms at the channel–drain interface, the final drain current equation can be formulated as [12]

$$I_{\rm D} = A_{\rm c} k t_{\rm Si} E_{\rm g} \left[ \frac{A_{\rm m}}{\left(k - \frac{B_{\rm c} q}{E_{\rm g}}\right)} E\left(x_{\rm i}\right) - \frac{B_{\rm m}}{\left(k + \frac{B_{\rm c} q}{E_{\rm g}}\right)} F\left(x_{\rm i}\right) \right],\tag{17}$$

where

$$E = \frac{e^{x\left(k - \frac{Dcq}{E_g}\right)}}{x}$$

and  $F = \frac{e^{-x\left(k + \frac{Dcq}{E_g}\right)}}{x}$ . (18)

The subthreshold slope (SS) of a device indicates the sharpness of the transition from OFF- to ON-state. The SS for a device can be determined as the gate voltage change required to achieve a one-decade change in drain current:

$$SS = \left. \left( d \log(I_{\rm D}) / dV_{\rm GS} \right)^{-1} \right|_{V_{\rm DS} = \rm const}.$$

(19)

Similarly, the transconductance  $(g_m)$  of a device is defined as the first-order differential of the drain current w.r.t. the gate voltage for constant drain voltage, i.e.,  $g_m = \frac{\partial I_D}{\partial V_{GS}}\Big|_{V_{DS}=\text{const}}$ . Both of these factors, i.e.,  $g_m$  and SS, provide information about the switching speed of the device. Also, the transconductance generation factor (TGF), which is one of the important figures of merit, can be evaluated as the ratio of the transconductance to drain current for fixed gate voltage

$$\Phi_{s}(x)|_{x=x_{i}} = \Phi_{s}(x)|_{x=0} + \frac{E_{g}}{q}$$

$$x_{i} = \left(\frac{1}{k}\ln\frac{\left(V_{\text{bis}} + \frac{E_{g}}{q} + \frac{qN}{\varepsilon_{\text{Si}}k^{2}} - V_{\text{GS}} + V_{\text{FBi}}\right) + \sqrt{\left(V_{\text{bis}} + \frac{E_{g}}{q} + \frac{qN}{\varepsilon_{\text{Si}}k^{2}} - V_{\text{GS}} + V_{\text{FBi}}\right)^{2} - 4A_{\text{m}}B_{\text{m}}}{2A_{\text{m}}}\right).$$

(13)

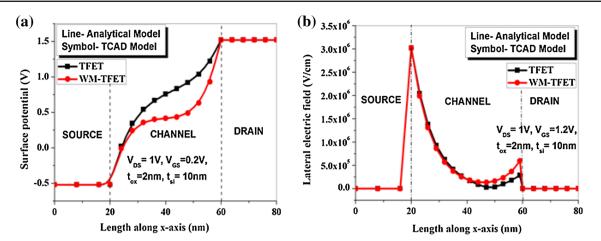

Fig. 3 Comparison of a the surface potential and b lateral electric field variation along the x-axis for both models at constant gate voltage

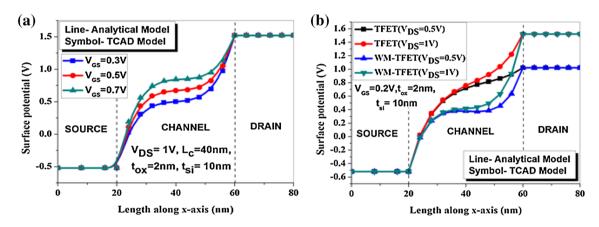

Fig. 4 Surface potential variation along the x-axis for the WM-TFET model with different values of a gate voltage and b drain voltage

and drain voltage, i.e.,  $TGF = g_m/I_D$ . The gain of the device per unit power dissipation can also be determined from the TGF [9].

#### **3** Results and discussion

The accuracy of the presented analytical model was corroborated using the 2-D TCAD Synopsis Sentaurus device simulator. The carrier transport phenomenon in the model was analyzed using Kane's nonlocal BTBT model [8]. Several other models, such as the Shockley–Read–Hall (SRH) recombination model, bandgap-narrowing model, and electron-barrier tunneling model, were also considered. Here, doping-dependent mobility models and high-field saturation models were also used to explore the driving capability of the present model. The results for the proposed model are compared with results for a conventional TFET with gate metal workfunction of 4.2 eV.

Considering the effect of the workfunction modulation, the variation of the surface potential and absolute lateral electric field for the present model are illustrated in Fig. 3a and b, respectively. The significant impact of the spatially modulated metal alloy is evident from the surface potential characteristics in the channel region, thus affecting the gate control capability. However, for the present model, the surface potential remains unchanged in the source and drain regions, as for the conventional TFET. Similarly, the lateral electric field (Fig. 3b) shows equivalent values in the source and drain region, whereas it varies marginally in the channel region due to the impact of the workfunction variation. The lateral electric field is one of the important parameters for calculation of the drain current.

The surface potential variation for the WM-TFET model with different gate voltages is illustrated in Fig. 4a. It is clearly evident that, with increasing gate voltage, the gate control over the channel increases, thereby increasing the surface potential. The increased slope of the surface potential results in reduced tunneling distance in ON-state, thus improving the drain current at higher gate voltage. Figure 4b shows the influence of the drain voltage on the surface potential distribution for both models. The impact is significant at the channel–drain interface. Figure 4b reveals the reduced drain-induced barrier lowering (DIBL) effect, as the slope

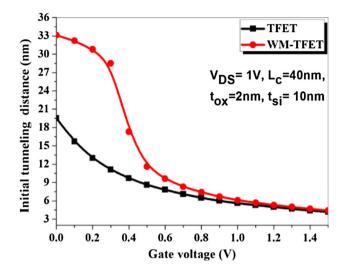

**Fig. 5** Variation of the initial tunneling distance for both models w.r.t. gate voltage

of the surface potential is unaffected by change in the drain voltage.

Figure 5 displays the variation in the initial tunneling distance for the WM-TFET model with respect to gate voltage at constant  $V_{DS}$ , compared with the conventional TFET model. The present model exhibits higher initial tunneling distance in OFF-state, resulting from the spatially modulated workfunction, and thus significantly reduced OFF-current and SS. On the other hand, the proposed model provides marginally higher initial tunneling distance in ON-state compared with the conventional TFET, thus exhibiting poor ON-current performance.

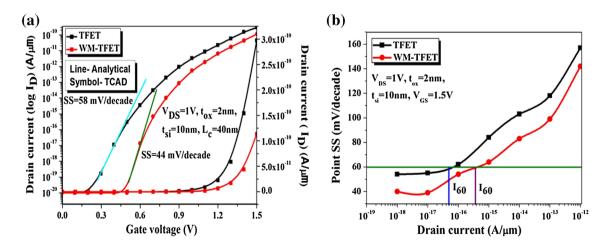

The average and point SS for both models are illustrated in Fig. 6a, b. The transfer characteristic for both models is shown on linear and logarithmic scales in Fig. 6a. It is evident that the conventional TFET model provides higher ON-current compared with the WM-TFET. On the other hand, the proposed model exhibits steeper subthreshold slope as a result of the workfunction modulation of the linearly graded metal alloy. The model shows significantly reduced average SS compared with the basic model. In Fig. 6b, the point SS is plotted with respect to drain current for both models.  $I_{60}$  is one of the figures of merit, determining the maximum drain current for SS = 60 mV/decade [41]. The drain current  $I_{60}$  was evaluated for the proposed model to investigate the impact of the workfunction modulation. The present model exhibits higher  $I_{60}$  (~ 1 decade) compared with the TFET model.

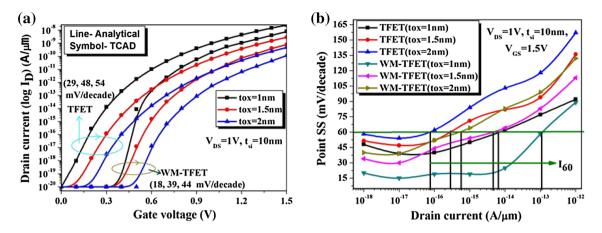

Figure 7a shows the  $I_{\rm D} - V_{\rm GS}$  characteristics for both models for different gate oxide thickness  $(t_{\rm ox})$  values and the resulting average SS. Each reduction in  $t_{\rm ox}$  leads to an increase in the drain current for both models. However, the WM-TFET model exhibits steeper SS for each gate oxide thickness due to the enhanced control of the linearly modulated gate over the channel. Similarly, Fig. 7b indicates the effect of gate oxide scaling on  $I_{60}$  for both models. It is evident that the  $I_{60}$  value for the present model is improved as the gate oxide thickness is reduced, as for the TFET model.

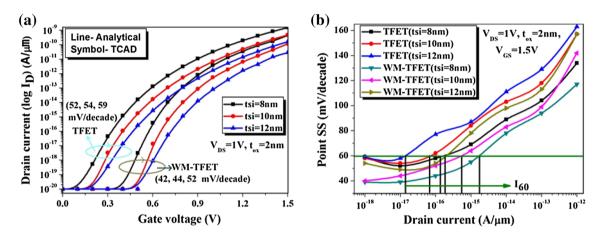

The  $I_D - V_{GS}$  characteristics of both the TFET and WM-TFET models for different silicon body thickness ( $t_{Si}$ ) values along with the average SS are illustrated in Fig. 8a. The average SS is reduced further with reduction in  $t_{Si}$  for the WM-TFET model compared with the conventional TFET model, revealing the impact of the workfunction modulation on the channel. Thus, downscaling of the body thickness results in higher drain current performance and low power consumption (low OFF-current and SS) for the present model, as for the TFET model. Figure 8b shows the variation of the point SS for both models w.r.t. drain current for different values of silicon body thickness. The impact of the spatial modulation of the metal alloy workfunction is evident in Fig. 8b, with improved  $I_{60}$  as  $t_{Si}$  is reduced.

Fig. 6 a Drain current as function of gate voltage, and b variation of the point SS w.r.t. drain current for constant gate voltage and drain voltage

Fig. 7 a Drain current (log I<sub>D</sub>) as a function of gate voltage. b Point SS as a function of drain current for different gate oxide thicknesses

Fig. 8 a Drain current (log  $I_D$ ) as a function of gate voltage, and **b** point SS as a function of drain current for different silicon body thicknesses

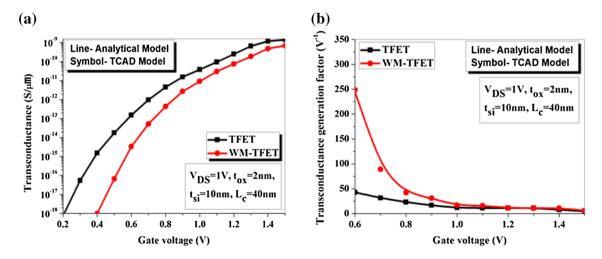

Fig. 9 a Variation of transconductance (log  $g_m$ ) and b TGF w.r.t. gate voltage for both models at  $V_{DS} = 1 \text{ V}$

Figure 9a and b illustrate the transconductance and TGF for both models as functions of gate voltage. For constant drain voltage, the transconductance of the conventional TFET model is higher compared with the present model due to the marginal difference in drain current behavior between the models, indicating a lower amplification capability for the present model. The unit power dissipation gain factor TGF for both device models is shown in Fig. 9b. The TGF gain factor is quite high for the proposed model at low gate voltage, due to the steep slope of the transfer characteristics. This is a result of the introduction of the linearly graded gate in the TFET.

### **4** Conclusions

The performance in terms of various electrical parameters such as the surface potential, electric field, initial tunneling distance, drain current, average SS,  $I_{60}$ , transconductance, and unit gain TGF is investigated for the WM-TFET model. Prominently improved efficiency is exhibited by the present model compared with the conventional TFET, with significantly improved  $I_{60}$  and reduced average SS (~ 14 mV/decade). Also, the effect of downscaling the gate oxide and silicon body thicknesses on the variation of the average and point SS of the WM-TFET is investigated. This model represents one potential solution for ultralow-power applications due to its low OFF-current and steeper SS.

#### Compliance with ethical standards

Conflict of interest There is no conflict of interest.

#### References

- Shin, S., Jang, E., Jeong, J.W., Park, B.G., Kim, K.R.: Compact design of low power standard ternary inverter based on OFF-state current mechanism using nano-CMOS technology. IEEE Trans. Electron Devices 62, 2396–2403 (2015)

- Kumar, S., Raj, B.: Compact channel potential analytical modeling of DG-TFET based on evanescent-mode approach. J. Comput. Electron. 14, 820–827 (2015)

- Datta, S., Liu, H., Narayanan, V.: Tunnel FET technology: a reliability perspective. Solid State Electron. 54, 861–874 (2014)

- Zhang, Q., Zhao, W., Seabaugh, A.: Low subthreshold-swing tunnel transistors. IEEE Electron Devices Lett. 27, 297–300 (2006)

- Samuel, T.S.A., Balamurugan, N.B., Bhuvaneswari, S., Sharmila, D., Padmapriya, K.: Analytical modelling and simulation of singlegate SOI TFET for low-power applications. Int. J. Electron. 101, 779–788 (2014)

- Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling fieldeffect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Devices Lett. 28, 743–745 (2007)

- Lee, M.J., Choi, W.Y.: Analytical model of single-gate silicon-oninsulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electron. 63, 110–114 (2011)

- Kumari, P., Dash, S., Mishra, G.P.: Impact of technology scaling on analog and RF performance of SOI-TFET. Adv. Nat. Sci. Nanosci. Nanotechnol. 6, 045005-1–045005-10 (2015)

- Dash, S., Mishra, G.P.: A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). Superlattices Microstruct. 86, 211–220 (2015)

- Narang, R., Saxena, M., Gupta, R.S., Gupta, M.: Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans. Nanotechnol. 12, 951–957 (2013)

- Vandenberghe, W.G., Verhulst, A.S., Groeseneken, G., Soree, B., Magnus, W.: Analytical model for a tunnel field-effect transistor. Proceedings of IEEE Mediterranean Conference on Electrotechnical Conference, pp. 923–928 (2008)

- Dash, S., Mishra, G.P.: A 2D analytical cylindrical gate tunnel FET (CG-TFET) model: impact of shortest tunneling distance. Adv. Nat. Sci. Nanosci. Nanotechnol. 6, 035005-1–035005-10 (2015)

- Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for doublegate tunnel FETs. IEEE Trans. Electron Devices 61, 1494–1500 (2014)

- Bagga, N., Sarkar, S.K.: An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans. Electron Devices 62, 2136–2142 (2015)

- Baral, B., Das, A.K., De, D., Sarkar, A.: An analytical model of triple-material double-gate metal-oxide-semiconductor field-effect transistor to suppress short-channel effects. Int. J. Numer. Model. 29, 47–62 (2016)

- Pandey, P., Vishnoi, R., Kumar, M.J.: A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J. Comput. Electron. 14, 280–287 (2015)

- Boucart, K., Ionescu, A.M.: Double gate tunnel FET with highk gate dielectric. IEEE Trans. Electron Devices 54, 1725–1733 (2007)

- Choi, W.Y., Lee, W.: Hetero-gate-dielectric tunneling field effect transistors. IEEE Trans. Electron Devices 57, 2317–2319 (2010)

- Ishii, R., Matsumura, K., Sakai, A., Sakata, T.: Work function of binary alloys. Appl. Surf. Sci. 169–170, 658–661 (2001)

- Sarkhel, S., Sarkar, S.K.: A comprehensive two dimensional analytical study of a nanoscale linearly graded binary metal alloy gate cylindrical junctionless MOSFET for improved short channel performance. J. Comput. Electron. 13, 925–932 (2014)

- Dash, S., Sahoo, G.S., Mishra, G.P.: Subthreshold swing minimization of cylindrical tunnel FET using binary metal alloy gate. Superlattices Microstruct. 91, 105–111 (2016)

- Misra, V., Zhong, H., Lazar, H.: Electrical properties of Ru-based alloy gate electrodes for dual metal gate Si-CMOS. IEEE Trans. Electron Devices 23, 354–356 (2002)

- Li, T.L., Hu, C.H., Ho, W.L., Wang, H.C.H., Chang, C.Y.: Continuous and precise work function adjustment for integratable dual metal gate CMOS technology using Hf-Mo binary alloys. IEEE Trans. Electron Devices 52, 1172–1179 (2005)

- Lee, Y., Nam, H., Park, J.D., Shin, C.: Study of work-function variation for high-κ/metal-gate Ge-source tunnel field-effect transistors. IEEE Trans. Electron Devices 62, 2143–2147 (2015)

- Sarkhel, S., Bagga, N., Sarkar, S.K.: Compact 2D modeling and drain current performance analysis of a work function engineered double gate tunnel field effect transistor. J. Comput. Electron. (2015). doi:10.1007/s10825-015-0772-3

- Tsui, B.Y., Huang, C.F.: Wide range work function modulation of binary alloys for MOSFET application. IEEE Trans. Electron Devices 24, 153–155 (2003)

- Choi, K.M., Choi, W.Y.: Work-function variation effects of tunneling field-effect transistors (TFETs). IEEE Electron Devices Lett. 34, 942–944 (2013)

- Todi, R.M., Erickson, M.S., Sundaram, K.B., Barmak, K., Coffey, K.R.: Comparison of the work function of Pt–Ru binary metal alloys extracted from MOS capacitor and schottky-barrier-diode measurements. IEEE Trans. Electron Devices 54, 807–813 (2007)

- Hou, Y.T., Li, M.F., Low, T., Kwong, D.L.: Metal gate work function engineering on gate leakage of MOSFETs. IEEE Trans. Electron Devices 51, 1783–1789 (2004)

- Lee, C.K., Kim, J.Y., Hong, S.N., Zhong, H., Chen, B., Misra, V.: Properties of Ta–Mo alloy gate electrode for *n*-MOSFET. J. Mater. Sci. 40, 2693–2695 (2005)

- Nabatame, T., Nunoshige, Y., Kadoshima, M., Takaba, H., Segawa, K., Kimura, S., Satake, H., Ota, H., Ohishi, T., Toriumi, A.: Changes in effective work function of Hf<sub>x</sub>Ru<sub>1-x</sub> alloy gate electrode. Microelectron. Eng. **85**, 1524–1528 (2008)

- Lin, R., Lu, Q., Ranade, P., King, T.J., Hu, C.: An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Devices Lett. 23, 49–51 (2002)

- Singanamalla, R., Yu, H.Y., Daele, B.V., Kubicek, S., Meyer, K.D.: Effective work-function modulation by aluminum-ion implantation for metal-gate technology (poly-Si/TiN/SiO<sub>2</sub>). IEEE Electron Device Lett. 28, 1089–1091 (2007)

- Lin, C.S., Yeh, R.H., Li, I.X., Hong, J.W.: Electrical characteristics of a-SiGe: H thin-film transistors with Sb/Al binary alloy Schottky source/drain contact. Solid-State Electron. 47, 1787–1791 (2003)

- Kai, H., Xueli, M., Hong, Y., Wenwu, W.: Modulation of the effective work function of TiN metal gate for PMOS application. J. Semicond. 34, 086002-1–086002-4 (2013)

- Lee, K.C., Fan, M.L., Su, P.: Investigation and comparison of analog figures-of-merit for TFET and FinFET considering workfunction variation. Microelectron. Reliab. 55, 332–336 (2015)

- Christen, H.M., Rouleau, C.M., Ohkubo, I., Zhai, H.Y., Lee, H.N., Sathyamurthy, S., Lowndes, D.H.: An improved continuous compositional-spread technique based on pulsed-laser deposition and applicable to large substrate areas. Rev. Sci. Instrum. 74, 4058– 4062 (2003)

- Ohkubo, I., Christen, H.M., Khalifah, P., Sathyamurthy, S., Zhai, H.Y., Rouleau, C.M., Mandrus, D.G., Lowndes, D.H.: Continuous composition-spread thin films of transition metal oxides by pulsed laser deposition. Appl. Surf. Sci. 223, 35–38 (2004)

- Sentaurus Device User Guide. Synopsys, Inc., Mountain View (2010)

- Panda, S., Dash, S., Behera, S.K., Mishra, G.P.: Delta-doped tunnel FET (D-TFET) to improve current ratio (*ION/IOFF*) and ONcurrent performance. J. Comput. Electron. (2016). doi:10.1007/ s10825-016-0860-z

- Vandenberghe, W.G., Verhulst, A.S., Soree, B., Magnus, W., Groeseneken, G., Smets, Q., Heyns, M., Fischetti, M.V.: Figure of merit for and identification of sub-60 mV/decade devices. Appl. Phys. Lett. 102, 013510-1–013510-4 (2013)