RESEARCH

# A verified durable transactional mutex lock for persistent x86-TSO

Eleni Vafeiadi Bila<sup>1,2</sup> · Brijesh Dongol<sup>1</sup>

Received: 5 November 2023 / Accepted: 19 July 2024 © The Author(s) 2024

# Abstract

The advent of non-volatile memory technologies has spurred intensive research interest in correctness and programmability. This paper addresses both by developing and verifying a durable (aka persistent) transactional memory (TM) algorithm,  $dTML_{Px86}$ . Correctness of  $dTML_{Px86}$  is judged in terms of *durable opacity*, which ensures both *failure atomicity* (ensuring memory consistency after a crash) and *opacity* (ensuring thread safety). We assume a realistic execution model, Px86, which represents Intel's persistent memory model and extends the *Total Store Order* memory model with instructions that control persistency. Our TM algorithm,  $dTML_{Px86}$ , is an adaptation of an existing software transactional mutex lock, but with additional synchronisation mechanisms to cope with Px86. Our correctness proof is operational and comprises two distinct types of proofs: (1) proofs of invariants of dTML<sub>Px86</sub> and (2) a proof of refinement against an operational specification that guarantees durable opacity. To achieve (1), we build on recent Owicki–Gries logics for Px86, and for (2) we use a simulation-based proofs for Px86 programs. Our entire development has been mechanised in the Isabelle/HOL proof assistant.

**Keywords** Persistent memory · Transactional memory · Verification · Refinement · Isabelle/HOL

# **1** Introduction

Non-volatile memory (NVM) technologies, e.g., Intel Optane, enable byte-addressable accesses as allowed by DRAM, while retaining the benefits of persistent storage. NVM has the potential to radically impact future systems since they can be designed to efficiently *recover* from a system-wide crash. However, NVM also introduces new programming challenges and requires previous notions of correctness to be reconsidered. Such challenges are particularly acute for concurrent programs, where one additionally has to understand inter-

- <sup>1</sup> University of Surrey, Guildford, UK

- <sup>2</sup> Arm Ltd, Cambridge, UK

Brijesh Dongol b.dongol@surrey.ac.uk

Eleni Vafeiadi Bila eleni.vafeiadibila@arm.com

actions between *persistency* (concerning the order in which memory updates are persisted) and *weak memory consistency* (concerning the order in which memory updates in one thread become visible to other threads).

There has been widespread interest on NVM, with several works characterising their semantics in the context of *hardware* weak memory models [12, 57, 59, 60]. Alongside these low-level semantics, a separate line of work has focussed on adapting correctness conditions such as *linearisability* [34] and *opacity* [33], obtaining corresponding conditions such as *durable linearisability* [38] and *durable opacity* [5]. Such conditions provide a basis for developing high-level synchronisation mechanisms such as concurrent objects, in the case of (durable) linearisability, and transactional memory, in the case of (durable) opacity.

Our work brings these two lines of work together in the context of *recoverable concurrent transactional memory* [14, 39, 41, 47]. In particular, we develop dTML<sub>Px86</sub>, which is an adaptation of the *durable* Transactional Mutex Lock (dTML) algorithm [5], which is itself a durable extension of the Transactional Mutex Lock [15] with logging mechanisms that support recoverability. The dTML algorithm has been designed for a strong memory model (PSC) [44], which extends sequential consistency (SC) [48] with persistency. However, PSC is a strong memory model that is unrealistic for modern architectures (e.g., Intel), which only provide weak memory guarantees.

#### 1.1 Designing, modelling and verifying dTML<sub>Px86</sub>

Unlike prior works, as the name implies,  $dTML_{Px86}$  assumes Intel's x86 persistency and consistency model (Px86) [37], which extends the x86 Total Store Order (TSO) model [64] with a persistency semantics [12, 44, 57, 59, 60]. Here, like in TSO, each write is first cached in a local *FIFO store buffer* (and only visible to the writing thread), then later propagated to the volatile shared memory (whereby it becomes visible to other threads). Writes in the volatile shared memory are later *persisted* by propagating them to NVM.

In Px86, the order in which writes become persistent may differ from the order in which they were issued. To address this, Px86 provides instructions, e.g., **flush**, **flush**<sub>opt</sub>, that explicitly flush locations<sup>1</sup> to NVM, ensuring that the corresponding locations are persisted. The **flush** instruction flushes a location line in a synchronous manner, blocking the executing thread until the prior write has been persisted. The *optimised flush* instruction (**flush**<sub>opt</sub>) flushes a single location but in an asynchronous manner (without blocking the execution of the corresponding thread). The **flush**<sub>opt</sub> instruction is not ordered with respect to any following write, **flush**<sub>opt</sub>, or **flush** (when applied to an address in a different location) instructions [57, Fig. 3], and only serves to *tag* locations that are to be persisted later. As a result, the execution of a **flush**<sub>opt</sub> on an address x, does not provide any guarantees about the value of x in persistent memory. To restrict the additional weak behaviors that **flush**<sub>opt</sub> introduces, Px86 provides a *store fence* (**sfence**) instruction that orders store instructions with **flush**<sub>opt</sub>. The **flush**<sub>opt</sub> instruction is guaranteed to take effect (the contents of the given location reach the persistent memory) when a following **sfence** instruction is executed.

$dTML_{Px86}$  is designed to make use of  $flush_{opt}$  instructions for efficiency. However, this introduces new verification challenges. Namely,  $flush_{opt}$  instructions are difficult to reason about and, in fact, some earlier logics [58] only provided partial support for  $flush_{opt}$  instructions, requiring a program with  $flush_{opt}$  instructions to be transformed into a program with

<sup>&</sup>lt;sup>1</sup> Instructions such as **flush**, **flush**<sub>opt</sub> and **sfence** actually apply to cache lines instead of locations. However, as in [8], for brevity we make the assumption that each cache line only holds one location, eliminating the need to reason about other locations on the same cache line.

**flush** instructions only. This transformation technique was known to be incomplete [58]. Full support for **flush**<sub>opt</sub> was only provided after development of the view-based semantics of Px86 (which we call Px86<sub>*view*</sub>) [12] and a corresponding Owicki–Gries logic [8]. Our proofs for dTML<sub>Px86</sub> represent the first large-scale proofs of correctness for a realistic program that uses **flush**<sub>opt</sub> instructions.

We aim to achieve full operational proofs of correctness, therefore we build on the aforementioned  $Px86_{view}$  semantics [12] and Owicki–Gries logic [8]. However, using this logic directly in our current work is not possible for two reasons.

- Like prior works on verifying Px86 programs [12, 58], Bila et al. [8] have only focussed on reasoning about the behaviour *upto the first crash* of the program. To fully establish correctness of dTML<sub>Px86</sub>, it is critical to also reason about the program after restarting the system.

- (2) The assertions of PIEROGI defined by Bila et al. [8] are inadequate for reasoning about certain phenomena that occur in dTML<sub>Px86</sub>. In particular, we must often reason about memory patterns by considering the order in which writes occur.

One of our contributions is an extension of the view-based semantics [12] as well as the associated logic [8] to enable reasoning about program recovery (after a crash), as well as new assertions that enable reasoning about the last writes to a location.

Our correctness proof of  $dTML_{Px86}$  uses *forward simulation* to establish a refinement with respect to an abstract operational specification (called dTMS2 [5]). This, to our knowledge, is the first operational proof of refinement for the Px86. Other works have used refinement to verify durable linearisability directly under the *declarative* Px86 model [24, 56]. Unlike our work, these prior works are not accompanied by any mechanisation. Dalvandi and Dongol [16] have considered operational refinement proofs of transactional memory algorithms under the RC11 memory model with full mechanisation in Isabelle/HOL. These proofs have a different set of complexities (due to relaxed and release-acquire accesses), but do not require consideration of durability or recovery as we do in dTML<sub>Px86</sub>.

#### **1.2 Contributions**

This paper comprises the following main contributions.

- (1) We develop a durable transactional memory dTML<sub>Px86</sub> that guarantees durable opacity under Px86<sub>view</sub> (and hence Px86). As mentioned above, dTML<sub>Px86</sub> makes use of **flush**<sub>opt</sub> instructions for improved efficiency, which increases the verification challenge.

- (2) We develop a extension of the Px86<sub>view</sub> semantics to enable operational reasoning about the behaviour of program *after* a crash, i.e., the recovery and subsequent execution. This is coupled with an extended Owicki–Gries logic that is also capable of reasoning about recovery steps.

- (3) To take advantage of our operational reasoning technique, we apply a simulation-based proof to show correctness of  $dTML_{Px86}$  by refinement. The proof proceeds via a long-established technique of establishing a forward simulation between the implementation and an abstract specification [5, 18, 22]. In the context of transactional memory, we prove that  $dTML_{Px86}$  is a refinement of an operational model, dTMS2 [5], whose traces are guaranteed to be durably opaque.

- (4) We mechanise our entire development in Isabelle/HOL, ranging from the semantics, logic (including soundness of the atomic Hoare triples), and all proofs pertaining to dTML<sub>Px86</sub>, including proofs of the invariant and simulation.

# 1.3 Supplementary material

The Isabelle/HOL development accompanying this paper is available at [7].

# 1.4 Overview

This paper is organised as follows. In Sect. refsec:motivation, we provide some background and further motivation for our work, and in Sect. 3, we recap durable opacity as well as an operational model that guarantees durable opacity. In Sect. 4, we present a view-based operational model for Px86, including our extensions that model recovery after a crash. We present our extended dTML<sub>Px86</sub> algorithm in Sect. 5. We present the Owicki–Gries proof technique (further extended to cope with recovery) and the invariants of dTML<sub>Px86</sub> in Sect. 6. In Sect. 7 we present the durable opacity proof of dTML<sub>Px86</sub> and in Sect. 8 we discuss related work.

# 2 Background and motivation

In this section, we provide some basic high-level background and general motivation for our work.

# 2.1 Px86 semantics

To illustrate the behaviours of different persistent memory instructions, we use three examples (see Fig. 1) by Raad et al. [59], which demonstrate the behaviour of **flush**<sub>opt</sub> instructions. The assertion at the end of each program (indicated by  $\frac{1}{2}$ ) expresses *persistent invariant* [8], i.e., the persistent memory state if the corresponding program crashes.

The program in Fig. 1a first writes the value 1 to location x, then issues an optimised flush instruction to x. Finally, it writes the value 1 to location y. During its execution, both values 0 and 1 possible values for both locations x and y in the persistent memory. This is because **flush**<sub>opt</sub> x by itself does not guarantee that x is persisted before **store** y 1 is executed. In fact, after executing **store** y 1, it may be the case that y may be set to 1 in persistent memory *before* x is set to 1.

To prevent potential reorderings between optimised flushes and later instructions, one can use the **sfence** (store fence) instruction as mentioned above. Other options would be using (RMW) instructions such as a compare-and-swap (CAS) or fetch-and-add (FAA). As illustrated in Fig. 1b adding an **sfence** instruction before **store** y 1 prevents the **flush**<sub>opt</sub> x from being reordered after it. Thus, if the persistent value of y is 1, then **store** y 1 must have been executed, and hence **sfence** must have also been executed, which means that the persistent value of x is 1.

The program in Fig. 1c constitutes a message passing example. As in TSO, loading the value 1 for y (stored in register r) in the second thread, indicates that the store of value 1 at y from the first thread has been already evicted from its local store buffer. Since the store of value 1 to x precedes the store to y in the first thread, this means that the write to x has also been evicted from the first thread's store buffer and therefore is visible to the second thread. The **flush**<sub>opt</sub> x instruction in the second thread cannot be reordered before the preceding load. Hence, when the **flush**<sub>opt</sub> x is executed, the value of x seen by the second thread must be 1. Moreover, after the **sfence** is executed, we can be sure that the value of x in persistent

| store              | opt $x$ ; | store $x$ 1;<br>flush <sub>opt</sub> $x$ ;<br>sfence;<br>store $y$ 1;<br>(b) | <b>store</b> x 1;<br><b>store</b> y 1;  | $\begin{vmatrix} r := \mathbf{load} y; \\ \mathbf{if} (r=1) \\ \mathbf{flush}_{opt} x; \\ \mathbf{sfence}; \\ \mathbf{store} z 1; \\ \mathbf{c}) \end{vmatrix}$ |  |

|--------------------|-----------|------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\oint : x, y \in$ | $\{0,1\}$ | $\not{z} \colon y{=}1 \Rightarrow x{=}1$                                     | $\not z \colon z{=}1 \Rightarrow x{=}1$ |                                                                                                                                                                 |  |

**Fig. 1** Example Px86 programs by Raad et al. [59] where the assertion  $\frac{1}{2}$  defines the possible persisted values during the execution. In all examples *x*, *y*, *z* are distinct locations with initial value 0, and *r* is a (thread-local) register.

memory is 1. Thus, if the persistent value of z is 1 (meaning that the store to z has been executed), then the persistent value of x is also 1.

### 2.2 Implementation challenges under Px86

*Transactional memory* (TM) aims to simplify concurrent programming by executing operations (loads, stores) within a transaction with an *illusion of atomicity*. That is, all changes to data inside a transaction are performed as if they were a single operation. Transactions also execute in an all-or-nothing manner—either all operations occur (i.e., the corresponding transaction *commits*), or none occur (i.e., the corresponding transaction *aborts*). We aim to develop a TM algorithm that ensures *durable opacity* [5], which we discuss in §3.

There are two main challenges when developing durable TM algorithms under weak memory models such as Px86.

- (1) The first challenge concerns thread synchronisation. In a weak memory context, a read of a shared location may return a stale value, i.e., a value that is not the location's last written value. To address this, we must use instructions with strong ordering guarantees (e.g., CAS) at key points within dTML<sub>Px86</sub> to prevent transactions from reading stale values.

- (2) The second challenge concerns *durability*. Without correct placement of explicit flush instructions and the careful design of a recovery mechanism, there is no guarantee of correctness after a system crash. To tackle this, we must strategically position **flush**<sub>opt</sub> and **sfence** instructions in a way that does not compromise the algorithm's efficiency. We must also design a recovery process that enables the state to be reset to a consistent state after a crash.

# 3 Durable opacity

Opacity has been extensively covered in the literature [2, 3, 17, 21, 33, 49], while the formal definition of durable opacity may be found in [5, 6]. We provide these formal definitions in Sect. C, and explain the key concepts here through example (Sect. 3.1). Formally, we only require an operational characterisation of durable opacity called dTMS2 [5, 6], which we present as an input/output automaton in Sect. 3.2. dTMS2 has been used in prior proofs of durable opacity [5, 6, 23] including recent model checking encodings under Px86 [61].

Note that in this paper, for simplicity, we conflate threads and transactions, i.e., each thread is assumed to execute at most one transaction. This restriction can easily be lifted, but at the cost of additional notational overhead [16], whereby we explicitly track the transaction executed by each thread in a special state variable. In the following sections, we often use the terms *thread* and *transaction* interchangeably.

#### 3.1 Opacity and durable opacity

The discussion and example below is adapted from our earlier work [23].

Correctness conditions for TM are defined in terms of *histories* of externally visible events, which are the external calls (invocations) and returns (responses) of TM operations. Typically, we have a pair of events for operations TMBegin, TMRead, TMWrite and TMCommit, noting that an operation call may return with an abort.

A *concurrent history* comprises an interleaving of (external) events from the different operations executed by different transactions. Each history is assumed to be *well formed*, i.e., the history, when restricted to a single transaction starts with a TMBegin, possibly followed by a number of TMRead and TMWrite operations, possibly followed by a TMCommit operation (see Fig. 2). Moreover, each operation executed by a transaction must have responded before the next operation is invoked.

A transaction is *complete* in a history if it has responded with TMCommit(ok) or an abort event, and once completed, the transaction must not execute any further operations. However, a transaction within a history may not be complete, i.e., may be a *live* transaction.

TM implementations are typically designed to be *serialisable*, i.e., there is a total order of *committed transactions* that is consistent with a sequential history. The TM implementations of interest in this paper in fact guarantee *strict serialisability*, which means that the total order of operations must additionally respect the real-time order, i.e., if transaction  $t_1$ commits before transaction  $t_2$  starts, then  $t_1$  must serialise before  $t_2$ . Concurrent (i.e., overlapping) transactions may, however, be serialised in any order. TM implementations also typically provide a semantics for live and aborted transactions. A well-studied condition here is *opacity* [33], which ensures that there exists a total order across *all* transactions so that the committed transactions are strictly serialised and the aborted transactions are consistent with the serialisation order.

While the above provides semantics for transaction consistency, under NVM, we also require a further guarantee of *failure atomicity*. To this end, we follow the notion of *durable opacity* [5], where all transactions committed before a crash are persistent (after the crash), and in addition, the effects of any partially executed transactions are generally not visible after the crash. This concept is similar to that of durable linearisability [38], for concurrent objects.

A *durable concurrent history* is a concurrent history interleaved with crash events. A durable concurrent history is *well formed* iff the history with crash events removed is well formed and, moreover, no transaction that started before the crash continues executing after the crash.

*Durable opacity*, defined over durable concurrent histories, simply requires that the given history is opaque after all crash events are removed. Note that this means that any live transactions before a crash are aborted, and the writes of any committed transactions are persisted, i.e., are not lost after crash.

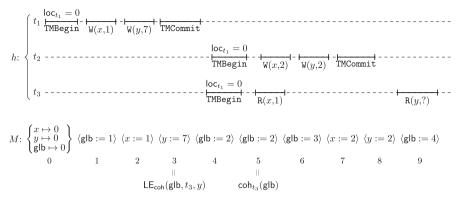

**Example 1** (Dongol and Le-Papin [23]) Consider the history given below, where we elide the response events as well as the TMBegin / TMCommit operations, focussing instead on the

allowable order of the transactions  $t_1$ - $t_9$ . We use  $R_i \ x \ v$  to denote a completed read operation by transaction  $t_i$  on variable x returning value v. (Similarly  $W_i \ x \ v$ .) We use  $R_i \ x \ to$  denote a TMRead operation that has been invoked by  $t_i$  but not returned. All transactions except for transactions  $t_4$  and  $t_5$  are committed. Transaction  $t_4$  is a live transaction that is interrupted by a crash, and transaction  $t_5$  is an aborted complete transaction.

To show that the history above is durably opaque, we must remove the crash events, and show that the remaining history is opaque. Here, we must find a total order among *all* (including live and aborted) transactions so that the values returned by the read operations are consistent with the memory semantics w.r.t. the committed transactions. This total order must respect the real-time order of transactions, e.g.,  $t_1$  and  $t_2$  may not be reordered. Assuming all variables are initialised to 0, an ordering that satisfies these constraints is:  $t_5 \prec t_1 \prec t_3 \prec t_2 \prec t_4 \prec t_6 \prec t_7 \prec t_8$ . Other orders are possible, however, for example,  $t_1$  cannot occur before  $t_5$  even though  $t_5$  aborts (if it did,  $R_5$  y 0 would be inconsistent with the memory semantics).

One caveat of durable opacity pertains to transactions that have already invoked (but not returned from) TMCommit when a crash occurs. When removing crash events from the history, such transactions may either be treated as a committed transaction, or a live (and hence aborted) transaction [5].

**Example 2** Consider the history given below, which comprises committed transactions  $t_1$  and  $t_5$  and live transactions  $t_2$ ,  $t_3$  and  $t_4$  that are interrupted by a crash. We assume that both  $t_2$  and  $t_3$  have started committing when crash occurs, but  $t_3$  has not.

The history is durably opaque, e.g.,  $t_1 \prec t_2 \prec t_3 \prec t_4 \prec t_5$  is a valid total order, where we treat  $t_2$  as an aborted transaction, but  $t_3$  as a committed transaction. Transaction  $t_4$  can only be considered as a live (and hence aborted) transaction.

#### 3.2 The dTMS2 operational specification

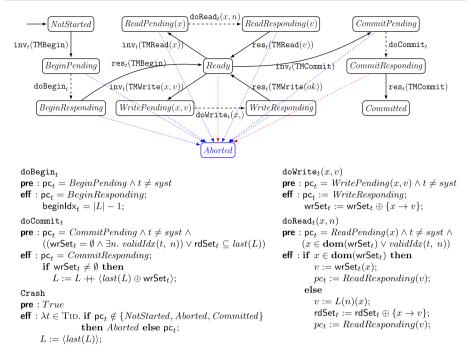

While Sect. 3.1 provides a pedagogical overview of durable opacity, the formal aspects needed for this paper are provided by an operational specification, dTMS2 [5]. dTMS2 extends the TMS2 operational model [20] with a crash-recovery operation (Crash). The transitions of dTMS2 are given in Fig. 2. TMS2 has been shown to imply opacity [50], while dTMS2 has been shown to imply *durable opacity* [5]. Thus every history of dTMS2 is guaranteed to be durably opaque. Later in Sect. 6, we will show that dTML<sub>Px86</sub> is a refinement of dTMS2, and hence also guaranteed to satisfy durable opacity.

The memory of dTMS2 is modelled as a sequence of mappings from locations to values  $L \in (LOC \rightarrow VAL)^*$ . We refer to each such mapping as a memory snapshot. Interestingly,

**Fig.2** Transitions of dTMS2 for a transaction *t*, where *validIdx*(*t*, *n*) = beginldx<sub>*t*</sub>  $\leq n < |L| \land rdSet_t \subseteq L(n)$  and  $\oplus$  denotes a functional override. For example  $f \oplus \{x \to v\} = \lambda y$ . if y = x then *v* else f(y). Blue arrows represent possible transitions for either an abort or crash. Red arrows represent transitions that are possible for a crash only. Dashed arrows (e.g., doBegin<sub>t</sub>) represent internal transitions.

as in other works on refinement-based proofs of durability [18], there is no need distinguish between volatile and persistent memory state in the abstract specification, and the entire state is considered to be persistent. Like  $dTML_{Px86}$ , dTMS2 supports operations (TMBegin), read (TMRead), write (TMWrite) and commit (TMCommit).

Writing transactions of dTMS2 assume a deferred update policy, i.e., each transaction t maintains a write set (wrSet<sub>t</sub>) that records the values that t has written during its execution (see doWrite<sub>t</sub>(x, v) in Fig.2). The memory is updated by writing back the elements of the wrSet<sub>t</sub> to memory when the transaction commits (TMCommit). In particular, when a writing transaction t commits (see doCommit<sub>t</sub> in Fig.2), t creates a new memory snapshot by applying its write set to final memory in L, then appending the resulting memory snapshot to L.

To ensure read consistency, the reads performed from memory are recorded in a local read set (rdSet<sub>t</sub>) for each transaction t (see the **else** case of doRead<sub>t</sub>(x) in Fig. 2). To judge consistency, the largest memory index is stored in beginldx<sub>t</sub>, recording the earliest memory snapshot against which t can serialise (see doBegin<sub>t</sub> in Fig. 2). A read-only transaction must be validated w.r.t. *some* memory snapshot indexed at or after beginldx<sub>t</sub> (see doRead<sub>t</sub>(x, n) in Fig. 2). Validation only succeeds (see validIdx) against a memory snapshot L(n) if each read in the given read set is consistent with L(n). A read in a writing transaction is similar except that the validity check must be w.r.t. the *last* memory snapshot when the location being read is not in the transaction's write set. If the location being read is in the transaction's write set, then the value in the write set is returned.

$\begin{array}{lll} v, u \in \mathrm{VAL} \triangleq \mathbb{N} & x, y, \ldots \in \mathrm{Loc} & o \in \mathrm{DOBJ} & f \in \mathrm{F} \\ a, b, \ldots \in \mathrm{Reg} & t \in \mathrm{TiD} \triangleq \mathbb{N} & i, j, k, \ldots \in \mathrm{LaB} \\ \hat{a}, \hat{b}, \ldots \in \mathrm{Aux} \mathrm{VAr} & \hat{e} \in \mathrm{Aux} \mathrm{Exp} ::= v \mid \hat{a} \mid \hat{e} + \hat{e} \mid \cdots \\ & e \in \mathrm{Exp} ::= v \mid a \mid e + e \mid \cdots & \mathrm{BExp} ::= \mathrm{boolean-valued} \; \mathrm{Exp} \\ & \alpha \in \mathrm{AST} ::= \mathbf{skip} \mid a := e \mid a := \mathbf{load} \; x \mid \mathbf{store} \; x \; e \\ & \mid a := \mathbf{CAS} \; x \; e \; e \mid \mathbf{mfence} \mid \mathbf{flush} \; x \mid \mathbf{flush}_{\mathrm{opt}} \; x \mid \mathbf{sfence} \mid o.f \\ & ls \in \mathrm{LST} ::= \alpha \; \mathbf{goto} \; j \mid \mathbf{if} \; B \; \mathbf{goto} \; j \; \mathbf{else} \; \mathbf{to} \; k \mid \langle \alpha \; \mathbf{goto} \; j, \hat{a} := \hat{e} \rangle \\ & \Pi \in \mathrm{Prog} \triangleq \mathrm{TiD} \times \mathrm{LAB} \to \mathrm{LST} \; pc \in \mathrm{PC} \triangleq \mathrm{TiD} \to \mathrm{LAB} \end{array}$

Fig. 3 Programming language syntax.

As shown in Fig. 2, following the notion of a canonical automata [52], each 'do' transition is internal, and is preceded and succeeded by a corresponding external invocation and response transition. A transaction can abort (indicated by pc value *Aborted*) after invocation, but before responding. It can crash by transitioning to *Aborted* from any state after starting, but before it has committed or aborted.

# 4 View-based Px86 model

This paper builds on the *view-based model* for  $Px86_{view}$  proposed by Cho et al. [12], which has been shown to be equivalent to Px86 [59].  $Px86_{view}$  abstractly captures underlying architectural complexities in terms of timestamps. To support the modelling and verification of our TM implementation, we extend  $Px86_{view}$  as follows:

- (1) We add a new CRASH transition to model a system-wide crash. This is needed because in contrast to prior work [12, 58], we wish to allow reasoning about our TM execution even after a crash/recovery event takes place.

- (2) We introduce a syntax and semantics for high-level durably linearisable [38] objects.

In the following section, we provide a description of the  $Px86_{view}$  programming language and semantics, emphasising on our extensions.

#### 4.1 Programming language

The syntax of our language is given in Fig. 3, which is the syntax from prior work [8, 12] extended with high-level method calls.

Atomic statements (in AST) may be a no-op (**skip**), a local assignment (a := e), a load of a shared location (a := load x), a store to a shared location (**store** x e), an atomic compareand-swap ( $a := CAS x e_1 e_2$ ), a memory fence (**mfence**), a flush instruction (**flush** x), an optimised flush instruction (**flush**<sub>opt</sub> x), a store fence (**sfence**) or a call to an atomic method f of object o (o, f).

A labelled statement LST is either:

- (1) a statement of the form  $\alpha$  goto *j*, comprising an atomic statement  $\alpha$  to be executed and the label *j* of the next statement;

- (2) a conditional statement of the form **if** *B* **goto** *j* **else to** *k*, which facilitates branching, directing execution to label *j* if *B* holds and to *k*, otherwise; and

- (3) a statement incorporating an auxiliary update, denoted as (α goto j, â := ê). An auxiliary update behaves like α goto j, but additionally updates the value of the auxiliary variable â with the auxiliary expression ê within the same atomic step.

Following [8], a program  $\Pi$  is represented as a function that maps pairs of the form  $(t, i \in TID \times LAB)$  to *labelled statements* in LST, representing the next statement to be executed.

Control flow within each thread is tracked by a *program counter function*, *pc*, which records the program counter of each thread. The initial label of each thread is a designated label  $\iota$  (in LAB). During a program's execution, the *pc* value of a thread changes according to  $\Pi$  and at the end of the thread's execution, *pc* is assigned to a designated value  $\zeta \in LAB$ .

**Example 3** (Program) The program Fig. 1a, assuming that the executing thread has id 1, is given as follows:

$\Pi \triangleq \left\{ \begin{array}{l} (1, \iota) \mapsto \text{store } x \ 1 \ \text{goto } 2, \\ (1, 2) \mapsto \text{flush}_{\text{opt}} x \ \text{goto } 3, \\ (1, 3) \mapsto \text{store } y \ 1 \ \text{goto } \zeta \end{array} \right\}$

#### 4.2 The Px86<sub>view</sub> semantics

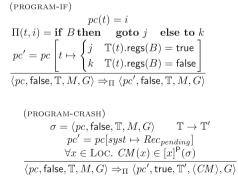

Our operational semantics is based on earlier work by Cho et al. [12]. A selection of transition rules of the semantics is given in Fig. 4.

A state is modelled by a tuple  $\sigma = \langle pc, rec, \mathbb{T}, M, G \rangle$ .

- $pc: TID \rightarrow LAB$  maps each thread to the next instruction to be executed.

- *rec* : *bool* is a flag that indicates when a recovery process is in progress. In the event of a crash, *rec* is set to true to indicate that an implementation-specific recovery process is about to start its execution. We assume that after the recovery process completes, *rec* is reset to false.

- $\mathbb{T}$  : TID  $\rightarrow$  THREAD maps each thread to its current thread state, where THREAD is a record of *thread views* (see below) and local register store (regs : REG  $\rightarrow$  VAL).

- $M \in MEMORY$  is a list of *messages* modelling the current memory. The first message of each memory is a store  $CM : LOC \rightarrow VAL$ , and the subsequent messages have the form (LOC := VAL). Initially, we assume M = (CM), where CM(x) = 0 for all  $x \in LOC$ .

- $G : AUXVAR \rightarrow VAL$  records the current values of auxiliary variable.

We denote the components of state  $\sigma$  as  $\sigma$ . T,  $\sigma$ . M, etc. We refer to the indices of a memory list as *timestamps*. For ts > 0, the location and a value of a message m are denoted as m.loc and m.val, respectively. The length of the memory list M is denoted as |M|. We say that a message with timestamp  $ts_1$  and location x is not overwritten from timestamp  $ts_2$ 's perspective if the following holds:  $\forall ts \in (ts_1, ts_2]$ . M[ts].loc  $\neq x$ . We denote the above as  $x \notin M(ts_1..ts_2]$ . Furthermore, we use  $\sqcup$  to obtain the maximum among timestamps (i.e.  $ts_1 \sqcup ts_2 = \max(ts_1, ts_2)$ ).

The views of a thread state THREAD comprises the following components.

- coh : Loc  $\rightarrow \mathbb{N}$ , modelling the *coherence view*, which is used to determine the last write to the given location seen by the thread. In combination with  $v_{rNew}$  below, coh determines the range of observable values by *t* for a given location.

- $v_{rNew}$  :  $\mathbb{N}$ , modelling the latest timestamp among all timestamps seen by the thread.

- v<sub>pReady</sub> : N, used to ensure that **load**, **sfence**, **mfence** and **CAS** instructions are ordered w.r.t. subsequent **flush**<sub>opt</sub> instructions.

- v<sub>pAsync</sub> : Loc → N, modelling the *asynchronous view*, which is used to determine values to be persistent after the execution of an **sfence**.

- v<sub>pCommit</sub>: Loc → N modelling the *persistent view*, which is used to determine the set of values of a given location in persistent memory.

$$(ASSIGN) \qquad (STORE) \qquad (LOAD-INTERNAL) \\ \alpha = a := e \qquad v = T.regs(e) \qquad M[ts] \equiv \langle x := v \rangle \\ T:regs(a) \rightarrow v] \qquad T.cob(x) = ts \\ T' = T[regs(a) \rightarrow v] \qquad T' = T \begin{bmatrix} regs(a) \rightarrow v, \\ (T,M) \xrightarrow{\alpha} \langle T',M \rangle \end{bmatrix} \qquad T' = T \begin{bmatrix} regs(a) \rightarrow v, \\ (T,M) \xrightarrow{\alpha} \langle T',M \rangle \end{bmatrix} \qquad (SFENCE) \\ (SFENCE) \qquad \alpha = a := load x \qquad (SFENCE) \\ \alpha = a := load x \qquad (SFENCE) \\ x \notin M[ts] \equiv \langle x := v \rangle \qquad T' = T \begin{bmatrix} regs(a) \rightarrow v, \\ v_{New \rightarrow \sqcup ts} \\ v_{New \rightarrow \sqcup ts} \\ v_{PReady \rightarrow \sqcup ts} \\ v_{PReady \rightarrow \sqcup ts} \end{bmatrix} \qquad (SFENCE) \\ \alpha = a := CAS x e_1 e_2 \\ v_1 = T.regs(e_1) \\ w_2 = T.regs(e_2) \\ M[ts] = \langle x := v \rangle \\ T' = T.eqs(e_1) \\ w_2 = T.regs(e_2) \\ M' = M + \lfloor \langle x := v \rangle \end{bmatrix} \qquad T' = T \begin{bmatrix} regs(a) \rightarrow true, \\ v_{New \rightarrow \sqcup M} \end{bmatrix} \\ (CAS-SUCCESS) \\ \alpha = a := CAS x e_1 e_2 \\ v_1 = T.regs(e_1) \\ w_2 = T.regs(e_2) \\ M' = M + \lfloor \langle x := v \rangle \end{bmatrix} \qquad T' = T \begin{bmatrix} regs(a) \rightarrow true, \\ (v_{New \rightarrow \sqcup M} \end{bmatrix} \\ (V_{New \rightarrow \sqcup M} \end{bmatrix} \\ (V_{New \rightarrow \sqcup M} \end{bmatrix} \\ (CAS-FAIL-INTERNAL) \\ \alpha = a := CAS x e_1 e_2 \\ M[ts] = \langle x := v \rangle \\ T.coh(x) < ts \\ M[ts] = \langle x := v \rangle \\ T.coh(x) < ts \\ M[ts] = \langle x := v \rangle \\ T' = T [regs(a) \rightarrow false] \\ (T,M) \xrightarrow{\alpha} \langle T',M \rangle \qquad (CAS-FAIL-EXTERNAL) \\ \alpha = a := CAS x e_1 e_2 \\ M[ts] = \langle x := v \rangle \\ T' = T [regs(a) \rightarrow false] \\ T' = T [v_{pAsync}(x) \rightarrow \sqcup T.coh(x) \sqcup T.v_{pReady}] \\ (T,M) \xrightarrow{\alpha} \langle T',M \rangle \qquad (CAS-HI) \\ T = hotom x \\ T' = T [v_{pAsync}(x) \rightarrow \sqcup T.coh(x) \sqcup T.v_{pReady}] \\ (FLUSHOPT) \\ \alpha = flush_{opt} x \\ T' = T [v_{pAsync}(x) \rightarrow \sqcup T.coh(x) \sqcup T.v_{pReady}] \\ (FLUSHOPT) \\ (FLUSHO$$

(PROGRAM-NORMAL)  $\begin{array}{c} pc(t) = i \quad \Pi(t,i) = \alpha \ \operatorname{\textbf{goto}} \ j \\ \langle \mathbb{T}(t), M \rangle \xrightarrow{\alpha} \langle T', M' \rangle \\ \underline{pc' = pc[t \mapsto j]} \quad \mathbb{T}' = \mathbb{T}[t \mapsto T'] \\ \overline{\langle pc, \mathsf{false}, \mathbb{T}, M, G \rangle \Rightarrow_{\Pi} \langle pc', \mathsf{false}, \mathbb{T}', M', G \rangle} \end{array}$ (PROGRAM-GHOST) pc(t) = i  $\Pi(t, i) = \langle \alpha \text{ goto } j, \hat{a} := \hat{e} \rangle$  $\begin{aligned} \langle \mathbb{T}(t), M \rangle &\xrightarrow{\alpha} \langle T', M' \rangle \\ pc' &= pc[t \mapsto j] \quad \mathbb{T}' = \mathbb{T}[t \mapsto T'] \\ G' &= G[\hat{a} \mapsto G(\hat{c})] \end{aligned}$  $\langle pc, \overline{\mathsf{fals}} \rangle$

**Fig. 4** Sample of transition rules of  $Px86_{view}$  for a program  $\Pi$ .

We assume that all the registers and views are initialised to 0.

As shown in Fig. 4, execution of a **store** x v instruction adds a message  $\langle x := v \rangle$  to the memory list and updates the coherence view. A r := load x instruction either reads from an earlier write performed by the same thread (LOAD- INTERNAL) or from a write performed by another thread (LOAD- EXTERNAL), which update different thread view components. If the read happens to read the first message of the memory returns M[0](x), otherwise it returns M[ts].val (assuming M[ts].loc). We capture both scenarios using the notation  $M[ts] \equiv \langle x := v \rangle$ .

The **CAS** instruction is modelled by two transition rules (CAS-SUCCESS and CAS-FAILURE). The CAS-SUCCESS transition (for  $a := CAS \ x \ e_1 \ e_2$ ) takes place when the value of register  $e_1$  is equal to the last write at x (the last memory message with location x). In this case, a message  $\langle x := v_2 \rangle$ , where  $v_2$  is the value of register  $e_2$ , is appended in the end of the memory list and register a is assigned true. The CAS-FAILURE transition takes place when the last write at x does not have the value  $v_1$ . In this case, register a is assigned false. The effect of the CAS-FAILURE transition is a equivalent to the effect of a **load** instruction on location x.

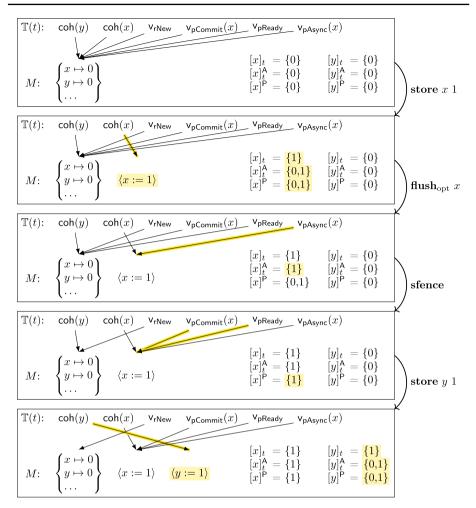

A more detailed description of the views of a thread is given in §A, while an example execution is given below.

*Example 4* (Program execution) Fig. 5 illustrates how the *view* components of a thread state  $\mathbb{T}(t)$  change when *t* executes a program.

- (1) Initially, the memory  $\sigma$ .*M* only includes the *initial message*, and all the components of *t*'s view state point to timestamp 0 (i.e., the initial message).

- (2) After the execution of store x 1 the message (x := 1) is added to the memory. The store transition causes the coherence view of t for x (i.e., σ.T(t).coh(x)) to become 1.

- (3) Execution of **flush**<sub>opt</sub> x causes σ.T(t).v<sub>pAsync</sub>(x) to point to memory index 1. Thus, after executing a subsequent **sfence**, x := 1 will be guaranteed to have been persisted (after step 4 below).

- (4) The **sfence** instruction causes the  $\sigma.\mathbb{T}(t).v_{pCommit}(x)$  view for t to point to the same message as the  $\sigma.\mathbb{T}(t).v_{pAsync}(x)$  view, indicating that x := 1 is now persisted.

- (5) Finally, execution of store y 1 adds to memory M the message (y := 1) at index 2. All the views in T(t) remain the same apart from the coherence view of y (i.e., σ.T(t).coh(y)).

#### 4.2.1 Modelling crashes and recovery

In contrast to prior works [8, 12], which only modelled execution upto the first crash, we provide explicit mechanisms to enable reasoning about crashes and the subsequent recovery operation. We introduce a CRASH transition that creates a new initial message and resets the views of each thread.

Specifically, the memory component of the state,  $\sigma.M$ , satisfies *CM* immediately after a crash in state  $\sigma$  if for every  $x \in$  LOC, there exists some *ts* such that  $\sigma.M[ts] \equiv \langle x := CM(x) \rangle$  and  $x \notin \sigma.M(ts..[]_t \sigma.T(t).v_{pCommit}(x)]$ . To formalise this, we first define the set of possible persistent timestamps for location x in  $\sigma$ :

$$\mathsf{TS}^{\mathsf{P}}(\sigma, x) \triangleq \left\{ ts \mid \mathsf{MemLoc}(x, ts, \sigma.M) = x \land x \notin \sigma.M(ts..\bigsqcup_{t} \sigma.\mathbb{T}(t).\mathsf{v}_{\mathsf{pCommit}}(x)] \right\}$$

where MemLoc(x, t, M)  $\triangleq$  if (t = 0) then x else M[t].loc. The set of timestamps  $\mathsf{TS}^{\mathsf{P}}(\sigma, x)$  represent the set of timestamps of messages that have been *persisted* in state  $\sigma$ , and thus their

**Fig.5** A depiction of a subset of the *current views*, the thread state  $(\mathbb{T}(t))$ , and  $Px86_{view}$  memory list (*M*). The assertions over the thread state are explained in Example 8. The highlighted components of the state capture the effects of each instruction.

corresponding values can be read for location x if a crash occurs at this point of execution. This set corresponds to all the timestamps of the memory messages with location x that are not overwritten before maximum of each thread's  $v_{pCommit}$  view for location x (i.e.,  $\prod_{t} \sigma.\mathbb{T}(t).v_{pCommit}(x)$ ).

**Example 5** Consider the program executed in Example 4. The set  $\mathsf{TS}^{\mathsf{P}}(\sigma, x)$  changes as follows:  $\mathsf{TS}^{\mathsf{P}}(\sigma, x) = \{\} \xrightarrow{\mathsf{store } x \ 1} \mathsf{TS}^{\mathsf{P}}(\sigma, x) = \{0, 1\} \xrightarrow{\mathsf{flush}_{opt} x} \mathsf{TS}^{\mathsf{P}}(\sigma, x) = \{0, 1\} \xrightarrow{\mathsf{store } y \ 1} \mathsf{TS}^{\mathsf{P}}(\sigma, x) = \{1\}$

The set of values corresponding to these timestamps is given by

$$[x]^{\mathsf{P}} \triangleq \lambda \sigma. \mathsf{Vals}(\mathsf{TS}^{\mathsf{P}}(\sigma, x), x, \sigma. M)$$

Deringer

where  $Vals(TS, x, M) \triangleq \{MemVal(x, t, M) | t \in TS\}$  returns the values at the given set of timestamps, assuming MemVal $(x, t, M) \triangleq if (t = 0)$  then M[0](x) else M[t].val. We call the set  $[x]^P$  the *persistent view* of location x. The persistent view of any location x in Loc is global (not specific to a thread) and captures the possible values of x in persistent memory. It constitutes one of the *view-based* expressions that we use to form assertions in the proof outlines of Px86<sub>*view*</sub> programs [8]. We present other *view-based* expressions in Sect. 6.1.

We assume that recovery is executed by a unique system thread, *syst*, that is different from any program thread. Recovery is only enabled in state  $\sigma$  if  $\sigma$ .*rec* holds. Moreover, we assume a special label, *Rec<sub>pending</sub>*, which we assume is the label of the first recovery instruction. Upon completion of the recovery procedure, we assume that *pc<sub>syst</sub>* is set to *Rec<sub>complete</sub>*, and that there is a transition from this state to a state in which *rec* is set to false.

# 5 dTML<sub>Px86</sub>: a durable transaction mutex lock for Px86

In this section, we describe TML and the extensions required for durable opacity under Px86. An adaptation of TML that ensures durable opacity under the simpler PSC memory model (cf. [44]) has been presented in prior work [5]. In addition to assuming a more realistic memory model, unlike Bila et al. [5], our adapted algorithm  $dTML_{Px86}$ , uses optimised flush instructions to increase performance [37], but at the cost of significantly increasing the verification challenge.

#### 5.1 The dTML<sub>Px86</sub> algorithm

Pseudocode for  $dTML_{Px86}$  is given in Fig. 6 as "fall-through" execution, which is notationally more convenient than our goto language (Sect. 4.1). Our Isabelle/HOL encoding uses the goto model (and hence is consistent with the language in Sect. 4.1).

In order to handle the weak behaviours introduced by Px86, we introduce several extensions to the original TML implementation [15]. Specifically, the lines highlighted blue ensure correct thread synchronisation under weak memory, while the lines highlighted green are required to ensure correctness under persistency. The variables highlighted grey are auxiliary. All the local variables apart from the auxiliary ones are modelled as registers. To distinguish them from global variables, we index the registers with the *id* of the transaction that they belong to. As before, we assume that thread identifiers coincide with the transaction identifiers. Moreover, for simplicity, line numbers for return statements are omitted. From now on, will use the term *internal* read for a read that a transaction performs to a location that the same transaction previously wrote, and *external* read for a read that a transaction performs to a location that has been written by another transaction.

We assume that all locations, the registers for every transaction, the global variable glb and the auxiliary variable recGlb, are initialised to zero. The auxiliary variable writer is initialised to *None*. We explain the behaviour of  $dTML_{Px86}$  in stages, starting with the basic algorithm.

#### 5.1.1 The basic TML algorithm

TML performs writes in an *eager* manner, also known as *direct update*, i.e., it updates shared memory within the write operation itself. This is in contrast to lazy algorithms that store writes locally in a write set, and update shared memory at a later stage, e.g., during the commit

$\mathsf{TMWrite}(x, v)$ TMBegin Bp: do  $loc_t := load glb;$ Wp: if  $even(loc_t)$  then B1: **until**  $even(loc_t)$ ; W1:hasWritten<sub>t</sub> := **CAS** glb loc<sub>t</sub> (loc<sub>t</sub> + 1); return ok; W2:if hasWritten<sub>t</sub> then W3: $(\operatorname{loc}_t := \operatorname{loc}_t + 1, \operatorname{writer} := t)$  $\mathsf{TMRead}(x)$ else return aborted  $Rp: r_t := \mathbf{load} x;$ W4: if  $\neg log.contains(x)$  then R1: if  $even(loc_t) \land \neg hasRead_t$  then  $W5: c_t := \mathbf{load} x;$ R2:  $hasRead_t := CAS glb loc_t loc_t;$ W6:  $log.update(x, c_t);$ R3: if hasRead<sub>t</sub> then W7: store x v;return  $r_t$ ; W8 : flush<sub>opt</sub> x; else return *abort*; return ok;  $R4: c_t := \text{load glb};$ R5: if  $c_t = \log_t$  then TMRecover *Rec*1 : while  $\neg log.isEmpty()$ return  $r_t$ ; else return *abort*: Rec2:  $c_{syst} := log.getKey();$ Rec3: store  $c_{sust}$  log.getVal $(c_{sust})$ ; Rec4: TMCommit **flush**<sub>opt</sub>  $c_{syst}$ ; Cp: if  $odd(loc_t)$  then Rec5: sfence; C1: sfence; Rec6:  $log.update(c_{syst}, \bot);$ C2: log.empty(); $Rec7 : c_{syst} :=$ load glb; C3:Rec8: if  $even(c_{sust})$  then  $\langle$ **store** glb (loc<sub>t</sub> + 1), writer := NoneRec9: (store glb  $c_{sust} + 2$ , **return** commit;  $\operatorname{recGlb} := c_{syst} + 2 \rangle$ Rec10 : else (store glb  $(c_{syst} + 1)$ ,  $\operatorname{recGlb} := c_{sust} + 1 \rangle$

Fig. 6 Durable Transactional Mutex Lock.

operation. Additionally TML adopts a *strict* policy for transactional synchronisation: as soon as a transaction attempts to write to a variable, all other transactions running concurrently will be aborted when they invoke a read or a write operation. To enforce this synchronisation policy, TML uses a single *global versioned lock* [19], glb, and a local register  $loc_t$  to record a snapshot of glb at the beginning of the transaction *t*. A writing transaction is in progress iff the value of glb is odd.

A transaction *t* starts by calling TMBegin, then reading glb and storing the read value in the register  $loc_t$  (*Bp*). If the value of glb is odd, another writing transaction is in progress so *t* does not start. Instead, it reattempts to start by rereading glb.

Operation TMWrite(x, v) first checks whether  $\mathsf{loc}_t$  is even (Wp). If not, then *t* must already be the writing transaction, and hence, it can proceed and update the value of the given location *x* to *v* (*W*7). If  $\mathsf{loc}_t$  is even, it means that the current transaction is not yet a writing transaction, thus it attempts to become a writing transaction by performing a compare-and-swap (**CAS**) operation (*W*1). If this **CAS** succeeds, TMWrite becomes the writing transaction and increments  $\mathsf{loc}_t$  (*W*3), making  $\mathsf{loc}_t$  odd, then proceeds to update *x* to *v* (*W*7). In addition, at *W*3, the auxiliary variable writer is set to *t*. If the **CAS** at *W*1 fails, the transaction *t* aborts.

Operation TMRead(x) first reads the value at the given location x and stores it in the register  $r_t$  (Rp). The lines R1 to R3 are used to ensure weak-memory synchronisation under TSO and are explained below. At line R4, the operation reads the current value of glb. If this value is the same as  $\mathsf{loc}_t$ , then either this transaction is the writing transaction, or no other transaction has performed any writes since this transaction started. In both cases the transaction returns the read value. If the test at R5 fails, then the transaction aborts.

Transaction t commits by first checking whether  $loc_t$  is odd (Cp). If so, it means that t is a writing transaction (and hence glb is odd), thus it makes glb even by incrementing glb and setting the auxiliary variable writer to *None*. If t is a read-only transaction (i.e.,  $loc_t$  is even), it simply commits.

We now describe the necessary extensions for adapting TML to the persistent x86 setting. From now on, we assume that the underlying memory model is the persistent x86 and the instructions that are used correspond to the atomic statements of the  $Px86_{view}$  programming language (see Sect. 4.1)

# 5.1.2 Correct synchronisation under Px86

Under Px86, in the presence of multiple writes to a location, a read may return a *stale value*, i.e., a value that is not the last written value. To ensure that a writing transaction serialises correctly, it must successfully perform a **CAS** at line *W*1, which guarantees that it reads the last written value of glb. However, in the standard TML and dTML algorithms [5, 15, 17] (which assume SC and PSC memory, respectively), this synchronisation is never performed by read-only transactions. Using approach in the Px86 setting is problematic since a read-only transaction may complete with a stale value of glb, without ever reading from the latest write to glb.

**Example 6** Consider the program in Fig. 6 without lines R1-R3 (which have been introduced to address correctness under Px86). An execution of this program can reach a state with the following memory sequence:

$$\langle M_0, \langle \mathsf{glb} := 1 \rangle, \langle x := 1 \rangle, \langle \mathsf{glb} := 2 \rangle, \langle \mathsf{glb} := 3 \rangle, \langle x := 2 \rangle, \langle \mathsf{glb} := 4 \rangle \rangle$$

after executing two transactions  $t_1$  and  $t_2$ , where  $t_1$  writes 1 at location x and commits and afterwards  $t_2$  writes 2 at location x and commits. Now suppose transaction  $t_3$  starts, reads glb := 2 (i.e. loc<sub>t</sub> = 2), allowing it to complete TMBegin, and then performs a TMRead(x) operation. The Px86 semantics allows it to read from the stale write  $\langle x := 1 \rangle$  (which has been written by transaction  $t_1$ ), and then commit. Since  $t_1 \prec t_2$  and  $t_2 \prec t_3$ ,  $t_3$  reading the value of x written by  $t_1$ , causes the generated history to violate the real-time ordering constraint of opacity.

To address this, we follow a similar approach to Dalvandi and Dongol [16] in the RC11 memory model,<sup>2</sup> and introduce a **CAS** in the TMRead operation (*R*2), mimicking a fetchand-add-zero, to ensure that the last value of glb is read. If this **CAS** succeeds, the executing transaction can immediately return the read value, and if this **CAS** fails, the transaction can immediately abort (*R*3). Note that this **CAS** only needs to performed if the corresponding transaction has not previously performed a read or a write. Thus at line *R*1, we bypass *R*2 when loc<sub>t</sub> is odd or hasRead<sub>t</sub> holds. To see how the introduction of lines R1 - R3 addresses the issues, consider the following example.

**Example 7** Consider the program in Fig. 6 (with lines R1-R3). Execution of this program can also reach the state in Example 6 after the execution of the transactions  $t_1$  and  $t_2$  described in Example 6. Once again, suppose transaction t starts, then reads glb := 2 (i.e., loc<sub>t</sub> = 2),

<sup>&</sup>lt;sup>2</sup> Note that although our solution to weak memory synchronisation is similar to the RC11 memory model [16], there are subtle differences in the way our solution guarantees correctness of reads. Unlike RC11 memory model which requires a "release" synchronisation on the read corresponding to Rp, in TSO, it is sufficient to perform a standard read.

allowing it to complete TMBegin. Suppose *t* then executes a TMRead(*x*) operation reading the stale write  $\langle x := 1 \rangle$ . However, now (unlike Example 6) *t* proceeds to line *R*2 and since loc<sub>t</sub> is not the last written value of glb, the CAS fails, and thus *t* aborts.

#### 5.1.3 Read-only transactions in Px86

Like Dalvandi and Dongol [16], we observe new behaviours of  $dTML_{Px86}$  that would not be present under SC memory, but without violating durable opacity. In particular, a readonly transaction, *t*, is not immediately invalidated when glb is updated by another writing transaction, provided *t* continues to read from transactional locations that are consistent with a stale value of glb. This read-only transaction would be able to successfully commit if it *never* reads a value for *x* that is more recent than its copy of glb. In case a read-only transaction reads a value of a location *x* at *Rp* that is more recent than its local copy of glb, the load of glb at *R*4 would also read a more recent copy of glb and the transaction would subsequently abort.<sup>3</sup>

#### 5.1.4 Ensuring durability

Durability of dTML under PSC has been studied in previous work [5]. The main idea there was to introduce a durably linearisable [38] persistent undo log that records the previous values of locations that have been overwritten by incomplete writing transactions. The log is reset to empty when the writing transaction commits. If a crash occurs when a incomplete writing transaction *t* is in flight, the subsequent recovery operation sets the state to the last consistent state by undoing the writes of *t* using the undo log. The recovery mechanism from the undo log is similar to this previous work [5], but we use **flush**<sub>opt</sub> and **sfence** instructions instead of **flush**.

As in earlier work [5], there is no need to explicitly persist glb. For transactions to successfully execute TMBegin after a crash, there is no necessity for transactions to read a particular value of glb at line Bp, as long as the read value is even. Lines Rec8-Rec10 of TMRecover ensure that there is at least one even value visible for glb after a system crash.

#### 5.1.5 Alternative designs

While developing dTML<sub>Px86</sub>, we considered several design alternatives. For instance, one option is to move the **CAS** instruction of line R2, to line Bp. In this way, a transaction *t* could have retried loading the most recent value of glb into  $loc_t$  until it succeeds before starting. This would have allowed the transaction to avoid aborting at a later stage. However, while this design may have resulted in fewer aborts, it would likely lead to a considerable increase in overall latency since transactions would be require to execute several **CAS** instructions within the TMBegin operation.

Another design alternative is to use a **flush** instruction instead of the **flush**<sub>opt</sub>; **sfence** sequence in *Rec*4 and *Rec*5. Since the value of each location recorded in the log, is persisted sequentially and by only one thread, we expect the **flush** instruction in this case to be equally or more efficient than the current solution.

Both alternative designs would not affect significantly the verification effort.

<sup>&</sup>lt;sup>3</sup> Note that this particular synchronisation property is much simpler to guarantee in Px86 than in the RC11 model [16], which requires careful management of release-acquire annotations.

# 5.2 dTML<sub>Px86</sub> model

We build a transition system model for  $dTML_{Px86}$ . In this model, we must clarify possible histories of the algorithm, which in turn requires us to clarify the invocation and response events. We assume that the algorithm is executed by a *most-general client* [22] that calls the operations of  $dTML_{Px86}$ .

# 5.2.1 dTML<sub>Px86</sub> executions and histories

For each transaction t, we assume a program counter,  $pc_t$ , (initially NotStarted) that is used to model the control flow of transaction t. When t is in flight, but not executing any operation, we have  $pc_t = Ready$ . Similarly,  $pc_t = Aborted$  and  $pc_t = Committed$  iff t has aborted or committed, respectively. Otherwise  $pc_t$  is a line number corresponding to the instruction of the operation t is executing.

We assume each operation  $op \in \{\text{TMBegin}, \text{TMRead}(x), \text{TMWrite}(x, v), \text{TMCommit}\}\$ generates an event  $inv_t(op)$  when op starts executing and  $res_t(op)$ , when op completes.

# 5.2.2 Ensuring well-formed histories

To ensure well-formedness of histories, we must ensure that transaction identifiers are not reused. Additionally, a live (i.e., in-flight) transaction before a crash must not continue its execution after the crash. To this end, we implicitly assume a *persistent transaction manager* that allocates new transaction identifiers. In our model, like earlier works [5] we use program counters to concisely characterise this assumption. First note that we assume program counter values of all threads except the system thread are unchanged after a CRASH transition (see Fig. 4), thus any transaction t with  $pc_t = NotStarted$  can be executed after a crash. To ensure that in-flight transactions are not resumed, we assume that recovery starts by setting  $pc_t$  to *Aborted* for every transaction t such that  $pc_t \notin \{NotStarted, Aborted, Committed\}$  (cf. TMCrashRecovery in Fig. 2).

### 5.2.3 Modelling log operations

The final source of complexity is the *durably linearisable* [38] log, *log*, which we model as a (persistent) mapping from locations to values. In our model, we use a sequential specification of *log* that does not enforce any *client-side memory synchronisation* (see [16, 66]) because the TML algorithm only allows a single writer at a time, and hence there is never any race on *log*. Moreover, because we assume that *log* is durably linearisable, the effect of each *log* operation is persisted before the operation returns, and hence its client (i.e., our dTML<sub>Px86</sub> algorithm) never accesses unpersisted *log* values. We assume that *log* supports the following operations.

*log*.**isEmpty**() that returns true whenever the *log* is empty (i.e., all elements are mapped to  $\perp$ ).

*log*.contains(x) that returns true whenever the log contains x (i.e., x is not mapped to  $\perp$ ).

log.contains(x) that updates the logged location x to value v.

*log*.getKey() that non-deterministically returns a location whose value is not  $\perp$ . *log*.getVal(x) that returns the value of x in *log*.

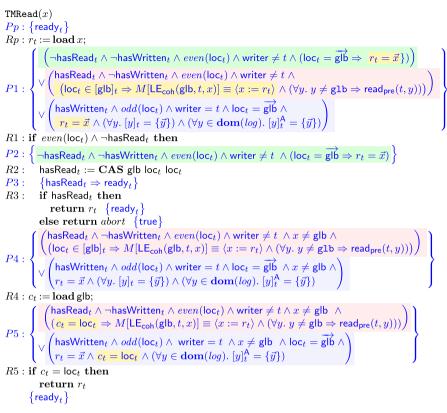

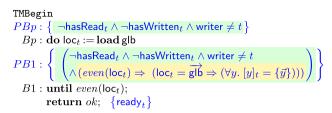

Fig. 7 TMRead annotation.

The log is stored in the *G* state component in Fig. 4 and updated according to SC semantics. An actual implementation of *log* may synchronise threads, e.g., with **mfence** operations, which affects the persistency and thread views of the variables of  $dTML_{Px86}$ . Our proof makes no such assumptions about *log*, namely we assume the *weakest possible* ordering guarantees. Thus, an implementation of *log* that performs additional thread synchronisation would not affect soundness of our result.

# 6 Invariants of dTML<sub>Px86</sub>

This section describes the key invariants of  $dTML_{Px86}$  and mechanisms for proving their correctness. These will be used in the simulation proof in Sect. 7. Our work builds on the PIEROGI logic for  $Px86_{view}$  [8], which uses view-based expressions derived from the *view* components of the thread state. We only require a subset of the PIEROGI assertions. However, we also introduce new view-based expressions simplify reasoning about  $dTML_{Px86}$  (see Sect. 6.1). This is combined with an Owicki–Gries style proof method to establish correctness of proof outlines (Sect. 6.2). However, unlike PIEROGI, because we additionally reason about the behaviour of a program after a crash, we slightly modify the interpretation of a persistent invariant as used in PIEROGI (see Sect. 6.2). PIEROGI requires that we establish a set of proof rules for atomic statements. We present a subset of these, including our new view-based

expressions for  $dTML_{Px86}$  in §B. In Sect. 6.4, we present an example proof outline for the TMRead operation and finally, in Sect. 6.3, we present the persistent invariant.

#### 6.1 View-based expressions

We first recap two key PIEROGI view-based expressions that are used in our proof.

The *thread view* expression,  $[x]_t$ , of a thread *t* for a location *x* captures the values that are visible to *t* for *x*. It indicates the values that can be read from *t* via the execution of a **load** or **CAS** instruction on *x*. The formal definition of  $[x]_t$  is constructed by firstly specifying the set of timestamps of the visible to *t* memory messages with location *x* ( $\mathsf{TS}_t(\sigma, x)$ ), and then by extracting the set of the values that correspond to those timestamps using Vals. We define:

$$[x]_{t} \stackrel{t}{=} \lambda \sigma. \operatorname{Vals}(\operatorname{TS}_{t}(\sigma, x), x, \sigma.M) \qquad (\text{thread view})$$

where  $\mathsf{TS}_t(\sigma, x) \triangleq \begin{cases} ts |\mathsf{MemLoc}(x, ts, \sigma.M) = x \land \\ \sigma.\mathbb{T}(t).\mathsf{coh}(x) \le ts \land x \notin \sigma.M(ts..\sigma.\mathbb{T}(t).\mathsf{v}_{\mathsf{rNew}}] \end{cases}$ Similarly, the *asynchronous view* expression,  $[x]_t^{\mathsf{A}}$ , of a thread *t* for a location *x* is thread-

Similarly, the *asynchronous view* expression,  $[x]_t^A$ , of a thread t for a location x is threadlocal and captures the values that can be persisted after the execution of an **sfence** instruction by t. This only depends on the view  $v_{pAsync}(x)$  of t, which potentially changes after a **flush**<sub>opt</sub> on x by t. The formal definition of  $[x]_t^A$  is constructed by firstly specifying the set of timestamps of the asynchronous view of thread t for location x and state  $\sigma$ . Then, as before, we extract the set of values that correspond to those timestamps using Vals. We define:

$$[x]_t^{\mathsf{A}} \triangleq \lambda \sigma. \mathsf{Vals}(\mathsf{TS}_t^{\mathsf{A}}(\sigma, x), x, \sigma. M)$$

(asynchronous view)

where  $\mathsf{TS}_t^\mathsf{A}(\sigma, x) \triangleq \{ ts \mid \mathsf{MemLoc}(x, ts, \sigma.M) = x \land x \notin \sigma.M(ts..\sigma.\mathbb{T}(t).\mathsf{v}_{\mathsf{pAsync}}(x)) \}.$

**Example 8** Consider again the example execution in Fig. 5. This time we consider the assertions associated with each program state. Initially, views  $[z]_t$ ,  $[z]_t^A$  and  $[z]^P$  for  $z \in \{x, y\}$  all comprise the set {0}, meaning that the only value they can read is from the initial message.

- (1) After execution of store x 1, we have  $[x]_t = \{1\}$ , since the coherence view changes, while  $[x]_t^A = [x]^P = \{0, 1\}$  since these views can see the value for x in either the initial message or  $\langle x := 1 \rangle$ . The view assertions on y are unchanged.

- (2) After execution of **flush**<sub>opt</sub> x, since v<sub>pAsync</sub>(x) is updated, the value 0 is no longer visible to the asynchronous view, and hence [x]<sup>A</sup><sub>t</sub> = {1}. Note that the persistent memory may still see both 0 and 1 and hence [x]<sup>P</sup> = {0, 1}.

- (3) Next **sfence** is executed, whereby the both  $v_{pCommit}(x)$  and  $v_{pReady}$  are updated, and this means that we have  $[x]^{p} = \{1\}$ .

- (4) Finally **store** *y* 1 is executed, which has a similar effect to the first step, but on *y* instead of *x*.

Next, we present an extension to PIEROGI that enable reasoning about written values before a given timestamp. The *last entry* views return the timestamp of the memory message with location equal to the given location and a timestamp less than or equal to the given limit.

$$\begin{split} \mathsf{MemLastEntryLim}(x, t, M) &\triangleq \bigsqcup \{ ts \mid \mathsf{MemLoc}(x, t, M) = x \land ts \leq t \} \\ \mathsf{LE}(x) &\triangleq \lambda \sigma. \mathsf{MemLastEntryLim}(x, |\sigma.M| - 1, \sigma.M) \\ \mathsf{LE}_{\mathsf{coh}}(y, t, x) &\triangleq \lambda \sigma. \mathsf{MemLastEntryLim}(x, \mathsf{coh}_t(y)(\sigma), \sigma.M) \\ &\quad \vec{x} \triangleq \lambda \sigma. \mathsf{MemVal}(x, \mathsf{LE}(x)(\sigma), \sigma.M) \end{split}$$

MemLastEntryLim(x, t, M) returns the maximum timestamp of the memory messages with location x and timestamp less or equal to timestamp t, LE(x) returns the timestamp of the last memory message on location x, and  $LE_{coh}(y, t, x)$  returns the timestamp of the last write to x before t's coherence view for y. The expression  $\vec{x}$  returns the value of the last message of the memory with location x in the given state.

#### 6.2 Owicki–Gries reasoning

In this section, we describe our Owicki–Gries style framework that we used to show that a proof outline is *valid*. Our framework follows PIEROGI [8], but we revise the notion of a persistent invariant to enable one to describe the execution of a program after a crash. In particular, given a multi-threaded program  $\Pi$ , in addition to the local correctness and global correctness checks, we also check that the persistent invariant is maintained by *all* program transitions, including those of the recovery operation. As such the persistent invariant can be used as an assumption when proving local correctness and global correctness. The use of a global invariant to simplify Owicki–Gries proofs is a well known technique [26].

We refer to the set of *assertions* (i.e. predicates over  $Px86_{view}$  states) that use view-based expressions (§6.1) as an ASSERTION<sub>PV</sub>. A *proof outline* is a tuple (*in*, *ann*, *I*, *fin*), where *in*, *fin*  $\in$  ASSERTION<sub>PV</sub> are the initial and final assertions, *I* is the persistent invariant and *ann* is an *annotation function* that models program annotations. Specifically, *ann*  $\in$  ANN = TID×LAB  $\rightarrow$  ASSERTION<sub>PV</sub>, associates each program point (*t*, *i*) with its associated assertion. We let *Recovery* denote the set of all statements of the recovery operation and *crash* be a statement corresponding to a CRASH transition.

**Definition 1** (Valid proof outline) A proof outline (in, ann, fin, I) is *valid* for a program  $\Pi$  iff the following hold:

Initialisation. For all  $t \in \text{TID}$ ,  $in \Rightarrow I \land ann(t, \iota)$ . Finalisation.  $I \land (\bigwedge_{t \in \text{TID}} ann(t, \zeta)) \Rightarrow fin$ . Local correctness. For all  $t \in \text{TID}$  and  $i \in \text{LAB}$ , either:

- $\Pi(t, i) = \alpha$  goto *j* and  $\{I \land ann(t, i)\} \alpha \{I \land ann(t, j)\}$ ; or

- $\Pi(t, i) =$ **if** *B* **goto** *j* **else to** *k* and both

- $-I \wedge ann(t, i) \wedge B \Rightarrow ann(t, j)$  and

- $-I \wedge ann(t, i) \wedge \neg B \Rightarrow ann(t, k)$  hold; or

- $\Pi(t, i) = \langle \alpha \text{ goto } j, \hat{a} := \hat{e} \rangle$  and  $\{I \land ann(t, i)\} \alpha \{(I \land ann(t, j))[\hat{e}/\hat{a}]\}.$

Global Correctness. For all  $t_1, t_2 \in \text{TID}$  such that  $t_1 \neq t_2$  and  $i_1, i_2 \in \text{LAB}$ :

- if  $\Pi(t_1, i_1) = \alpha$  goto j, then  $\{I \land ann(t_2, i_2) \land ann(t_1, i_1)\} \alpha \{ann(t_2, i_2)\};$

- if  $\Pi(t_1, i_1) = \langle \alpha \text{ goto } j, \hat{a} := \hat{e} \rangle$ , then  $\{I \land ann(t_2, i_2) \land ann(t_1, i_1)\} \alpha$  $\{ann(t_2, i_2)[\hat{e}/\hat{a}]\}.$

- $[ann(t_2, t_2)] = [ann(t_2, t_2)]$

Crash invariance. Both of the following hold:

- for all  $\alpha \in Recovery$ ,  $\{I\} \alpha \{I\}$

- {*I*} crash {*I*}

Initialisation (resp. Finalisation) ensures that the initial (resp. final) assertion of each thread holds in the initial (resp. final) state. Local correctness ensures the validity of the program annotation of each thread, while global correctness ensures the global correctness of the program annotation of each thread under the execution of other threads. In essence,

the local correctness proof for a thread t checks for each atomic statement of t if its postcondition (given as annotation) can be established by its pre-condition (given as annotation). Similarly, the global correctness proof for a thread t checks that the pre-condition of each atomic statement of t is stable against the atomic statements of the other threads. Note that **if** B **goto** j **else to** k does not generate a global correctness proof obligation since B is an expression over thread-local variables, thus does not change the global state.

To show that a proof outline is valid (Definition 1) we use two types of rules: standard decomposition rules and rules for atomic statements.

#### 6.2.1 Standard decomposition rules

The standard decomposition rules of Hoare logic such as weakening preconditions, strengthening postconditions, and decomposing conjunctions and disjunctions apply (see [8]).

#### 6.2.2 Rules for atomic statements and correctness of view-based assertions

The proof rules that we use constitute all the rules of the PIEROGI framework [8] as well as some additional rules developed enable proofs of correctness for  $dTML_{Px86}$ . All the proof rules used in this work have been mechanised and proved sound against our extensions to  $Px86_{view}$  in Isabelle/HOL. Each rule captures the impact of the execution of atomic statements (discussed in §4.1) on assertions formed by view-based expressions (outlined in §6.1).

We have two general types of rules used to discharge local and global correctness proof obligations. Local correctness proof rules often describe how views are changed through the execution of a thread:

**Example 9** Assuming that the statement in question is executed by thread t, the rule  $\{[x]_t^A = S\}$  flush<sub>opt</sub> x  $\{[x]_t^A \subseteq S\}$  states that the *asynchronous view* of x for thread t in the post-state is equal or a subset of its *asynchronous view* in the pre-state, after executing flush<sub>opt</sub> x.

Global correctness proof rules are often used to show stability of assertions.

**Example 10** Assuming that the statement in question is executed by thread t and  $t \neq t'$ , the rule  $\{[y]_{t'} = S\}$  sfence  $\{[y]_{t'} = S\}$  states that the *thread view* of any address y for any thread remains unchanged after the execution of **sfence**.

Other global correctness rules describe how the memory (and hence available values for a thread to observe change).

**Example 11** Assuming that the statement in question is executed by thread t and  $t \neq t'$ , the rule  $\{[x]_{t'} = S\}$  store x  $v\{[x]_{t'} = S \cup \{v\}\}$  states that the value v for x is available for thread t' to read after the execution of store x v.

A full set of rules for proving local and global correctness of view-based assertions is presented in Sect. B.

### 6.3 Persistent invariant of dTML<sub>Px86</sub>

To prove corrrectness of dTML<sub>Px86</sub>, we construct a multithreaded program  $\Pi_{dTML_{Px86}}$  based on the model introduced in Sect. 5.2.  $\Pi_{dTML_{Px86}}$  includes all dTML<sub>Px86</sub> operations, invocation

events, response events and the system crash event. With the exception of the system thread, which is only capable of executing the TMRecover operation, any thread *t* in TID is free to perform any number of operations (excluding the recovery operation) as long as the resulting execution history conforms to the control flow and well-formedness constraints.

In this section, we present the most important aspects of the persistent invariant, which comprises a collection of properties that the  $dTML_{Px86}$  implementation guarantees in every program state. The corresponding proofs have been mechanised in Isabelle/HOL.

#### 6.3.1 Memory properties

The first three properties describe memory patterns that occur during the execution of  $dTML_{Px86}$ . In each of the properties below, we assume that  $i, j \in dom(M)$  and that i < j.

**Property 1** The values of glb are monotonically increasing within the memory sequence M, i.e.,

$$\forall v_i, v_j. M[i] \equiv \langle \mathsf{glb} := v_i \rangle \land M[j] \equiv \langle \mathsf{glb} := v_j \rangle \implies v_i \leq v_j$$

Property 1 is needed because unlike in prior work [5], the recovery process of  $dTML_{Px86}$  does not reset glb to 0. This is actually necessary to avoid TMRead operations returning stale values (i.e., values that were in persistent memory, but subsequently modified) after a crash. The following example demonstrates this phenomenon.

**Example 12** Consider the program in Fig. 6 that resets glb to zero (store glb 0) after *Rec*6 instead of executing lines Rec7 - Rec10. An execution of this program can reach a state with the following memory sequence:

$$\{ \{ \mathsf{glb} \mapsto 2, x \mapsto 5, \_ \mapsto 0 \}, \langle x := 3 \rangle, \langle \mathsf{glb} := 0 \rangle, \langle \mathsf{glb} := 1 \rangle, \langle y := 1 \rangle, \langle \mathsf{glb} := 2 \rangle \}$$

which is reached from the initial state after a

- (1) A writing transaction updates x to 3 then commits (so glb = 2),

- (2) Another writing transaction writes updates x to 5 (so log(x) = 3),

- (3) A crash occurs (resulting in the initial state above),

- (4) The modified recovery operation described above executes (appending ⟨x := 3⟩ then ⟨glb := 0⟩ to the memory),

- (5) A third writing transaction that updates y to 1 commits successfully.

Now assume that another transaction t starts, then reads 2 for glb from the *initial message*, allowing it to complete TMBegin, then performs a TMRead(x) operation. In this case, according Px86 semantics the initial value of x (i.e., 5) is still observable at Rp. The test at R1 succeeds and the **CAS** instruction at R2 can still succeed, since the last value of glb is 2. As a result, t can successfully complete the TMRead operation and subsequently commit, violating durable opacity.

**Property 2** If there exists a write between two writes to glb such that the value of glb is unchanged, then the location of any intermediate write between these two writes must be on glb, i.e.,

$$\forall v. \ M[i] \equiv \langle \mathsf{glb} := v \rangle \land M[j] \equiv \langle \mathsf{glb} := v \rangle \implies \forall k \in [i, j]. \ M[k].\mathsf{loc} = \mathsf{glb}$$

🖄 Springer

Property 2 holds since this memory pattern described by the antecedent only occurs when two or more transactions that have not yet executed a TMRead or TMWrite invoke TMRead operations and successfully execute their CAS instruction at R2. The first of these reading transactions introduces a write to glb that immediately follows either

- (1) The initial message, or

- (2) A write to glb by a writing transaction at C3, or

- (3) A message added by the TMRecover process at Rec9 or Rec10.

The subsequent TMRead operations introduce writes to glb with unchanged values.

**Property 3** Between a memory message on glb with even value and another memory message on a location different from glb, there exists a message with location on glb with odd value, i.e.,

$i > 0 \land M[i].loc = glb \land even(M[i].val) \land M[j].loc \neq glb \implies$  $\exists k \in (i, j). M[k].loc = glb \land odd(M[k].val)$

Property 3 describes a memory pattern that occurs when a transaction successfully performs a TMWrite. Note that excluding the initial message and the messages added from the recovery process, the only way that messages with a location different from glb are added to the memory is by executing W7. Prior to this, the writing transaction performs a successful CAS at W1. The execution of W1 adds a message to memory with location glb and odd value.

# 6.3.2 Coherence property for non-writing transactions

The next property uses  $\mathsf{maxcoh}_t \triangleq \lambda \sigma$ .  $\bigsqcup_x (\sigma.\mathbb{T}(t)).\mathsf{coh}(x)$ , which denotes the maximum coherence value for *t* across all locations and  $\mathsf{vrnew}_t \triangleq \lambda \sigma$ .  $(\sigma.\mathbb{T}(t)).\mathsf{v_{rNew}}$ , which retrieves the value of  $\mathsf{v}_{\mathsf{rNew}}$  for *t*. We let Recovering  $\triangleq \lambda \sigma$ .  $\sigma.rec = \mathsf{true}$ .

**Property 4** When a TMRecover process is not in progress, for any transaction that is not a writing transaction, the coherence view for all the locations in memory is less than or equal to its  $v_{rNew}$  view, i.e.,

$\forall t \in \text{TID.} \neg \text{Recovering} \land \text{writer} \neq t \implies \text{maxcoh}_t \leq \text{vrnew}_t.$

Property 4 holds because the only cases in which  $coh_t(x) > vrnew_t$ , is when t is executing a write on x or performing an internal read to x. Both cases are precluded for non-writing transactions.

# 6.3.3 Properties about tracked locations and log

We now describe a set of properties describing the memory locations that are tracked by Px86 and *log*. Note that we assume that all locations in LOC different from glb can be transactionally written and read.

Property 5 The domain of log does not contain the location glb, i.e.,

$$\forall x \in \mathbf{dom}(log). \ x \neq \mathsf{glb}$$

**Property 6** For all locations  $x \neq \text{glb}$  that is not in *log*, the persistent view includes only their last written value, i.e.,

$\forall x \in \text{Loc. } x \neq \mathsf{glb} \land x \notin \mathbf{dom}(\log) \implies [x]^{\mathsf{P}} = \{\vec{x}\}$

# 6.3.4 Properties about glb and recGlb

Next we have three properties for glb and the auxiliary variable recGlb.

**Property 7** In the presence of a writing transaction, last value of glb in the memory must be odd, i.e.,

writer

$$\neq None \implies odd(\overrightarrow{\mathsf{glb}})$$