# Low insertion loss, high power handling and good performance 90° phase shifter for X-band radar application

Babak Menbari · Massoud Dousti

Received: 5 March 2014/Accepted: 19 August 2014/Published online: 19 November 2014 © Springer Science+Business Media New York 2014

Abstract In this paper, a monolithic microwave integrated circuit 90° phase shifter circuit for X band radar application is designed and fabricated using 0.1 µm pseudomorphic high electron mobility transistor technology based on GaAs with  $f_t = 85$  GHz. This block is used in passive phase shifters. The structure of 90° used double single port double throw (SPDT) in both input/output. The SPDT used a high yield and good performance switch. The switches have low insertion loss and phase variation. The measurement results of  $90^{\circ}$  block with -6 V control voltage indicate that the insertion loss is less than -1.6 dB and phase shift is  $87 \pm 3.5^{\circ}$  over 8–12 GHz. The 1 dB compression point (P1dB) is more than 25 dBm. The die size is 1 mm<sup>2</sup>. The measurements show good correlation between simulation and measurement results. So, the result demonstrates the great potential of the proposed block for high performance phased array radar systems.

Keywords Phase shifter · pHEMT · SPDT · MMIC

# 1 Introduction

Today's PPS are important elements in phase array radars, antenna switch and positioning systems. The phase shifters have two kinds of structures, passive and active. The PPS is a bilateral network, but the active-type is an unilateral network. The advantage of PPS is that it can be used to

B. Menbari (🖂) · M. Dousti

M. Dousti e-mail: m\_dousti@srbiau.ac.ir both transmit and receive path at the same time. The structure of PPS is a combination of low/high pass filters. For radio frequency (RF)/microwave switch design, PIN diode [1], Micro Electro Mechanical System (MEMS) [2], Low Temperature Co-fire Ceramic (LTCC) [3] and Field Effect Transistor (FET) (in both GaAs and CMOS processes) are the four commonly used technologies. However, considering the cost, integration, switching speed, power consumption, and linearity, FET switches based on III–V compounds (e.g., GaAs), especially pHEMTs, are the most attractive choice on the wireless communication market [4].

Many different passive and active MMICs PS have been reported in literature [5–7]. A switched high-pass/low-pass phase shifter for the X band with 6-bit resolution has been reported in [6]. The technology can be implemented in MMICs. So, the designer can be able to use lumped elements such as inductors, capacitors, resistors and transistors together. Here the dimension of the chip is much smaller than other methods [8]. All connections between elements (microstrip lines) are simulated using advanced design system (ADS) Momentum for planar electromagnetic simulations to take into account the coupling between adjacent microstrip lines.

In Sect. 2, the optimization of switch will explain how to use phase shifter designing. In Sect. 3, the configuration of SPDT is introduced and in the last Sect. 4, the structure of  $90^{\circ}$  phase shifter block indicated optimized switch and SPDT are presented.

# 2 Optimized switch

In this section, an original method is used to describe the investigation on the improvement of the insertion loss and

Department of Electrical Engineering, Science and Research Branch, Islamic Azad University, Tehran, Iran e-mail: b.menbari@srbiau.ac.ir

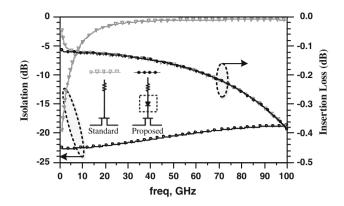

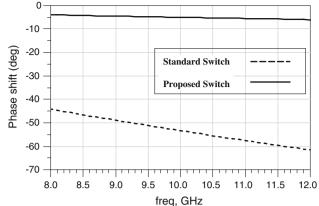

Fig. 1 Simulated insertion loss and isolation for the switch in standard and proposed form

isolation of the pHEMT switch. Fundamentally, the role of the switch is very important in PPS designing. In PPSs, some undesired effects occur due to parasitic elements of transistors. These affects are found in the phase and insertion loss variation of the PPS. The Fig. 1 illustrates GaAs pHEMT switch in standard and proposed form. In this method, the undesired effects of transistors are reduced.

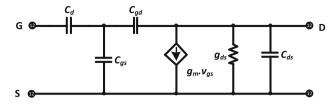

As shown in Fig. 1, a diode is added on a gate of transistor. Usually, a diode is modeled by a dynamic resistor  $(R_d)$  and a capacitor  $(C_d)$ . The  $C_d$  is the junction capacitor between the anode and cathode of diode in the depletion region. The  $C_d$  and gate capacitor  $(C_g)$  are series together as shown in Fig. 2. Also, the  $C_d$  is significantly less than  $C_g$ .

$$\frac{C_{g\times}C_d}{C_g + C_d} \cong C_d \quad if \quad C_g \gg C_d \tag{1}$$

The Eq. (1) shows that  $C_g$  of the proposed switch is smaller than the standard form. The Fig. 2 shows the equivalent circuit of the proposed switch. The parameters of the proposed switch in Fig. 1 can be modeled with parasitic elements like as  $a C_{d} C_{gs}$ ,  $C_{ds}$ ,  $C_{gd}$ ,  $g_{ds}$  and  $g_m v_{gs}$ as shown in Fig. 2. The next equation is extracted from the solving of polynomial function for the Z-parameters matrix where the  $Z_{in}$  is the input impedance of the proposed switch.

The input impedance of the proposed switch is given by:

Fig. 2 Equivalent circuit of the proposed switch

If we assume that the transistor is unilateral, then  $C_{gd}$  is omitted.

$$Z_{in} = \frac{\left[g_{ds}.R_L.C_d + C_d + G_{ds}.R_L.C_{gs} + C_{gs}\right] + \left[C_d.C_{ds}.R_L\right]s}{\left[g_{ds}.C_{gs}.C_d.R_L + C_{gs}.C_d\right]s + \left[C_{gs}.C_{ds}.C_d.R_L\right]s^2} = \frac{\left(C_d + C_{gs}\right)}{s(C_{gs}.C_d)}$$

(3)

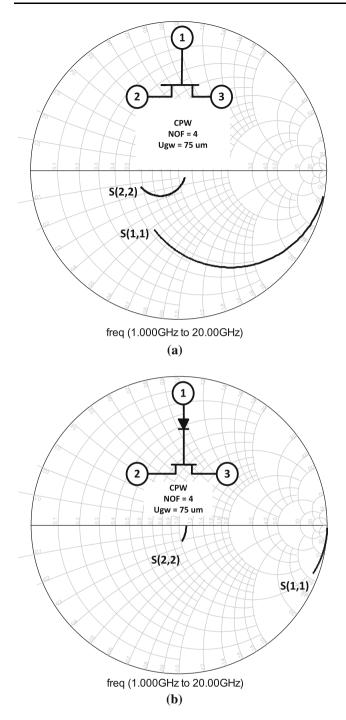

The behaviors of the switches are illustrated in Fig. 3 [4]. Figure 3 shows the study of the characteristics of standard and proposed switches. The the Fig. 3(a) shows that the gate capacitor  $(C_{\rho})$  of the transistor changes significantly in 20 GHz bandwidth. If the input power increases, the non-linear effect of the transistor will be found through the large signal phenomenon of pHEMT transistor. But in Fig. 3(b), the  $C_g$ of the proposed switch is decreased, hence, the large signal and nonlinear effects of the new method are declined. Table 1 shows the value of  $C_g$  as a function of frequency from Fig. 3.

As it is evident in the Fig. 4 and Table 1, the proposed switch is suitable for the phase shifter designing. Because in PPS application, the behavioral switch have an undesirable effect in PPS specification, so, it has been tried to design a good switch with minimum undesirable effect. The Fig. 4 shows that the phase variation is decreased in proposed switch, whereas in standard switch the phase variation is too much in on–off mode. In standard switch, the phase variation is maximum 2 degrees in on–off mode@ 10 GHz. Some parameters such as phase uniformity, the best insertion loss and maximum input power handling are very important in PPSs [9].

$$Z_{in} = \frac{\left[g_{ds}.R_L.C_d + C_d + g_{ds}.R_L.C_{gd} + g_m.R_L.C_{gd} + C_{gd} + g_{ds}.R_L.C_{gs} + C_{gs}\right] + \left[C_{ds}.C_d.R_L + C_{gd}.C_d.R_L + C_{gd}.C_{ds}.R_L + C_{gs}.C_{gd}.R_L\right]s}{C_d.\left[g_{ds}.R_L.C_{gd} + g_m.R_L.C_{gd} + C_{gd} + g_{ds}.R_L.C_{gs} + C_{gs}\right]s + C_d.\left[C_{ds}.C_d.R_L + C_{gd}.C_d.R_L + C_{gd}.C_{ds}.R_L + C_{gs}.C_{gd}.R_L\right]s^2}$$

(2)

Fig. 3 The smith chart of (a) Standard switch structure. (b) Proposed method structure

**Table 1** The  $C_g$  values in standard and the proposed method

| 8                                                                                        |                  |                 |                 |

|------------------------------------------------------------------------------------------|------------------|-----------------|-----------------|

|                                                                                          | 1 GHz            | 10 GHz          | 20 GHz          |

| $(C_g \text{of Standard mode}) \text{ pF}$<br>$(C_g \text{of Proposed mode}) \text{ pF}$ | 0.0286<br>0.0032 | 0.293<br>0.0311 | 0.638<br>0.0627 |

Fig. 4 The phase shift of standard and proposed switch

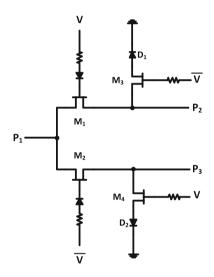

Fig. 5 Schematic of SPDT

# **3** SPDT structure

In this section, we describe how by using the proposed method, the performance of the GaAs switch can be improved. The schematic circuit diagram of the implemented SPDT switching circuit is shown in Fig. 5. The size of the transistors has been selected for high power handling. Since the breakdown voltage in a GaAs HEMT is larger than the pinch off voltage, power handling of the switch is set by the open channel current limit of a transistor. Therefore, in order to have a design with acceptable power handling, total gate width of the series pHEMTs has to be selected in a fitting manner [10].

In Fig. 5, the series transistors  $M_1$  and  $M_2$  perform the main switching functions, and the shunt transistor M3 and M4 increase the isolation of the switch. Under these conditions, one of the RF inputs ( $P_2$  or  $P_3$ ) is connected to the common

Fig. 6 (a) Simulation result of Insertion loss and Isolation (b) Simulation result of 1 dB compression point and pout versus pin

port (P<sub>1</sub>) through a low value of the complementary HEMT's on—resistance, while another one is isolated from the common port by the large value of the drain—source resistance in the "off" mode. The D<sub>1</sub> and D<sub>2</sub> are increased the power handling of SPDT switches. The Fig. 6 shows the simulation results of the proposed SPDT switch. As shown in Fig. 6(a), the insertion loss is 0.7 dB with variation of  $\pm 0.1$  dB and its isolation is better than 28 dB. Also, Fig. 6(b) shows that the P<sub>1</sub>dB of the circuit is 28 dBm [10].

# 4 90° phase shifter Block structure

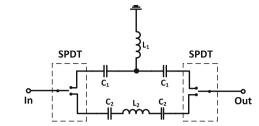

The Fig. 7 illustrates the proposed 90° block structure. This configuration has two SPDT switches in input and output of block. The proposed block includes a high pass and a band pass filter.

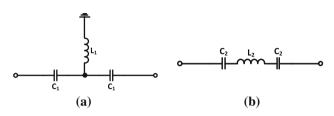

The Fig. 8(a) shows the structure of high pass filter through which the SPDT switch leads signal to high pass section of the proposed block. Then, the signal finds a path to the ground via  $L_1$  and  $C_1$ .

Fig. 7 Proposed 90° block

Fig. 8 (a) High pass filter (b) Band pass filter

The Fig. 8(b) illustrates the band pass filter at the second state. The signal finds the ground via  $L_2$ ,  $C_2$  to 50  $\Omega$  impedance matching.

The Eqs. (4) and (5) are the transfer function of high pass and band pass filter respectively.

$$H_{H,P}(s) = \frac{\left(C_1^2 L_1 Z_0\right) s^3}{1 + (C_1 Z_0) s + (2C_1 L_1) s^2 + (C_1^2 L_1 Z_0) s^3}$$

(4)

$$H_{B,P}(s) = \frac{(C_2^2 Z_0)s^2}{(2C_2)s + (C_2^2 Z_0)s^2 + (C_2^2 L_2)s^3}$$

(5)

The S-parameters of the high pass filter are given by:

$$S_{H,P11} = \frac{j(2C_1\omega - C_1^2 L_1\omega^3 - Z_0^2 L_1\omega)}{2Z_0 - 2Z_0 L_1 C_1\omega^2 + j(Z_0^2 L_1\omega + 2C_1\omega - C_1^2 L_1\omega^3)}$$

(6)

$$S_{H.P12} = \frac{2Z_0}{2Z_0 - 2Z_0 L_1 C_1 \omega^2 + j (Z_0^2 L_1 \omega + 2C_1 \omega - C_1^2 L_1 \omega^3)}$$

(7)

By using the above equations, the best values of  $L_I$  and  $C_I$  are calculated. To achieve the best impedance matching in input and output circuit of central angular frequency  $(\omega_0)$ ,  $S_{II} = 0$  should be considered, so the relationships between  $L_I$  and  $C_I$  are:

$$L_1 = \frac{2C_1\omega_0}{C_1^2\omega_0 + Z_0^2\omega_0}$$

(8)

From  $S_{21}$ , the values of phase shift,  $L_1$  and  $C_1$  in central angular frequency ( $\omega_0$ ) are obtained as follows:

$$\Delta \varphi = -\tan^{-1} \left( \frac{Z_0^2 L_1 \omega_0 + 2C_1 \omega_0 - C_1^2 L_1 \omega_0^3}{2Z_0 - 2Z_0 L_1 C_1 \omega_0^2} \right) \tag{9}$$

$$C_1 = \frac{Z_0 \tan\left(\Delta \ \varphi \ / 2\right)}{\omega_0}; L_1 = \frac{\sin(\Delta \varphi)}{Z_0 \omega_0} \tag{10}$$

Also, the S-parameters of the band pass filter are given by:

$$S_{B,P11} = \frac{j(C_2 L_2 \omega^2 - 2)}{2Z_0 C_2 \omega + j(C_2 L_2 \omega^2 - 2)}$$

(11)

$$S_{B,P12} = \frac{2Z_0 C_2 \omega}{2Z_0 C_2 \omega + j(C_2 L_2 \omega^2 - 2)}$$

(12)

By using above equations, the best value of  $L_2$  and  $C_2$  are calculated. To give the best impedance matching of circuit in  $\omega_0$ ,  $S_{11}$  should be equal to zero. So  $L_2$  and  $C_2$  are:

$$\frac{d}{d\omega} \left( -\tan^{-1} \left( \frac{L_2 C_2 \omega^2 - 2}{2 Z_0 C_2 \omega} \right) \right) \Big|_{\omega = \omega_0} = \frac{-1}{Z_0 C_2 \omega_0^2}$$

(13)

By evaluating Eqs. (9) and (13), the best value of  $C_2$  and  $L_2$  are achieved.

$$L_2 = \frac{2Z_0 \tan(\Delta \varphi/2)}{\omega_0}; C_2 = \frac{1}{2Z_0 \omega_0 \tan(\Delta \varphi/2)}$$

(14)

The values of  $C_1$ ,  $C_2$ ,  $L_1$  and  $L_2$  are shown in Table 2.

Table 2

Components values

| Elements | <i>C</i> <sub>1</sub> | <i>C</i> <sub>2</sub> | $L_{I}$       | <i>L</i> <sub>2</sub> |

|----------|-----------------------|-----------------------|---------------|-----------------------|

| Values   | 0.83 <i>pF</i>        | 29 <i>pF</i>          | 0.9 <i>nH</i> | 0.6 <i>nH</i>         |

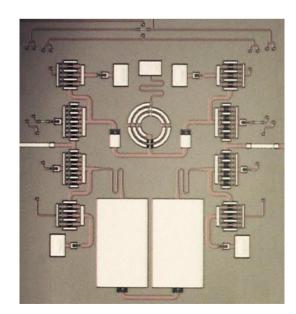

**Fig. 9** Photograph of 90° block

185

The Fig. 9 shows the photograph of  $90^{\circ}$  block in pHEMT GaAs technology.

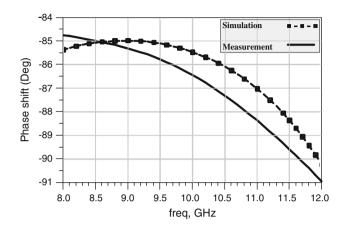

The Fig. 10 shows the simulation and the measurement results of 90° phase shifter block. The measured phase shift is  $87^{\circ} \pm 3.5^{\circ}$  over 8–12 GHz.

Fig. 10 The measurement and the simulation results of  $90^{\rm o}$  phase shifter

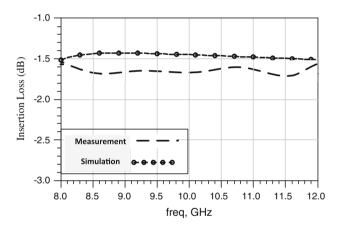

Fig. 11 The measurement and the simulation results of insertion loss

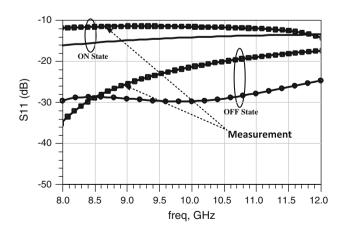

**Fig. 12** The measurement and the simulation results of  $S_{11}$

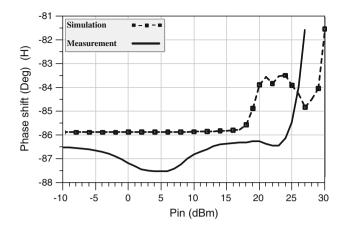

Fig. 13 The measurement and the simulation results of phase variation versus input power

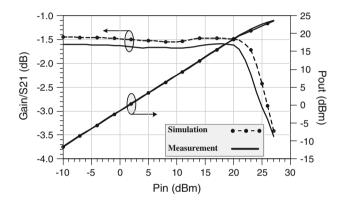

Fig. 14 The measurement and the simulation results of 1 dB compression point and output power versus input power

Table 3 Comparison of 90° phase shifter blocks

| Process               | Freq<br>(GHz) | Phase<br>range               | IL (dB)           | Ref          |

|-----------------------|---------------|------------------------------|-------------------|--------------|

| 0.18 μm RF<br>CMOS    | 9–15          | $90^{\circ} + 4^{\circ}$     | $-16 \pm 1.3^{*}$ | [4]          |

| 0.5 μm pHEMT<br>GaAs  | 4–12          | $93^{\circ} \pm 7^{\circ}$   | $^{-}$ 1.95 ± 0.7 | [11]         |

| 0.6 μm MESFET<br>GaAs | 4–6           | 90°                          | $-1.2 \pm 0.5$    | [12]         |

| 0.3 μm pHEMT<br>GaAs  | 40–60         | 90°                          | $-4 \pm 0.4$      | [13]         |

| 0.25 μm pHEMT<br>GaAs | 3.6-4.2       | 90°                          | <6.4*             | [14]         |

| 0.15 μm pHEMT<br>GaAs | 8-12          | $87^{\circ} \pm 3.5^{\circ}$ | $-1.6 \pm 0.1$    | This<br>work |

\* All states of phase shifter

The Fig. 11 shows the simulation and the measurement of the insertion loss of the proposed block. The measured insertion loss is  $-1.6 \pm 0.1$  dB over 8–12 GHz.

The Fig. 12 shows the simulation and the measurement of the  $S_{11}$  of 90° block in "ON" and "OFF" state.

The Fig. 13 illustrates phase shift of the block versus input power. This diagram shows that the output phase shift has less phase variation in 25 dBm input power.

In the Fig. 14, 1 dB compression point of the proposed block is determined. The result shows that  $P_1$ dB is 25 dBm.

The Table 3 presents a detailed comparison between some of the same studies.

### 5 Conclusions

In this study, by using 0.15  $\mu$ m pHEMT technology, a MMIC 90° block is fabricated and measured in X-band. In this work, a transistor switch is optimized by using the proposed method, and then utilized in the SPDT switch. The SPDT switch is used in the proposed block. The measurement results of the proposed block show that the insertion loss is -1.6 dB, the phase shift is  $87^{\circ} \pm 3.5^{\circ}$  over 8-12 GHz. The phase linearity and P<sub>1</sub>dB are more than 25 dBm. The die size is 1 mm<sup>2</sup>. The measurement shence show a good correlation between simulation and the measurement results. So, the results demonstrate the great potential of the proposed block for high performance phased array radar systems.

### References

- Tayrani, R., Teshiba, M. A., Sakamoto, G. M., Chaudhry, Q., Alidio, R., Kang, Y., et al. (2003). Broad-Band SiGe MMICs for phased-Array radar Applications. *IEEE Journal of solid-state circuit*, 38(9), 1462–1470.

- Hung, J. J., Dussopt, L., & Rebeiz, G. M. (2004). Distributed 2and 3-Bit W-Band MEMS phase shifters on glass substrates. *IEEE Transactions on Microwave Theory and Techniques*, 52(2), 600–606.

- Gray, H. A., Karavanic, E., Shih Hsu, V., & Donoghue, D. (2010). An integrated 6 × 4 mm<sup>2</sup> LTCC front end module for WLAN radio applications, EuMC, Microwave IEEE conference, (pp. 1062–1065).

- Kang, D. W., Lee, H. D., Kim, C. H., & Hong, S. (2006). Kuband MMIC phase shifter using a parallel resonator with 0.18 μm CMOS Technology. *IEEE Transactions on Microwave Theory* and Techniques, 54(1), 294–301.

- Hayashi, H., & Muraguchi, M. (1999). An MMIC Active phase shifter using a variable resonant circuit. *IEEE Transactions on Microwave Theory and Techniques*, 47(10), 2021–2026.

- Fujii, K. (1998). A sophisticated analysis procedure for an MMIC phase shifter. *IEEE Journal of solid-state circuit*, 33(4), 666–668.

- Dousti, M., Delacressonniere, B., Temcamani, F., & Gautier, J. L. (1997). Active MMIC wideband time delay. *Microwave & Optical Technology Letters*, 16, 382–385.

- Ellinger, F., Jäckel, H., & Bächtold, W. (2003). Varactor-loaded transmission-line phase shifter at C-band using lumped elements. *IEEE Transactions on Microwave Theory and Techniques*, 51(4), 1135–1140.

- 9. Menbari, B., Dousti, M., & Hajghassem, H. (2014). A Wide range, high yield and good performance pHEMT switch for

- Menbari, M., Dousti, M., & Hajghassem, H. (2014). A Wide range Monolithic pHEMT SPDT Switch. *Microwave and Optical technology letters*, 56(6), 1454–1458.

- 11. Miyaguchi, K., Hieda, M., Nakahara, K., Kurusu, H., Nii, M., Kasahara, M., et al. (2001). An ultra-broad-band reflection-type phase-shifter MMIC with series and parallel LC circuits. *IEEE Transactions on Microwave Theory and Techniques*, 49(12), 2445–2452.

- Ellinger, F., Vogt, R., & Bächtold, W. (2001). Ultra compact, low loss, varactor tuned phase shifter MMIC at C-band. *IEEE Microwave Wireless Components Letters*, 11, 104–105.

- Nam, S., Payne, A. W., & Robertson, I. D. (2001). RF and microwave phase shifter using complementary bias techniques. *Electronics Letters*, 37(18), 1124–1125.

- Xiaofeng, Y., & Jiangyi, S. (2013). C-Band 6-bit phase shifter for a phase array antenna. *Journal of semiconductors*, 34(4), 045009.

Babak Menbari was born in Arak, Iran, on August 27, 1980. He received B.S. and M.S. degrees from Azad Arak University in 2004 and 2006, respectively. He received his Ph.D. of electronic (MMIC designing) in Srbiau University 2013. His employment in included semiconductor researches in R&D center of IRAN semiconductor Industrials. He is managing the design center of MMIC chip in his company. His research contains linear and non-linear microwave/RF circuits and systems design, millimeter wave circuits design, and MMIC technology.

Massoud Dousti received B.S. in Electrical Engineering from Orleans University, Orleans, France and M.S. degrees in Electronics (Microwave and Optics) from Limoges University, Limoges, France, in 1991 and 1994 and Ph.D. in Electronics (Active Microwave Circuits) from University of Paris VI, Pierre et Marie Currie, in 1999 respectively. He served as a teaching assistant in the Department of Electrical Engineering at Ensea, Cergy Pon-

toise, France from 1998 to 2000. In 2001 he joined Department of Electrical Engineering of Science and Research Branch, Islamic Azad University, Tehran, IRAN, where he is now an Associate Professor. His research interests are linear and non-linear microwave/RF circuits and systems design, millimeter wave circuits design, and MMIC technology.