### RUNTIME VERIFICATION

# An overview of the MOP runtime verification framework

Patrick O'Neil Meredith · Dongyun Jin · Dennis Griffith · Feng Chen · Grigore Roşu

Published online: 23 April 2011 © Springer-Verlag 2011

**Abstract** This article gives an overview of the, monitoring oriented programming framework (MOP). In MOP, runtime monitoring is supported and encouraged as a fundamental principle for building reliable systems. Monitors are automatically synthesized from specified properties and are used in conjunction with the original system to check its dynamic behaviors. When a specification is violated or validated at runtime, user-defined actions will be triggered, which can be any code, such as information logging or runtime recovery. Two instances of MOP are presented: JavaMOP (for Java programs) and BusMOP (for monitoring PCI bus traffic). The architecture of MOP is discussed, and an explanation of parametric trace monitoring and its implementation is given. A comprehensive evaluation of JavaMOP attests to its efficiency, especially in comparison with similar systems. The implementation of BusMOP is discussed in detail. In general, BusMOP imposes no runtime overhead on the system it is monitoring.

$\begin{tabular}{ll} \textbf{Keywords} & Runtime \ verification \cdot Monitoring \cdot Testing \cdot \\ Real \ time \ systems \end{tabular}$

Supported in part by NSF grants CCF-0916893, CNS-0720512, and CCF-0448501, by NASA contract NNL08AA23C, and by a Samsung SAIT grant.

P. O. Meredith (⋈) · D. Jin · D. Griffith · F. Chen · G. Roşu Department of Computer Science, University of Illinois at Urbana-Champaign, 201 N Goodwin Ave., Urbana, IL 61801, USA e-mail: pmeredit@cs.uiuc.edu; pmeredit@gmail.com

D Iir

e-mail: djin3@cs.uiuc.edu

D. Griffith

e-mail: dgriffi3@cs.uiuc.edu

G. Roşu

e-mail: grosu@cs.uiuc.edu

#### 1 Introduction

Runtime monitoring of requirements can increase the reliability of the resulting hardware or software systems. There is an increasingly broad interest in uses of monitoring in software development and analysis, as reflected, e.g., by abundant approaches proposed recently ([3,11,15,18,24,25,28,30,43,46] among others), and also by the runtime verification (RV) and the formal aspects of testing (FATES) initiatives [9,29,30,33,34,58] among many others. Hardware approaches to monitoring have seen less active research. Most attempts in hardware to perform monitor tasks have been for the purposes of performance measures or temperature control. Lu and Forin [45] is an approach that generates monitors from formal properties that are implemented in hardware, but these hardware monitors are actually used to monitor software programs.

Monitoring oriented programming (MOP) [19–22,47] is a generic monitoring framework that integrates specification and implementation by checking the former against the latter at runtime. In MOP, one specifies desired properties using logical formalisms with actions to handle violations or validations of the specified property. MOP tools will then automatically synthesize monitors from property specifications and integrate them within the application together with user-provided handling code.

### 1.1 Related work

We next discuss the relationships between the MOP framework and other related paradigms, including AOP, design by contract, runtime verification, and other trace monitoring approaches. Broadly speaking, all the approaches discussed below are instances of runtime monitoring. Interestingly, even though most of the systems mentioned below

target the same programming languages, no two of them share the exact same logical formalism for expressing properties. This observation strengthens our belief that probably there is *no silver bullet logic* (or *super logic*) for all purposes. A major objective in the design of the MOP framework was to avoid hardwiring particular logical formalisms into the system.

#### 1.1.1 Aspect oriented programming languages

Since its proposal in [42], Aspect oriented programming (AOP) has been increasingly adopted and many tools have been developed to support AOP in different programming languages, e.g., AspectJ and JBoss [40] for Java, and AspectC++ [5] for C++. Built on these general AOP languages, numerous extensions have been proposed to provide domain-specific features for AOP. Among these extensions, Tracematches [3] and J-LO [15] support history(trace)-based aspects for Java.

Tracematches enable the programmer to trigger the execution of certain code by specifying a parametric regular pattern of events in a computation trace, where the events are defined over entry/exit of AspectJ pointcuts. When the pattern is matched during the execution, the associated code will be executed. In this sense, Tracematches support tracebased pointcuts for AspectJ. J-LO is a tool for runtimechecking temporal assertions. These temporal assertions are specified using parametric linear temporal logic (LTL) and the syntax adopted in J-LO is similar to Tracematches' except that the properties are specified in a different formalism. J-LO also uses the same parametricity semantics as Tracematches. J-LO mainly focuses on checking at runtime properties rather than providing programming support. In J-LO, the temporal assertions are inserted into Java files as annotations that are then compiled into runtime checks. Both Tracematches and J-LO support parametric events, i.e., free variables can be used in the specified properties and will be bound to specific values at runtime for matching events.

The MOP framework has logic plugins, which encapsulate different logical formalisms and allow it to capture the capabilities of Tracematches and J-LO. JavaMOP is the instantiation of the MOP framework for Java programs (see Sect. 3.2).

JavaMOP allows for two different modes of matching traces, referred to as total trace matching and suffix trace matching. Total is the default mode of JavaMOP, while suffix mode is used by prefixing a JavaMOP property with the suffix modifier (see Fig. 7 and the accompanying text).

With total matching, e.g., with the pattern a\*b, a sequence of events abb will trigger the validation handler of the

generated MOP monitor only at the first b event and then the violation handler (if any) at the second b.

With suffix matching, however, the pattern will be matched twice, once for each b event: the first matches either the whole trace a b or the partial trace consisting of just the first b with zero occurrences of a, while the second matches the subsequent partial trace b (the second b in the trace) with zero occurrences of a; thus, the related advice will be executed twice.

With suffix matching, one can count matches of a pattern open close without a need to reset the monitor after each match, as would be required with total match monitoring. On the other hand, total trace matching is more suitable for runtime verification of formal properties, because it is the only semantics that makes sense for some logical formalisms, such as LTL, and thus many users expect this behavior for pattern languages like regular expressions and context-free grammars (CFGs), as well.

J-LO can be captured by the JavaMOP with total matching because LTL (see Sect. 6.3) is supported by the MOP framework. MOP supports regular expressions as part of its extended regular expression (ERE) logic plugin (see Sect. 6.2), and Tracematches may be captured by JavaMOP using these ERE patterns with suffix matching.

#### 1.1.2 Runtime verification

In runtime verification, monitors are automatically synthesized from formal specifications, and can be deployed offline for debugging, or online for dynamically checking properties during execution. MaC [43], PathExplorer (PaX) [31], Eagle [10], and RuleR [11] are runtime verification frameworks for logic based monitoring, within which specific tools for Java—Java-MaC, Java PathExplorer, and Hawk [24], respectively—are implemented. All these runtime verification systems work in outline monitoring mode and have hardwired specification languages: MaC uses a specialized language based on interval temporal logic, JPaX supports just LTL, and Eagle adopts a fixed-point logic. Java-MaC and Java PathExplorer integrate monitors via Java bytecode instrumentation, making them difficult to port to other languages. Our MOP approach supports inline, outline, and offline monitoring; allows one to define new formalisms to extend the MOP framework; and is adaptable to new languages (we discuss two such instances in this paper).

Temporal Rover [25] is a commercial runtime verification tool based on the future time metric temporal logic. It allows programmers to insert formal specifications in programs via annotations, from which monitors are generated. An automatic test generation (ATG) component is also provided to generate test sequences from logic specifications. Temporal Rover and its successor, DB Rover, support both inline and offline monitoring. However, they also have their

specification formalisms hardwired and are tightly bound to Java. MOP currently has no metric temporal logic plugin.

### 1.1.3 Design by contract

Design by Contract (DBC) [49] is a technique allowing one to add semantic specifications to a program in the form of assertions and invariants, which are then compiled into runtime checks. It was first introduced as a built-in feature of the Eiffel language [27]. Some DBC extensions have also been proposed for a number of other languages. Jass [12] and jContractor [1] are two Java-based approaches.

Jass is a precompiler which turns the assertion comments into Java code. Besides the standard DBC features such as pre-/post-conditions and class invariants, it also provides refinement checks. The design of trace assertions in Jass is mainly influenced by CSP [37], and the syntax is more like a programming language. jContractor is implemented as a Java library which allows programmers to associate contracts with any Java class or interface. Contract methods can be included directly within the Java class or written as a separate contract class. Before loading each class, ¡Contractor detects the presence of contract code patterns in the Java class bytecode and performs on-the-fly bytecode instrumentation to enable checking of contracts during the program's execution. ¡Contractor also provides a support library for writing expressions using predicate logic quantifiers and operators such as Forall, Exists, suchThat, and implies. Using iContractor, the contracts can be directly inserted into the Java bytecode even without the source code.

Java modeling language (JML) [44] is a behavioral interface specification language for Java. It provides a more comprehensive modeling language than DBC extensions. Not all features of JML can be checked at runtime; its runtime checker supports a DBC-like subset of JML. Spec# [8] is a DBC-like extension of the object-oriented language C#. It extends the type system to include non-null types and checked exceptions and also provides method contracts in the form of pre- and post-conditions as well as object invariants. Using the Spec# compiler, one can statically enforce non-null types, emit run-time checks for method contracts and invariants, and record the contracts as metadata for consumption by downstream tools.

We believe that the logics of assertions/invariants used in DBC approaches fall under the uniform format of our logic engines, so that an MOP environment following our principles would naturally support monitoring DBC specifications as a special methodological case. In addition, the MOP framework also supports outline monitoring, which we find important in assuring software reliability (e.g., monitoring for and detecting and fixing deadlocks) but which is not provided by any of the current DBC approaches that we are aware of.

#### 1.1.4 Other related approaches

Program query language (PQL) allows programmers to express design rules that deal with sequences of events associated with a set of related objects [46]. Both static and dynamic tools have been implemented to find solutions to PQL queries. The static analysis conservatively looks for potential matches for queries and is useful to reduce the number of dynamic checks. The dynamic analyzer checks the runtime behavior and can perform user-defined actions when matches are found. PQL has a "hardwired" specification language based on CFGs and supports only inline monitoring. CFGs can potentially express more complex languages than regular expressions, so in principle PQL can express more complex safety policies than Tracematches. The MOP CFG plugin described in Sect. 6.5 allows the MOP framework to specify most of the properties that may be specified in PQL.

Program trace query language (PTQL) [28] is a language based on SQL-like relational queries over program traces. The current PTQL compiler, Partiqle, instruments Java programs to execute the relational queries on the fly. PTQL events are timestamped and the timestamps can be explicitly used in queries. PTQL queries can be arbitrarily complex and, as shown in [28], PTQL's runtime overhead seems acceptable in many cases but we were unable to obtain a working package of PTQL and compare it in our experiments with JavaMOP because of license issues. PTQL properties are globally scoped and their running mode is inline. PTQL provides no support for recovery, its main use being to detect errors.

The PSL to Verilog compiler, P2V [45], is the sole attempt to perform runtime monitoring of *formal properties* in hardware, other than our BusMOP instance (see Sects. 3.3 and 5), of which we are aware. P2V is similar to BusMOP in that monitors are implemented in hardware rather than software, and that both approaches thus have no runtime overhead on the CPU. P2V, however, is more like the above approaches in that it is designed for monitoring actual programs rather than peripheral devices. Also it requires a dynamically extensible soft-core processor implemented on an FPGA, while our approach can potentially be applied to any COTS communication architecture. Further, P2V uses hardwired logic (PSL) while BusMOP allows different formalisms.

### 1.1.5 Discussion

All this research and associated tools show that runtime monitoring is an increasingly accepted, powerful, and beneficial approach for developing reliable software and hardware. Here we summarize the systems discussed above, and show how they may be classified in terms of the five orthogonal attributes of the MOP framework: programming language, logic, scope, running mode, and handlers. The programming

| Approach        | Language | Logic      | Scope  | Mode    | Handler     |

|-----------------|----------|------------|--------|---------|-------------|

| Hawk [25]       | Java     | Eagle      | global | inline  | violation   |

| J-Lo [16]       | Java     | ParamLTL   | global | inline  | violation   |

| Jass [13]       | Java     | assertions | global | inline  | violation   |

| JavaMaC [43]    | Java     | PastLTL    | class  | outline | violation   |

| jContractor [2] | Java     | contracts  | global | inline  | violation   |

| JML [44]        | Java     | contracts  | global | inline  | violation   |

| JPaX [32]       | Java     | LTL        | class  | offline | violation   |

| P2V [45]        | C, C++   | PSL        | global | inline  | validation/ |

|                 |          |            |        |         | violation   |

| PQL [46]        | Java     | PQL        | global | inline  | validation  |

| PTQL [29]       | Java     | SQL        | global | outline | validation  |

| Spec# [9]       | C#       | contracts  | global | inline/ | violation   |

|                 |          |            |        | offline |             |

| RuleR [12]      | Java     | RuleR      | global | inline  | violation   |

| Temporal        | C, C++   | , MiTL     | class  | inline  | violation   |

| Rover [26]      | Java,    |            |        |         |             |

|                 | Verilog  | ,          |        |         |             |

|                 | VHDL     |            |        |         |             |

| Tracematches [8 | ] Java   | Reg. Exp.  | global | inline  | validation  |

Fig. 1 Runtime monitoring breakdown

language determines what language the programs to be monitored must be written in. The logic specifies which formalism is used to specify the property. The scope determines where to check the property; it can be class invariant, global, interface, etc. The running mode denotes where the monitoring code runs; it can be inline (weaved into the code), online (operating at the same time as the program), outline (receiving events from the program remotely, e.g., over a socket), or offline (checking logged event traces). The handlers specify what actions to perform under exceptional conditions; there can be violation and validation handlers. It is worth noting that for many logics, violation and validation are not complementary to each other, i.e., the violation of a formula does not always imply the validation of the negation of the formula.

Most runtime monitoring approaches can be framed in terms of these attributes, while in the MOP framework they may be configured. Figure 1 lists the attributes for most of the software monitoring systems discussed above. For example, JPaX can be regarded as an approach that uses LTL to specify class-scoped properties, whose monitors work in offline mode and only detect violation.

This observation essentially motivates the design discipline of the MOP framework and specification language, namely that one should be allowed to choose the most appropriate logic and the most efficient monitoring algorithm for her/his own applications: while programming languages are designed and intended to be universal, logics and specifications tend to work best when they are domainspecific.

<sup>&</sup>lt;sup>1</sup> Offline implies outline, and inline implies online.

```

\texttt{full-binding connected decentralized SafeEnum}(\texttt{Vector}\,\overline{\texttt{v},\,\texttt{Enumeration e}})\,\{

Vector instanceV

Enumeration instanceE:

event createE after(Vector v) returning(Enumeration e) :

call(* Vector.elements()) && target(v)

{instanceE = e; instanceV

event updateV after(Vector v) :

(call(* Vector.add * (..)) || call(* Vector.remove(..))) && target(v)

{instanceV = v:}

event useE after(Enumeration e)

call(* Enumeration.nextElement()) && target(e)

\{instanceE = e:\}

fsm :

start

updateV -> start

createE -> enumCreated

enumCreated

useE -> enumCreated

updateV -> invalidEnum

invalidEnum

{\tt updateV} \to {\tt invalidEnum}

@fail {

{\tt System.out.println("Enumeration"} \ + \ {\tt \_MONITOR.instanceE}

"created from Vector" + __MONITOR.instanceV

+ "not used properly at " + _LOC);

```

Fig. 2 A JavaMOP Specification (SafeEnum)

### 1.2 Examples

Figure 2 shows an example specification using JavaMOP; recall that this is the MOP instance for Java programs (see Sects. 3.2 and 4). Detailed explanation of the specification syntax can be found in Sects. 3.1 and 3.2.1. This specification, called SafeEnum, describes the correct behavior of using Enumerations in Java. Essentially, this specification requires that an Enumeration created from a Vector not be used if the Vector has been updated since the Enumeration was created. This is important in legacy code that still uses Vectors and Enumerations because Java does not warn of this practice, it simply allows for non-deterministic results.

The specification is composed of five parts. The first line is the header of the specification, starting with three modifiers, full-binding, connected, and decentralized; the first states that monitor instances for this property should only raise failures when every parameter for the monitor instance has been bound (Sect. 4.4), the second states that the objects bound to the parameters must be connected by an event that actually occurs (Sect. 4.4), and the last chooses the way to index monitors for different parameter bindings (Sect. 4.3). An ID for the specification is given after modifiers and followed by parameters of the property; in this example, two parameters are used, namely a Vector object v and an Enumeration object e.

The second part contains the declaration of two monitor variables: instanceV and instanceE. Each monitor instance for each instantiation of the specification parameters has distinct monitor instance variables. Thus, they can be used for many purposes: logging, extra states for monitoring, statistics, and

so on. Here, they are used for bug reporting, to keep track of which Vector and Enumeration cause the failure.

The third part of the specification contains event declarations. Three events are defined: createE for the creation of an Enumeration, updateV for updates to a Vector, and useE for uses of an Enumeration. JavaMOP borrows (and extends; see Sect. 3.2) the syntax of AspectJ [41] for event declarations. For example, the createE event is declared to occur "after" a function call to the elements() method of class Vector. Note that the target clause is used to bind parameters in the event. Each event also sets one or both of the monitor variables, which will, again, be distinct for each binding of the parameters, using an *event action* (the Java code within the curly braces).

The fourth part of the specification is a formal description of the desired property. As discussed in Sect. 2, MOP is specification formalism independent, and one may choose different logics to specify properties. In this example, the property description begins with fsm, meaning that a finite state machine (FSM) is used, and continues with a finite state description of the monitor. Monitors for FSM properties are initially in the first state listed in the specification, in this case start. The monitor stays in the start state until an Enumeration is created from a given Vector. Once the Enumeration has been created, it is safe to use the Enumeration until such time as the underlying Vector is modified, at which point the invalidEnum state is entered. Using an Enumeration in the invalidEnum state will result in a failure of the property.

The last part of the specification consists of handlers to execute in different states of the corresponding monitor, such as pattern match or failure. In Fig. 2, the handler starts with @fail, defining the action, a simple warning in this case, to execute when the trace fails to match the pattern. The handler reports which Vector and Enumeration are used incorrectly, and the line number where the failure occurs (given by the MOP-reserved variable \_\_LOC). The \_\_MONITOR keyword is resolved to the monitor object by JavaMOP. This is needed because there is no way from the context to tell if a given variable reference refers to a variable declared locally or a monitor instance variable.

JavaMOP specifications are compiled into AspectJ [41] aspects. Specifications as short as the one in Fig. 2 compile into several hundred lines of AspectJ code. The generated aspect can then be weaved into a program one wishes to monitor, using any AspectJ compiler. Once weaved, simply running the program as normal results in a monitored run of the program.

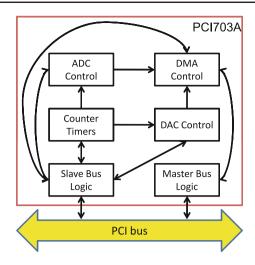

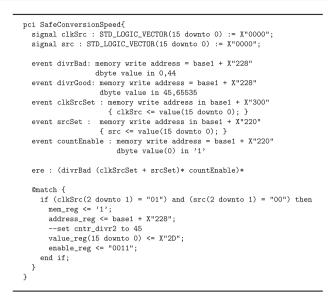

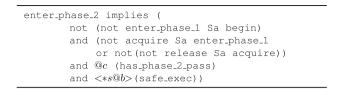

Figure 3 shows an example specification using BusMOP, the MOP instance for peripheral component interconnect (PCI) Bus monitoring (see Sects. 3 and 5). The main use for this instance is ensuring the proper use of peripherals connected to the PCI Bus. Improper use of peripherals may result from bugs in drivers or from misuse of the drivers by

```

pci SafeCounterModify{

STD_LOGIC_VECTOR(15 downto 0) := X"0000";

signal cntrlCurrent

signal cntrlOld : STD_LOGIC_VECTOR(15 downto 0) := X"0000"

event countDisable : memory write address = base1 + X"220"

dbyte value(0) in '0'

event cntrlMod : memory write address in base1 + X"220"

{cntrlOld <= cntrlCurrent; cntrlCurrent <= value(15 downto 0); }

event countEnable : memory write address = base1 + X"220"

dbvte value(0) in '1'

ere : ((countEnable countDisable) | cntrlMod | countDisable)*

@fail {

mem_reg <= '1':

address reg <= base1 + X"220"

value_reg(15 downto 0) <= cntrl0ld:

cntrlCurrent <= cntrlOld:

enable_reg <= "0011";

```

Fig. 3 A BusMOP specification (SafeCounterModify)

application programs. This specification, SafeCounterModify, states a desired property of the PCI703A digital-to-analog and analog-to-digital converter PCI board (ADC) [26]. The ADC has counters that are used to determine when input data are fully converted and ready to be placed on the PCI bus. The specification in Fig. 3 is concerned with the ADC's Counter 2. It requires that any modification to cntr\_cntrl2, the control register on the ADC for Counter 2, happens only while the Counter 2 is not enabled (running). Counter 2 is enabled when the 0th bit of cntr\_cntrl2 is set to '1'.

As in Fig. 2, the first line is the header of the specification. The keyword pci specifies that this property should generate bus listening code for the PCI bus. Again an ID naming the specification is provided. This time, because BusMOP does not have parameters, there is no parameter list.

The second part of the specification declares two signals, cntrlCurrent and cntrlOld, much like the monitor variables of Fig. 2, but BusMOP has no monitor instances, so there is only one copy of the variables. These variables are used to store the previous value of cntr\_cntrl2, which is the control register for Counter 2 on the ADC board. This is necessary because PCI bus properties cannot prevent incorrect behavior, but only detect and correct it. The stored value is used to restore the value of the register when the pattern fails to match (see below).

The third part of the specification contains event declarations, much like those in Fig. 2, but using an instrumentation language specific to PCI Bus traffic, rather than AspectJ. Three events are defined. The keyword dbyte used in each event tells BusMOP that the quantity will be 16 bits wide (i.e., double byte). Event countDisable occurs when cntr\_cntrl2, which is address X"220" in the address space of the ADC's address space), has its 0th bit (value(0)) set to '0', which disables Counter 2. The third event, countEnable, is analogous, but, as mentioned earlier, the bit is set to '1'. The event cntrl-Mod occurs when cntr\_cntrl2 is modified. The keyword in is used rather than = to define the address for cntrlMod. This is

because when no value for the read or write is specified, it is possible to check a whole range of addresses. Note that this event overlaps with countDisable and countEnable. The order of the events in Fig. 3 is significant because simultaneous events are handled by reporting them in the declared order (see Sect. 5). Each cntrlEnable saves the previous value of the register, so that it may be restored if the property is violated. The special variable value refers to the value of the data on the bus. A pipeline is kept where the previous value is stored to cntrlOld before cntrlCurrent receives the new bus value, so that the previous value may be recovered if the pattern fails (the event action occurs before the pattern is checked).

As in Fig. 2, the fourth part is a formal description of the desired property, this time using an ERE. This pattern specifies the desired behavior where all modifications must happen *after* disabling the counter (note again the order of event declarations, which ensures that the cntrlMod encountered from a countDisable is reported *after* the cntrlMod). The pair (countEnable countDisable) enforces that no changes can be made to cntrl\_cntrl2 while Counter 2 is enabled, other than disabling it.

The last part of the specification is the handler for a pattern failure, similar to SafeEnum. An assignment of '1' to the special variable mem\_reg alerts the system that a memory write is eminent. The address of the write is placed in address\_reg (note that it is the control register for Counter 2). The special variable value\_reg is the value to be written out by the monitor, and it is given the value of cntrlOld, which stores the previous value of cntr\_cntrl2. Lastly, the enable\_reg is specific to the PCI Bus interface (see Sect. 5).

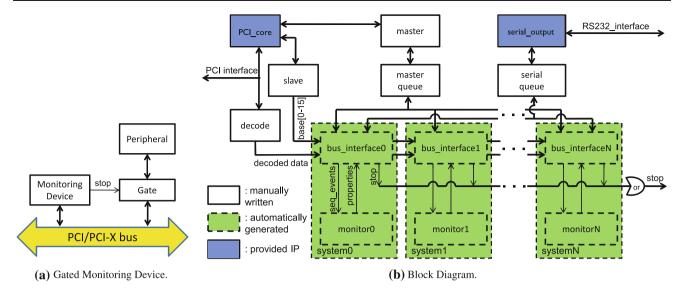

BusMOP specifications are compiled into hardware description language (HDL). As in JavaMOP, the size of the generated code is far greater than that of the original specification. The HDL code is compiled into an FPGA bitstream and programmed onto an FPGA that is inserted into an empty slot on the PCI bus of the system one wishes to monitor.

The examples given in Figs. 2 and 3 may monitor completely different properties in completely different problem domains, but they follow the same pattern and philosophy. By a clear separation of monitor generation and monitor integration, MOP provides fundamental and generic support for effective and efficient application of runtime monitoring in different problem domains, and can be understood from at least three perspectives:

- As a discipline allowing one to improve safety, reliability and dependability of a system by monitoring its requirements against its implementation at runtime;

- As an extension of programming languages with logics. One can add logical statements anywhere in the program, referring to past or future states of the program. These statements are like any other programming language boolean expressions, so they give the user a

- maximum of flexibility on how to use them: to terminate the program, guide its execution, recover from a bad state, add new functionality, etc.;

- 3. As a lightweight formal method. While firmly based on the logical formalisms and mathematical techniques, MOP's purpose is not program verification. Instead, the idea is to avoid verifying an implementation against its specification before operation, by not letting it go wrong at runtime.

Section 2 introduces the generic MOP framework. Section 3 discusses the two current language instances of MOP, giving a brief overview and describing their syntax. Section 4 presents topics specific to the efficient implementation of JavaMOP, as well as a thorough evaluation of JavaMOP, while Sect. 5 focuses on BusMOP. A performance evaluation of BusMOP (the MOP instance for monitoring PCI bus traffic) is unnecessary, as it has zero runtime overhead.<sup>2</sup>

#### 2 MOP framework

All monitoring systems share some features, such as program instrumentation and monitor integration, even when they aim at different domains or goals. MOP separates monitor generation and integration and provides a generic, extensible framework for runtime monitoring, allowing one to instantiate MOP with specific programming languages and specification formalisms to support different domains. In this section, we focus on the overall architecture of MOP.

### 2.1 Architecture

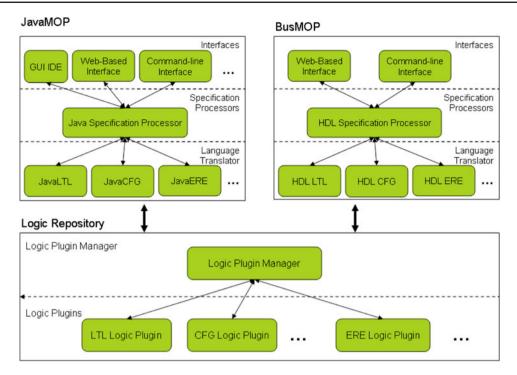

Figure 4 shows the architecture of MOP. There are two kinds of high level components in MOP, namely the logic repository and language clients. The logic repository, shown in the bottom of Fig. 4, contains various logic plugins and a logic plugin manager component. The logic plugin is the core component to generate monitoring code from formulae written in a specific logic; for example, the LTL plugin synthesizes state machines from LTL formulae. The output of logic plugins is usually pseudocode and not bound to any specific programming language. This way, the essential monitoring generation can be shared by different instances of MOP using different programming languages. The logic plugin manager bridges the communication between the language clients and the logic plugin. More specifically, it receives the monitor generation request from the language client and distributes the request to an appropriate plugin. After the plugin synthesizes the monitor for the request, the logic plugin manager

<sup>&</sup>lt;sup>2</sup> Overhead is exactly 0% if no recovery actions are performed. Recovery actions take up a tiny portion of the bus bandwidth, and could theoretically add non-zero runtime overhead. This was negligible in practice, even with continuously recovering properties.

Fig. 4 Architecture of MOP

collects the result and sends it back to the language client. This way, one can easily add new logic plugins into the repository to support new specification formalisms in MOP without changing the language client.

### 2.2 Language client

The language client hides the programming languageindependent logic repository and provides language specific support for the different MOP instances. Because the language client is the language-specific portion of an MOP instance, we occasionally refer to the language client by the name of the MOP instance to which it belongs. Language clients are responsible for all language-specific aspects of monitoring, such as instrumentation, parametricity, online/inline/ outline, modifiers, etc. They are usually composed of three layers: the bottom layer contains language translators that translate the abstract output of logic plugins into concrete code in a specific programming language; the middle layer is the specification processor, which extracts formulae from the given property specification and then instruments the generated monitoring code into the target program; finally, the top layer provides usage interfaces to the user.

We next explain in some detail the Java language client for the JavaMOP instance (which by abuse of terminology we will simply call JavaMOP). JavaMOP generates AspectJ [41] aspects from a specification. At the bottom layer, it has language translators for CFGs, the pseudocode output generated by the past time linear temporal logic with calls and returns plugin, and FSM descriptions. All plugins not mentioned use FSM descriptions as an output language. At the mid level, as mentioned, the Java client instruments the program with the generated monitor code by creating a stand-alone aspect that can be weaved into the program using any AspectJ compiler, such as ajc [6]. At the top level, there is a command line interface and a web-based interface. The two current MOP instances are discussed in Sect. 3, and, respectively, Sect. 4 (JavaMOP) and Sect. 5 (BusMOP), and the discussions essentially apply to the language clients associated with each instance.

## 2.3 Logic plugins

Every logic plugin implements and encapsulates a monitor synthesis algorithm for a particular specification formalism, such as the past-time linear temporal logic (PTLTL) and the CFG plugins supported in the current MOP framework (see Sect. 6 for a complete list of available plugins). The logic plugin accepts, as input, a set of events and a formula or pattern written in the underlying formalism and outputs an abstract monitor. This abstract monitor is usually a piece of pseudocode, which checks a trace of events against the given formula.

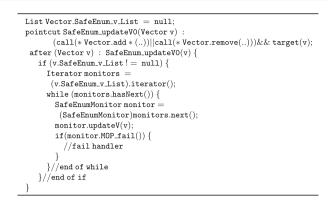

We next explain in some detail one particular plugin, the plugin for FSM specifications. Figure 5 shows the monitoring code generated by the MOP FSM plugin from the FSM specification in Fig. 2.

FSM monitors are simple, as one might expect. Static arrays keep the next state. There is one array for each event

```

//Declaration of monitor state

int state = 0;

static final int transition_createE[] = {2, 3, 3, 3};

static final int transition_updateV[] = {0, 1, 1, 3};

static final int transition_useE[] = {3, 3, 2, 3};

//Code for state update

state = transition_createE[state];

state = transition_updateV[state];

state = transition_useE[state];

//Code for category checks

Category_fail = state == 3;

```

Fig. 5 Java code for the FSM in Fig. 2

in the specification, as can be seen in Fig. 5. When an event arrives, the proper array is queried with the current state, and the next state is returned. After the state is updated, the category checks are preformed to see which handlers must run. Because the specification only checked @fail, we only have one check, which is for fail. As can be seen, fail is reached if the machine is in state 3. This code must be combined with generic code to handle the other properties of the specification, such as connectedness or full-binding, as well as the indexing system used for parametric trace slicing. The FSM plugin, as well as the others, is described in Sect. 6.

#### 3 MOP instances

As one may expect, when putting together various languages and specification formalisms, each with its own syntax and semantics, consistency and syntactic separation may become a non-trivial problem. In this section, we discuss the four dimensions that need to be instantiated in order to develop a new MOP instance (like JavaMOP or BusMOP), how they are instantiated, and where the boundary between the various components of an instance is. Since the semantics of the various pieces is typically implicit and not formally defined, in what follows we place emphasis on syntax.

## 3.1 MOP syntax

Every MOP instance needs to instantiate the MOP framework in four dimensions: (1) a specification language based on the problem domain, which is mainly related to how one defines events in the domain; (2) a target language for generated monitors; (3) supported logic plugin specification formalisms; and (4) the handlers allowed in the specification. Two MOP instances have been implemented and experimented with at this point: JavaMOP and BusMOP. We expect to see more MOP instances in the future because many problem domains can benefit from monitoring.

Each instance of MOP uses an instance of the generic MOP syntax. The syntax of any instance of MOP can be generated by defining certain syntactic categories (non-terminals) of the MOP grammar, which can be seen in Fig. 6. All of the grammars used to define MOP syntax in this article use Extended Backus-Naur Form (EBNF) [39]. Non-

terminals in the grammars are surrounded by "(" and ")". Braces ("{" and "}") enclose portions of the grammar that may appear zero or more times. Brackets ("[" and "]") enclose portions of the grammar that are optional (i.e., it may or may not appear). Concrete examples of the syntax defined below can be seen in Figs. 2 and 3.

#### 3.1.1 Shared syntax

The following syntax constructs are shared by different MOP instances:

- (Specification): (Specification) describes the generic MOP specification syntax which can be instantiated for MOP language instances and MOP logic plugins.

- \(\langle Event\rangle\): The \(\langle Event\rangle\) declaration code allows for the definition of events, which may then be referred to in the property (see \(\langle Property\rangle\) below). Event declarations can also have arbitrary code associated with them \(\langle Instance Action\rangle\)), which is run when the event is observed \(\langle (Instance Event Definition\rangle\)), e.g. code to modify the program or the monitor state. For manual indication of events that can start a trace, the keyword creation is used at the beginning of each declaration.<sup>3</sup>

- \(\bar{Property}\): Every MOP specification may contain zero or more properties. A \(\bar{Property}\) consists of a named formalism (\(\lambda Logic Name\rangle\)), followed by a colon, followed by a property specification using the named formalism (see \(\lambda Logic Syntax\rangle\) below) and usually referring to the declared events. If the property is missing, then the MOP specification is called \(rangle\) Raw specifications are useful when no existing logic plugin is powerful or efficient enough to specify the desired property; in that case, one embeds the custom monitoring code manually within the \(\lambda Instance Action\rangle\) code.

- (Property Handler): Handlers contain arbitrary code from the instance source language, and are invoked when a certain logic state (see (Logic State) below) or category is reached, e.g., match, fail, or a particular state in a FSM description.

## 3.1.2 Instance-specific syntax

The following constructs are based on the particular instance of MOP used for a particular specification. More information on the instances of MOP can be found in the remainder of this section, and Sect. 4 (JavaMOP) and 5 (BusMOP).

(Instance Modifier): (Instance Modifier)s are specific to each language instance of MOP. Syntactically, they can be any valid identifier restricted by the given language. They change the behavior of the monitoring code.

<sup>&</sup>lt;sup>3</sup> The creation keyword has no effect in BusMOP specifications.

#### Shared syntax

```

\langle Specification \rangle ::= \{ \langle Instance\ Modifier \rangle \} \langle Id \rangle \langle Instance\ Parameters \rangle " \{ \} \}

\{\langle Instance\ Declaration \rangle\}

\{\langle Event \rangle\}

\{\langle Property \rangle

\{\langle Property\ Handler\rangle\}

\langle Event \rangle ::= ["creation"]" event" \langle Id \rangle \langle Instance Event Definition \( \) "\{" \land Instance Action \( \) "\{" \}"

\langle Property \rangle ::= \langle Logic\ Name \rangle ":" \langle Logic\ Syntax \rangle

⟨Property Handler⟩ ::= "@" ⟨Logic State⟩ ⟨Instance Handler⟩

Instance-specific syntax

\langle Instance\ Modifier \rangle ::= \langle Id \rangle

\langle Instance\ Parameters \rangle ::= \langle JavaMOP\ Parameters \rangle \mid \langle BusMOP\ Parameters \rangle \mid ...

\langle Instance\ Declaration \rangle ::= \langle JavaMOP\ Declaration \rangle \mid \langle BusMOP\ Declaration \rangle \mid ...

\langle Instance\ Event\ Definition \rangle ::= \langle JavaMOP\ Event\ Definition \rangle \mid \langle BusMOP\ Event\ Definition \rangle \mid ...

\langle Instance\ Action \rangle ::= \langle JavaMOP\ Event\ Action \rangle \mid \langle BusMOP\ Event\ Action \rangle \mid ...

\langle Instance\ Handler \rangle ::= \langle JavaMOP\ Event\ Handler \rangle \mid \langle BusMOP\ Event\ Handler \rangle \mid ...

Logic-plugin-specific syntax

\langle Logic\ Name \rangle ::= \langle Id \rangle

\langle Logic\ Syntax \rangle ::= \langle FSM\ Syntax \rangle \mid \langle ERE\ Syntax \rangle \mid \langle LTL\ Syntax \rangle \mid \langle PTLTL\ Syntax \rangle \mid \langle CFG\ Syntax \rangle \mid \langle PTCaRet\ Syntax \rangle \mid ...

\langle Logic\ State \rangle ::= \langle FSM\ State \rangle \mid \langle ERE\ State \rangle \mid \langle LTL\ State \rangle \mid \langle PTLTL\ State \rangle \mid \langle CFG\ State \rangle \mid \langle PTCaRet\ State \rangle \mid ...

```

Fig. 6 MOP syntax

- (Instance Parameters): Allow one to define the parameters of a parametric specification using the language corresponding to the MOP instance. Not all MOP instances are parametric (e.g., BusMOP), however, so this non-terminal may be empty.

- (Instance Declaration): (Instance Declaration)s are specific to each language instance of MOP. They allow for the declaration of monitor local variables.

- (Instance Event Definition): (Instance Event Definition)s

are specific to each language instance of MOP. They

define the conditions under which an event is triggered.

- (Instance Action): An event can have arbitrary code associated with it, called an action. The action is run when the event is observed. An action can modify the program or the monitor state, and the syntax of the allowed statements are dependent upon the MOP instance in question. Typically, the statements used in actions have different variables and functions that may be referred to than handlers. This is why different non-terminals are used for actions and handlers.

- (Instance Handler): (Instance Handler)s are arbitrary code that is executed when a property handler is triggered.

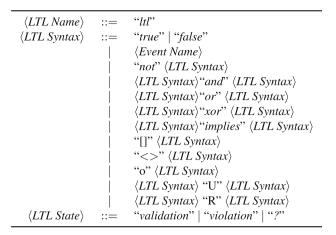

#### 3.1.3 Logic-plugin-specific syntax

The following constructs are based on the logic plugin(s) used in a particular specification. More information on logic plugins can be found in Sect. 6.

- \(\lambda Logic Name \rangle\): An identifier to indicate in which logic a property is defined.

- \(\lambde Logic Syntax \rangle\): This refers to the syntax of the actual property definition, and is defined in the syntax section for each plugin.

- \(\lambda Logic State \rangle\): \(\lambda Logic State \rangle\)s are constants defined for each plugin, stating for which monitor states or categories (match, fail, etc.) a handler may be written.

### 3.2 The JavaMOP instance

JavaMOP is an MOP development tool for Java, supporting several logical formalisms and a general specification language using them to describe Java program behaviors [21]. It compiles property specifications into optimized monitoring code. The generated code uses AspectJ [41], and is currently<sup>4</sup> program-independent. For example, a user can write a JavaMOP specification for a library. Then, JavaMOP generates monitoring code for this specification. This code can be applied to any program that uses the library.

In JavaMOP, an event corresponds to a pointcut, which an AspectJ compiler (such as ajc [6]) can use to weave monitoring code into the original program. Pointcuts include function call, function return, function begin, function end, field assignment, object creation, and more complex ones

$<sup>^4</sup>$  We intend to incorporate program static analysis to further reduce runtime overhead soon [16].

with pointcut operators, which combine multiple simpler pointcuts. JavaMOP generates monitoring code for each pointcut—corresponding to an event in a JavaMOP specification—to maintain monitoring state, to check if the program conforms to the specification, and to trigger a handler if appropriate.

A system behavior can be described using one of several logical formalisms supported by JavaMOP, including all those described in Sect. 6. A specification will be interpreted by the logic repository, a generic server used by all instances of MOP, and transformed into generic monitor code as mentioned in Sect. 2. JavaMOP translates the monitor pseudocode to AspectJ code. Any logic which can be translated to FSM (ERE, LTL, PTLTL) are reported to JavaMOP using the MOP FSM plugin syntax to reduce the number of translation algorithms necessary in JavaMOP (see Sect. 6.1).

A user can write a handler in Java for each monitoring state. There can be more monitoring states than simple match and fail, depending on logical formalism. A handler can be used for logging, recovering, blocking, or any other purpose. Since handlers are specified as arbitrary Java code, a user has quite a bit of latitude to achieve his or her purposes.

### 3.2.1 JavaMOP syntax

The syntax of JavaMOP is discussed below, as an instance of the generic MOP syntax defining the relevant modifiers and language-specific syntax (Java for declarations and event/hand- ler actions, enriched with AspectJ for event definitions). The formal syntax can be seen in Fig. 7. Anything not explicitly described below can be considered to be identical to the generic MOP syntax. Note that some non-terminals such as ⟨*Event*⟩ refer to language instance specific non-terminals, which are defined below for JavaMOP.

(JavaMOP Modifier): The three binding modifiers refer to the different binding modes described in Sect. 4.4, the default is any-binding. The modifier "unsynchronized" tells JavaMOP that the monitor state needs not be protected against concurrent accesses; the default is synchronized. The unsynchronized monitor is faster, but may suffer from races on its state updates if the monitored program has multiple threads. The "decentralized" modifier refers to decentralized monitor indexing. The default indexing is centralized, meaning that the indexing trees needed to quickly access and garbage-collect monitor instances are stored in a common place; decentralized indexing means that the indexing trees are scattered all over the code as additional fields of objects of interest. Decentralized indexing typically yields lower runtime overhead, though it may not always work for all settings. More information on indexing can be found in Sect. 4.3.

The "perthread" modifier causes JavaMOP to consider events from each thread as though from separate runs of the program, (i.e., one parametric monitor for each thread monitors only events from its own thread). The "suffix" modifier causes JavaMOP to consider a trace as matching if any suffix of that trace would match.

- (JavaMOP Parameters) and (JavaMOP Declaration) These are ordinary Java parameters (as used in methods) and Java declarations. The former are the parameters of the JavaMOP specification and the latter are additional local monitor variables that one can access and modify in both event actions and property handlers. Each parameter from (JavaMOP Parameters) should be used in at least one event of the specification.

- (JavaMOP Action), ( JavaMOP Handler), and (Java-MOP Event Definition): (JavaMOP Action) are normal Java statements that may also refer to monitor local variables. (JavaMOP Handler), however, slightly extends Java with three special variables:

- \_\_RESET: a special expression (evaluates to void) that resets the monitor to its initial state, but does not affect any user defined variables of the monitor;

- \_LOC: a string variable that evaluates to the line number generating the current event;

- \_MONITOR: a special variable that evaluates to the current monitor object, so that one can read/write monitor variables.

Similarly, the advice used to define JavaMOP events slightly extends the AspectJ advice syntax. The \(\langle Java-MOP \) Event Definition\(\rangle\) follows the AspectJ syntax except for its extension with \(\langle JavaMOP \) Pointcut\(\rangle\), which can only be added in a top-level conjunct context. \(\langle AspectJ \) Pointcut\(\rangle\) and \(\langle AspectJ \) AdviceSpec\(\rangle\) are both standard AspectJ syntax [6]. The additional pointcuts have the following meaning:

- "thread": The thread pointcut captures the current thread and takes an identifier as a parameter. The identifier can be a class name or a variable name. For the former, the type of the captured thread should be a sub-class of the given class to trigger the event. For the latter, the captured thread is bound to the variable. The thread pointcut allows for the easy specification of properties which are parameterized by the current thread of execution.

- "condition": The condition pointcut takes a boolean expression as a parameter. An event containing a condition pointcut is not triggered if the boolean expression evaluates to false. This differs only from the if pointcut in standard AspectJ in that monitor instance variables may be used in the conditional expression.

```

\langle JavaMOP\ Modifier \rangle ::= "full-binding" | "maximal-binding" | "any-binding" | "connected" | "unsynchronized" | "insynchronized" | "insynchroniz

"decentralized" | "perthread" | "suffix"

\langle JavaMOP\ Parameters \rangle ::= "("[\{\langle JavaMOP\ Type \rangle\ \langle Id \rangle\ ","\}\ \langle JavaMOP\ Type \rangle\ \langle Id \rangle\}]")"

⟨JavaMOP Declaration⟩ ::= syntax of declarations in Java

\langle \textit{JavaMOP Event Definition} \rangle ::= \langle \textit{AspectJ AdviceSpec} \rangle ":"

⟨AspectJ Pointcut⟩ ["&&" ⟨JavaMOP Pointcut⟩]

\langle JavaMOP\ Pointcut \rangle ::= "thread" "(" \langle Id \rangle ")"

"condition" "(" \( BooleanExpression \) ")"

⟨AspectJ Pointcut⟩

⟨JavaMOP Pointcut⟩ "&&" ⟨JavaMOP Pointcut⟩

⟨AspectJ Pointcut⟩ ::= syntax of Pointcut in AspectJ

⟨AspectJ AdviceSpec⟩ ::= syntax of AdviceSpec in AspectJ

\langle TypeList \rangle ::= list of Exception types in Java

\langle Boolean \ Expression \rangle ::= \langle Id \rangle \mid "!" \langle Boolean \ Expression \rangle

⟨Boolean Expression⟩ ⟨Boolean Operator⟩ ⟨Boolean Expression⟩ | "(" ⟨Boolean Expression⟩ ")"

⟨Boolean Operator⟩ ::= " || " | "&&" | " | " &" | " == " | "! = "

\langle JavaMOP \ TypeList \rangle ::= "("[\{\langle JavaMOP \ Type \rangle ","\} \ \langle JavaMOP \ Type \rangle]")"

⟨JavaMOP Action⟩ := Java statements, which may refer to monitor local variables

\langle JavaMOP\ Handler \rangle := Java statements with additional keywords

\langle JavaMOP Type \rangle := Any valid Java type

```

Fig. 7 JavaMOP syntax

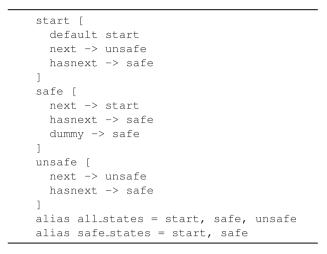

#### 3.3 The BusMOP instance

BusMOP [52] was designed to address the safety problem of third party consumer off-the-shelf (COTS) components. The complexity of safety critical systems has grown to the point where the ability to use COTS in a safe manner is almost mandatory. In addition, the vast majority of OS crashes in PCs are caused by faulty peripherals or their drivers. BusMOP answers both of these problems by allowing the specification and monitoring of properties with respect to PCI Bus traffic (soon to be expanded to other bus architectures).

In BusMOP, the events correspond to reads and writes of specified values to specified memory locations on the bus. PCI Bus interrupts are also allowed as events. The monitors, and the logic to extract events from bus traffic, are synthesized from hardware design language (HDL) code and programmed onto a field programmable gate array (FPGA), which is plugged into the PCI Bus.

BusMOP supports the FSM, ERE, LTL, and PTLTL plugins of MOP (see Sect. 6). PTCaRet and CFG have the problem of unbounded logic response time, which would cause the monitor to not meet timing constraints in some cases, and are thus not suitable for inclusion in BusMOP. It is also not clear exactly where the structured capabilities of these logics are useful when considering flat bus traffic traces.

Handlers in BusMOP can be specified using arbitrary VHDL code. Several resources are provided for the user for use in handler code, such as serial output for logging, and the actual ability to write to the PCI Bus to perform recovery. Recovery actions in BusMOP require bus arbitration to undo deleterious actions of faulty peripherals or their drivers.

This bus arbitration is the only possible overhead incurred by BusMOP, in cases of heavy Bus traffic. In the majority of systems, BusMOP can be used with no runtime overhead.

### 3.3.1 BusMOP syntax

Below we discuss the BusMOP syntax. Anything not explicitly described below can be considered to be identical to the generic MOP syntax. Note that some non-terminals such as *(Event)* refer to language instance specific non-terminals, which are defined below for BusMOP. The grammar for the syntax can be seen in Fig. 8.

- \(\begin{align\*} \BusMOP \text{ Modifiers} \): Modifiers in BusMOP are used to distinguish the bus architecture to be monitored. Currently, only standard parallel PCI is supported. PCI-E will be supported using a bridge adapter that will sit between the PCI Express bus slot and the peripheral to monitor.

- \( \lambda BusMOP \) Parameters\( \rangle \) and \( \lambda BusMOP \) Declaration\( \rangle \):

BusMOP is not parametric because there is no clear unit of parametrization. \( \lambda BusMOP \) Declaration\( \rangle \)'s are standard VHDL signal declarations. These are used to define additional local monitor variables that one can access and modify in both event actions and property handlers.

- (BusMOP Event Definition): BusMOP event definitions use an original syntax to define interesting potential bus traffic. At the basic level there are three types of events: memory, IO, and interrupt. The last event is triggered when there is an interrupt on the bus. The first two are further subdivided into reads and writes. The difference between memory and IO is the address space of the read

```

\langle BusMOP\ Modifier \rangle ::= "pci"

\langle BusMOP\ Parameters \rangle ::= \epsilon \text{ (i.e., none)}

\langle BusMOP\ Declaration \rangle ::= syntax of declarations in VHDL

\langle BusMOP\ Event\ Definition \rangle ::= ":" \langle Memory\ or\ IO \rangle \langle Read\ or\ Write \rangle "address" "= " \langle Arithmetic\ Op \rangle

"value" ["(" (Index) ")"] ["not"] "in" (Range) "{" [(BusMOP Action)] "}"

": " (Memory or IO) (Read or Write) "address" "in" (Range)

"interrupt" "{" [\langle BusMOP Action \rangle] "}"

\langle Memory \ or \ IO \rangle ::= "memory" | "io"

\langle Read\ or\ Write \rangle ::= "read" | "write"

\langle Range \rangle ::= \langle Arithmetic Op \rangle ["," \langle Arithmetic Op \rangle]

\langle Arithmetic Op \rangle ::= \langle Number \rangle \mid \langle ID \rangle

\langle Arithmetic Op \rangle " + " \langle Arithmetic Op \rangle

\langle Arithmetic Op \rangle "&" \langle Arithmetic Op \rangle

\langle Arithmetic Op \rangle " — " \langle Arithmetic Op \rangle

"(" (Arithmetic Op) ")"

\langle Number \rangle ::= \langle VHDL \ number \ or \ bitstring \rangle

\langle ID \rangle ::= \langle VHDL \ identifier \rangle

\langle BusMOP\ Action \rangle := Bus\ statements, which may refer to monitor local variables

\langle BusMOP \ Handler \rangle := Bus \ statements, which may refer to monitor local variables, with additional output variables

```

Fig. 8 BusMOP syntax

or write in question. This is important for correctly specifying the necessary bus enable signals in the generated code. Reads and writes can be concerned with the read or write of a specific location with a select range of values, or a read or write to a range of locations where the value is of no concern. Specifying a range of read or write addresses is valuable for enforcing memory safety policies (such as, if the value 0xdeadbeef is written to address 0xffff0000 then allow no writes to some buffer until 0x000000 is written to 0xffff0000).  $\langle Arithmetic Op \rangle$  allows for arithmetic operations combining variables and literal numbers. This is useful both for specifying monitor local variables and monitor input variables. Placing a numerical index on the keyword "value" indicates that one bit, specified by the index, should be checked rather than the whole value read or written. The monitor input variables hold the values of inputs to the monitor, and are as follows:

- The value register holds the value of the read or write in question.

- The address register holds the address of the read or write in question.

- The baseN registers allow a user to specify a memory value relative to a given peripheral. Without this support monitoring would be very difficult due to the plug-and-play PCI bus interface that assigns memory spaces to peripherals at boot time.

- \( \lambda BusMOP Action \rangle \): Actions are arbitrary VHDL statements that may refer to monitor local variables as well as the input variables described above in \( \lambda BusMOP Event Definition \rangle \). As mentioned in \( \lambda Instance Action \rangle \), these statements are executed when the event for which they are defined is observed.

- \(\langle BusMOP Handler \rangle :\) Handlers are arbitrary VHDL statements that may refer to monitor local variables as well as the input variables described above in \(\langle BusMOP Event Definition \rangle .\) In addition, there are variables the may be set in order to perform recovery actions. They are as follows:

- The io\_reg is used to specify a read or write to I/O space. It is asserted as '1' to select the I/O space.

- The mem\_reg is used to specify a read or write to memory space by asserting it as '1'.

- The address\_reg is used to specify the 32 bit address of a read or write.

- The value\_reg is used to specify the value of a 32 bit read or write.

- The enable\_reg is used to specify the byte enables for a read or write (specific to PCI, see Sect. 5).

- The serial\_reg allows output of an ASCII value to a serial port for debugging.

- The stop\_reg register that stops the peripheral in question from reading from or writing to the PCI bus when it is asserted as '1'.

As mentioned in *(Instance Handler)* these statements are executed when a property handler is triggered.

### 4 JavaMOP

Each instance of MOP has issues specific to its domain. Java-MOP must deal with the complexities of parametric monitoring, in order to make itself useful in highly object-oriented systems. We first provide an introduction to parametric trace slicing (Sect. 4.1). We next cover improving the efficiency

of parametric monitoring (4.2). Lastly, we discuss different modes of parameter binding, which define which parameter instance monitors trigger handlers (Sect. 4.4).

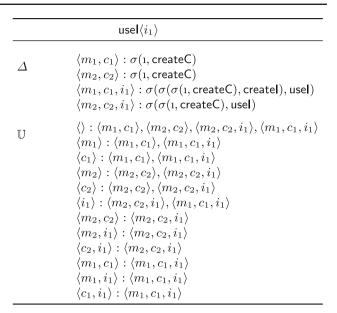

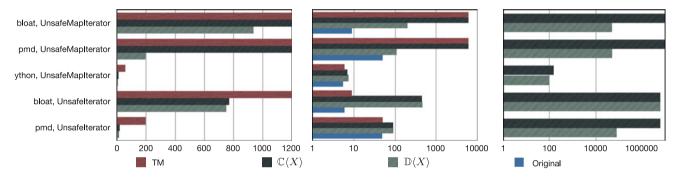

### 4.1 Parametric trace slicing and naive monitoring

Parametric specifications are widely used in practice, particularly in object oriented languages, like Java, where we need to describe properties over a group of objects. For example, consider again the property in Fig. 2 from Sect. 1. Here the events are parametrized by the Vector v and the Enumeration e. This is because we do not want uses of an Enumeration  $e_1$  to be flagged as an error because of an intervening modification to Vector  $v_2$ , when it has Vector  $v_1$  as its underlying Vector.

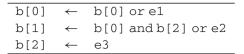

When monitoring a parametric specification, the observed execution trace is parametric, i.e., the events in the trace come with parameter information. For example, a possible parametric trace for the specification in Fig. 2 is: updateV $\langle v \mapsto v_1 \rangle$  createE $\langle v \mapsto v_1, e \mapsto e_1 \rangle$  createE $\langle v \mapsto v_1, e \mapsto e_2 \rangle$  createE $\langle v \mapsto v_2, e \mapsto e_3 \rangle$  useE $\langle e \mapsto e_3 \rangle$  useE $\langle e \mapsto e_1 \rangle$  updateV $\langle v \mapsto v_1 \rangle$  useE $\langle e \mapsto e_2 \rangle$ .

Every event in this trace is associated with a concrete parameter binding, such as  $\langle v \mapsto v_1, e \mapsto e_2 \rangle$  that indicates that the parameters v and e in Fig. 2 are bound to concrete objects  $v_1$  and  $e_2$ , respectively. Such a parametric trace represents a set of non-parametric traces each of which corresponds to a particular parameter binding. For example, the above trace contains 11 non-parametric traces for 11 parameter bindings (one for each of five singleton objects, and one for each element in the cross product of the singleton objects). The non-parametric traces for four of these bindings are summarized in the table below.

| Parameter binding                              | Non-parametric trace slice        |

|------------------------------------------------|-----------------------------------|

| $\langle v \mapsto v_1 \rangle$                | updateV updateV                   |

| $\langle v \mapsto v_1, e \mapsto e_1 \rangle$ | updateV createE useE updateV useE |

| $\langle v \mapsto v_1, e \mapsto e_2 \rangle$ | updateV createE updateV useE      |

| $\langle v \mapsto v_2, e \mapsto e_3 \rangle$ | createE useE                      |

The second and third of these fail to match the pattern in Fig. 2, thus two failures are produced. It is highly non-trivial to monitor parametric specifications efficiently since there can be a tremendous number of parameter bindings during a single execution. For example, in a few experiments that we carried out, millions of parameter bindings were created [22]. Most other approaches for monitoring parametric specifications handle parameters in a logic-specific way [3,15,46], i.e., they extended the underlying specification formalisms with parameters and devised algorithms for the extended formalism. Such a solution results in very complicated monitor synthesis algorithms and makes it difficult to support new problem domains. In MOP, parameters are handled in a completely logical formalism independent manner and separated from the monitor synthesis process, vastly simplifying the

implementation of new logic plugins. Surprisingly, this logic independent consideration of parameters turns out to be more efficient than those closely coupled systems (see Sect. 4.5) thanks to the clean separation of concerns. In the following sections, we will explain parametric monitoring in more detail.

### 4.1.1 Events, traces, properties, and parameters

First, we introduce the notions of event, trace and property, first non-parametric and then parametric. Trace slicing is then defined as a reduct operation that forgets the events that are unrelated to the given parameter instance. Most of this discussion is derived from [23].

**Definition 1** Let  $\mathcal{E}$  be a set of (non-parametric) events, called **base events** or simply **events**. An  $\mathcal{E}$ -trace, or simply a (non-parametric) **trace** when  $\mathcal{E}$  is understood or not important, is any finite sequence of events in  $\mathcal{E}$ , that is, an element in  $\mathcal{E}^*$ . If event  $e \in \mathcal{E}$  appears in trace  $w \in \mathcal{E}^*$  then we write  $e \in w$ .

Example Consider again the SafeEnum policy from Fig. 2.  $\mathcal{E} = \{\text{createE}, \text{updateV}, \text{useE}\}\$ and execution traces corresponding to this are sequences of the form createE useE updateV createE useE, etc. For now we ignore the distinction between "good" and "bad" execution traces.

**Definition 2** An  $\mathcal{E}$ -property P, or simply a (base or non-parametric) **property**, is a function  $P: \mathcal{E}^* \to \mathcal{C}$  partitioning the set of traces into categories  $\mathcal{C}$ . It is common, but not enforced, that  $\mathcal{C}$  includes "match", "fail", and "don't know" (or "?") categories. In general,  $\mathcal{C}$ , may be any set and is referred to as the set of *verdict categories* when it eases readability.

Example Consider again Fig. 2. The FSM has no match category as we did not define it. The fail category is reached by "falling off the machine", i.e., receiving an event in a state for which there is no transition. For example, the trace createE updateV useE would result in the fail category.

We next extend the above definitions to the parametric case, i.e., traces containing events that carry concrete data instantiating abstract parameters.

Example Event useE is parametric in the Enumeration; if e is the name of the generic Enumeration parameter and  $e_1$  and  $e_2$  are concrete Enumerations, then parametric useE events have the form  $useE\langle e\mapsto e_1\rangle$ ,  $useE\langle e\mapsto e_2\rangle$ , etc.

In what follows, let  $[A \rightarrow B]$  be the set of total functions and  $[A \rightarrow B]$  be the set of partial functions, both from A to B.

**Definition 3** (Parametric events and traces) Let X be a set of parameters and let V be a set of corresponding parameter values. If  $\mathcal{E}$  is a set of base events like in Definition 1, then

let  $\mathcal{E}\langle X \rangle$  be the set of corresponding *parametric events*  $e\langle \theta \rangle$ , where e is a base event in  $\mathcal{E}$  and  $\theta$  is a partial function in  $[X \rightarrow V]$ . A *parametric trace* is a trace with events in  $\mathcal{E}\langle X \rangle$ , that is, a word in  $\mathcal{E}\langle X \rangle^*$ .

To simplify writing, we occasionally assume the parameter values set V implicit.

*Example* A parametric trace for our property in Fig. 2 can be: updateV $\langle v \mapsto v_1 \rangle$  createE $\langle v \mapsto v_1, e \mapsto e_1 \rangle$  createE $\langle v \mapsto v_1, e \mapsto e_2 \rangle$  createE $\langle v \mapsto v_2, e \mapsto e_3 \rangle$  useE $\langle e \mapsto e_3 \rangle$  useE $\langle e \mapsto e_1 \rangle$  updateV $\langle v \mapsto v_1 \rangle$  useE $\langle e \mapsto e_1 \rangle$  useE $\langle e \mapsto e_2 \rangle$ .

We take the freedom to only list the parameter values when writing parameter instances, that is,  $\langle v_1 \rangle$  instead of  $\langle v \mapsto v_1 \rangle$ . With this notation, the above trace is:

update $V\langle v_1 \rangle$  create $E\langle v_1, e_1 \rangle$  create $E\langle v_1, e_2 \rangle$  create $E\langle v_2, e_3 \rangle$  use $E\langle e_3 \rangle$  use $E\langle e_1 \rangle$  update $V\langle v_1 \rangle$  use $E\langle e_1 \rangle$  use $E\langle e_2 \rangle$ .

As mentioned earlier, this trace induces *eleven trace slices*. The slice corresponding to  $\langle v_1, e_1 \rangle$  is updateV createE useE updateV useE.  $\square$

**Definition 4** Partial functions  $\theta$  in  $[X \rightarrow V]$  are called *parameter instances*.  $\theta$ ,  $\theta' \in [A \rightarrow B]$  are *compatible* if for any  $x \in \mathsf{Dom}(\theta) \cap \mathsf{Dom}(\theta')$ ,  $\theta(x) = \theta'(x)$ . We can *combine* compatible instances  $\theta$  and  $\theta'$ , written  $\theta \sqcup \theta'$ , as follows:

$$(\theta \sqcup \theta')(x) = \begin{cases} \theta(x) & \text{when } \theta(x) \text{ is defined} \\ \theta'(x) & \text{when } \theta'(x) \text{ is defined} \\ \text{undefined} & \text{otherwise} \end{cases}$$

$\theta \sqcup \theta'$  is also called the *least upper bound* (*lub*) of  $\theta$  and  $\theta'$ .  $\theta$  is *less informative* than  $\theta'$ , or  $\theta'$  is *more informative* than  $\theta$ , written  $\theta \sqsubseteq \theta'$ , if for any  $x \in X$ , if  $\theta(x)$  is defined then  $\theta'(x)$  is also defined and  $\theta(x) = \theta'(x)$ .

**Definition 5** (*Trace slicing*) Given parametric trace  $\tau \in \mathcal{E}\langle X \rangle^*$  and  $\theta$  in  $[X \rightarrow V]$ , let the  $\theta$ -trace slice  $\tau \upharpoonright_{\theta} \in \mathcal{E}^*$  be the non-parametric trace defined as:

$$\begin{array}{ll} - & \epsilon {\upharpoonright}_{\theta} = \epsilon, \text{ where } \epsilon \text{ is the empty trace/word, and} \\ - & (\tau \; e \langle \theta' \rangle) {\upharpoonright}_{\theta} = \left\{ \begin{array}{ll} (\tau {\upharpoonright}_{\theta}) \, e & \text{when } \theta' \sqsubseteq \theta \\ \tau {\upharpoonright}_{\theta} & \text{when } \theta' \not\sqsubseteq \theta \end{array} \right. \end{array}$$

The trace slice  $\tau \upharpoonright_{\theta}$  first filters out all the parametric events that are not relevant for the instance  $\theta$ , i.e., which contain instances of parameters that  $\theta$  does not care about, and then, for the remaining events relevant to  $\theta$ , it forgets the parameters so that the trace can be checked against base, non-parametric properties. It is crucial to discard events for parameter instances that are not relevant to  $\theta$  during the slicing, including those more informative than  $\theta$ , in order to achieve a "proper" slice for  $\theta$ : in our running example, the trace slice for  $\langle v_1 \rangle$  should contain only updateV events and no createE or useE events.

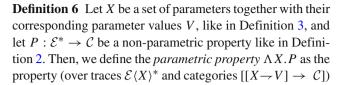

$$\Lambda X.P : \mathcal{E}\langle X \rangle^* \to [[X \to V] \to \mathcal{C}]$$

defined as  $(\Lambda X.P)(\tau)(\theta) = P(\tau|_{\theta})$  for any  $\tau \in \mathcal{E}\langle X \rangle^*$  and any  $\theta \in [X \rightarrow V]$ . If  $X = \{x_1, \ldots, x_n\}$  we may write  $\Lambda x_1, \ldots, x_n.P$  instead of  $(\Lambda \{x_1, \ldots, x_n\}.)P$ . Also, if  $P_{\varphi}$  is defined using a pattern or formula  $\varphi$  in some particular trace specification formalism, we take the liberty to write  $\Lambda X.\varphi$  instead of  $\Lambda X.P_{\varphi}$ .

A parametric property is, therefore, similar to a normal property, except that the domain is parametric traces, and the output, rather than being one category, is a mapping of parameter instances to categories. This allows the parametric property to associate an output category for each parameter instance from  $[X \rightarrow V]$ .

### 4.1.2 Monitors and parametric monitors

Here we define monitors M and parametric monitors  $\Lambda X.M$ . Like for parametric properties, which are just properties over parametric traces, parametric monitors are also just monitors, but for parametric events and with instance-indexed states and output categories: a parametric monitor  $\Lambda X.M$  is a monitor for the parametric property  $\Lambda X.P$ , with P the property monitored by M [23].

Monitors are defined as a variant of Moore machines:

**Definition 7** A *monitor M* is a tuple  $(S, \mathcal{E}, \mathcal{C}, 1, \sigma : S \times \mathcal{E} \rightarrow S, \gamma : S \rightarrow \mathcal{C})$ , where S is the set of states,  $\mathcal{E}$  is the set of input events,  $\mathcal{C}$  is the set of output categories,  $1 \in S$  is the initial state,  $\sigma$  is the transition function, and  $\gamma$  is the output function. The transition function is extended to handle traces of events (i.e.,  $\sigma : S \times \mathcal{E}^* \rightarrow S$ ) the standard way.

The notion of a monitor above is often impractical. Actual implementations of monitors need not generate all the state space *a priori*, but rather on an "as needed" basis. Allowing monitors with infinitely many states is a necessity in our context. Even though only a finite number of states is reached during any given (finite) execution trace, there is, in general, no bound on how many may be reached. For example, monitors for CFGs have potentially unbounded stacks as part of their state. Also, as shown shortly, parametric monitors have domains of functions as state spaces, which are infinite as well.

**Definition 8**  $M = (S, \mathcal{E}, \mathcal{C}, 1, \sigma, \gamma)$  is a monitor for property  $P : \mathcal{E}^* \to \mathcal{C}$  if  $\gamma(\sigma(1, w)) = P(w)$  for each  $w \in \mathcal{E}^*$ . Every monitor M defines the property  $\mathcal{P}_M : \mathcal{E}^* \to \mathcal{C}$  with

$\mathcal{P}_M(w) = \gamma(\sigma(1, w))$ ; We write  $\mathcal{P}_M$  to denote the property defined by M. Monitors M and M' are *equivalent*, written  $M \equiv M'$  if  $\mathcal{P}_M = \mathcal{P}_{M'}$ .

We next define parametric monitors in the same style as the other parametric entities defined in this paper: starting with a base monitor and a set of parameters, the corresponding parametric monitor can be thought of as a set of base monitors running in parallel, one for each parameter instance.

**Definition 9** Given parameters X with corresponding values V and monitor  $M = (S, \mathcal{E}, \mathcal{C}, 1, \sigma: S \times \mathcal{E} \to S, \gamma: S \to \mathcal{C})$ , the *parametric monitor*  $\Lambda X.M$  is the monitor ( $[[X \to V] \to S], \mathcal{E}(X), [[X \to V] \to \mathcal{C}], \lambda \theta.1, \Lambda X.\sigma, \Lambda X.\gamma)$ , with  $\Lambda X.\sigma$ :  $[[X \to V] \to S] \times \mathcal{E}(X) \to [[X \to V] \to S]$  and  $\Lambda X.\gamma$ :  $[[X \to V] \to S] \to [[X \to V] \to \mathcal{C}]$  defined as

$$(\Lambda X.\sigma)(\delta, e\langle \theta' \rangle)(\theta) = \begin{cases} \sigma(\delta(\theta), e) & \text{if } \theta' \sqsubseteq \theta \\ \delta(\theta) & \text{if } \theta' \not\sqsubseteq \theta \end{cases}$$

$$(\Lambda X.\gamma)(\delta)(\theta) = \gamma(\delta(\theta))$$

for any

$$\delta \in [[X \rightarrow V] \rightarrow S]$$

and any  $\theta, \theta' \in [X \rightarrow V]$ .

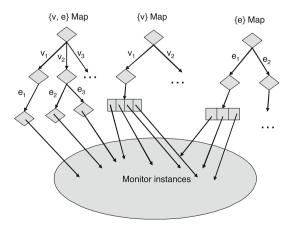

Therefore, a state  $\delta$  of parametric monitor  $\Lambda X.M$  maintains a state  $\delta(\theta)$  of M for each parameter instance  $\theta$ , takes parametric events as input, and outputs categories indexed by parameter instances (one category of M per instance). Intuitively, one can think of a parametric monitor as a *collection* of "monitor instances". Each monitor instance, which is indexed by a parameter instance, keeps track of the state of one trace slice. The rule for  $\Lambda X.\sigma$  can be read as stating that when an event with parameter instance  $\theta'$  is evaluated, it updates the state for all monitor instances more informative than the instance for  $\theta'$ , and the instance for  $\theta'$  itself, leaving all other monitor instances untouched. The rule for  $\Lambda X.\gamma$  simply states that  $\gamma$  is applied to a state, as normal, but the state is found by looking up the state of the monitor instance for  $\theta$ .

## 4.1.3 Naive parametric monitoring

Intuitively, the necessary steps for online monitoring of parametric properties are as follows:

- 1. Begin with a monitor instance for the empty parameter instance ⊥ initialized to the start state of the monitor, 1.

- 2. As each event,  $e(\theta)$ , arrives there are two possibilities:

- There is already a monitor instance for  $\theta$ , in this case the instance is simply updated with e.

- There is not already a monitor instance for  $\theta$ , in this case an instance is created for  $\theta$ . It is initialized to the state of the *most informative*  $\theta'$  less informative than  $\theta$ . Such a  $\theta'$  is guaranteed to exist because we begin with a monitor instance for  $\bot$ , which is less informative than all other possible  $\theta$ 's. We also create monitor

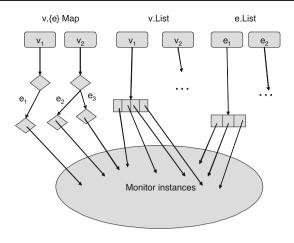

**Fig. 9** Naive monitoring algorithm  $\mathbb{B}\langle X \rangle$

instances for every parameter instance that may be created by combining  $\theta$  with previously seen parameter instances. Each of these created instances is initialized similarly to the instance for  $\theta$ , using the most informative instance less than itself. All created monitor instances are updated with e after initialization.

3. *e* is then used to update the monitor instances for all  $\theta'$  that are strictly more informative than  $\theta$ .

We next present a more concrete monitoring algorithm for parametric properties first introduced in [23]. It is derived from the algorithm  $\mathbb{A}\langle X\rangle$ , which is omitted here, that was also first presented in [23]. A first challenge here is how to represent the states of the parametric monitor. We encode the functions  $[[X \rightarrow V] \rightarrow S]$  as tables with entries indexed by parameter instances in  $[X \rightarrow V]$  and with contents states in S. Such tables will have finite entries since each event binds only a finite number of parameters. Figure 9 shows our monitoring algorithm for parametric properties. Given parametric property  $\Lambda X.P$  and M a monitor for P,  $\mathbb{B}\langle X\rangle(M)$  yields a monitor that is equivalent to  $\Lambda X.M$ , i.e., a monitor for  $\Lambda X.P$ .