# From control law diagrams to Ada via Circus

Ana Cavalcanti<sup>1</sup>, Phil Clayton<sup>2,3</sup> and Colin O'Halloran<sup>2</sup>

<sup>1</sup> University of York, York, UK. E-mail: Ana.Cavalcanti@cs.york.ac.uk

<sup>2</sup> Systems Assurance Group, QinetiQ, Malvern, UK

<sup>3</sup> Veonix, Worcester, UK

**Abstract.** Control engineers make extensive use of diagrammatic notations; control law diagrams are used in industry every day. Techniques and tools for analysis of these diagrams or their models are plentiful, but verification of their implementations is a challenge that has been taken up by few. We are aware only of approaches that rely on automatic code generation, which is not enough assurance for certification, and often not adequate when tailored hardware components are used. Our work is based on *Circus*, a notation that combines Z, CSP, and a refinement calculus, and on industrial tools that produce partial Z and CSP models of discrete-time Simulink diagrams. We present a strategy to translate Simulink diagrams to *Circus*, and a strategy to prove that a parallel Ada implementation refines the *Circus* specification; we rely on a *Circus* semantics for the program. By using a combined notation, we provide a specification that considers both functional and behavioural aspects of a large set of diagrams, and support verification of a large number of implementations. We can handle, for instance, arbitrarily large data types and dynamic scheduling.

Keywords: Z, CSP, Simulink, Refinement

## 1. Introduction

Control systems can be conveniently specified diagrammatically; in particular, engineers are comfortable with control law diagrams. In the avionics and automotive sectors, at least, the use of Matlab's Simulink [Mat] for drawing and simulation is standard; it also includes facilities for automatic code generation.

Since safety-critical applications often involve control systems, the validation of control law diagrams has been of great interest: numerical modelling and simulation are the techniques routinely used. Formal analysis, due to the typical complexity and scale of diagrams, is a major challenge; it is not unusual for a diagram to have hundreds of pages. Verification of a diagram's implementation is no simpler.

Existing work is mostly concerned with properties of the specification or design of a control system [Tiw02, FK04, JH05, DBCHP03] described by a diagram. They are valuable contributions, in that they extend the restricted static analysis capabilities of tools like Simulink. The work in this paper, on the other hand, provides a complementary facility: proof of correctness of code, as opposed to validation of requirements or designs. More precisely, we present a technique to prove that a (parallel) implementation of a diagram satisfies the functional and behavioural properties that it defines. For that, we define a formal model for discrete-time single-rate Simulink diagrams suitable for reasoning based on refinement, a formal model for Ada programs [Bar05] written in a subset of this language similar to SPARK Ada and with a particular architecture, and a verification strategy based on the application of refinement laws to compare them.

Correspondence and offprint requests to: A. L. C. Cavalcanti, E-mail: Ana.Cavalcanti@cs.york.ac.uk

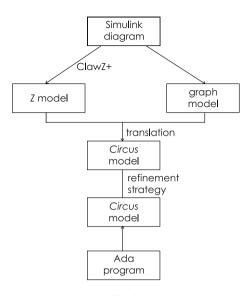

Fig. 1. Verification strategy

As far as we know, ClawZ [ACOS00] is the only effort on formal verification of implementations of control laws. This is a translator from Simulink diagrams to specifications written in a version of Z [WD96] implemented in the theorem prover ProofPower [KAW96]. The Z specifications are used to define refinement conjectures that connect a diagram and an Ada subprogram (procedure or function); they are proved using tools integrated with ProofPower [AC05]. We have measured experiments in the context of industrial applications that show a reduction factor between two and a half and four and a half in the human effort required for establishing acceptance when the ClawZ approach and tools are used. There is a cost reduction of 20% in relation to conventional development and verification of safety–critical systems in the area of avionics.

In this paper, we build on ClawZ to specify more complete models of diagrams: we capture their inherent parallelism, as well as functionality. We also establish correctness of the scheduler (as well as the procedures and functions). All this is achieved with the same high level of automation of ClawZ.

The Matlab semantics for Simulink is given implicitly by its simulator. Many works provide a formal semantics of various properties of diagrams; there are results using automata [Tiw02], the data-flow language Lustre [CCM<sup>+</sup>03], asynchronous processes [JZW<sup>+</sup>00], Hoare logic [BHM03], and timed formalisms [CD06], to cite a few. What we provide here is not just yet another formal model for Simulink. Our semantics distinguishes itself in that it is appropriate for refinement-based reasoning, and, therefore, program verification.

The use of code generators is appealing, and they are the basis of several development approaches advocated by works on analysis of Simulink models [K S02, GHOS06]. When code correctness and certification are an issue, however, the use of code generators does not provide enough assurance; verification of the generator or of the generated code is needed. The frequent updates to generators make the cost of their verification prohibitive. In any case, requirements imposed by the target hardware often mean that complex tailored algorithms need to be used, instead of automatically generated code; experience in the automotive industry, for example, is reported in [R B01]. Here, we pursue a cost-effective approach to code verification.

What we present is a sound and practical approach to prove correctness of implementations of control diagrams. In our technique, the formalisms are hidden from engineers, as the verification strategy is amenable to high levels of automation that ensure practicality. We use a refinement technique based on *Circus* [CSW03], a combination of Z and CSP. With an integrated approach, we significantly extend the class of diagrams that can be modelled, and program properties that can be verified.

We provide a strategy to translate the output of an extended version of ClawZ and a graph model that captures the data-flow of the diagram to a *Circus* specification; Fig. 1 summarises our approach. In addition, we present a verification technique for parallel Ada implementations based on the result of the translation. Effectively, the translation defines a *Circus* semantics for discrete-time Simulink diagrams; it is a suitable starting point for reasoning based on refinement.

Using *Circus*, we capture the functionality and concurrency of a diagram, including features related to conditional execution and order of interactions. Moreover, the *Circus* specification can capture the behaviour of the system over any number of cycles. With a *Circus* model, scheduling and the data operations can be verified jointly, and so we can cater for sophisticated dynamic scheduling policies. Since we do not rely on model checking, there are no restrictions on the size of data types.

With *Circus*, separate analyses of programs to cover functionality and scheduling independently are not needed. Our approach to verification is based on a *Circus* model of the Ada program, and a refinement strategy based on *Circus* laws. We establish the correctness of both the sequential subprograms, and the overall parallel behaviour. For the subprograms, we reuse the well-established verification technique based on ClawZ and ProofPower [CC06], but we cover all the properties verified using ClawZ and much more.

The technique presented here is specific for Ada programs use a specific architecture commonly used in embedded control systems where time is critical and processing resources are limited. The approach, however, can be adapted to different architectural patterns. In addition, there are no assumptions about the structure of the diagrams, and the verification is entirely compositional.

In practice, many of the changes to the requirements of control systems involve tuning of values of variables; they have no impact on the structure of the diagrams or programs, which tend to be stable. The tactics of refinement and proof are independent of particular values and can be reused directly. Structural changes to diagrams and programs have more of an impact, but since our approach is based on refinement, and so, compositional, the cost of the effort entailed by the change is proportional to its size.

The existing experience with ClawZ improves our confidence in the suitability of the *Circus* semantics. In addition, the availability of tools simplifies the mechanisation of the generation of *Circus* models. We have already implemented a tool that works with ClawZ, and generated models for industrial examples [ZC09]. In [CC005], we presented an initial version of the semantics; here we formalise an improved and extended version. Most importantly, we explain how the semantics can be used to prove programs correctness.

In the next section, we present a brief introduction to Simulink diagrams. In Sect. 3 we describe ClawZ and *Circus*. Our translation strategy which defines a *Circus* semantics for discrete-time Simulink diagrams is presented in Sect. 4. Section 5 discusses the *Circus* models for Ada programs. The refinement strategy is presented in Sect. 6. Finally, in Sect. 7 we briefly address related work, and in Sect. 8, we summarise our results, and discuss future work. Appendix A formalises a graph model of diagrams. Appendix B gives *Circus* refinement laws of general interest used in our technique.

## 2. Control law diagrams

In a control law diagram, systems are modelled by directed graphs of blocks connected by wires. Roughly speaking, wires carry signals, and blocks represent functions that determine how outputs are calculated from the inputs. In a continuous-time model, signals vary continuously; in a discrete model, signals are sampled at fixed time intervals, so that input and output take place in cycles. Blocks can be themselves defined by diagrams, and so large diagrams typically have a hierarchical structure.

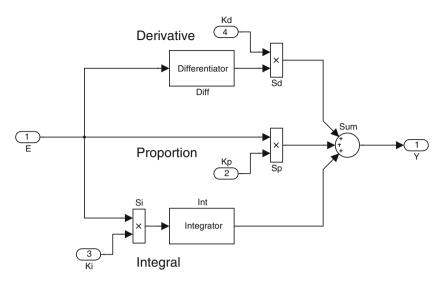

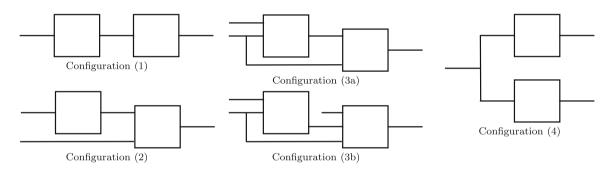

A simple example of a Simulink diagram is presented in Fig. 2; it specifies a PID (Proportional Integral Derivative) controller. This is a simple feedback mechanism that is, however, in widespread use in real control applications. Its main purpose is the correction of an error in some measured value. Typically, the value of the error is obtained using a sensor, and correction is achieved by outputting information used to regulate an actuator. For example, a temperature controller obtains the amount by which it may be too hot or too cold, and indicates how the source of heat should be regulated. This is calculated as the weighted sum of the correction actions indicated by three different methods: proportional, integral, and derivative. The first method produces a correction proportional to the error; the integral value takes the history of errors into account; and finally the derivative correction value considers the rate of change in the error. The controller reads the error and outputs the correction over and over again at predefined intervals.

In our example, the inputs of the PID controller are the error E, and the weights, Kp, Ki, and Kd, for the proportional, integral, and derivative values. Annotations indicate the branches that calculate the correction according to the Derivative, Proportion, and Integral methods.

Inputs and outputs of the diagram are represented by rounded blocks containing numbers. Each block has a name, and in the case of the inputs and outputs, the blocks are named after them. In our example, we have input blocks E, Kp, Ki, and Kd, and one output block, Y.

Fig. 2. PID (proportional integral derivative) controller

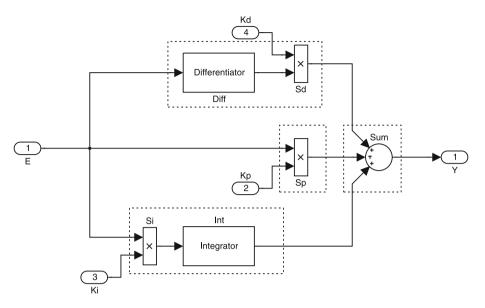

Fig. 3. PID differentiator

Typically, a block takes some input signals and produces some outputs according to a function determined by the kind of block in question. Different block shapes and annotations inside the blocks give a visual indication of their functionality. The circle is a sum block. The block with a  $\times$  symbol are product blocks. There are libraries of basic blocks in Simulink, and they can also be user-defined.

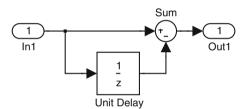

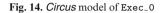

In our example, the blocks enclosing names, that is, the blocks named Diff and Int, are subsystems. The names in (the rectangles that represent) the blocks, Differentiator and Integrator, respectively, are just annotations that give an indication of the functionality of the subsystems. They are defined by other diagrams named after the blocks. For example, the diagram Diff is presented in Fig. 3.

Blocks can have state. For instance, blocks labelled 1/z are unit delay blocks: they store the value of the input signal, and output the value stored in the previous cycle. In each cycle, the output of a diagram depends on the values of the inputs and of the state in the blocks, if any, but other factors may be relevant.

For example, subsystems may be conditionally executed: an action subsystem has an activate input and is executed when it is true; an enabled subsystem has an enabling input and is executed when its value is greater than zero. When a subsystem is not executed, its outputs are not calculated, and can either be held or reset to an initial value. Any state in blocks within the subsystem is held until the subsystem is about to be executed again, at which point the state can be modified, held, or reset to an initial value.

Merge blocks take a number of inputs and produce one output: the most recently calculated input. Typically, the inputs are connected to conditionally executed subsystems, and in each cycle only one of them produces a calculated output. This is the output produced by the merge block. If none of the inputs are calculated in a cycle, then the merge block repeats its previous output.

ClawZ uses Z to provide a relational model for blocks, which covers state, but not concurrency and the behaviour of conditionally executed subsystems and merge blocks.

# 3. ClawZ and Circus

This section describes the notation (*Circus*) and tool (ClawZ) used in our work. In particular, we explain how ClawZ defines a semantics for diagrams; it is a partial semantics, in that it covers only block functionality.

## 3.1. ClawZ

As already mentioned, ClawZ is a tool suite for verification of Ada programs against Simulink diagrams. It provides a self-contained formal account of the functionality of the blocks of a diagram, and of the diagram itself using Z. Verification is based on refinement, with conjectures built in terms of the Z specifications.

The essence of the semantics of a diagram is defined by three elements: the functionality embedded in the Simulink block library, the way in which library blocks are used and connected by wires in the diagram, and the time model. Timing features are not covered in ClawZ and in our work: we assume a discrete-time model, so that the system specified has a cyclic behaviour, in which at each cycle it reads some inputs and produces some outputs. This is the model used in software implementations of control systems.

In specifying the semantics of a diagrammatic notation, the first concern is perhaps the definition of a linear abstract representation. This is already provided by Simulink, which represents diagrams as a list of block specifications in a structured ASCII file, the mdl file. Each specification refers to a basic block in the Simulink library or to a user-defined block specified by another diagram, and records information like inputs and outputs, initial value of the state, if any, and so on. The reference to the block library is an implicit specification of functionality, and the information about inputs and outputs defines a graph structure.

The formal semantics of the basic blocks and, more importantly, of subsystem blocks defined by diagrams (involving basic blocks and, possibly, further subsystem blocks) is defined by ClawZ as Z schemas. It describes how the outputs of the blocks are calculated from its inputs, and perhaps some state information. This gives a more complete view of the diagram functionality than its (linear) Simulink representation. For this reason, it is a convenient starting point to construct a *Circus* model of the diagram.

Formally, ClawZ implements a function which, given a diagram, and the name of one of its blocks, gives a formal characterisation of that block as a set of bindings (records). Typically, this set is defined by a schema. In other words, the Z specification provided by ClawZ does not follow the traditional style in which schemas are used to define the state of the system, and its operations. Instead, the specification uses schemas as one of the fundamental type constructors of Z; blocks (and diagrams) are record types defined by schemas in Z.

An implicit parameter of the semantic function defined by ClawZ, which we call ClawZ itself, is the formalisation of the Simulink block library. It provides a record type definition for each block. For example, the block Sum in Fig. 3 is an instance of a sum block that negates its second input; in effect, this is a subtraction. Its model in the ClawZ library is the schema below.

z

$In1?, In2? : \mathbb{R}$  $Out1! : \mathbb{R}$  $Out1! = In1? -_R In2?$

The notation adopted here is the Z dialect of ProofPower, which is very close to the Z standard; we point out the few differences as needed. The Z that precedes the schema above is used by ProofPower to distinguish Z paragraphs from definitions in HOL or SML. The components of the schema are components (fields) of the records in the set that characterises the block. For the inputs, we have components In1?, In2? and so on, depending on the number of inputs of the block. Similarly, for the outputs, we have components Out1!, Out2!, and so on. The block in our example has two inputs and one output.

A theory of real numbers for Z is available in ProofPower; above, we declare the components of the schema to be of type real. The predicate uses a difference operator  $(-_R)$  for real numbers to define the output. The set defined by  $Sum_PM$  contains all the bindings with components In1?, In2?, and Out1! whose values are of type real, and are related as described in the predicate.

Some blocks require a parameter upon instantiation. For example, a unit delay takes the initial value of its state. In this case, it is formalised as a (possibly generic) function using an axiomatic description. The generic parameter is the type X of the state, input, and output. The function takes a binding with a single component X0 and yields a set of bindings that characterises the unit delay block. The type of the bindings in this set is defined by an unnamed horizontal schema [In1?,  $initial\_state$ , state', Out1! : X] with an empty predicate part. The value of X0 is used to initialise the state.

$$-[X]$$

$UnitDelay_g : [X0 : X] \rightarrow \mathbb{P} [In1?, initial_state, state, state', Out1! : X]$

$\forall pars : [X0 : X] \bullet$   $UnitDelay\_g pars = [In1?, initial\_state, state, state', Out1! : X |$  $initial\_state = pars.X0 \land Out1! = state \land state' = In1?]$

The function is generic because unit delay blocks work on several types of signals: real numbers, vectors, and so on. The value X0 of the argument record is used to initialise the *intial\_state* components of the bindings in the resulting set. In general, the bindings in the set that characterises a block with a state includes, besides input and output components, the three extra components *initial\_state*, *state*, and *state'*. They record the value of the state when the system starts its execution, the value of the state at the beginning of the current cycle, and the value of the state at the end of the cycle, respectively.

In practical terms, given a diagram, ClawZ produces a Z specification that characterises each of its blocks, as well as the whole diagram. As an example, part of the output of ClawZ for the PID diagram in Fig. 2 is presented in Fig. 4. The name of a block in the Z specification includes, besides that explicitly indicated in the diagram, the name of the subdiagram in which the block occurs, and the name of the diagram itself. For instance, the Sum block in the subdiagram Diff (Fig. 3) is defined by the schema  $pid_{-2}Diff_{-2}Sum$ .

This schema, as well as those for the Sd and Sum blocks in the top diagram, that is,  $pid_{-}Sd$  and  $pid_{-}Sum$ , are specified directly in terms of library definitions:  $Sum_PM$  presented above and others. For the UnitDelay block, as discussed above, the definition in the Z library is a function; in a particular model it is applied to an appropriate argument to define a set of bindings. In our case, the argument is a binding  $X0 \cong 0 \ e \ 0$  with a single component X0 whose value is the real number 0, written  $0 \ e \ 0$  in ProofPower.

The schema *pid* defines the top diagram; it declares the inputs and outputs of the system, and an extra component for each of the blocks at this level, that is, Diff, Int, Sd, Si, Sp, and Sum. The names of the input and output components are still generic, that is, *In1*?, *In2*?, and so on, and *Out1*!. This ensures that the model of a top diagram is similar to that of a subsystem diagram or even of a block; such uniformity is beneficial for reasoning. The types of the block components are the sets of bindings that specify them. The predicate of *pid*, which is omitted for the sake of conciseness, specifies how the inputs and outputs of the diagram and of each of the blocks are connected. The type  $\mathbb{U}$  is a universal type in ProofPower.

The definition of Diff is similar to that of the top diagram in *pid*. It is a schema that declares the inputs and outputs, and each of the blocks in the diagram Diff. The predicate, which is similar to that of *pid*, equates, for instance, the inputs of the Sum block to the input of the diagram and the output of the Unit Delay block. It also defines that the output of the diagram is that of Sum. The repeated equality UnitDelay.In1? = Sum.In1? = In1? is not part of the Z standard notation, but is accepted in ProofPower; it is a shorthand for the conjunction of UnitDelay.In1? = Sum.In1? and Sum.In1? = In1?. Similarly, the predicate of the *pid* schema is a conjunction of equations that reflect the wiring in Fig. 2.

In summary, the inputs of a diagram or of a block are modelled as components *In1?*, *In2?*, and so on; similarly, outputs have conventional names *Out1*!, *Out2*!, and so on. If the block has a state, there are components *state*, *state'*, and *initial\_state* to record its value at the beginning and at the end of the cycle, and at the beginning of the first cycle. The other components, if any, represent blocks; for each block in the top diagram or in a subsystem diagram, there is a component. The predicate is a conjunction of equalities that specify how the inputs and outputs are connected.

The ClawZ model of a diagram specifies the functionality of all of its blocks, over one cycle of execution. It does not, however, capture the graph structure of the diagram, and so does not have an explicit record of opportunities for parallelisation. This is addressed by the *Circus* model proposed here.

```

pid_{--}Diff_{--}Sum \cong Sum_{-}PM

pid_{--}Diff_{--}UnitDelay \cong UnitDelay_q (X0 \cong 0 \ e \ 0)

_pid__ Diff_

In1? : \mathbb{U};

Sum : pid_{--}Diff_{--}Sum;

UnitDelay : pid__Diff__UnitDelay;

Out1!: \mathbb{U}

Out1! = Sum.Out1!;

UnitDelay.In1? = Sum.In1? = In1?;

Sum.In2? = UnitDelay.Out1!

pid_{--}Sd \cong Product_M2

pid_{--}Sum \cong Sum_P3

z

_pid_

In1? : U; In2? : U; In3? : U; In4? : U;

Diff : pid_{--}Diff;

Int : pid_{--}Int;

Sd : pid_{--}Sd;

Si : pid_{-}Si;

Sp : pid_{--}Sp;

Sum : pid_{--}Sum;

Out1!: \mathbb{U}

```

Fig. 4. ClawZ output for the PID (ProofPower notation)

# 3.2. Circus

This is a language for refinement; *Circus* includes specification constructs from Z and Morgan's refinement calculus [Mor94], CSP constructs to model communication and concurrency, and guarded commands, including assignments and conditionals. It is distinctive in that it mixes (Z) data operations and (CSP) constructs for communication and parallelism in a flexible way. Events are not attached to state changes: when an event happens, there is no implicitly associated state change. State changes have to be explicitly specified, just like they are in programming languages. (This approach is in contrast with that adopted in other combinations of CSP with a state-based notation [TS99, Fis00]). Moreover, refinement can be carried out compositionally.

Like in Z, a *Circus* program is a sequence of paragraphs, but they also include channel and process declarations. Figure 5 gives an example: a factorial calculator that uses a memory register.

```

channel disp

channel set, add, mult, out : \mathbb{N}

process Mem \cong begin

state Register == [r : \mathbb{N}]

Prod.

\Delta Register

x?:\mathbb{N}

r' = r * x?

• (\mu X \bullet (set?x \to r := x \Box add?x \to r := r + x \Box mult?x \to Prod \Box disp \to out!r \to Skip); X)

end

channel calc : \mathbb{N}

process Fact \cong begin

FCalc \cong (n: \mathbb{N} \bullet \mathbf{if} \ n = 0 \to Skip \| n \neq 0 \to mult?n \to FCalc(n-1) \mathbf{fi})

• (\mu X \bullet calc?n \to set!1 \to FCalc(n); disp \to X)

end

process System \cong (Mem || \{ set, mult, disp, out \} | \{ calc, set, mult, disp \} || Fact ) \{ set, mult, disp \}

```

Fig. 5. Example of a simple Circus specification

Communications are events, just like in CSP. In our example, we first of all declare a few channels. The channel disp does not have a type, and so it is used just for synchronisation: to request the memory register to output its value through the channel *out* of type  $\mathbb{N}$ . The channels *set*, *add*, and *mult* also have type  $\mathbb{N}$ ; they are used to update the memory using the communicated value.

A process encapsulates state and exhibits behaviour. An explicit definition of a process is a sequence of paragraphs; the specifications of Mem and Fact in Fig. 5 are examples. A distinguished paragraph introduces the state schema in the style of Z; in the case of Mem, this is the *Register* schema with the single component r of type  $\mathbb{N}$ , but *Fact* is stateless. Encapsulation means that the state is local; interaction with the process is only via communications through channels.

At the end of an explicit definition, a main action specifies the behaviour of the process. Actions are defined using a combination of Z (state) operations, CSP constructs, and guarded commands.

In *Mem*, the main action is recursive; it repeatedly offers the choice of interaction over any of the channels *set*, *add*, *mult*, and *disp*. Communication over *set* takes an input value x, which is assigned to r; the input *set*?x declares x as a local variable whose scope is the assignment or, in more general terms, the action prefixed by the input communication. Similarly, the input prefixing add? $x \rightarrow r := r + x$  declares the local variable x for use in the assignment r := r + x. The value communicated over add is assigned to x and used to increment the register. For the sake of example, we specify the state update that corresponds to an input over *mult* using a Z schema *Prod*, instead of simply using r := r \* x. The style of definition of Z state operations is standard, and the input variable x? of *Prod* is linked to the local variable x declared by the input communication. Finally, we observe that interaction on *disp* does not lead to any state operation; instead, it is a request for the output of the value of r through the channel *out*.

In the case of Fact, the main action is also recursive: it repeatedly accepts a request to calculate the factorial of a natural number n, after which it sets the memory, uses it to calculate the factorial, and requests that the output is displayed. The extra channel *calc* is declared just before the definition of *Fact*.

Typically, a process definition includes several paragraphs to specify actions that are combined in the main action to define the behaviour of the process. In our simple examples, we have, the action *Prod* in the process *Mem*, and the action *FCalc* in the process *Fact*. The latter is a parametrised action with parameter n of type  $\mathbb{N}$ ; it uses the initialised register to calculate the factorial of n. A conditional determines if it should terminate immediately, if n = 0, or multiply the value of the register by n before recursing, if n > 0. The basic action *Skip* terminates immediately without changing the state.

Like actions, processes can also be combined using CSP operators: sequence, choice, parallelism, hiding, and others. Parallelism is alphabetised just like in CSP: we can either define a synchronisation set or the alphabet of the parallel processes or actions. A synchronisation set contains the channels on which the parallel processes (or actions) need to synchronise; communications on all other channels occur independently. If, on the other hand,

we use the alphabetised parallel operator, for each parallel process or action, we define an alphabet; in this case, the process (or action) can only communicate on a channel c if it is in its alphabet, and needs to synchronise with all other processes or actions that also have c in their alphabet.

In our example, we define the process *System* as the parallel composition of *Mem* and *Fact*. We use the interface parallel operator, and define the alphabets of *Mem* and *Fact*. Since we leave *add* out of the alphabet of *Mem*, it cannot communicate over this channel, although such communications may be helpful in other uses of *Mem*. Synchronisation is required for the channels in the intersection of the alphabets; in our example, they are *set*, *mult*, and *disp*. These are internal channels used only for communications between the components of the system; therefore, they are hidden in the definition of *System*. In summary, our system takes inputs over *calc*, and produces outputs using *out*; all other channels are hidden, and communications over them are not visible to the environment of *System*.

In the case of a parallelism of actions, there is a concern about conflicting access to state components (and local variables). For that reason, the parallel operators for actions define partitions of the variables in scope. For example, the composition of actions  $A_1$  and  $A_2$  using the alphabetised parallel operator with a synchronisation set cs is written  $A_1 [[ns_1 | cs | ns_2]] A_2$ , where  $ns_1$  and  $ns_2$  are disjoint sets of names of variables in scope. Both  $A_1$  and  $A_2$  have access to the initial value of all variables; however,  $A_1$  can only modify those named in  $ns_1$ , and  $A_2$  can only modify those in  $ns_2$ . Figure 5 presents a parallelism between processes, but not between actions. An example of action parallelism is provided in the next section (Fig. 10).

A refinement calculus and strategy is available for *Circus* [CSW03]. The strategy aims at calculating concurrent implementations from centralised specifications. Here, we provide a few novel refinement laws, which are clearly marked in Appendix B, and a strategy tailored to the verification of Ada implementations with respect to models of diagrams. In this case, we aim at removing the massive parallelism in the models.

# 4. Translation strategy

We formalise the *Circus* model of a diagram as a function  $\llbracket d \rrbracket^C$  that takes the linear representation of a diagram d and provides a *Circus* specification. In this section, we present the definition of this function; the meta-notation that we use to describe the *Circus* specification is based on the Z and *Circus* mathematical and action notations. When there is the possibility of ambiguity, to differentiate the occurrences of symbols of the meta-notation from those of the target *Circus* specification, we use a sans-serif font for the meta-notation.

There are two intermediary models that we extract from d in order to define the *Circus* model. The first is the Z model defined by ClawZ; formally this is the result of applying the ClawZ function described in the previous section to d. In fact, we consider a few extensions to ClawZ to cater for a larger number of blocks. They, however, do not interfere with the structure of the model already described.

The second model of the diagram captures its structure as a graph. It is described in Sect. 4.1 below, and formalised in Appendix A. Section 4.2 describes the channels used in the *Circus* specification. Modelling of blocks is the subject of Sect. 4.3. Finally, in Sect. 4.4 we explain how the models of the blocks are used to define a *Circus* model for the diagram. As detailed in the sequel, in the *Circus* model of a diagram, blocks, as well as the diagram itself, are defined as processes.

For clarity, we present the definition of  $[\![d]\!]^C$  in an incremental way, with the various paragraphs of the *Circus* specification interspersed with comments and examples. We start the definition below, where we use a let clause to name the results of applying the ClawZ and DF functions to d.

$\llbracket d \rrbracket^C = \operatorname{let} \operatorname{clawz} = \operatorname{ClawZ}(d); \quad df = \mathsf{DF}(d) \bullet$

As already said, the function ClawZ is that defined by ClawZ. The function DF defines a graph that captures the data flow in *d*. It is specified in the next section.

## 4.1. Graph model

To provide an accurate *Circus* model of a diagram, we use a graph model that captures its data flow. It is formally specified in Appendix A; here we illustrate the graph structure by means of examples.

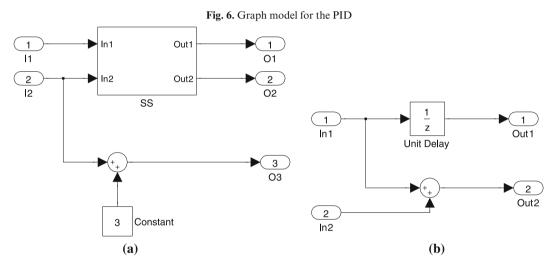

The function DF associates a diagram to a record (binding) that registers the diagram name (in a field *spec*), the names of its *inputs* and *outputs*, and a mapping *blocks* that associates each of its blocks, identified by their names, to information about its wiring. The type *Graph* defined in Appendix A defines the set of such records. The range of the mapping *blocks* is specified using the type *BlockWiring*. Part of the record for the PID diagram,

$$\begin{cases} spec == PID, \\ inputs == \{ E, Kp, Ki, Kd \}, \\ outputs == \{ Y \}, \\ blocks == \{ Si \mapsto \langle inps == \langle E, Ki \rangle, outs == \langle Si\_out \rangle, \\ flows == \{ \{ Si\_out \} \mapsto \langle enabled == always, \\ ordered == false, \\ rinps == \{ E, Ki \} \rangle \} \rangle, \\ Diff \mapsto \langle inps == \langle E \rangle, outs == \langle Diff\_out \rangle, \\ flows == \{ \{ Diff\_out \} \mapsto \langle enabled == always, \\ ordered == false, \\ rinps == \{ E \} \rangle \} \rangle, \\ Sum \mapsto \langle inps == \langle Sd\_out, Sp\_out, Int\_out \rangle, outs == \langle Y \rangle, \\ flows == \{ \{ Y \} \mapsto \langle enabled == always, \\ ordered == false, \\ rinps == \{ Sd\_out, Sp\_out, Int\_out \} \rangle \} \rangle, \\ \dots \} \rangle$$

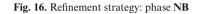

Fig. 7. Independent flows of execution

that is, DF(d), where d is the Simulink textual representation of the PID, is in Fig. 6. In this case, the name of the diagram is *PID*, the inputs are *E*, *Kp*, *Ki*, and *Kd*, and the output is *Y*. Each block is associated to its wiring information; in Fig. 6, we present the wiring for *Si*, *Diff*, and *Sum*.

The inputs and outputs of the diagram are named after its input and output blocks. The internal wires are named after the block that produces it as an output, using suffix \_out, if there is only one output, or \_out1, \_out2 and so on, if there is more than one output. For clarity of the model, however, when the output of a block is connected to an output port, we name the channel after the output. In our example, the output of the Sum block, for instance, is named Y, after the output of the diagram, rather than  $Sum_out$ .

The wiring of a block is defined by a binding that records its inputs (*inps*), outputs (*outs*), and the dependencies between them, that is, the *flows* of execution. To explain the need to model flows of execution, we first consider the diagram in Fig. 7a. It has two inputs 11 and 12, and three outputs 01, 02, and 03. The subsystem block SS is defined by the diagram in Fig. 7b. If we considered only the diagram in Fig. 7a, we could say that SS takes two inputs and produces two outputs. Inspection of Fig. 7b, however, reveals that O2 can be provided only once both inputs are available, but O1 can be determined from just 11. So, a model that defines that SS can output O1 only once both 11 and 12 are input is too restrictive. The graph model, therefore, needs to record that SS has two (independent) flows of execution: one that calculates O1 and another that calculates O2. For O2, both inputs are required, but not for O1.

In principle, each output determines a potentially independent flow of execution that calculates it, but a group of outputs may all be part of a single flow. Typically, the calculations involved in the definition of the value of each output are different, but they may, for example, depend on exactly the same inputs. Therefore, the flows are recorded as a function from sets of outputs to a binding (of type *Flow* as defined in Appendix A) that records information about the flow of execution that determines these outputs.

Fig. 8. If action subsystems

Relevant information about a flow determines its required inputs (*rinps*). For the block SS in Fig. 7a, for instance, the required inputs for the flow { O2 } is { I1, I2 }, but for { O1 }, it is { I1 }.

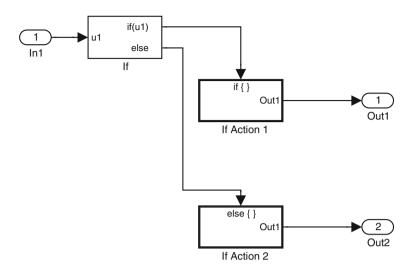

To cater for action and enabled subsystems, we also need to record whether or not a flow of execution is always enabled. As an example, we consider the diagram in Fig. 8. A basic lf block takes the input ln1; if it is greater than 0, then the first output is *true*, which is represented by 1 in Simulink, otherwise the second output is 1. These outputs are connected to the action ports of two action subsystems.

The output of an action subsystem depends on whether the value provided in its action port is 1 or not, that is, on whether the subsystem is enabled or not. The graph model for such a subsystem block, therefore, needs to record, for each of the flows defined by its outputs, the name of the action port. For If Action 1, we have a single flow {Out1}, and its enabling port is just  $If_{-}out1$ . (As explained in Appendix A, formally, this is recorded in the field *enabled* of the record of type Flow that models the flow as  $esigs({If_{-}out1})$ .)

Finally, we need to record whether the output of a flow of execution depends on the order of its required inputs. This is necessary to cater for merge blocks, which take a number of inputs and output the latest calculated one. The characterisation of a merge block with two inputs is as follows.

Intuitively, a merge block combines its inputs into a single output whose value is equal to the most recently computed, that is, updated, input. Even inputs that are not updated need to be provided (communicated), before the output is available. So, above the value of rinps for the single flow { Out1 } includes both inputs.

In our example, as indicated in Fig. 6, the blocks are very simple: they have one flow, which is always enabled, and whose output does not depend on the input order. Blocks like Diff represent a diagram, but from the point of view of the PID, it is just a block; its internal communications are abstracted away.

In the previous examples involving subsystem blocks, the information about their flows can be extracted by an analysis of the structure of the diagrams that define them. Even basic blocks, however, can have interesting flows of execution. For example, the unit delay block can produce outputs before it receives (all) the inputs. To construct the graph model of a diagram, we, therefore, need a library that records information about the basic blocks that compose diagrams, just like in ClawZ.

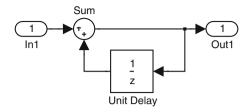

We consider, for instance, the diagram in Fig. 9, which defines the lnt block of the PID diagram (see Fig. 2). In constructing the model of this diagram, we need the information that the output of Unit Delay is available before its input is received. The input is the output of a Sum block that takes the output of Unit Delay itself as input. A model for the diagram that requires all inputs of all blocks to be provided before their outputs are produced would, therefore, incorrectly allow for a deadlock.

Fig. 9. PID integrator

Since Unit Delay is a basic block, however, to determine the immediate availability of its output, we need to resort to recorded information about such blocks. Its characterisation is as follows; the input is named In1, and the output Out1. As in ClawZ, this is just a convention; when blocks in diagrams are considered, the proper names of the inputs and outputs have to be determined in accordance with the wiring.

$\begin{array}{l} \langle inps == \langle In1 \rangle, \\ outs == \langle Out1 \rangle, \\ flows == \left\{ \{ Out1 \} \mapsto \langle enabled == always, ordered == false, rinps == \emptyset \rangle \right\} \rangle \end{array}$

Its only input is not required by its only flow { Out1 }, so the value of its rinps field is the empty set.

It is the graph model of a diagram that identifies, for instance, the channels declared and used in its *Circus* model. This is described in detail in the next section.

# 4.2. Channels

The *Circus* specification of a diagram first declares all signals as channels; for that, the information in the fields inputs, outputs, and each of the fields outs in the blocks fields of df is used.

**channel** df.inputs, df.outputs, { B : Block • df.blocks(B).outs } : U

Even though df.inputs is a set of signals, we use it above to denote a list of the signals in this set; the same comment applies to df.outputs and to the set of sequences df.blocks(B).outs of signals: one for each block B of the diagram. The type Block contains the valid block names; Appendix A gives the formalisation of the df model. All these signals are declared as channels of type  $\mathbb{U}$ .

We also declare a synchronisation channel  $end_cycle$ ; after taking all its inputs and producing all its outputs, each process representing a block of a diagram waits to synchronise on  $end_cycle$  before proceeding to the next cycle. In this way, the behaviour of all block processes are kept in phase.

```

channel end_cycle

```

In this paper, we only consider single-rate diagrams; for multi-rate diagrams, we will explore the timed version of *Circus* named *Circus* Time [SCJS10].

The Circus specification corresponding to the PID, for example, starts as follows.

**channel**  $E, Kp, Ki, Kd, Y, Si_out, Diff_out, Int_out, Sd_out, Sp_out : U$ **channel** $<math>end_cycle$

Next, the *Circus* specification includes the ClawZ library, which is used in clawz. There is then a process for each block, and at the end, the definition of the diagram; the are defined in the following sections.

## 4.3. The blocks

The model of a block is a single centralised process defined explicitly, independently of whether the block is simple, like Sd, or a subsystem, like Diff. This process lifts the clawz model, which is based on type definitions, to *Circus* actions. For each block B in dom df.blocks, we define a *Circus* process also called B.

$\mathbf{process} \; \mathsf{B} \mathrel{\widehat{=}} \mathbf{begin}$

**process**  $Diff \cong$  **begin state**  $Diff\_State == [pid\_Diff\_UnitDelay\_state : U]$   $pid\_Diff\_Sum == Sum\_PM$  $pid\_Diff\_UnitDelay \cong UnitDelay\_g(X0 \cong 0 \ e \ 0)$

$\begin{array}{l} \_pid\_\_Diff\_\\ In1?: \mathbb{U}\\ Sum: pid\_\_Diff\_\_Sum\\ UnitDelay: pid\_\_Diff\_\_UnitDelay\\ Out1!: \mathbb{U}\\ \hline\\ Out1!=Sum.Out1!\\ UnitDelay.In1?=Sum.In1?\\ Sum.In1?=In1?\\ Sum.In2?=UnitDelay.Out1!\\ \end{array}$

$\_Init\_$

$\begin{array}{l} Diff\_State'\\ \exists \ b: \ pid\_\_Diff\_\_UnitDelay \bullet \ pid\_\_Diff\_\_UnitDelay\_state' = \ b.initial\_state \end{array}$

$\begin{array}{c} Calculate_Diff \_ \\ \Delta Diff\_State \\ In1?, Out1! : \mathbb{U} \\ \hline \exists b: pid\__Diff \bullet \\ b.In1? = In1? \land b.UnitDelay.state = pid\__Diff\__UnitDelay\_state \land \\ b.UnitDelay.state' = pid\__Diff\__UnitDelay\_state' \land b.Out1! = Out1! \\ \end{array}$

$Calculate\_Diff\_out == Calculate\_Diff \setminus (pid\_\_Diff\_\_UnitDelay\_state') \land \exists Diff\_State$

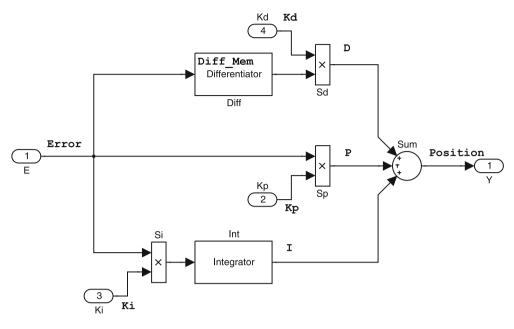

$$\begin{split} &Execute\_Diff\_out \stackrel{}{\cong} \left( \begin{array}{c} \mathbf{var} \ In1: \mathbb{U} \bullet \\ & \left( \begin{array}{c} E?x \rightarrow In1:=x; \\ \mathbf{var} \ Out1: \mathbb{U} \bullet Calculate\_Diff\_out; \ Diff\_out!Out1 \rightarrow Skip \end{array} \right) \end{array} \right) \\ &Flows \stackrel{}{\cong} Execute\_Diff\_out \\ &Calculate\_Diff\_State \stackrel{}{\cong} Calculate\_Diff \setminus (Out1!) \\ &StateUpdate \stackrel{}{\cong} \mathbf{var} \ In1: \mathbb{U} \bullet E?x \rightarrow In1:=x; \ Calculate\_Diff\_State \\ &\bullet \ Init; \\ & \mu X \bullet (Flows \parallel \{ \} \mid \{ B \in \} \mid \{ pid\_Diff\_UnitDelay\_state \} \parallel StateUpdate); \ end\_cycle \rightarrow X \\ &\mathbf{end} \end{split}$$

Fig. 10. Circus process for the block Diff

We consider a block whose flows are always enabled and do not depend on the order of the inputs.

The state of B includes a component for each component named state used in the definition of B in clawz.

| _state B_State                                                              |  |

|-----------------------------------------------------------------------------|--|

| $clawz(B)_{}h(def1)_{-}state,\ldots,clawz(B)_{}h(defn)_{-}state:\mathbb{U}$ |  |

To determine the names defi used in the definition of the *state* components of  $B_State$ , we consider the signature of the ClawZ definition clawz(B). As already said, this is a set of bindings. Its signature, therefore, is the power set of a schema type, or more plainly, of a record type defined by listing the record fields and respective (maximal) types. For example, the schema *pid\_Diff* (in Fig. 4) characterises the PID Diff block. Its signature is the powerset of the schema type defined below.

$[In1?, Out1!: \mathbb{A}; Sum: [In1, In2?, Out1!: \mathbb{A}]; UnitDelay: [In1?, Out1!, initial state, state, state': \mathbb{A}]]$

The type  $\mathbb{A}$  is the given set of values used in number systems. Because the above signature has a component *UnitDelay* whose type is a schema with a component called *state* (as defined by *UnitDelay\_g* in the ClawZ library) the process *Diff* (see Fig. 10) has a state component *pid\_Diff\_UnitDelay\_state*.

We specify a function stateN, which, given a schema type S, defines the set of sequences of component names that can be used to select a (sub)component of S whose type is itself a schema with a component named state. For the schema type above, stateN identifies the set containing the sequence  $\langle UnitDelay \rangle$ .

We define stateN(S) in terms of a function stateT(s, T), which applies to Z (maximal) types T, rather than just schema types S. The Z types include given sets, power sets, cartesian products, and schemas. The first parameter s of stateT is a sequence of component names. Formally, state(S) is defined as  $stateT(\langle \rangle, S)$ , and intuitively, s is the sequence of names that can be used to select a component of S that has type T.

We provide an inductive definition for stateT(s, T) based on the structure of types T in Z.

#### **Definition 4.1**

$$state T(s, TN) = state T(s, \mathbb{P} T) = state T(s, T_1 \times T_2) = \emptyset$$

$$state T(s, [i \bullet c_i : T_i] = \{s\}, \text{ if } \exists i \bullet c_i = state$$

$$state T(s, [i \bullet c_i : T_i] = [] i \bullet state T(s \cap \langle c_i \rangle, T_i), \text{ if } \neg \exists i \bullet c_i = state$$

We use TN to stand for a type name, that of a given set, and T,  $T_1$ ,  $T_2$ , and  $T_i$  to stand for arbitrary type descriptions. For given sets, power sets, and cartesian products, stateT gives the empty set of selector sequences: given sets have no components, and, in a model of a block, we do not have other blocks arranged in a power set or a cartesian product. What we do have is blocks directly inside other blocks. In our example, for instance,  $pid_{--}Diff$  is the model of a block that includes as components models of other blocks. In the case of the component Sum, it is a block without state, but in the case of UnitDelay, we do have a state. Correspondingly, in the definition of stateT, we consider schema types [ $i \cdot c_i : T_i$ ] which include components  $c_i$  of type  $T_i$ . If any of the names  $c_i$  is state, then the sequence s is identified as a selector for a schema type with a state component. Otherwise, we consider each of the components  $c_i$  individually. For each of them, we consider the result of recursively applying stateT to the sequence obtained by appending  $c_i$  to s, and to the type  $T_i$  of  $c_i$ . The result is the distributed union of the sets of selector sequences so obtained.

The sequences of names in stateN(clawz(B)) are exactly the sequences defi used above to construct the names of the state components of the process B as specified above. The name h(defi) used in the declaration of the state schema B\_State is the \_\_-separated list of the names in defi. The simple definition of the syntactic function h is omitted. For our example, the name of clawz(B) is  $pid_-Diff$  and, since the result of applying state to its signature is just the singleton sequence  $\langle UnitDelay \rangle$ , the name of the state component is  $pid_-Diff_-UnitDelay$ . We observe that such names always identify a definition of the model of a block.

After the state declaration, we include clawz(B). In our example, the schema  $pid_-Diff$ , as well as the schemas  $pid_-Diff_-Sum$  and  $pid_-Diff_-UnitDelay$  used in the specification of  $pid_-Diff$ , are included. They were originally presented in Fig. 4, as part of the ClawZ output.

The initialisation of the state is based on the clawz(B) specification.

| Init                                                                                         |

|----------------------------------------------------------------------------------------------|

| B_State'                                                                                     |

|                                                                                              |

| $\exists b : clawz(B)_{-h}(defi) \bullet clawz(B)_{-h}(defi)_{-state'} = b.initial_{-state}$ |

|                                                                                              |

A state component  $clawz(B)_{-h}(defi)_{-state}$ , corresponding to the component named *state* of the bindings in the set  $clawz(B)_{-h}(defi)$ , is initialised with the value of the component *initial\_state* of the bindings in this set. In *Init*, we identify a binding b of type  $clawz(B)_{-h}(defi)$ ; its value for *initial\_state* defines the initial value of  $clawz(B)_{-defi-state}$ . For instance, if  $clawz(B)_{-h}(defi)$  is a type that models a unit delay block, like in our example,  $clawz(B)_{-h}(defi)$  is a set whose bindings all have the same value for *initial\_state*: that specified in the linear representation of the diagram. In Fig. 10, the definition of the *Init* schema is a very direct instantiation of its characterisation above;  $clawz(B)_{-h}(defi)$  is  $pid_{-D}Diff_{-U}UnitDelay$ .

The definition clawz(B) specifies the state changes resulting from the execution of B as well as its outputs, but clawz(B) is not an operation over the state  $B_State$ : it is a type. We define a schema *Calculate\_B* that lifts clawz(B) to a data operation on  $B_State$ . It includes the input and output variables *In1?*, *In2?*, *Out1!*, *Out2!*, and so on, of clawz(B), following the standard Z style of specifying data operations. In *Calculate\_B*, we identify a binding b of type clawz(B) using the input values in Ini? to determine the value of the Ini? components of b, and the *\_state* components to determine the value of the corresponding *.state* components of b. The new value of the state and the outputs are defined by b.

| _ | _ Calculate_B                                                                                            |

|---|----------------------------------------------------------------------------------------------------------|

|   | $\Delta BState$                                                                                          |

|   | lni?, Outj! : ₪                                                                                          |

| ╞ | $\exists b : clawz(B) \bullet$                                                                           |

|   | $b.\text{lni}? = \text{lni}? \land b.d(\text{defi}).state = \text{clawz}(B)\h(\text{defi})\_state \land$ |

|   | $b.d(\text{defi}).state' = \text{clawz}(B)_{-}h(\text{defi})_state' \land b.\text{Outj}! = \text{Outj}!$ |

If  $B_State$  has a component clawz(B)\_ $h(defi)_state$ , it is because clawz(B) has a component that can be selected using defi with *state* and *state*' components. This justifies the references above to  $b.d(defi)_state$  and  $b.d(defi)_state'$ . The result of d(defi) is the .-separated list of the names in defi.

If clawz(B) does not involve any such component defi, then the set of bindings specified by  $Calculate_B$  is actually the same as that specified by clawz(B). In this case,  $Calculate_B$  has only the lni? and Outj! components of clawz(B), and its predicate is reduced to  $\exists b : clawz(B) \bullet b.lni? = lni? \land b.Outj! = Outj!$ . It is simple to prove that, for every binding c of type [lni?, Outj! : U], we have that  $c \in clawz(B)$  if, and only if,  $c \in Calculate_B$ . The argument can proceed as follows.

| $c \in Calculate_B$                                                                    |                             |

|----------------------------------------------------------------------------------------|-----------------------------|

| $\Leftrightarrow \exists b : clawz(B) \bullet b.lni? = c.lni? \land b.Outj! = c.Outj!$ | [definition of Calculate_B] |

| $\Leftrightarrow \exists b : clawz(B) \bullet b = c$                                   | [property of bindings]      |

| $\Leftrightarrow c \in clawz(B)$                                                       | [one-point rule]            |

In our example, the schema  $Calculate_Diff$  lifts  $pid_Diff$  to an operation over  $Diff_State$ . For that, we establish a correspondence between the *state* and *state'* components of the bindings in the component UnitDelay of  $pid_Diff$  and the state components  $pid_Diff_UnitDelay_state$  and  $pid_Diff_UnitDelay_state'$ .

Each flow in a block calculates some of the outputs Outj!. For each flow identified by a set f of signals in the domain of df.blocks(B).flows we define an action  $Execute_N_f$ , where  $N_f$  is a unique name determined by the set f. It can be, for instance, formed by a list of the elements in f; that is a unique name, since the flows of a block produce disjoint outputs. In our example, as shown in Fig. 6, the block Diff has a single flow that calculates the value output through the channel  $Diff_out$ . We, therefore, define an action  $Execute_Diff_out$ .

An  $Execute_N_f$  action uses a schema  $Calculate_N_f$  that defines the values of the outputs in f. It is specified in terms of  $Calculate_B$  using the schema calculus: we hide the final value of the state, any inputs that are not required and outputs that are not produced, and conjoin the result with  $\Xi B_State$  so that the state is not modified. The schema  $\Xi B_State$  specifies that the values of the state components are preserved.

$Calculate_{\mathcal{N}_{f}} \cong (Calculate_{\mathcal{B}} \setminus (\alpha B_{\mathcal{S}} State', nrinps, npouts)) \land \Xi B_{\mathcal{S}} State$

where nrinps = { Ini? | df.blocks(B).inps(i)  $\notin$  df.blocks(B).flows(f).rinps } npouts = { Outj! | df.blocks(B).outs(j)  $\notin$  f }

We use  $\alpha S$  to denote a list of the components of a schema S. The set nrinps contains the names lni? of the components that represent the inputs of B, as defined by df, that are not required for the flow f. As a slight abuse of notation, we refer to this set in a hiding, where a list of its elements is required. The same comment applies to npouts, which contains the names Outj! of the outputs of B that are not produced by f.

In our example, we have defined the schema  $Calculate_Diff_out$ , which calculates the value of the output  $Diff_out$  of the block, but does not change  $pid_Diff_UnitDelay_state$ . All inputs are required and the single output of the block is produced, so only the state component is hidden.

The action  $Execute_Nf$  takes the required inputs, and then calculates and produces the outputs of f.

$\begin{aligned} Execute_{\mathcal{N}_{f}} & \widehat{=} \begin{pmatrix} \text{var rinps} : \mathbb{U} \bullet \\ \begin{pmatrix} |||(\text{inp, lni}) : \text{crinps} \bullet (\text{inp}?x \to \text{lni} := x, \{\text{lni}\}); \\ (\text{var pouts} : \mathbb{U} \bullet \\ Calculate_{\mathcal{N}_{f}}; |||(\text{out, Outj}) : \text{cpouts} \bullet (\text{out!Outj} \to Skip, \{\}) \end{pmatrix} \end{pmatrix} \end{pmatrix} \\ \text{where rinps} &= \{\text{lni} \mid \text{df.blocks}(B).\text{inps}(i) \in \text{df.blocks}(B).\text{flows}(f).\text{rinps} \} \\ \text{pouts} &= \{\text{Outj} \mid \text{df.blocks}(B).\text{outs}(j) \in f \} \\ \text{crinps} &= \{(\text{inp, lni}) \mid \text{inp} \in \text{df.blocks}(B).\text{flows}(f).\text{rinps} \land \text{df.blocks}(B).\text{inps}(i) = \text{inp} \} \\ \text{cpouts} &= \{(\text{out, Outj}) \mid \text{out} \in f \land \text{df.blocks}(B).\text{outs}(j) = \text{out} \} \end{aligned}$

First,  $Execute_N_f$  declares variables lni to record the values of the required inputs: those in the set characterised by rinps. Namely, we declare lni when the i-th input is required by f. Once again we refer to a set, in this case rinps, to denote a list of its elements, in this case in the variable declaration. Similarly, to calculate the outputs,  $Execute_N_f$  declares the variables in the set pouts; it contains the name Outj whenever the j-th output is produced by f. In  $Execute_Diff_out$ , there is one input variable In1, and one output variable Out1.

The inputs of a block can be received in interleaving, that is, in an arbitrary order, through each of the channels inp corresponding to an input required by f. The set crinps contains the pairs (inp, lni) where inp is a channel that corresponds to a required input of f, and i, used to form the name lni, is the position of that input of B. In  $Execute_N_f$ , actions inp? $x \to \text{lni} := x$  that take an input x through the channel inp and assign it to the local variable lni are interleaved. This is formalised as an iterated interleaving over all pairs (inp, lni) in crinps. The name lni is used to define the name partition of the interleaved action, as required by the interleaving operator for actions to enforce absence of conflict in the access to state components and local variables (see Sect. 3.2). We use the pair (inp? $x \to \text{lni} := x$ , {lni}) to describe that each interleaved action inp? $x \to \text{lni} := x$  is associated with the partition {lni}.

Similarly, outputs are sent in interleaving through the channels out in f. The value output through such a channel out is that in Outj, where j is the position of the corresponding output in B. The value of Outj is defined by the schema  $Calculate_N_f$ . The pairs (out, Outj) are the elements of the set cpouts. The interleaved actions do not change any state components or local variables, so their name partitions are empty. In our example, there is only one input and one output, so in *Execute\_Diff\_out* the interleaving is reduced to a single prefixing. The required input is E; as the only input, its position is 1, so the corresponding variable in rinps is In1. The only output is  $Diff_out$ , with corresponding variable Out1.

After the specification of all the actions  $Execute_{-}N_{f}$ , an action Flows combines them in parallel.

$Flows \cong \| f: \text{dom} df.blocks(B).flows \bullet (Execute_N_f, df.blocks(B).flows(f).rinps, \{\})$

The alphabets of each of the parallel actions  $Execute_N_f$  are the required inputs of f. This means that any inputs that are required by more than one flow are shared by synchronisation. There are no shared outputs. The flows do not change any of the state components, so each of the parallel actions  $Execute_N_f$  are associated to the empty set {} of variable names in the parallelism. Above, we describe each of a parallel actions as a triple, containing the action, and its associated alphabet and name set. Since in Diff there is only one flow, in Fig. 10, the parallelism in the action  $Execute_Diff_out$ .

The schema *Calculate\_B* is also used to define a schema *Calculate\_B\_State* as specified below; it defines the new value of the state after the execution of the block B.

$Calculate_B_State \cong Calculate_B \setminus (Outj)$

where  $j \in 1 \dots #df.blocks(B).outs$

In *Calculate\_B\_State* all output variables Outj of *Calculate\_B* are hidden. An example is presented in Fig. 10: the action *Calculate\_Diff\_State*, which is defined in terms of *Calculate\_Diff* by hiding *Out1*!.

The action State Update that updates the state takes all the inputs in df.blocks(B).inps in interleaving. Like in *Execute\_N*<sub>f</sub>, appropriate variables are declared to record inputs, but all inputs are required.

$$StateUpdate \stackrel{\frown}{=} \left( \begin{array}{c} \operatorname{var} \operatorname{Ini} : \mathbb{U} \bullet \\ \left( \begin{array}{c} \|\|(\operatorname{inp}, \operatorname{Ini}) : \operatorname{cinps} \bullet (\operatorname{inp} ? x \to \operatorname{Ini} := x, \{\operatorname{Ini}\}); \\ Calculate\_B\_State; \end{array} \right) \end{array} \right)$$

where cinps = { (inp, lni) | inp = df.blocks(B).inps(i) }

In our example, we declare an action StateUpdate which takes the only input through E and executes the action specified by  $Calculate_Diff_State$  to update the state.

As explained previously, the main action at the end of the process definition specifies its behaviour. For B, it is as shown below. It starts with the initialisation, and recursively proceeds in parallel to execute each of the flows and update the state, before synchronising on  $end_cycle$ . The flows proceed independently, but a block can only start a new cycle when all the flows, (and all the blocks of the diagram) have finished.

• Init;

$$\mu X \bullet (Flows [[ \{ \} | rlnps | \{ \alpha B_State \} ]] StateUpdate ); end_cycle \rightarrow X end$$

The flows do not update the state, and so the action Flows is associated with the empty set {} of variable names; on the other hand, StateUpdate is associated with the set  $\alpha B_State$  including all state components. The synchronisation set rlnps contains all the inputs required by at least one flow of B. This is because, when an input is received, it needs to be made available to the flows that require it and to the action that updates the state, and so they all synchronise to receive the shared input.

$\mathsf{rInps} \mathrel{\widehat{=}} \bigcup \{\!\!\! \{ f: \mathrm{dom}\, \mathsf{df.blocks}(B).\mathsf{flows} \bullet \mathsf{df.blocks}(B).\mathsf{flows}(f).\mathsf{rinps} \ \!\!\! \}$

As already observed, not all inputs are necessarily required by a flow. Therefore, if we took the range of df.blocks(B).inps as the synchronisation set, we would be too restrictive. If a block has no state, the recursion in the main action only executes *Flows* followed by the synchronisation on *end\_cycle*.

### 4.4. The diagram

As already indicated, our *Circus* model abstracts from specific timing aspects of a Simulink diagram; it ignores, for instance, definitions of sampling periods and step sizes that determine the length of the cycle size. Instead, we use synchronisation (on the channel  $end_cycle$ ) to make sure that the calculations embedded in the blocks are kept in step and, therefore, take the correct inputs and specify the expected outputs. In this context, the time-based block diagram semantics is reduced to that of a data flow chart [Mat].

Accordingly, to define the semantics of a Simulink diagram, we use basically the CSP standard approach to modelling networks of components [Hoa85]. As explained above, each box (block) is modelled as a process, and each line (wire) is modelled as a channel. To give the semantics of the network (diagram), we therefore use the parallel composition of the block processes, with the synchronisation sets defined by the channels in their interface. (In CSP terminology, these block diagrams are called connection diagrams.)

The synchronisation required by the parallelism in the model of a network of processes determines the possible flows of execution for the diagram. A connection is modelled by a synchronisation on the same channel. In the case of our model, the channels are those that represent inputs and outputs of the diagram, and those named after the outputting block with the \_*out* suffix.

For the PID, for example, synchronisation ensures that the input taken through the channel E is shared by the processes Diff, Sp, and Si. On the other hand, since these processes do not synchronise with each other on any other of their data channels, their subsequent execution is independent. Each block process recurses to proceed with the next cycle of calculations; to make sure that they all finish (and start) a new cycle together, we require that they synchronise on  $end_-cycle$ .

Finally, we hide all channels that represent internal wires, rather than inputs and outputs. From the point of view of the user of the control system modelled by the diagram, data flowing in these wires is invisible. In fact, they are just a modelling device used to specify the system as a control law diagram. By regarding them as internal channels, we are providing a specification that encapsulates the structure of blocks. In practical terms, this means that, in an implementation, we do not need to have a separate process for each block; refinement can lead to combination and splitting of blocks.

Precisely, the *Circus* model for the whole diagram is a process called df.spec defined as the parallel execution of all the block processes as specified below.

**process** df.spec  $\widehat{=}$  ( || B : dom df.blocks  $\bullet$  (B,  $\alpha$ B)) \ (Signal \ (df.inputs  $\cup$  df.outputs)) where  $\alpha$ B = ran df.blocks(B).inps  $\cup$  ran df.blocks(B).outs  $\cup$  {*lend\_cycle*}

The alphabet  $\alpha$ B of each block B includes its inputs and outputs, and *end\_cycle*. Signal is the set of all channels that correspond to wires in the diagram: all except *end\_cycle*. Therefore, the set defined above as Signal (df.inputs  $\cup$  df.outputs) includes all channels that represent neither an input nor an output of the diagram: they correspond to the wires that connect blocks.

For the PID diagram, the Circus model is the process defined below.

process  $PID \cong$ Si {  $E, Ki, Si_out, end_cycle$  }  $\left(\begin{array}{c} Si \ \| E, Ki, Si\_out, end\_cycle \ \| \\ \| \\ Diff \ \| E, Diff\_out, end\_cycle \ \| \\ \| \\ Int \ \| Si\_out, Int\_out, end\_cycle \ \| \\ \| \\ Sd \ \| Kd, Diff\_out, Sd\_out, end\_cycle \ \| \\ \| \\ Sp \ \| E, Kp, Sp\_out, end\_cycle \ \| \\ \| \\ Sum \ \| Sd \ out, Sp \ out, Int\_out \ Y \ end \ cycle \ \| \\ \end{array}\right) \setminus \{Si\_out, Diff\_out, Int\_out, Sd\_out, Sp\_out \ \| \\ Sum \ \| Sd \ out, Sp \ out, Int\_out \ Y \ end \ cycle \ \| \\ \end{array}\right)$

As hinted above, the processes  $S_i$ , Diff and  $S_p$ , for example, are required to synchronise on the input channel E that they share, and on end\_cycle. This is exactly the intersection of their alphabets. Similarly, the internal channel  $Diff_out$  is in the alphabet of both Diff and Sd; so, these processes are required to synchronise on *Diff\_out* and *end\_cycle*. All the *\_out* channels are hidden.

By modelling the wiring via channels, and allowing the definition that an output can be produced (that is, communicated) before an input is received, we can cope with feedback loops. More specifically, in such a case, the input and output are modelled by parallel actions. History is kept in the state.

As said before, typically a diagram is hierarchical, in the sense that some blocks may be themselves defined by other diagrams. In general, at the top level we have a diagram with a single block that takes all the inputs and produces all the outputs of the system. If we use this single-block diagram to generate a Circus model, we obtain a single process encapsulating the ClawZ output. This is the most adequate model for the verification of a sequential implementation: we basically use the current ClawZ technique [CC06]. On the other hand, if we have a parallel implementation as a target, we should work with a *Circus* model of the diagram that defines the top-level block (and remove parallelism as needed, as explained in Sect. 6).

In our example, we use the parallel *Circus* model presented in Sect. 4 for the diagram in Fig. 2, because we have a parallel implementation as a target. Since the implementation of the Diff block, for example, is sequential, we do not need to use the alternative parallel model that would be generated by the translation of its diagram in Fig. 3. In this parallel model of Diff, there would be, for instance, a channel Unit\_Delay\_out corresponding to the communication between the Unit Delay and the Sum blocks in Fig. 3. This parallel model of Diff would be architecturally more elaborate than its sequential implementation. Since Unit\_Delay\_out is internal, this parallel model would be equivalent to the sequential model provided in Fig. 10 for Diff, but the latter is more adequate for our verification.

As already indicated, our simple example does not illustrate parallel flows in blocks, but parallelism does show up in the diagram model, reflecting the fact that the three correction actions can be calculated independently. The PID model is appropriate in both size and complexity to illustrate the main concepts and strategies involved in our verification technique. In the next section, we present an implementation of our PID, before discussing how we can prove that such implementation is correct.

## 5. Ada programs and their *Circus* models

The only realistic design for a system like the PID is a sequential implementation, because this is a very simple and small control system. In this case, to prove its correctness, we do not need *Circus*: the current technique based on ClawZ is enough. To illustrate the application of our refinement technique, however, we consider a parallel implementation, whose architecture is representative of those commonly used in embedded control systems where time is critical and processing resources are limited. The use of more powerful microprocessors reduces the need for concurrency for performance reasons; however, fault-tolerant architectures still require concurrent master/slave implementations. The growing requirement for multiple linked control systems (such as a flight, engine, and fuel control systems) means that overall system control still requires concurrent implementations as that presented in the sequel for our simple PID example.

Fig. 11. Architecture of the Ada implementation

```

with F_Sch; use F_Sch; with PID;

with Timing; use Timing; with Task_3;

procedure Exec_3 is begin

package body Task_3 is

Task_3.Init;

loop

procedure Init is

delay until Start_Time;

begin

Task_3.Step;

PID.Init_Derivative;

delay until End_Time;

end Init;

end loop;

end Exec_3;

procedure Step is

begin

if Cur_F = 1

then

PID.Calc_Derivative;

else -- Cur_F = 2

null:

end if;

end Step;

end Task_3;

```

Fig. 12. Ada code of Exec\_3 and Task\_3

Typically, the cycle of the diagram is broken down into time frames, and schedulers determine the subprograms that are executed in each time frame. For our PID example, we have an Ada implementation in which the cycle is broken into two frames. In complex applications, the use of frames is slightly more complicated than this, with the need for major and minor time frames, but using a single kind of time frame is enough to illustrate the principles of our verification technique.

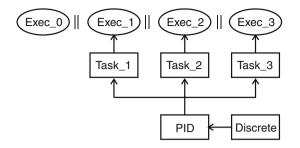

Our implementation comprises four main programs Exec\_0, Exec\_1, Exec\_2, and Exec\_3, which execute concurrently. The notion of main program is not part of the Ada model of concurrency. In fact, the Ada multi-threading facilities are not used in the implementations that we consider: the main programs are Ada procedures that are executed by different processors. Figure 11 presents the architecture: we use ellipses to distinguish the procedures that correspond to the main programs; the double bars indicate that they run in parallel. Each of them initialises a few variables, and loops; the body of the loop executes for the duration of a time frame, and schedules part of its functionality.

We present in Fig. 12 the code for the procedure Exec\_3. It uses an Ada package Timing, which declares constants that characterise the frame, and variables like Start\_Time and End\_Time, which are used to define the time to start and to finish the computations of a frame. Another package, Task\_3, implements the scheduling for Exec\_3. After executing the initialisation procedure of Task\_3, that is, Task\_3.Init, the procedure Exec\_3 loops: at the start of each frame, it carries out the scheduled tasks, as defined in the procedure Task\_3.Step, and waits until the end of the frame to proceed.

The package Task\_3 is also presented in Fig. 12. It uses another package F\_Sch that declares a frame counter Cur\_F. It also uses a package PID, which implements the functionality of the blocks. The initialisation procedure of Task\_3, named Init, initialises the state of the Diff block using the procedure Init\_Derivative of the package PID, which we present in Fig. 13. In the procedure Step, Task\_3 schedules Calc\_Derivative, also a procedure of the PID package, in the first frame of every cycle; it carries out the calculations of the Diff and Sd blocks. The implementation of PID uses one further package, Discrete which provides procedures of general interest to calculate differentials and integrals.

```

procedure Calc_Integral is

with Discrete:

with External_Inputs; use External_Inputs;

begin

with External_Outputs; use External_Outputs;

Discrete.Integ (

Input => Error,

package body PID is

Κ

=> Ki,

Output => I);

end Calc_Integral;

Diff_Mem : Float;

procedure Init_Integral is

procedure Calc_Derivative is

begin

begin

I := 0.0:

Discrete.Diff (

end Init_Integral;

Input => Error,

=> Kd,

Κ

procedure Init_Derivative is

Mem

=> Diff_Mem,

Output => D);

begin

Diff_Mem := 0.0;

end Calc_Derivative;

end Init_Derivative;

procedure Calc Output is

procedure Calc_Proportion is

begin

Position := P + I + D;

begin

\tilde{P} := Kp * Error;

end Calc_Output;

end Calc_Proportion;

end PID;

```

Fig. 13. Ada code of PID

The main programs Exec\_1, Exec\_2, and Exec\_3 are all associated with a frame scheduler: Task\_1, Task\_2, or Task\_3. They are depicted in Fig. 11, where we use squares to indicate that they are Ada packages; they are connected to the procedures that use them. The procedure Exec\_0 only maintains timing information: it updates, for example, Start\_Time, End\_Time, and Cur\_F. Synchrony between the main programs is maintained by the use of delay until commands, which all rely on the values of the shared variables Start\_Time and End\_Time to determine the right time to start and end a frame.

In practice, Exec\_0 corresponds to an ASIC timer that regulates the execution of time frames. The procedure Exec\_1 implements the blocks Sp and Sum; Exec\_2 implements the blocks Si and Int; finally, Exec\_3, as already discussed, implements the blocks Diff and Sd.

To summarise, our verification strategy is for Ada implementations whose architecture can be characterised by: (1) the number of frames in which the cycle is broken; (2) the number of Exec procedures that define parallel processes; (3) the set of procedures that implement the functionality of a group of blocks; and (4) the allocation of these procedures to frames defined by each of the Task packages. This architectural pattern, in our experience, is characteristic of applications developed in military avionics.

At the moment, ClawZ can verify the correctness of only the procedures that implement block functionality. Our strategy covers their coordinated use in the way just explained. As a side effect, it ensures that any assumptions taken as preconditions for the verification of a procedure are discharged. This is achieved with the same level of automation of ClawZ, which has already proved to be acceptable in an industrial setting.