Ferhat Khendek Rachida Dssouli (Eds.)

# Testing of Communicating Systems

17th IFIP TC6/WG 6.1 International Conference TestCom 2005 Montreal, Canada, May/June 2005, Proceedings

ifip IFIP TC6

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos New York University, NY, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Ferhat Khendek Rachida Dssouli (Eds.)

# Testing of Communicating Systems

17th IFIP TC6/WG 6.1 International Conference TestCom 2005 Montreal, Canada, May 31 – June 2, 2005 Proceedings

Volume Editors

Ferhat Khendek Concordia University, Department of Electrical and Computer Engineering 1455, de Maisonneuve W., Montréal, Canada H3G 1M8 E-mail: khendek@ece.concordia.ca

Rachida Dssouli Concordia University, Concordia Institute for Information Systems Engineering 1455, de Maisonneuve W., Montréal, Canada H3G 1M8 E-mail: dssouli@ciise.concordia.ca

Library of Congress Control Number: 2005925777

CR Subject Classification (1998): D.2.5, D.2, C.2

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-26054-4 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-26054-7 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

$\otimes$  2005 IFIP International Federation for Information Processing, Hofstrasse 3, 2361 Laxenburg, Austria Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, IndiaPrinted on acid-free paperSPIN: 1143023006/31425 4 3 2 1 0

# Preface

This volume contains the proceedings of the 17th IFIP TC6/WG6.1 International Conference on Testing of Communicating Systems (TestCom 2005). The conference was held at Concordia University, Montréal, Canada, from May 31 to June 2, 2005. TestCom 2005 was organized by Concordia University and was sponsored by IFIP.

Following the trends initiated at the 16th edition of the conference held in Oxford, UK, the first call for papers issued in summer 2004 called for contributions from the general software testing community. The goal of the conference this year was to continue the broadening of the subject. The theme of the conference this year is "Meeting Software Testing." In response to the call for papers, we received 62 abstracts. Out of these abstracts, 53 turned into paper submissions. Each of these submissions was evaluated by at least 3 reviewers from the Technical Programme Committee, with the help of additional co-reviewers when needed. The Programme Committee meeting was held online from January 18 to January 30, 2005. Out of the 53 submitted papers, the Programme Committee selected 24 papers covering the traditional topics of TestCom, such as EFSM/FSM model-based testing, and also papers on general software testing reflecting the new trends in the conference.

We are very grateful to the keynote speaker, Prof. Tom Maibaum, from McMaster University, Hamilton, Canada. Prof. Maibaum addressed TestCom 2005 on this year's theme. He kindly provided an extended abstract, which is also included in this volume.

We are very grateful to the people who contributed to TestCom 2005 in one way or another. We would like to thank the authors of all submitted papers and the members of the Technical Programme Committee for their hard work during the evaluation of the papers and during the selection process. We are thankful to all the co-reviewers who are indispensable for any peer-reviewed volume. We are grateful to the members of the Steering Committee for their advice. Special thanks go to Prof. Guy Leduc, Université de Liège, Belgium, chairman of the Steering Committee, for his support since day one of the organization of TestCom 2005. We would like to thank also the members of the Organizing Committee for their devotion to the conference, and Dean Nabil Esmail from the Faculty of Engineering and Computer Science at Concordia University for his support. All the individuals who contributed to TestCom 2005 are listed in the following pages.

March 2005

Ferhat Khendek Rachida Dssouli

# **Conferences Committees**

#### **Conference Chairs**

R. Dssouli, CIISE, Concordia University, Canada

F. Khendek, ECE, Concordia University, Canada

#### Steering Committee

A.R. Cavalli, INT, FranceR. Groz, LSR-IMAG, FranceG. Leduc, Chairman, Université de Liège, BelgiumA. Petrenko, CRIM, Canada

#### **Technical Programme Committee**

G. von Bochmann, University of Ottawa, Canada S. Dibuz, Ericsson, Sweden P.G. Frankl, Polytechnic University, NY, USA J. Grabowski, University of Göttingen, Germany R.M. Hierons, Brunel University, UK T. Higashino, Osaka University, Japan D. Hogrefe, University of Göttingen, Germany T. Jeron, IRISA, France M. Kim, ICU University, Korea D. Lee, Ohio State University, USA G. Maggiore, TIM, Italy M. Núñez, Universidad Complutense de Madrid, Spain I. Schieferdecker, Fraunhofer FOKUS, Germany K. Suzuki, Kennisbron Ltd., Japan M. Toeroe, Ericsson, Canada A. Ulrich, Siemens, Germany H. Ural, University of Ottawa, Canada M.U. Uyar, City University of New York, USA J. Wu, Tsinghua University, China N. Yevtushenko, Tomsk State University, Russia H. Zhu, Oxford Brookes, UK

# Additional Reviewers

Baptiste Alcalde Gábor Bátori Sergiv Boroday Jiapeng Cai Dongluo Chen Ning Chen John Clark Michael Ebner David de Frutos-Escrig Xiaoming Fu Mohammed Ghriga Arnaud Gotlieb Hesham Hallal Toru Hasegawa Hyoung Seok Hong Cihui Huang

Jiale Huo Akira Idoue Lifa Jin Sungwon Kang Davy Khuu Keqin Li Tian Li Luis Llana Yan Liu Natalia López Stephane Maag Helmut Neukirchen Tomohiko Ogishi Svetlana Prokopenko Ismael Rodrguez Fernando Rubio

Soonuk Seol Xingang Shi Guoqiang Shu Tibor Szabo Beihang Tian Vadim Trennkaev Dario Vieira Elisangela R. Vieira Dong Wang Zhiliang Wang Constantin Werner Edith Werner Xia Yin Xing Yu Gábor Ziegler

# Local Organization Committee

S. Anderson, CIISE, Concordia University

R. Karunamurthy, ECE, Concordia University

S. Tablan, CIISE, Concordia University

### Sponsors

Concordia University, Canada IFIP Springer, Germany

# Table of Contents

| The Epistemology of Validation and Verification Testing                          | 1   |

|----------------------------------------------------------------------------------|-----|

| Passive Testing - A Constrained Invariant Checking Approach                      | 9   |

| Dependence Testing: Extending Data Flow Testing with Control<br>Dependence       |     |

| ·····                                                                            | 23  |

| Comparing Bug Finding Tools with Reviews and Tests                               | 40  |

| Cross-Language Functional Testing for Middleware                                 | 56  |

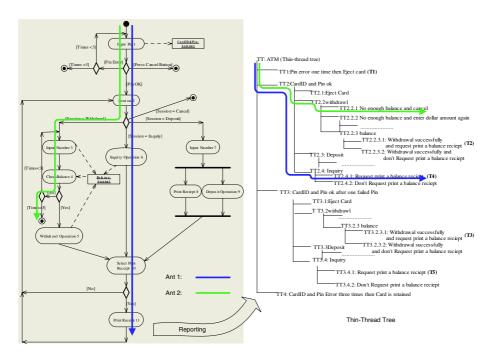

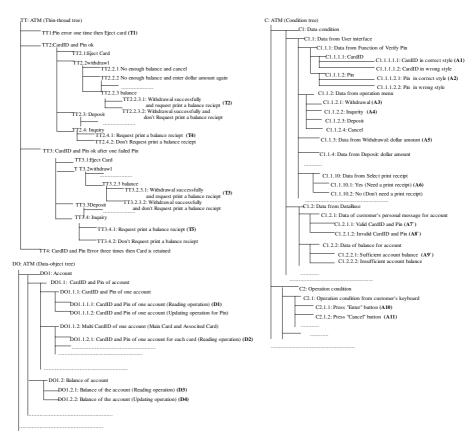

| Using Anti-Ant-like Agents to Generate Test Threads from the UML Diagrams        |     |

| ·                                                                                | 69  |

| Action Refinement in Conformance Testing                                         | 81  |

| Multiplexing of Partially Ordered Events                                         |     |

| ngan segang sena sena negara sena segang sena sena sena sena sena sena sena sena | 97  |

| Testing Communicating Systems: a Model, a Methodology, and a Tool                | 111 |

| Coping with Nondeterminism in Network Protocol Testing                           | 129 |

| Eliminating Redundant Tests in a Checking Sequence                               | 146 |

| On FSM-based Fault Diagnosis                                                     | 159 |

| State Identification Problems for Timed Automata                                 | 175 |

| Timing Fault Models for Systems with Multiple Timers                                                            |     |

|-----------------------------------------------------------------------------------------------------------------|-----|

| in the second | 192 |

| An Expressive and Implementable Formal Framework for Testing<br>Real-Time Systems                               |     |

| · · · · · · · · · · · · · · · · · · ·                                                                           | 209 |

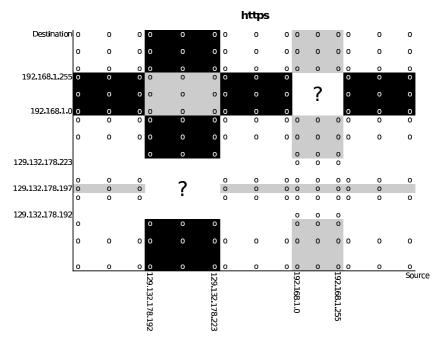

| Firewall Conformance Testing                                                                                    | 226 |

|                                                                                                                 |     |

| Test Generation for Interaction Detection in Feature-Rich<br>Communication Systems                              |     |

|                                                                                                                 | 242 |

| Fault Detection of Hierarchical Networks with Probabilistic Testing Algorithms                                  |     |

|                                                                                                                 | 258 |

| Detecting Trapdoors in Smart Cards Using Timing and Power Analysis                                              | 275 |

| ···· ··· ··· ··· ··· ··· ··· ··· ······                                                                         | 210 |

| From U2TP Models to Executable Tests with TTCN-3 -An Approach to Model Driven Testing-                          |     |

| ······································                                                                          | 289 |

| Using TTCN-3 for Testing Platform Independent Models                                                            | 304 |

|                                                                                                                 |     |

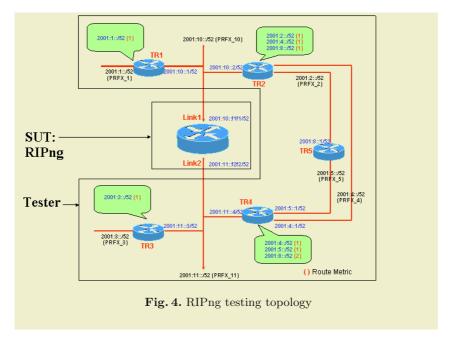

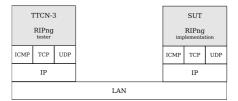

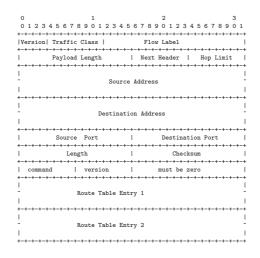

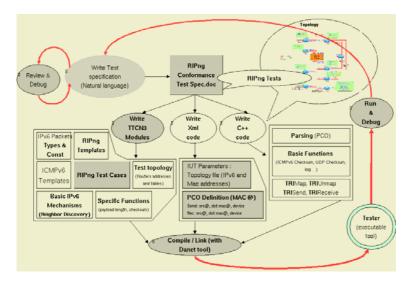

| Some Lessons from an Experiment Using TTCN-3 for the RIPng Testing                                              | 318 |

| A Model-Based Approach for Robustness Testing                                                                   | 333 |

|                                                                                                                 | 000 |

| Content-Level Conformance Testing: An Information Mapping Case Study                                            |     |

| ····· · · · · · · · · · · · · · · · ·                                                                           | 349 |

| Quiescence Management Improves Interoperability Testing                                                         | 365 |

|                                                                                                                 | 200 |

| Author Index                                                                                                    | 381 |

# The Epistemology of Validation and Verification Testing

T.S.E. Maibaum

Department of Computing and Software McMaster University tom@maibaum.org

Abstract. We wish to be able to give formal definitions (in the sense of science or engineering) for concepts like requirements validation and for the relationship between a requirements specification and an abstract design of the intended system. Ditto validation of designs and the final executable application with respect to the original "application concept", on the one hand, and the requirement specification, on the other. We have been developing a framework based on the work of the logical empiricists and other analytic philosophers over the last 80 years to support our understanding of software engineering concepts. Recent developments (dating from the 80s)in the area of "confirmation" (of a hypothesis concerning a theory by some (experimental) evidence) promises to illuminate some of these problematic concepts. In this talk we address the problem of establishing the very relation between requirement specifications and scenarios, as used, for example, in UML. The same framework can also be applied to the problem of testing implementations against designs, so called verification testing.

#### **1** Introduction

Requirements engineering (RE) is a black art! We are forever confronted by the assertion that, whilst requirements specifications may be a formal entity, analysable even in a mathematical sense, it is informally related to an informal "entity", the so-called *application concept*. If we cannot define precisely (and meaningfully) the statement "this scenario confirms (or discomfirms) this behaviour specification", then how can we pretend we know what a behaviour specification (and therefore a requirements specification) specifies? Suppose further that we are interested in questions such as the following: Is requirements language X better than Language Y for defining the requirements of applications of class W? On what basis can we justify the fact that we like the work reported in [21,32,,22,23] and that it says something important about requirements engineering?

On what basis can we answer these questions so that the answers can be justified on a "scientific" or "engineering" basis? If we cannot answer the first question, how can we begin to address the others? If some entities and relationships are informal, what is there left aside from anecdote to support requirements "meta-analysis"? The

© IFIP 2005

Original version co-authored with the late AM Haeberer and with the assistance of MV Cengarle, then of Institut für Informatik, Ludwig-Maximilians-Universität München.

purpose of this talk is to demonstrate that a *framework* can be defined, turning the "informal" entities and relationships of the above discussion into well defined concepts that are amenable to formal analysis.

# 2 Gedanken Experiments, Requirement Specifications and Confirmation

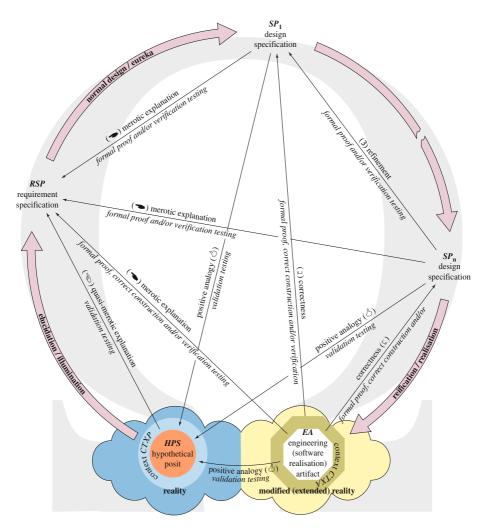

In former papers [16,17, 6,7, 8] we have endeavoured to lay the basis for the epistemological analysis of software engineering. In [17], we analyse superficially the relationships among the various objects in a metamodel of the software process we posited (called W) and which is reproduced in Figure 1.

At the leftmost lower corner of this figure we see the factual<sup>1</sup> relation *HPS+CTXP*  $\Im$  *RSP*, where *HPS* is what we called the hypothetical posit of the intended software artifact *EA* in [17], *CTXP* its context, and *RSP* the requirements specification for *EA*. In [17] we claim that the relation  $\Im$ , whose analysis is the purpose of this talk, is what we called there a *quasi merotic explanation*.

To be able to study formally the leftmost lower hollow arrow in Figure 1, which is nothing but the notorious process of *ab initio* requirements elicitation, we need a framework in which we can reason about the nature of this process, about the objects *HPS*, *CTXP*, and *RSP*, and about the relation  $\mathscr{P}$ . It is the purpose off his talk to analyse the nature of this relation and, in order to do that, to establish an adequate framework for reasoning about it and the objects involved. It is very important to bear in mind that, in its present state, the  $\Omega$  meta-model is idealised in various ways; one of them is that we are considering *ab initio* development, meaning that we are not considering legacy artifacts. This means that we consider requirement specifications as being elicited from (hypothetical) scenarios in which there are no legacy software artifacts or systems, and therefore, this eliciation process does not involve design recovery. Moreover, we will assume that there is no existing software artifact or system from which we can glean a single clue about decomposition; thus, merotic explanations<sup>2</sup> are inhabitants of our post-requirements world.

The process we have in mind for devising a new engineering artifact is as follows. See the figure at the end of this extended abstract. We have a somewhat vague requirement (called *protoRSP*) for a new artifact to be, *EA*, which at this point is merely a hypothetical posit HPS. This vague requirement protoRSP is actually a set of properties we know (or we desire) the artifact to be (represented here by the hypothetical posit) should exhibit. These properties are of two kinds, i.e., abstract (theoretical) ones, such as, for instance, behaviours, and their observable counterparts, i.e., sets of observable instances of them, which we will call evidence E (e.g., scenarios). In our engineering setting, evidence is produced both by the operation of an engineering artifact EA (after its construction!), or by the operation of an hypothetical posit HPS, as in a gedanken experiment. The sets of such evidence are part of what we are calling here the context CTXA of the engineering artifact EA, or the context CTXP of the hypothetical posit, respectively. Then, we construct an extension of the language belonging to our underlying science/technology and to the already existing engineering discipline with the necessary symbols, etc., to enable us to state precisely the requirements specification RSP, and to show how evidence produced by the operation of the hypothetical posit HPS confirms RSP, and that (if the status of our current technology makes its construction viable) the resulting engineering artifact EA will be in a certain relation with HPS that enables us to expect that

<sup>&</sup>lt;sup>1</sup> We classify the relationships among the objects in the  $\Omega$  meta-model into factual and logical, as we have done in [H&M00]. We give an exact definition of these clasificatory terms below.

<sup>&</sup>lt;sup>2</sup> An exact definition of what a merotic explanation is can be found in [17]. Informally speaking, we can consider that the structure of the resulting software artifact *EA* in a software process satisfying the  $\Omega$  meta-model (or any of the series of increasingly reified design specifications *SP<sub>i</sub>*) provides an explanation of why the requirements specification predicts (and retrodicts) correctly its operation. Since this explanation is composed from parts following *EA*'s (or *SP<sub>i</sub>*'s) structure, it was called "merotic".

*EA* will also produce evidence that *confirms RSP*. (As we argue in [17], this relation is a positive analogy, i.e., *HPS*  $\diamond$  *EA*. See the figure.) Then, we construct *EA*, through a process of design and reification, which adds design and realisation detail to the above extension.

If, on the one hand, *protoRSP* is a description in everyday language, or in a previous stage in the development of our scientific/technological language, of the evidence produced by *HPS* and, on the other hand, *RSP* is the exact description of the behaviour confirmed by evidence produced by *HPS* or *EA*, then we may be tempted to characterise *protoRSP* as what Carnap [4] calls an *explicandum* and the corresponding requirement specification *RSP* as its *explicatum*, both related by an *explication*<sup>3</sup>. As Carnap stated [4] "the task of explication consists in transforming a given more or less inexact concept into an exact one or, rather, in replacing the first by the second. We call the given concept (or the term used for it) the <u>explicandum</u>, and the exact concept proposed to take the place of the first (or the term proposed for it) the <u>explicatum</u>."

The analysis of the reason why we said that this is a simplistic viewpoint will introduce the core points of this talk. Notice that we had distinguished between, on the one hand, evidence, which is observable (perhaps with the aid of certain apparata), such as scenarios, and, on the other hand, certain abstract (mathematical) objects, such as behaviours. These abstract properties are of a very dangerous kind, because if we become overenthusiastic in their introduction, we can obtain a complete zoo of scientifically useless abstractions, such as, for instance, phlogiston, vital force, or entelechy. (Software engineering, as all the novel disciplines whose corpus is not well defined, is especially prone to accept such useless abstractions.) However, mass in physics is one of these concepts (as is *force*); mass is needed to state Newton's principle for relating force with acceleration. Otherwise, Newtonian mechanics cannot be developed, or even stated. If we look to current scientific language, even that familiar to laymen, we find many abstract terms denoting abstract objects or properties, such as, for instance, gene, electron, magnetic field, preservation of the angular momentum, or esprit de corps. For instance, some of Kepler's laws can be stated in a language the designata of whose nouns would be accepted by everyone as observables. However, this is not the case with Newtoninan Dynamics; terms such as angular momentum, gravitational field, and universal gravitational constant have non observable designata. Notwithstanding, nobody will say that these terms are useless; without them Newtonian Mechanics is unthinkable. The difference between Kepler's laws and Newtonian mechanics is the difference between empirical generalisations and scientific theories. This difference resides in their respective predictive powers; from Kepler's laws we can infer the movements and positions of the planets, whilst from Newtonian Mechanics we can infer the same but also particular laws, such as Kepler's laws. Unfortunately, it seems that the existence of such terms (nouns) with non-observable designata, is a must if we want an expressive scientific theory, or a statement belonging to a scientific theory, and not an empirical generalisation.

<sup>&</sup>lt;sup>3</sup> Notice that in this context (i.e., that of the Philosophy of Science) *explication* and *explanation* are not synonymous; we are using *explication* in the particular sense we are discussing, and *explanation* in the sense of *scientific explanation*.

However, an exaggerated use of theoretical terms leads us down the path to metaphysics, so Occam's razor comes into play. In our case, we have evidence, as for instance the collection of behavioural data hypothetically generated by an hypothetical posit, which can be stated in a language the designate of whose nouns are observable, and we have abstract objects, such as behaviours, which do not designate observable things, but from which we can infer hypotheses potentially confirmable by evidence (e.g., scenarios in UML). Thus, the vocabulary of the language whose nouns designate observable things and properties is smaller than the vocabulary of the language whose nouns designate representatives of these observable things plus abstract things and properties. Furthermore, the restriction of *observability*<sup>4</sup> of the former language makes wider the difference between the two languages, for it is obvious that universal quantifiers in the former must be finite, i.e., equivalent to generalised finite conjunctions (neither our senses nor any physical instrument enables us to observe a whole from infinitely many parts), whilst those of the latter language can be, and are usually, infinite. Moreover, we can have in the latter language modalities, such as permission and obligation, and temporal quantifiers, such as forever, once, and sometime in the future.

The principal problem is, in Clark Glymour's words [12], "How can evidence stated in one language confirm hypotheses stated in a language that outstrips the first? How can one make an inference from statements in the narrower language to statements in the broader language? The hypotheses of the broader language cannot be confirmed by their instances, for the evidence, if framed in the narrower tongue, provides none. Consistency with the evidence is insufficient, for an infinity of incompatible hypotheses may obviously be consistent with the evidence. The structure of the problem is: what relations between [...] observation statements, on the one hand, and statements [...] about unobservable things or unobservable properties, on the other hand, permit statements of the former kind to confirm statements of the latter kind?".

From what we have said above, it seems plausible to say that the relation  $\Im$  is one of confirmation between the evidence produced by *HPS*, on the one hand, and *RSP*, on the other. As a first approximation we can state the following:

**Definition.** Evidence E confirms RSP iff we can use some hypotheses deduced from RSP to deduce from E other hypotheses deducible from RSP.

This idea about the mechanism by which we can decide if a theory agrees or disagrees with a piece of evidence (observable) was first conceived by Carnap [5] and later explored and developed by Clark Glymour [12]. Let us call the former hypotheses in the above definition, *bootstrap hypotheses*; thus, our definition can be re-stated as: *evidence E confirms RSP iff we can deduce from RSP a set of bootstrap*

<sup>&</sup>lt;sup>4</sup> We are using *observable*, *observability*, and *abstract*, without giving a precise definition of what we are referring to. We will give precise definitions for them, actually for their exact counterparts, which will have the same spelling but which will actually be different terms with exact meanings, i.e., *designata*.

<u>subtheories of RSP</u> which enable the deduction from E of other hypotheses deducible from RSP. It is exactly in the conditions established for the deduction of bootstrap subtheories where, for instance, the necessary application of Occam's razor we had talked about above must be embedded. Such requirements are the source of the complexity of the confirmation procedure (the so-called bootstrap strategy of confirmation) we introduce below in the talk.

In discussing confirmation, we must here make something very clear. We need to separate carefully two different issues. The frst is the mechanism by means of which we can decide that a certain piece of evidence "agrees" or "disagrees" with a given theory. We will talk below of two of them: one is that succinctly presented in the discussion that led to the definition above and the other is the notorious and flawed hypothetico-deductive method (of Newton and others). The second is the criterion of confirmation. We can informally explain this issue by contrasting some of the proposed criteria. One, which we will call Popperian falsifiability (also used in the hypothetico-deductive method), is: if the evidence disagrees with the theory (we need some mechanism for deciding this, i.e., the first issue), then the theory should be discarded; conversely, if the evidence agrees with the theory, then we do not have any new information about the appropriateness of the theory for describing the phenomenon producing the evidence. Another criterion, advanced by Lakatos, says that a theory is something resulting from a difficult and expensive process and, therefore, nobody is willing to discard it because of a mere disagreement with a piece of evidence; so an auxilliary hypothesis is created to explain the disagreement. Finally, the Carnapian logical measure function [4] presents a criterion of confirmation based on degrees of confirmation: if the evidence disagrees with the theory, one can blame the theory or certain auxilliary hypotheses about the experimental method producing the evidence, the measurement instruments, etc. But actually, as in the Popperian case, we blame something, often the theory itself. The main difference between the Carnapian criterion of confirmation and Popperian falsifiability is about what we do when the theory agrees with the evidence. Here, instead of saying that we do not have more information about the appropriateness of the theory, we will say that the degree of confirmation of this theory is greater than the degree of confirmation of a theory not agreeing with this piece of evidence. Carnap associates with this degree of confirmation a logical function (which he calls Logical Probability [4]). This logical function is strongly related with Carnap's inductive logic (and today with theories about belief revision).

In this talk we will deal only with the first issue, i.e., how we can decide that a requirements specification *RSP* agrees or disagrees with a piece of evidence hypothetically produced by the hypothetical posit *HPS*. The second issue will be treated in a forthcoming paper, since if we adopt the Carnapian logical measure function, we should inspect also Carnap's inductive logic and his "continuum of inductive methods", which will bring us closer to the issue of requirements elicitation, and, therefore, to the leftmost lower hollow arrow in Figure 1. However, to be able to produce an effective setting for this talk, we need to append to the so-called bootstrap mechanism, which deals with the first issue above, some kind of confirmation criterion. We will use a not very complicated one, which is a modification of one put forward by Hempel.

#### References

- 1. Rudolf Carnap, On Inductive Logic. Philosophy of Science, Vol. 12, 72-97. 1945.

- 2. Rudolf Carnap, Continuum of Inductive Methods. Univ. of Chicago Press. 1952

- 3. Rudolf Carnap, *Meaning and Necessity*. Supplement A, *Empiricism, Semantics, and Ontology*. Midway Reprint Edition. 1988.

- 4. Rudolf Carnap, Logical Foundations of Probability. The University of Chicago Press. Second Edition. 1962.

- Rudolf Carnap, An Introduction to the Philosophy of Science (re-edited from Philosophical Foundations of Physics, Basic Books, 1966). Ed. Martin Gardner, Dover Publications, Inc. 1995.

- Maria V. Cengarle and Armando Haeberer, *Towards an epistemology-based methodology* for verification and validation testing. See <u>http://www.informatik.uni-muenchen.de</u> under M.V. Cengarle. 1999.

- María V. Cengarle and Armando M. Haeberer, *Specifications, programs, and confirmation.* Proceedings of the Workshop on Requirements, Design, Correct Construction, And Verification: Mind The Gaps! F.A.S.T. Gesellschaft f

ür angewandte Softwaretechnologie mbH- Munich April 2000. http://www.fast.de

- Cengarle, M V., Haeberer, A. M.. A formal approach to specification-based black-box testing. Proceedings of the Workshop on Modelling Software System Structures in a fastly moving scenario. June 13-16, 2000. Santa Margherita Ligure, Italia. www.disi.unige.it/person/FerrandoE/MSSSworkshop.

- 9. David Christensen, *Glymour on evidential relevance*, Philosophy of Science. Vol 50. 471-481, 1983.

- John Earman and Clark Glymour, What Revisions does Bootstrap Testing Need? A Reply. Philosophy of Science. Vol. 55. 261-264, 1988.

- 11. Clark Glymour, *Hypothetico-deductivism is Hopeless*. Philosophy of Science. Vol. 47. 322-325, 1980.

- 12. Clark Glymour, Theory and Evidence. Princeton Univ. Press. 1980.

- Clark Glymour, On testing and evidence. In John Earman ed. Testing Scientific Theories, Minnesota Studies in the Philosophy of Science, Vol. X. Univesity of Minnesota Press. 1983.

- 14. Clark Glymour, *Revisions of bootstrap testing*, Philosophy of Science. Vol 50. 626-629, 1983.

- 15. Carl G. Hempel, International Encyclopedia of Unified Science, Vol. 2, No. 7: *Fundamentals of Concept Formation in Empirical Science*. University of Chicago Press. 23-38, 1952.

- Armando M. Haeberer and Tom S. E. Maibaum, *The very idea of software development environments: a conceptual architecture for the arts environment*. In B. Nuseibeh and D. Redmiles, eds. Proc. of 13th IEEE Int. Conf. on Automated Software Engineering (ASE-98), IEEE CS Press, 260–269. 1998.

- 17. Armando M. Haeberer and Tom S. E. Maibaum, *Scientific rigour, an answer to a pragmatic question: a linguistic framework for software engineering*, to appear in Proc. of ICSE2001, 23rd Int. Conf. on Software Engineering. Toronto 2001.

- 18. Mary Hesse. The Structure of Scientific Inference. University of California Press. 1974.

- 19. Jako Hintikka, *Towards a Theory of Inductive Generalization*. In Y. Bar-Hillel, Proc. of the 1964 Congress for Logic, Methodology, and the Philosophy of Science. 274-288. Stanford University Press. 1962.

- 20. Michael Jackson, *Formal Methods and Traditional Engineering*. Journal of Systems and Software special issue on Formal Methods Technology Transfer. Vol. 40. 191-194. 1998.

- Michael A. Jackson and Pamela Zave, *Deriving Specifications from requirements: an Example.* Proc. ICSE'95 - 17th International Conference on SE. IEEE Computer Society Press, 15-24. 1995.

- 22. Axel van Lamsweerde and Emmanuel Letier, *Handling Obstacles in Goal-driven Requirements Engineering*. IEEE Transactions on SE, Vol. 26, September 2000.

- 23. Axel van Lamsweerde and L. Willemet, *Inferring Declarative Requirements Specifications from Operational Scenarios*. IEEE Transactions on SE, Vol. 24, No. 12, 1089-1114. December 1998.

- 24. Tom S.E. Maibaum, *Mathematical Foundations of Software Engineering: a roadmap*. In Eds. A. Finkelstein and J. Kramer, Future of Software Engineering, ICSE 2000. IEEE C.S. Press. 2000.

- 25. 25.E. Nagel, The Structure of Science. Harcourt, Brace. 1961.

- 26. Bryan G. Norton, *Linguistic Frameworks and Ontology*: A Re-Examination of Carnap's Metaphilosophy. Mouton Publishers. 1977.

- 27. Karl R Popper, The Logic of Scientific Discovery. Hutchinson, London 1968.

- 28. Herbert Simon, *The axiomatization of physical theories*. Philosophy of Science. Vol 37. 16-26, 1970.

- 29. Wlad M. Turski, *An Essay on Software Engineering at the Turn of Century*. In Ed. Tom Maibaum, Proc.of Fundamental Approaches to Software Engineering 2000, LNCS 1783, Springer. 2000.

- 30. Wlad M. Turski and Tom S.E. Maibaum, *The Specification of Computer Programs*. Addison-Wesley, 1987.

- 31. Walter G. Vincenti, What Engineers Know and How They Know It : *Analytical Studies from Aeronautical History*. Johns Hopkins U. Press. 1993.

- 32. Pamela Zave and Michael A. Jackson, *Four Dark Corners of Requirements Engineering*. ACM Tansactions on SE and Methodology, Vol. 6, No. 1. 1-30. 1997.

- 33. Jan M. Zytkow, *What revisions does bootstrap testing need*?. Philosophy of Science. Vol 53. 101-109, 1986.

# Passive Testing - A Constrained Invariant Checking Approach

Behrouz Tork Ladani<sup>1</sup>, Baptiste Alcalde<sup>2</sup>, and Ana Cavalli<sup>2</sup>

<sup>1</sup> Department of Computer Engineering, University of Isfahan, Isfahan, Iran ladani@eng.ui.ac.ir

<sup>2</sup> Institute National des Telecommunications GET-INT, Evry, France {ana.cavalli, baptiste.alcalde}@int-evry.fr

**Abstract.** Passive testing of a network protocol is the process of detecting faults in the protocol implementation by passively observing its input/output behaviors (execution trace) without interrupting the normal network operations. In observing the trace, we can focus on the most expected relevant properties of the protocol specification by defining some invariants on the specification and checking them on the trace. While intuitive extraction of the invariants from the protocol requirements with respect to the control portion of the protocol system is relatively simple, taking the data portion into account is difficult. In this paper we propose algorithms for checking the correctness of given invariants on the specification and extracting the required constraints on the variables (data portion). Once we generate the constraints for a given invariant, we can check if the execution trace is confirmed by the specification with respect to the invariant and its constraints. We show the applicability of the algorithm on a case study: the simple connection protocol (SCP).

**Keywords:** passive testing, invariants, invariant checking, constraint solving, SCP.

#### **1** Introduction

Testing network protocol implementations, to assure that they work as their specification, is of high importance. Instead of conventional active testing, there are propositions to use passive testing for network protocol systems, which means observing the input/output behavior of the implementation (i.e. execution trace) without interfering its normal behavior ([1], [2]). The naive approach to passive testing is to record the execution trace and try to find its faults by comparing it with the specification ([3], [4], [5]). Other approaches try to extract the critical properties of the specification in the form of some invariants and then try to observe them on the implementation ([6], [7]).

Most of passive testing methods are focused on the control parts of the system under test without considering the data parts, so it is sufficient for them to use finite state machines (FSMs) as the specification method. To take the data part of the protocols into account, extended finite state machines (EFSMs) are used to specify the system. EFSM uses parameterized input/output signals including variable parameters to encode data as well as predicates and actions to control the firing of the transitions by manipulating the relevant data. There are some methods proposed to perform passive testing using EFSM ([5], [8], [9]). These methods are based on exploring constraints of the variables and comparing the whole specification with the implementation regarding the constraints in a backward or forward manner (i.e. the naive approach).

In this paper we represent a method to perform passive testing based on the invariants on the EFSM. In our approach, first we have to extract the invariants intuitively from the protocol specification requirements regarding only the control portion of the protocols. After that, to take the data portion into account, we consider the invariant parameters as some variables. We present two algorithms for finding the corresponding constraints over the variables of the invariants automatically. The algorithms use the unification method [10] for checking the correctness of the given invariants over the EFSM and finding the constraints over its variables. Having the invariants and their corresponding constraints in hand, we can check the execution trace with the invariants using pattern matching methods.

It should be noted that finding suitable control-driven invariants, especially with the help of an expert is relatively simple; also there are some methods to extract a limited set of invariants from an EFSM automatically [7]. We use the notion of invariant introduced in [11] with little changes in the definitions to extract the control driven invariants intuitively.

The rest of the paper is organized as follows: in section 2 some preliminary concepts needed in the rest of the paper are described. In section 3 the notions of forward and backward invariants are described. In section 4, our algorithms for checking invariants on a given EFSM and extracting corresponding constraints are presented. Section 5 reports some experiments of the algorithms on the Simple Connection Protocol (SCP) to show the applicability of the method in detecting subtle errors in some given traces of the protocol. In section 6 we conclude the paper.

#### 2 Preliminaries

#### 2.1 Extended Finite State Machine

We use Extended Finite State Machines (EFSMs) to specify the network protocols.

**Definition 1.** An *Extended Finite State Machine (EFSM)* M is a 6-tuple M=(S, I, O, x, T,  $s_0$ ) where S is a finite set of states, I and O are the finite sets of input and output parametric symbols respectively, x is a vector denoting a finite set of variables, T is the finite set of transitions, and  $s_0$  is the initial state.

Each transition  $t \in T$  is a tuple (s, s', i, o, P, A) where s, s'  $\in$  S are the initial and final states of the transition respectively,  $i \in I$ ,  $o \in O$  are the input and output symbols (possibly with parameters) respectively, P is the predicate (a Boolean expression), and A is the sequence of actions.

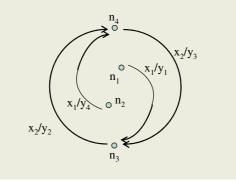

**Definition 2.** Let M=(S, I, O, x, T, s<sub>0</sub>) be an EFSM, the sequence  $i_1/o_1, \ldots, i_n/o_n$  is a *path* in M if for any  $1 \le j \le n$ ,  $i_j \in I$ ,  $o_j \in O$ , and there exist n transitions  $t_1 \ldots t_n \in T$  and n+1 states s,s<sub>1</sub>, ..., s<sub>n-1</sub>,s'  $\in$  S such that  $t_1 = (s,s_1,i_1, o_1)$ ,  $t_n = (s_{n-1},s',i_n, o_n)$  and for any 1<j<n we have  $t_j = (s_{j-1},s_j,i_j, o_j)$ .

#### 2.2 Substitution and Unification

Our algorithms use the unification method, so we borrow some definitions from the context of logic programming.

**Definition 3**. A *substitution*  $\theta$  is a set of bindings, each of the form V/T, such that V is a distinct variable and T is a term.  $\theta$  is called a *renaming* if it maps each variable to a new fresh variable.

Applying a binding V/T to an expression E, replaces each free occurrence of V in E by T. Applying a substitution  $\theta$  on an expression E denoted by E $\theta$  applies all the bindings in  $\theta$  to E simultaneously and independently.

**Definition 4.** Let  $\theta = \{V_1/T_1, ..., V_m/T_m\}$  and  $\alpha = \{U_1/S_1, ..., U_n/S_n\}$  be substitutions. The *composition* of  $\theta$  and  $\alpha$ , denoted by  $\theta \circ \alpha$  is defined as:

$\theta o \alpha = \{ V_1 / T_1 \alpha ,..., V_m / T_m \alpha \} U \{ U_k / S_k | U_k \notin \{ V_1 , ... , V_m \} \}$

**Definition 5.** A *unifier* of two simple expressions E and F is a substitution  $\theta$  such that  $E\theta = F\theta$ . If two simple expressions have a unifier, they are said to be *unifiable*; we also say that E is unified with F by the unifier  $\theta$ . A *most general unifier*, abbreviated as *mgu*, of two simple expressions E and F is a unifier  $\theta$  that is more general than any unifier of E and F. As an example two expressions P(X,f(X)) and P(b,f(a)) are not unifiable, while the most general unifier of the expressions P(X,f(a)) and P(b, f(Y)) is {X/b, Y/a}.

#### 2.3 Normalizing Action Sequences

We need in our algorithms to track the changes in the variable values made by the action sequences in each transition, so we define a special normal action sequence and present an algorithm to normalize a given action sequence. In normalizing an action sequence of a transition, a special renaming substitution is produced which we name the *normalizer substitution* of that action. The normalizer substitution is then used to propagate the changes of the variable values in a transition to predicates and actions of the successive transitions.

**Definition 6.** Let x be the set of variables in an EFSM, also let  $A=(l_1:=r_1, ..., l_n:=r_n)$  be an action sequence of size n in a transition in the EFSM, in which  $l_i \in x$  and  $r_i$  is an expression for  $1 \le i \le n$ . Also suppose that  $R_k = \{V \in x \mid V \text{ is used in expressions } r_1, r_2, ..., r_k\}$  for  $1 \le k \le n$ . A is a *normal action sequence* if  $l_i \notin R_i$  for  $1 \le j \le n$ .

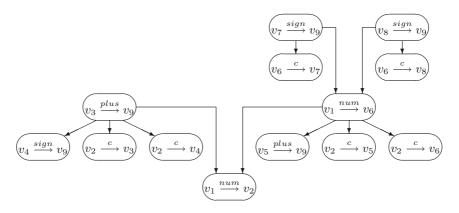

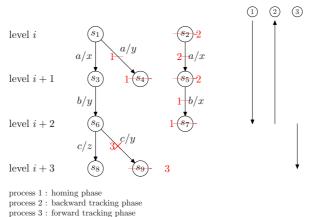

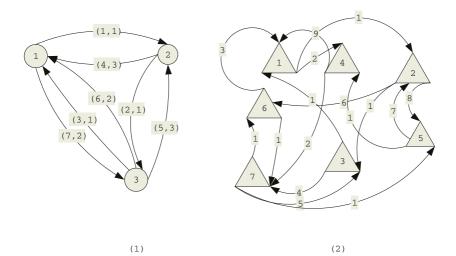

The algorithm depicted in figure 1 change a given action sequence to a normalized one and returns its corresponding normalizer substitution. The algorithm renames the new appearances of the variables whose values are changed in an action sequence. The normalizer substitution of the action is in fact the set of variable renaming substitutions performed in the above process.

#### **3** The Notion of Invariants

In this section we represent the notion of invariants on EFSM as introduced in [11] with little changes in the definitions. An invariant represents a specific property (which should be always true) on an EFSM which is in fact a statement about causal relationships between input/output pairs in the EFSM.

```

INPUT: An action sequence A=(l_1 := r_1, ..., l_n := r_n) in the EFSM

M = M = (S, I, O, x, Tr, s_{in})

OUTPUT: A normalizer substitution \theta

SIDE EFFECT: Action sequence A is changed to a normal one

Begin

\theta := \emptyset;

for i:=1 to n do begin

\mathbf{R} := \{ V \in x \mid V \text{ is used in expressions } r_1, \dots, r_i \}

if l_i \in R then begin

l'_i := new V; /* a new variable name */

\theta := \theta \cup \{ l_i / l'_i \};

l_i := l'_i

for j := i+1 to n do begin

l_j := l_j \theta; r_j := r_j \theta;

end;

end;

end;

End:

```

Fig. 1. Normalizing an action sequence

Regarding the way of expressing the temporal relationships of the input/outputs in an EFSM, two types of invariants are introduced. We call them forward and backward invariants. Note that to define the invariants we only consider the control parts of the protocol so we do not speak about the values of the variables in input or output parameters. In the next section we represent algorithms to find corresponding constraints on the variables of a given invariant that makes it correct on the EFSM.

#### 3.1 Forward Invariants

A forward invariant is used to express properties in the EFSM such as "each time the implementation performs a specific execution trace like  $i_1/o_1, ..., i_{n-1}/o_{n-1}$ ,  $i_n$ , the next observed output belongs to a specific set of output symbols". Based on this definition, we can assume that a forward invariant contains three elements: A preamble I/O sequence, a preamble input and a test output set. Intuitively a forward invariant is correct if for all paths in the EFSM matching with the preamble I/O sequence, and followed by an I/O pair containing an input equal to the preamble input, then the corresponding output essentially belongs to the test output set.

**Definition 7.** Let  $M=(S, I, O, x, Tr, s_{in})$  be an EFSM. We say that the F(PIO, PI, TOS) is a forward invariant for M if the following conditions are respected :

1. PIO is the preamble I/O sequence which is defined according to the following EBNF: PIO ::= a/z, PIO | \*,PIO |  $\epsilon$

In which  $a \in I \cup \{?\}$ ,  $z \in O \cup \{?\}$  and  $\varepsilon$  is the null sequence.

- 2. PI  $\in$  I is the preamble input and TOS  $\subseteq$  O is the test output set.

- 3. Each time that the sequence PIO is matched with any path in the EFSM, and it is followed by any transition with input PI, then we get essentially an output belonging to TOS.

Note that we deal with the wildcard ? as the standard one in pattern matching, while modify the usual meaning of the symbol \*. The symbol \* replaces any sequence of input/outputs not containing any pair with input equal to PI.

#### 3.2 Backward Invariants

Using a *backward invariant* we can express more subtle properties such as "*each time a specific output is produced by the implementation, then we must have that a specific trace had been produced before*". So a backward invariant contains three elements: A preamble output set, a test input and a test I/O sequence. Intuitively a backward invariant is correct if any transition in the EFSM in which its output symbol belongs to the preamble output set, have an input equal to test input and essentially preceded by a path matching with the test I/O sequence.

**Definition 8.** Let  $M=(S, I, O, x, Tr, s_{in})$  be an EFSM. We say that the B(TIO, TI, POS) is a backward invariant for M if the following conditions are respected :

1. TIO is the test I/O sequence which is defined according to the following EBNF:

- in which  $a \in I \cup \{?\}, z \in O \cup \{?\}$  and  $\epsilon$  is the null sequence.

- 2. TI  $\in$  I  $\cup$  {?} is the test input and POS  $\subseteq$  O is the test output set.

- 3. All transitions of M with an output symbol belonging to POS must essentially have an input symbol equal to TI and proceed by a path matching with TIO.

Let us remark that, in contrast with forward invariants (for the case of preamble input symbol), we do not force the test input symbol here to be an input action (it can be also the wildcard character "?"). Furthermore, our matching method is modified such that the symbol \* replaces any sequence of input/outputs not containing any pair with input equal to TI.

### **4** Extracting Invariant Constraints

To use an invariant for passive testing, it is needed to assure at first about the correctness of the invariant on the specification. While checking invariants on a FSM simply returns a Boolean value showing the correctness or fail of the invariant, checking an invariant on an EFSM either returns simply a false Boolean value showing that the invariant is incorrect on the EFSM or returns a set of constraints on the variables of the invariant showing that the correctness of the invariant depends on the set of constraints. For passively testing the implementation, it is sufficient to match the execution trace with the invariant while its constraints regarding the value of the variables in the trace don't conflict. In this section we represent algorithms for checking forward and backward invariants on an EFSM and extracting their corresponding constraint set. The constraint extraction process is done once and off-line.

#### 4.1 Forward Invariant Constraints

To check a given forward invariant on an EFSM, first we have to find the paths in the EFSM which are unifiable with the preamble part of the invariant. After that we should check if the invariant test set is reachable using all the unified paths or not, and if it is

reachable, then what is the constraint set to make it true. The constraint set is in fact constructed during the unification of the preamble part with the paths in the EFSM.

**Definition 9.** Let  $\rho = i_1/o_1, ..., i_n/o_n$  be an input sequence of size n and M=(S, I, O, x, Tr,  $s_{in}$ ) be an EFSM, we define  $U_n$  as the set of *forward matchers* of  $\rho$  containing quadruples (s, $\theta$ ,C, $\delta$ ) in which s is a state belongs to S,  $\theta$  and  $\delta$  are substitutions and C is a set of constraints (conjoined predicates) which is constructed inductively as follows:

- The initial forward matcher set is equal to  $U_0 = S \times \{\emptyset\} \times \{\emptyset\}$

- − If t=(s,s',a,z,P,A)∈ Tr is a transition in M, and U<sub>j-1</sub> contains a forward matcher quadruple (s,θ,C,δ) such that (a/z)δ is unifiable with (i/o), then U<sub>j</sub> contains quadruples (s',θ',C',δ') in which θ'= θ<sub>0</sub>mgu((a/z)δ, (i/o)), C'=C∪(P∧normalized (A))δ, and δ' is the normalizer of A.

Using the above definition we can describe our algorithm for checking the correctness of a given forward invariant on an EFSM and extracting its necessary constraints.

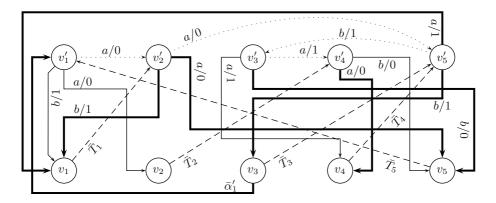

Let F(PIO, PI, TOS) be a forward invariant in which PIO is of size n. Suppose that  $U_n$  is the forward matcher set of PIO. If  $U_n$  is empty then the invariant is incorrect, else we check that for any transition labeled by the input PI, we receive an output unifiable with one of the items in the TOS. If there is no possible transitions, then the invariant is incorrect, else for each forward matcher quadruple  $(s,\theta,C,\delta)$  in  $U_n$ , if C is empty then the invariant is true, else the invariant is true constraint to C $\theta$ . The set of constraints C $\theta$  can be simplified using the existing constraint simplification algorithms. The algorithm is depicted more formally and detailed in figure 2.

The algorithm deals with invariants containing the wildcard character \*. Also we consider that both i=? and o=? hold. We have used some auxiliary functions: head(I) returns the first i/o couple of the sequence I and tail(I) removes the first i/o couple from I.

The Boolean function *path*(*s*, *s'*, *i*) returns true if there exist a path  $a_1/z_1, \ldots a_r/z_r$  from s to s' and for any  $1 \le j \le r$  we have  $a_j \ne i$ . Also the function *simplified*(*C*) returns the simplified version of the constraint set C. In fact this function solves the constraints such that the most constraining predicates on a single variable are remained. We don't enter in the details of this function. There are some well known methods to do this in the literature [12].

#### 4.2 Backward Invariant Constraints

To check a given backward invariant on an EFSM, first we have to find the set of transitions in the EFSM which have outputs unifiable with elements of the preamble output set in the invariant. After that, we should check whether the paths in the EFSM which are ended by the discussed outputs are unifiable with the test input and test I/O sequence in the invariant or not. And, if they are unifiable, what are the constraints on the variables of the invariant. The constraint set is in fact constructed during the unification of the test I/O sequence with the paths in the EFSM. We traverse the paths in the EFSM in a backward fashion to do the unification and extract the constraints.

**Definition 10.** Let  $\rho = i_1/o_1, \dots, i_n/o_n$  be an input sequence of size n and M=(S, I, O, x, Tr,  $s_{in}$ ) be an EFSM, we define  $V_0$  as the set of *backward matchers* of  $\rho$  containing quadruples ( $s, \theta, C, \delta$ ) in which s is a state belongs to S,  $\theta$  and  $\delta$  are substitutions and C is a set of constraints (conjoined predicates) which is constructed inductively as follows:

```

Input: M=(S, I, O, x, Tr, sin), I=F(PIO,PI,OTS)

Output: true/false or a set of constraints. Satisfaction of each constraint is sufficient to sat-

isfy the invariant.

Begin

/* PIO Matching: Finding the paths in the EFSM which are unifiable with the PIO */

I' := PIO; U := S \times \mathcal{O} \times \mathcal{O} \times \mathcal{O};

while I' \neq \varepsilon and U \neq \emptyset do begin

first = head(I'); I'=tail(I');

if first \neq * then begin /* first = i/o */

T:=Tr; U':= \emptyset;

while T \neq \emptyset do begin

choose t∈ T; /* t=(s,s',a,z,P,A) */

T:=T-\{t\};

if (s, \theta, C, \delta) \in U and unifiable((a/z)\delta, i/o) then begin

\theta' := \theta_0 mgu((a/z)\delta, i/o); C' := C \cup (P \land normalized(A))\delta;

\delta:=normalizer(A); \qquad U':=U'\cup\{(s',\theta',C',\delta')\};

end

end

U=U';

end

else begin /* first= * */

while head(I')=* do I':=tail(I');

first:= head(I'); /* first=i/o */

U := \{ (s, \theta, C, \delta) \mid s \in S, \exists (s, \theta, C, \delta) \in U, p = path(s', s, i) \};

end

end

/* TOS checking: Checking if TOS is reachable using the unified path or not and if so

what is its constraints*/

if U=Ø then return(false);

else begin

tf := false; T := Tr; CS := \emptyset;

while T \neq \emptyset do begin

choose t \in T; T := T - \{t\}; /* t = (s, s', a, z) */

if (s, \theta, C, \delta) \in U and unifiable(a\delta, i_n) then begin

\theta' := \theta_o mgu(a\delta, i_n);

if \mathbb{Z} o \in O \bullet (z\delta)\theta' = o\theta' then return(false);

tf:=true; CS:=CS \cup simplified(C \cup (P\land normalized(A))\delta);

end

end

end

if not tf then return false;

if CS = \emptyset then return true else return (CS);

End

```

Fig. 2. Algorithm for checking forward invariants and finding its corresponding constraints

- The initial backward matcher set is equal to  $V_n = S \times \{\emptyset\} \times \{\emptyset\}$

- \_ If t=(s, s', a, z, P, A)∈ Tr is a transition in M, and V<sub>j+1</sub> contains a backward matcher quadruple q=(s',θ,C,δ) such that (a/z)δ is unifiable with (i<sub>j</sub>/o<sub>j</sub>), then V<sub>j</sub> contains quadruples q'=(s,θ',C',δ') in which θ'= θ<sub>o</sub>mgu( (a/z)δ, (i<sub>j</sub>/o<sub>j</sub>)), δ' is the normalizer of A and C' = Cδ' ∪ (P ∧ normalized (A)). Delete the quadruple q from V<sub>j+1</sub>.

Input: M=(S, I, O, x, Tr, s<sub>in</sub>), I=B(TIO,TI,POS) Output: true/false or a set of constraints. Satisfaction of each constraint is sufficient to satisfy the invariant. Begin /\* POS Matching: Finding states in the EFSM which are unifiable with elements of the POS \*/  $T := Tr; V := S \times \{\mathcal{O}\} \times \{\mathcal{O}\} \times \{\mathcal{O}\}; error := false;$ while  $T \neq \emptyset$  and not *error* do begin choose  $t \in T$ ; /\* t=(s,s',a,z,P,A) \*/  $T:=T-\{t\};$ if  $\exists o \in POS \bullet unifiable((a/z)\delta, (TI/o))$  then begin  $\theta$ :=mgu(a/z, PI/o);  $\delta$ :=normalizer(A);  $C:=P \land normalized(A); \quad V:=V \cup \{(s, \theta, C, \delta)\};$ end else error :=true: end: if V=Ø then error :=true; /\* TIO matching: Checking if the TIO is matched with all paths ending to the states found in previous step or not and if so what is the constraint set \*/ I' := reverse(TIO);while not *empty*(*I*') and not *error* do begin  $V' := \emptyset;$  first :=head(I'); I':=tail(I'); if first  $\neq$  \* then begin /\* first = i/o \*/ T:=Tr;while  $T \neq \emptyset$  do begin choose  $t \in T$ ; /\* t=(s,s',a,z,P,A) \*/  $T:=T-\{t\}:$ if  $(s', \theta, C, \delta) \in V$  and  $unifiable((a/z)\delta, i/o)$  then begin  $\theta' := \theta_o mgu((a/z)\delta, (i/o)); \quad \delta' := normalizer(A);$  $C':=C\delta' \cup (P \land normalized(A)); \quad V':=V' \cup \{(s, \theta', C', \delta')\};$  $V=V-\{(s', \theta, C, \delta)\};$ end else error := True: end end else begin /\* first =\* \*/ while head(I') = \* do I' := tail'(I'); /\* skip a seq. of \*'s \*/ *first := head(I');* /\* first = i/o \*/  $V':=\{(s,\theta,C,\delta) \mid s \in S, \forall (s',\theta,C,\delta) \in V \bullet path(s, s', o)\};\$ end if  $V \neq \emptyset$  then error:= true else V:= V': end: if error then return (false);  $CS:=\emptyset$ : while  $V \neq \emptyset$  do begin **choose**  $v \in V$ ; /\* v=(s, $\theta$ ,C, $\delta$ ) \*/  $V:=V-\{v\}; \quad CS:=CS \cup simplify(C);$ end; if CS=Ø then return(true) else return(CS); End:

Fig. 3. Algorithm for checking backward invariants and finding its corresponding constraints

Using the above definition we can describe our algorithm for checking the correctness of a given backward invariant on an EFSM and extracting its necessary constraints. Let B(TIO, TI, POS) be a backward invariant. For all elements  $o_m \in POS$  ( $1 \le m \le POS|$  in which |POS| is the cardinality of POS) we concatenate the pair TI/ $o_m$  to the TIO to generate a set of input/output sequences like  $\rho_m = "TIO$ , TI/ $o_m$ ". Let the size of  $\rho_m$  be n. For each  $\rho_m$  ( $1 \le m \le |POS|$ ) we try to find its backward matcher set. If after constructing  $V_j$  ( $0 < j \le n$ ) in each iteration,  $V_j$  is empty or  $V_{j+1}$  is not empty, then the invariant is incorrect, else for each quadruple of the  $V_0$ , if C is empty, then the invariant is true without any condition, else the invariant is true constraint to simplified C $\theta$ . The algorithm is depicted more formally and detailed in figure 3. Auxiliary functions used are the same as described for the forward invariant checking algorithm.

#### 5 An Example: SCP Protocol

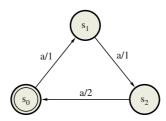

In this section we present the processing of the method we discussed in this paper for passively testing an implementation of the Simple Connection Protocol (SCP) to show the applicability of the method. SCP has the advantage of including most difficulties of passive testing in a protocol specification, and then is able to figure out the applicability of the algorithm on bigger protocols.

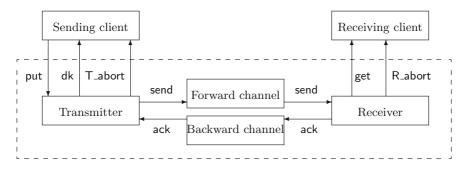

#### 5.1 The Simple Connection Protocol

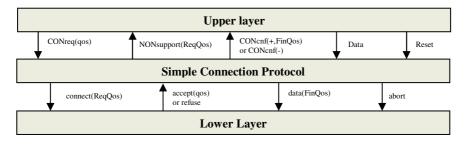

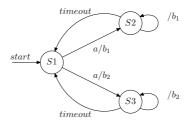

SCP allows us to connect an entity called upper layer to an entity called lower layer. The upper layer performs a dialogue with SCP to fix the quality of service desirable for the future connection. Once the negotiation is finished, SCP dialogues with the lower layer to ask for the establishment of a connection satisfying the previously negotiated quality of service. The lower layer accepts or refuses this connection request. If it accepts the connection, SCP informs the upper layer that connection was established and the upper layer can start to transit data towards the lower layer via SCP.

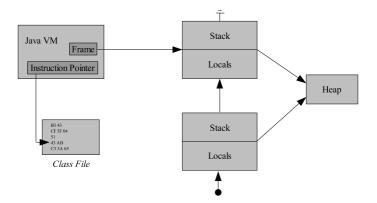

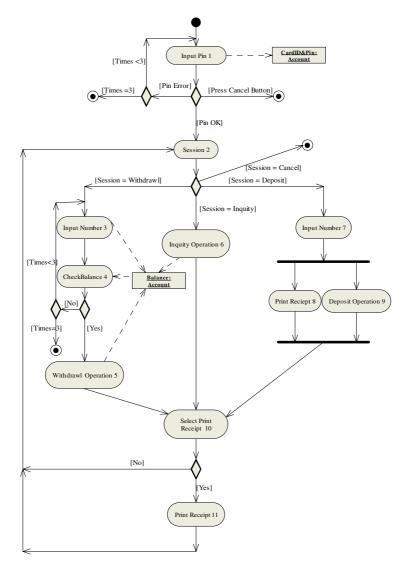

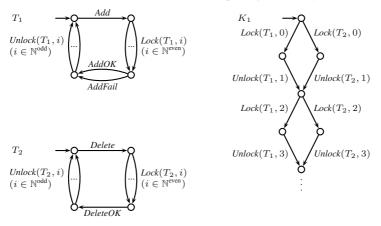

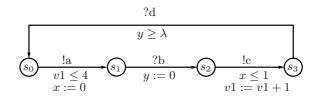

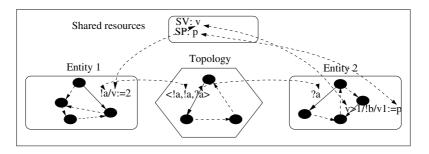

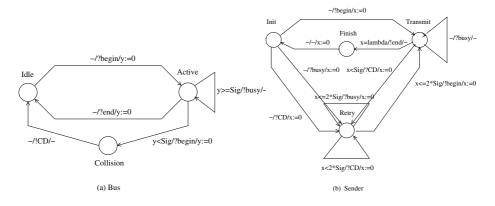

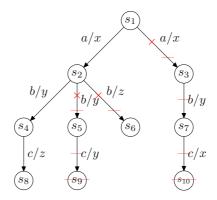

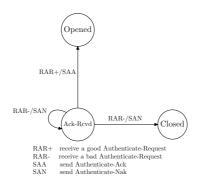

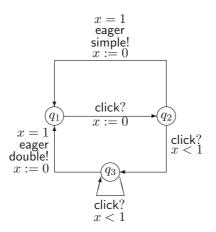

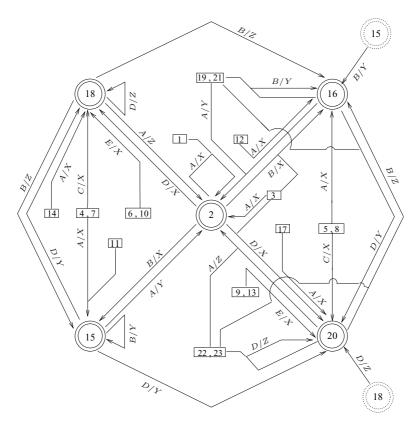

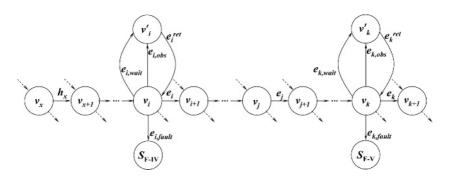

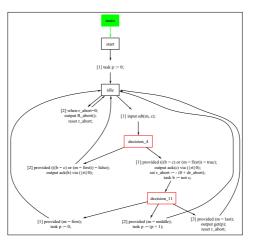

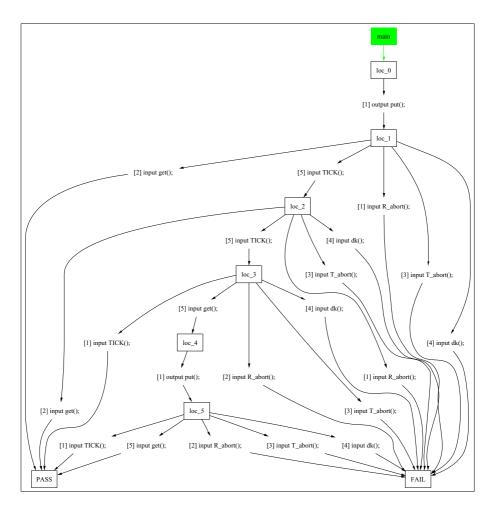

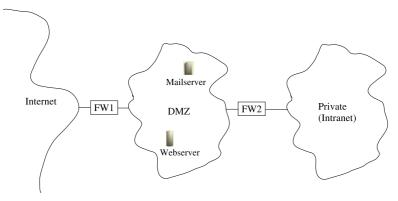

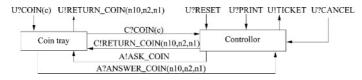

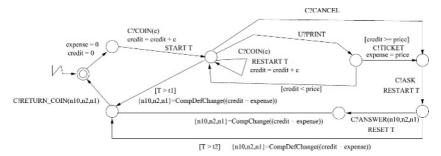

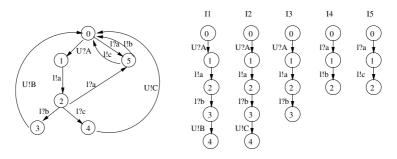

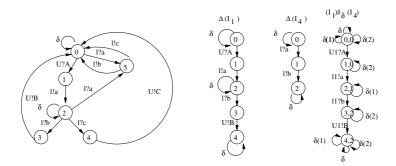

Once the transmission of the data finished, the upper layer sends a message to close the connection. On the other hand, if the lower layer refuses the connection, the system allows SCP to make three requests before informing the upper layer that the connection attempts all failed. If the upper layer wishes again to be connected to the lower layer, it is necessary to restart the QoS negotiation with SCP from beginning. Figure 4 shows the interactions of the SCP with its upper and lower layers.

#### 5.2 Defining Invariants

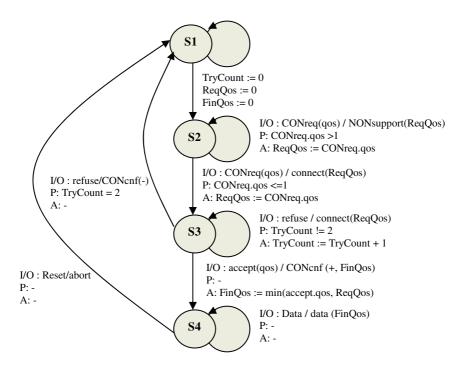

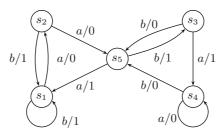

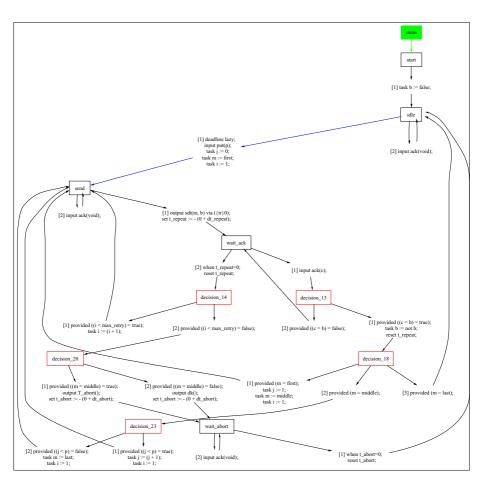

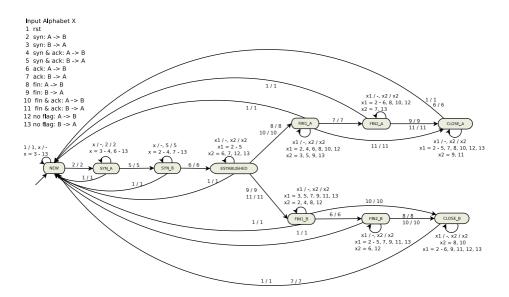

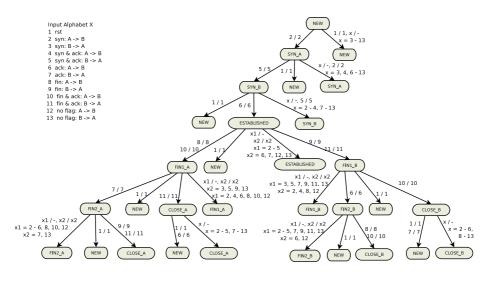

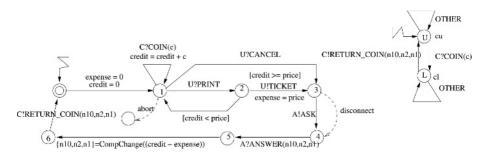

Let consider the EFSM specification of the Simple Connection Protocol depicted in figure 5. We suppose that the values of TryCount, ReqQos, FinQos, CONreq.qos, and accept.qos are defined in the interval [0;3]. Suppose that we want to passively test an implementation of the SCP regarding the following properties of the specification which are described using the invariants:

- I<sub>1</sub> = B ( < refuse/connect(x) > , ( refuse ) , { CONcnf(-) } ), means that SCP fail to connect the two layers (CONcnf(-)) only if the lower layer refused the connection twice before (refuse/connect(x), refuse/ ).

- I<sub>2</sub> = F ( < CONreq(x)/connect(y) > , (accept(w)) , { CONcnf(+,z) } ) , means that if SCP accepts to connect with the upper layer at his requested QoS (CON-

req(x)/connect(y) and the lower layer accept it at a given QoS, then a connection must be realized between the two layers.

- I<sub>3</sub> = F ( >, ( accept(x) ), { CONcnf(+,y) } ), means that if the lower layer accept the connection (accept(x)), this connection must be realized (CONcnf(+,y)).

- I<sub>4</sub> = B ( <> , ( accept(x) ) , { CONcnf(+,y) } ) , means that a connection is realized (CONcnf(+,x)), only if the lower layer accepted it before (accept(y)).

Note that  $I_1$  and  $I_4$  are forward invariants while  $I_2$  and  $I_3$  are backward invariants. In definition of the above invariants we have used a control driven approach i.e. in this stage, parameters of the signals are not important so we have used some variables instead of them.

Fig. 4. Interactions of the SCP with its upper and lower layers

#### 5.3 Finding Invariant Constraints

Now, we apply our method on the invariants to find their corresponding constraints. Table 1 shows the trace of the algorithms. For each forward (backward) invariant, the value of the intermediate forward (backward) matcher set i.e. U (i.e. V) and the ultimate constraint sets CS over the variables of the invariants have been shown. (See the algorithms in figures 2 and 3).

Applying the algorithms reveal that all the invariants are correct regarding the control part of the specification, but regarding the data part of the specification the invariants are true condition to some constraints which have been produced by the algorithms. For invariant  $I_1$ , there is no constraint over the variable of the invariant, so it should be matched by execution traces with any value for the variable x. For the other invariants, only such execution traces are matched with the invariants that the value of their input/output parameters does not cause any conflict with the corresponding constraints of the invariant.

#### 5.4 Passive Testing Using the Constrained Invariants

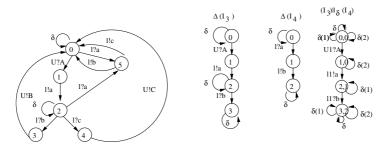

Now suppose that the following execution traces are generated by a faulty implementation of the SCP:

- Trace<sub>1</sub> = CONreq(1) / connect(1) , refuse / CONcnf(-)

- Trace<sub>2</sub> = CONreq(1) / connect(0) , accept(1) / CONcnf(+, 0).

Fig. 5. EFSM specification of SCP

We know that a transition error has occurred in the first trace because the specification forces two loops on state  $s_3$  before eventual transition to  $s_1$ , corresponding to the three requests SCP must do before failing the connection. In this trace, the connection is said to be failed on first try. For the second trace, there is an output error because the first I/O couple should be CONreq(1)/connect(1). We can imagine that the trace comes from an implementation in which the action on the transition from  $s_2$  to  $s_3$  is ReqQos:=CONreq.qos -1 and then such a trace is produced. This error has for consequence to connect the upper and lower layers with a QoS equals to 0 when it could be (normally) equal to 1.

Tables 2 and 3 show the invariants used in the checking of the first and the second trace respectively. We try to identify the constraints with the values of the variables extracted from the traces:

- **Trace<sub>1</sub>:** Since the analysis found CONcnf(-) in the trace and failed looking for the couple refuse/connect(x), then the trace is erroneous regarding the invariant I<sub>1</sub>. Note that the found error is control driven, so it is not needed to look at the constraints at all.

- **Trace<sub>2</sub>:** There are three invariants which are candidate for this trace. Matching the trace with the invariants shows that there is not any control driven error, so we use constraints and the value of the variables in the trace to decide about the possibility of data driven errors:

| Invariant                         | U <sub>1</sub> (or V <sub>1</sub> )                                                                                                                                                                                                                                                                  | U <sub>2</sub> (orV <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                         | Constraint set<br>(CS)                                               |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| I <sub>1</sub><br>(Back-<br>ward) | $ \begin{array}{l} V_1 = \{ \ (s_3, \theta_1, C_1, \delta_1 \ ) \ \} \\ \theta_1 = \varnothing \\ C_1 = \{ \ TryCount = 2 \ \} \\ \delta_1 = \varnothing \end{array} $                                                                                                                               | $V_2 = \{ (s_3, \theta_2, C_2, \delta_2) \}$<br>$\theta_2 = \{ \text{ReqQos/x} \}$<br>$\delta_2 = \{ \text{TryCount/y} \}$<br>$C_2=C_1\delta_2 \cup$<br>$\{ \text{TryCount!=2,y=TryCount+1} \}$<br>$= \{ \text{TryCount!=2} \}$                                                                                                                                            | $\begin{array}{l} CS\_I_1=C_2\theta_2=\\ \{TryCount=2\} \end{array}$ |

| I2<br>(For-<br>ward)              | $ \begin{array}{l} U_1 = \left\{ \begin{array}{l} (s_3, \theta_1, C_1, \delta_1 ) \right\} \\ \theta_1 = \left\{ \begin{array}{l} CONreq.qos/x, ReqQos/y \right\} \\ C_1 = \left\{ \begin{array}{l} CONreq.qos <= 1, \\ ReqQos = CONreq.qos \right\} \\ \delta_1 = \varnothing \end{array} \right. $ | $\begin{array}{l} U_2 = \{ (s_4, \theta_2, C_2, \delta_2) \} \\ \theta_2 = \theta_1 o \{ accept.qos/w, FinQos/z \} \\ = \{ CONreq.qos/x, ReqQos/y, accept.qos/w, FinQos/z \} \\ C_2 = C_1 \cup \{ CONreq.qos = min(accept.qos, ReqQos) \} \\ \delta_1 \\ = \{ CONreq.qos <= 1, ReqQos = CONreq.qos, FinQos=min(accept.qos, ReqQos) \} \\ \delta_2 = \emptyset \end{array}$ | CS_12=C202=<br>{x<=1, y=x,<br>z=min(w, y)}                           |

| I <sub>3</sub><br>(For-<br>ward)  | $\begin{array}{l} U_1 = \{ (s_3, \theta_1, C_1, \delta_1) \} \\ \theta_1 = \{ accept.qos/x, FinQos/y \} \\ C_1 = \{ y=min(x, ReqQos) \} \\ \delta_1 = \varnothing \end{array}$                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                            | $CS_{I_3}=C_1\theta_1=$<br>{y=min(x,<br>ReqQos)}                     |

| I4<br>(Back-<br>ward)             | $ \begin{array}{l} V_1 = \{ (s_4, \theta_1, C_1, \delta_1) \} \\ \theta_1 = \{ accept.qos/x, FinQos/y \} \\ C_1 = \{ y=min(x, ReqQos) \} \\ \delta_1 = \varnothing \end{array} $                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                            | $CS_{I_4=C_1\theta_1=} \\ \{y=min(x, ReqQos)\}$                      |

Table 1. Using algorithms to extract required constraints for the example invariants

$\begin{aligned} &CS-I_2 \cup \{x=1, \ y=0, \ w=1, \ z=0\} = \{x<=1, \ y=x, \ z=min(w, \ y)\} \cup \{x=1, \ y=0, \ w=1, \ z=0 \} \\ &= \{1=<1, \ 0=1, \ 0=min(1, \ 0) \} \end{aligned}$

1=<1 is true, 0=1 is false and 0=min(1, 0) is true, so the invariant  $I_2$  is false on Trace<sub>2</sub>. CS-I<sub>3</sub>  $\cup$  {x=1, y=0}={y=min(x, ReqQos)} $\cup$ {x=1, y=0} = { 0=min(1, ReqQos) } 0 is the minimum of 1 and ReqQos only if ReqQos is equal to 0, so the invariant  $I_3$

is true on the trace  $Trace_2$  if ReqQos=0.

CS-I<sub>4</sub>  $\cup$  {x=1, y=0}={y=min(x, ReqQos)}  $\cup$  { x=1, y=0 } = { 0=min(1, ReqQos) } 0 is the minimum of 1 and ReqQos only if ReqQos is equal to 0 so the invariant I<sub>4</sub> is true on the trace Trace<sub>2</sub> if ReqQos=0.

As we found an inconsistency in the checking of the invariant  $I_2$  with the trace Trace<sub>2</sub> we conclude that the trace  $T_2$  is false. Checking the other invariants on the trace is not necessary but figure here as an example of variable simplification.

Table 2. Using invariant  $I_1$  to check the execution trace Trace<sub>1</sub>

| Trace <sub>1</sub> | CONreq(1) | connect(1) | Refuse | CONcnf(-) |

|--------------------|-----------|------------|--------|-----------|

| I <sub>1</sub>     | Refuse    | connect(x) | Refuse | CONcnf(-) |

| Trace <sub>2</sub> | CONreq(1) | connect(0) | Accept(1) | CONcnf(+,0) |

|--------------------|-----------|------------|-----------|-------------|

| I <sub>2</sub>     | CONreq(x) | connect(y) | Accept(w) | CONcnf(+,z) |

| I <sub>3</sub>     |           |            | Accept(x) | CONcnf(+,y) |

| $I_4$              |           |            | Accept(x) | CONcnf(+,y) |

Table 3. Using invariants  $I_2$ ,  $I_3$  and  $I_4$  to check the execution trace Trace<sub>2</sub>

#### 6 Conclusion

Passive testing methods for network protocols can be classified into naïve and invariant based approaches. In the naïve approach the implementation trace which is recorded during the execution of the protocol under test is compared with total of the specification in a forward or backward manner. This is where, in the invariant based approach only critical properties of the specification (i.e. invariants) which are extracted by an expert are compared with the implementation trace. By using invariant based approach, not only a lot of extra processing is reduced, but also we can focus on the critical properties of the program under test.

Passive testing methods can be compared from another aspect. Some methods are limited to testing only control driven aspects of the implementation, i.e. the order of occurrences of the input/output signals, while other methods are capable of testing both control driven and data driven aspects of the implementation i.e. the values of the signal's parameters. For testing control driven aspects it is sufficient to use FSM for specification, while for data driven aspects it is needed to use EFSM.

In this paper we presented a new method for passive testing of both control driven and data driven aspects of the network protocols using an invariant based approach. The intended properties of the specification are expressed using some control driven invariants given by an expert. After that, using the given algorithms, the invariants are checked on the specification off-line. Also to take the data driven aspects into account, for the correct invariants, some constraints over the variables of the invariants are extracted. For passively testing the implementation traces, it is sufficient to compare, on-line, the trace with the invariants regarding the constraints using pattern matching. A trace is correct while it is matched with the invariant and the invariant's constraints are not conflicting regarding the values of the signal's parameters.

To show the applicability of the presented method, passive testing of the Simple Connection Protocol (SCP) using the presented method was illustrated.

#### References

- 1. R. Lai, "A survey of communication protocol testing", Journal of Systems and Software 62(1): 21-46 (2002).

- 2. D. Lee, and M. Yannakakis, "Principles and methods of testing finite state machines---A survey", Proc. IEEE 84, 8, (1996), 1089--1123.

- D. Lee, A. N. Netravali, K. Sabnani, B. Sugla, A. John, "Passive testing and applications to network management", IEEE International Conference on Network protocols, ICNP'97, pages 113-122. IEEE Computer Society Press, 1997

- 4. R. E. Miller and K. A. Arisha, "On Fault Location in Networks by Passive Testing", IPCCC 2000, Pheonix, AZ, Feb. 2000.

- M. Tabourier and A. Cavalli, "Passive Testing and application to the GSM-MAP Protocol", in Journal of Information and Software Technology 41(11) (15 Sept. 1999), Pages 813-821, Elsevier, 1999.

- J. A. Arnedo, A. Cavalli and M. Nunez, "Fast Testing of Critical Properties through Passive Testing", LNCS, vol. 2644/2003, Pages 295-310, Springer, 2003.

- A. Cavalli, C. Gervy and S. Prokopenko, "New Approaches for Passive Testing Using an Extended Finite State Machine Specification", in Journal of Information and Software Technology, 45:837-852, Elsevier, 2003.

- 8. D. Lee, D. Chen, R. Hao, R. E. Miller, J. Wu, and X. Yin, "A Formal Approach for Passive Testing of Protocol Data Portions", Proc. ICNP'2002.

- B. Alcalde, A. Cavalli, D. Khuu, D. Chen, D. Lee, "Network Protocol System Passive Testing for Fault Management - a Backward Checking Approach", in the Proceedings of the 24th IFIP WG 6.1, International Conference on Formal Techniques for Networked and Distributed Systems, FORTE 2004, 27-30 September, 2004, Madrid, Spain.

- 10. F. Baader, W. Snyder, "Unification Theory, Handbook of Automated Reasoning", Alan Robinson, Andrei Voronkov, eds., Vol. 1, Chapter 8, 446–533.

- 11. E.Bayse, A. Cavalli, M. Nunez and F. Zaidi, "A Passive Testing Approach based on Invariants: Application to the WAP", To be published in journal of Computer Network, 2004.

- 12. K. Marriott and P. J. Stuckey, "Programming with Constraints: An Introduction", Book, The MIT Press, 1998.

# Dependence Testing: Extending Data Flow Testing with Control Dependence

Hyoung Seok  $\mathrm{Hong}^1$  and  $\mathrm{Hasan}\ \mathrm{Ural}^2$

<sup>1</sup> Concordia Institute for Information Systems Engineering, Concordia University hshong@ciise.concordia.ca

<sup>2</sup> School of Information Technology and Engineering, University of Ottawa ural@site.uottawa.ca

Abstract. This paper presents a new approach to structural testing, called dependence testing. First we propose dependence oriented coverage criteria that extend conventional data flow oriented coverage criteria with control dependence. This allows one to capture the full dependence information of a program or specification systematically. We then describe a model checking-based approach to test generation for dependence testing. It is shown that dependence oriented coverage criteria can be characterized in the temporal logics LTL and CTL. This enables one to use any LTL and CTL model checkers as test generators. Finally, we show that the temporal logic-based characterization can also be used for reducing the cost of dependence testing.

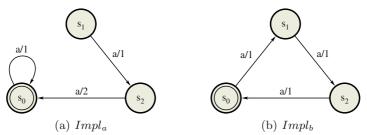

#### 1 Introduction