Kaihui Tu · Xifan Tang · Cunxi Yu · Lana Josipović · Zhufei Chu

# FPGA EDA

# **Design Principles and Implementation**

# FPGA EDA

Kaihui Tu · Xifan Tang · Cunxi Yu · Lana Josipović · Zhufei Chu

# FPGA EDA

**Design Principles and Implementation**

Kaihui Tu Beijing, China

Cunxi Yu University of Maryland, College Park College Park, MD, USA

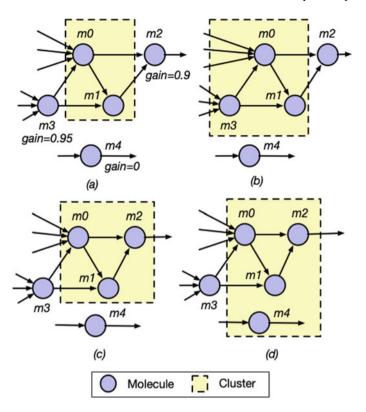

Zhufei Chu Ningbo University Ningbo, China Xifan Tang Los Gatos, CA, USA

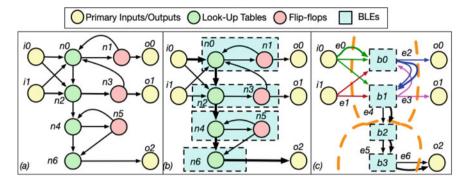

Lana Josipović ETH Zürich Zürich, Switzerland

ISBN 978-981-99-7754-3 ISBN 978-981-99-7755-0 (eBook) https://doi.org/10.1007/978-981-99-7755-0

© The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2024

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

Paper in this product is recyclable.

## Foreword

As the need for highly efficient systems has grown and the performance gains from Moore's Law have diminished, hardware acceleration has become ever more important. At the same time, chip design costs are skyrocketing, and application needs are rapidly changing, putting a completely custom silicon system out of reach for most applications. The unique, low-level hardware programmability of field-programmable gate arrays (FPGAs) has therefore become a key part of many systems, as a single chip can be programmed to enable a hardware solution for multiple applications.

To architect, implement, and program FPGAs requires sophisticated electronic design automation (EDA) tools, however, and indeed the greatest challenge of implementing a new FPGA architecture and making it usable has historically been the creation of these EDA tools. This book fills a crucial gap, as it covers all aspects of FPGA EDA tools. Some of these tools are similar to their custom (application-specific integrated circuit, or ASIC) cousins, but others are uniquely specialized to the implementation or targeting of FPGAs, and this book provides both the general overview and FPGA-specific discussion needed to fully understand FPGA EDA.

This work takes a holistic approach to FPGA EDA that is timely and important. Uniquely, it covers three sub-areas of FPGA EDA that together enable not only designing to and programming an FPGA, but also architecting a new FPGA and automating much of the implementation of its circuitry and layout. The first portion of this book explains the EDA tools needed describe a new FPGA architecture and evaluate its quality—crucial steps in making sure a new FPGA is usable and performant. Next it summarizes and compares a novel class of EDA tools that has emerged to rapidly implement the circuitry and layout of a new FPGA architecture, verify its correctness, and model its low-level characteristics. The higher implementation productivity enabled by these new tools is fueling wider adoption of embedded FPGA blocks within system-on-chip (SoC) designs and the development of application-tuned standalone FPGAs. Finally, this work details the full design and programming flow needed by end users of an FPGA, from high-level synthesis, through logic synthesis, physical implementation, and bitstream generation. This book is a key reference not only for FPGA end users and EDA developers but also FPGA architects. Its coverage of both current industrial practice and emerging approaches makes it relevant to both FPGA practitioners and researchers. As FPGA designs become more complex, FPGA architectures proliferate, and embedded FPGAs find their way into more SoCs, knowledge of the full spectrum of FPGA EDA tools will be crucial to system architects and this book will be one of their key resources.

Toronto, Canada August 2023 Vaughn Betz

### Preface

The electronic design automation (EDA) for field programmable gate array (FPGA) is a special interdisciplinary study area. EDA software runs throughout the entire life cycle of FPGA design, including chip design stage and application design stage. With the ever-increasing demand for customized and application-specific electronic systems, FPGAs have become a popular choice for implementing complex digital designs and FPGA EDA is the key to make that happen.

This book aims to provide a comprehensive and up-to-date principles and implementations of FPGA EDA technology, absorbing nutrients from both industry and academia. It is written for students, researchers, and practicing engineers who are interested in understanding the design and optimization of FPGA EDA system.

The book begins with an introduction to two fundamental concept: FPGA and EDA. It then covers the databases and methodologies across the whole design flow: at chip design stage, EDA tools help chip design engineers to explore the FPGA architecture and complete their intricate masterpiece, while at application design stage, EDA tools help application design engineers to etch their brilliant thoughts into circuits.

Writing a book is a challenging and rewarding experience. When writing this book, we realized the vastness of the FPGA EDA field and the complexity of this topic. We tried to make the book as accessible as possible by explaining the concepts in a simple and intuitive way. However, there is always room for improvement, and we welcome any feedback or suggestions from the readers.

Writing a book is definitely not a solitary endeavor, authors are from across Asia, Europe, and North America, and all of them have invested their huge amount of time and effort to finish this course. Meanwhile, I am thankful to the people who have provided their precious assistance and support throughout the writing process: Dr. Lijiang Gao, Dr. Borui Cai, Prof. Rui Zhang, Dr. Grace Zgheib, Dr. Colin Yu Lin, Dr. Zhihong Huang, Dr. Yi Shu, Dr. Tianwen Li, Dr. Yuanming Zhu, Dr. Junying Huang, Yu Bao, Dong Zhang, Jian Han, Larisa Li, Yuan Li... We also would like to acknowledge the numerous researchers, scholars, and professionals whose work we have drawn upon in this book. Their contributions have been invaluable in shaping our ideas and perspectives. Finally, I am grateful to the readers of this book, whose interest and support have made this project worthwhile. I hope that this book will prove to be a valuable resource for our audience and inspire them to further explore the fascinating world of FPGA EDA technology.

Beijing, China April 2023 Kaihui "Kelvin" Tu

# Contents

#### Part I Introduction

| 1 | Introduction |          |                                        |    |  |

|---|--------------|----------|----------------------------------------|----|--|

|   | 1.1          | FPGA     | Hardware Brief Introduction            | 3  |  |

|   |              | 1.1.1    | FPGA Concept                           | 3  |  |

|   |              |          | FPGA Hardware Evolution                |    |  |

|   |              | 1.1.3    | FPGA Compares With Other Architectures | 13 |  |

|   | 1.2          |          | EDA Brief Introduction                 |    |  |

|   |              | 1.2.1    | FPGA EDA Concept                       | 15 |  |

|   |              |          | FPGA Chip Design EDA                   |    |  |

|   |              |          | FPGA Application Design EDA            |    |  |

|   | Refe         | rences . | ·····                                  | 21 |  |

#### Part II FPGA Data Modeling

| 2 | Devic | e (Chip | Design) Modeling                  | 25 |

|---|-------|---------|-----------------------------------|----|

|   | 2.1   | Device  | Description Levels                | 25 |

|   |       | 2.1.1   | Abstract Levels                   | 25 |

|   |       | 2.1.2   | Reuse Levels                      | 28 |

|   | 2.2   | Device  | Model Classifications             | 28 |

|   |       | 2.2.1   | Primary Class                     | 29 |

|   |       | 2.2.2   | Metric Class                      | 32 |

|   |       | 2.2.3   | Guidance Class                    | 37 |

|   | 2.3   | Device  | Model Implementations             | 38 |

|   |       | 2.3.1   | Logic Resource Structure Model    | 38 |

|   |       | 2.3.2   | Configuration Bit Structure Model | 40 |

|   |       | 2.3.3   | Power Model                       | 41 |

|   |       | 2.3.4   | Performance (Timing) Model        | 42 |

|   |       | 2.3.5   | Area Model                        | 44 |

|   |       | 2.3.6   | Packing/Placement Guidance Model  | 44 |

82

|     |        | 2.3.7    | Routing Guidance Model              | 45 |

|-----|--------|----------|-------------------------------------|----|

|     |        | 2.3.8    | Bitstream Generation Guidance Model | 45 |

|     | Refere | ences    |                                     | 46 |

| 3   | Desig  | n (Appli | ication Design) Modeling            | 49 |

|     | 3.1    |          | Description Levels                  | 49 |

|     |        | 3.1.1    | Abstract Levels                     | 49 |

|     |        | 3.1.2    | Reuse Levels                        | 52 |

|     | 3.2    | Design   | Model Classifications               | 52 |

|     |        | 3.2.1    | Primary Class                       | 52 |

|     |        | 3.2.2    | Constraint Class                    | 54 |

|     |        | 3.2.3    | Report Class                        | 55 |

|     | 3.3    | Design   | Model Implementations               | 56 |

|     |        | 3.3.1    | Logic Resource Structure Model      | 56 |

|     |        | 3.3.2    | Configuration Bit Structure Model   | 58 |

|     |        | 3.3.3    | Constraint Model                    | 58 |

|     |        | 3.3.4    | Report Model                        | 59 |

|     | Refere | ences    | *                                   | 60 |

| Par | t III  | FPGA N   | Aetric Analysis                     |    |

| 4   | Power  | r Analys | sis                                 | 65 |

|     | 4.1    |          | ew                                  | 65 |

|     | 4.2    |          | Analysis Techniques                 | 68 |

|     | 4.3    |          | ry and Trends                       | 70 |

|     | Refere |          |                                     | 70 |

| _   |        |          |                                     |    |

| 5 | Performance (Timing) Analysis |                            |  |  |  |  |  |  |

|---|-------------------------------|----------------------------|--|--|--|--|--|--|

|   | 5.1                           | Overview                   |  |  |  |  |  |  |

|   | 5.2                           | Timing Analysis Techniques |  |  |  |  |  |  |

|   | 5.3                           | Summary and Trends         |  |  |  |  |  |  |

|   | Refe                          | rences                     |  |  |  |  |  |  |

| 6 | Area                          | Analysis                   |  |  |  |  |  |  |

|   | 6.1                           | Overview                   |  |  |  |  |  |  |

|   | 6.2                           | Area Analysis Techniques   |  |  |  |  |  |  |

|   | 6.3                           | Summary and Trends         |  |  |  |  |  |  |

References .....

#### Part IV FPGA Chip Design EDA

| 7 | Semi | i-custom | EDA                                  | 85         |

|---|------|----------|--------------------------------------|------------|

|   | 7.1  | Overvi   | ew                                   | 85         |

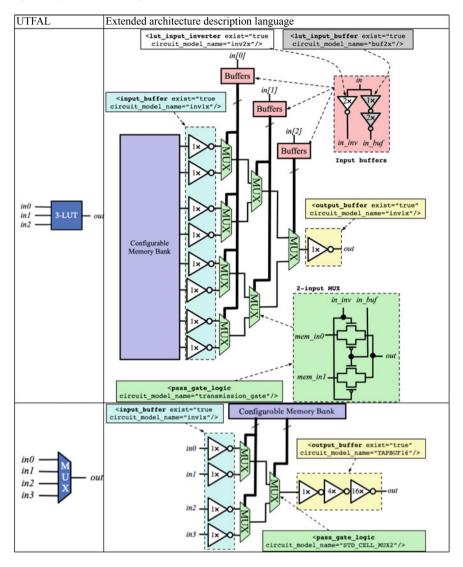

|   | 7.2  | Extend   | ed Architecture Description Language | 88         |

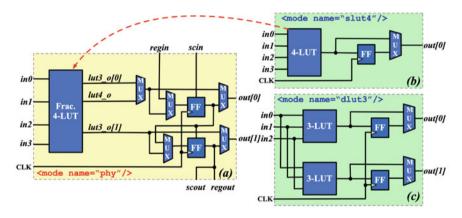

|   |      | 7.2.1    | Circuit Modeling                     | 89         |

|   |      | 7.2.2    | Physical Mode Modeling               | <b>9</b> 1 |

|   |      | 7.2.3    | Configuration Protocol               | 94         |

#### Contents

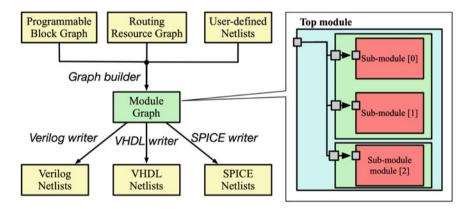

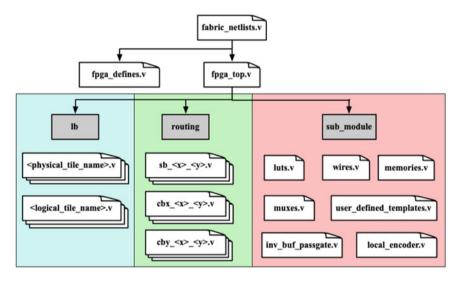

| 7.3   | Netlist Generator     |                        |     |  |  |  |

|-------|-----------------------|------------------------|-----|--|--|--|

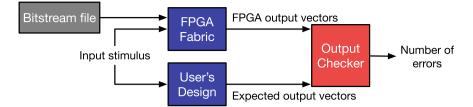

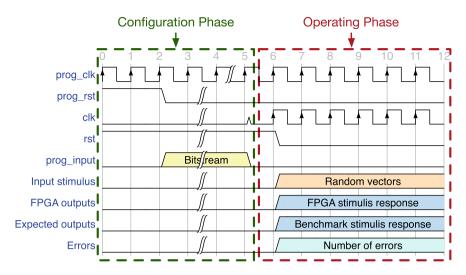

| 7.4   | Testbench Generator 1 |                        |     |  |  |  |

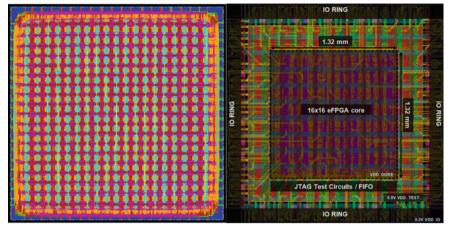

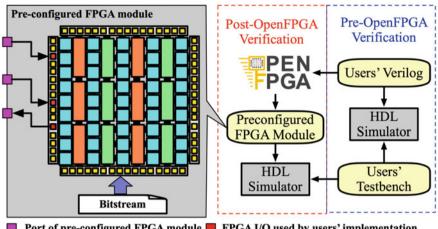

| 7.5   | Showcase 10           |                        |     |  |  |  |

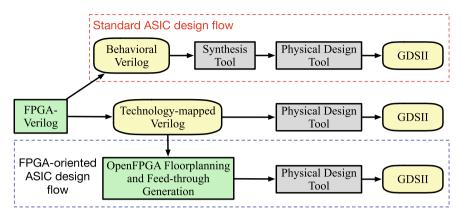

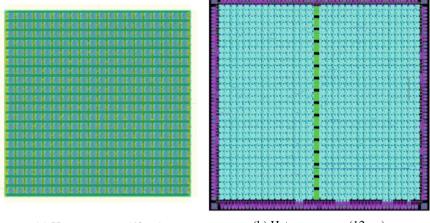

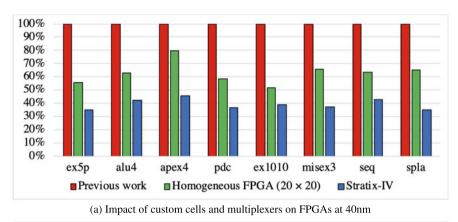

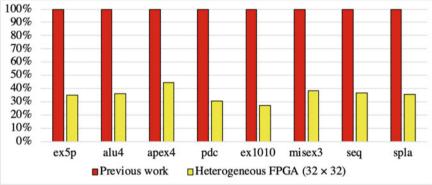

|       | 7.5.1                 | Methodologies          | 104 |  |  |  |

|       | 7.5.2                 | Performance Evaluation | 104 |  |  |  |

| 7.6   | Summary and Trends 1  |                        |     |  |  |  |

| Refer | ences .               |                        | 107 |  |  |  |

#### Part V FPGA Application Design EDA

| 8 | High-Level Synthesis           |          |                                              |     |  |  |

|---|--------------------------------|----------|----------------------------------------------|-----|--|--|

|   | 8.1                            | Overv    | iew                                          | 113 |  |  |

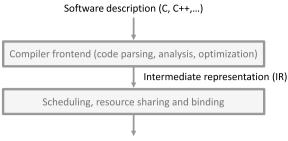

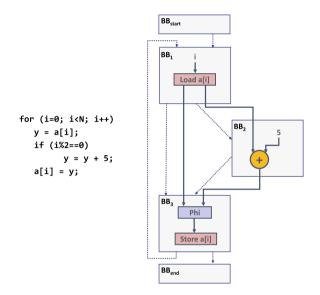

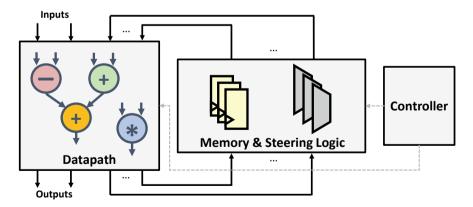

|   |                                | 8.1.1    | From Software Program to Intermediate        |     |  |  |

|   |                                |          | Representation                               | 113 |  |  |

|   |                                | 8.1.2    | From Intermediate Representation to Hardware |     |  |  |

|   |                                |          | Design                                       | 115 |  |  |

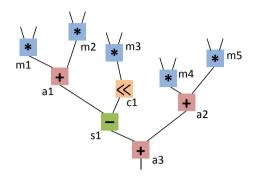

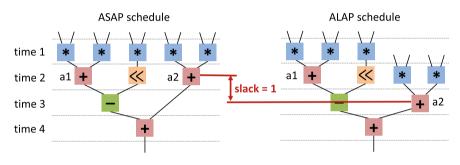

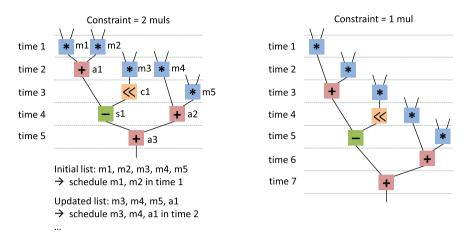

|   | 8.2                            | Datapa   | ath Scheduling                               | 116 |  |  |

|   |                                | 8.2.1    | Unconstrained Scheduling                     | 116 |  |  |

|   |                                | 8.2.2    | Constrained Scheduling                       | 118 |  |  |

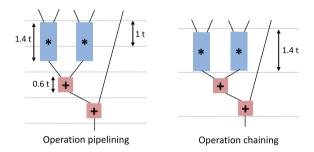

|   |                                | 8.2.3    | Timing Optimizations                         | 119 |  |  |

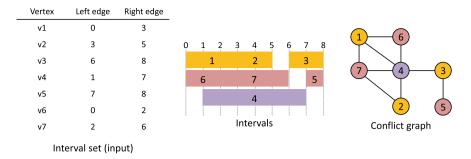

|   |                                | 8.2.4    | Resource Binding and Sharing                 | 120 |  |  |

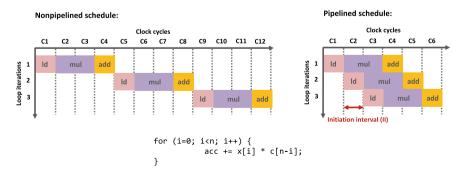

|   | 8.3                            | Extrac   | ting Parallelism Through HLS Scheduling      | 121 |  |  |

|   |                                | 8.3.1    | SDC-Based Modulo Scheduling                  | 121 |  |  |

|   |                                | 8.3.2    | Polyhedral Analysis and Optimization         | 122 |  |  |

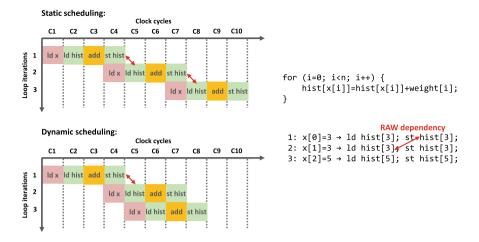

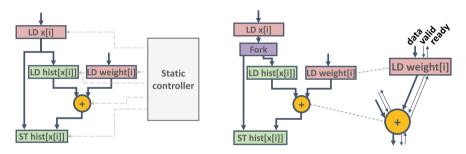

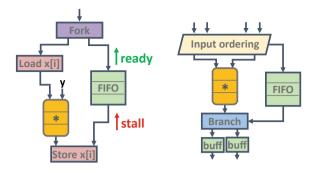

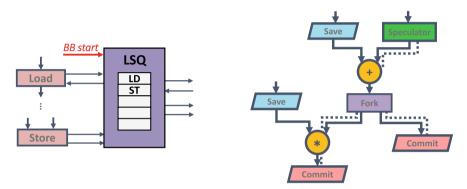

|   |                                | 8.3.3    | Dynamic Scheduling                           | 123 |  |  |

|   | 8.4 Current Status and Outlook |          |                                              | 127 |  |  |

|   |                                | 8.4.1    | HLS Frameworks                               | 127 |  |  |

|   |                                | 8.4.2    | HLS Code Restructuring and Annotations       | 128 |  |  |

|   |                                | 8.4.3    | Design Space Exploration                     | 129 |  |  |

|   |                                | 8.4.4    | Functional and Formal Verification in HLS    | 130 |  |  |

|   |                                | 8.4.5    | Frequency Estimates in HLS                   | 130 |  |  |

|   | Refe                           | rences . | ·····                                        | 131 |  |  |

| 9 | Logi                           | o Synth  | esis                                         | 135 |  |  |

| 1 | 9.1                            | •        | iew                                          | 135 |  |  |

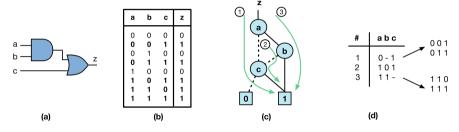

|   | 9.2                            |          | mentals of Boolean Logic                     | 135 |  |  |

|   | 1.2                            | 9.2.1    | Boolean Algebra                              | 136 |  |  |

|   |                                | 9.2.1    | Functional Representation                    | 130 |  |  |

|   |                                | 9.2.2    | Directed-Acyclic-Graph (DAGs) Boolean        | 157 |  |  |

|   |                                | 1.2.5    | Network                                      | 139 |  |  |

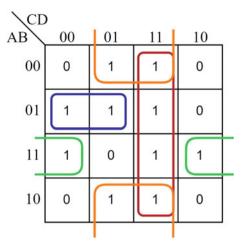

|   | 9.3                            | Logic    | Optimization                                 | 141 |  |  |

|   | 9.5                            | 9.3.1    | Functional Methodologies                     | 141 |  |  |

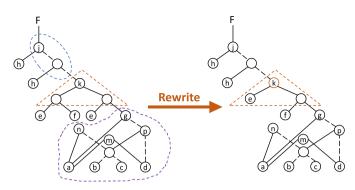

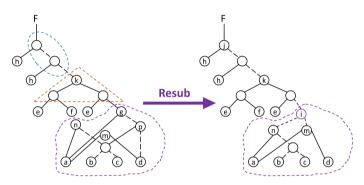

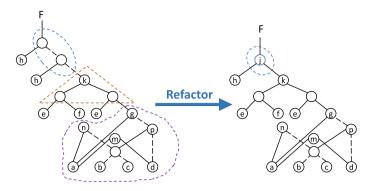

|   |                                | 9.3.2    | DAG-Aware Logic Optimization                 | 142 |  |  |

|   |                                | 9.3.2    | Exact Logic Optimization                     | 142 |  |  |

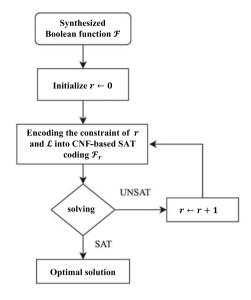

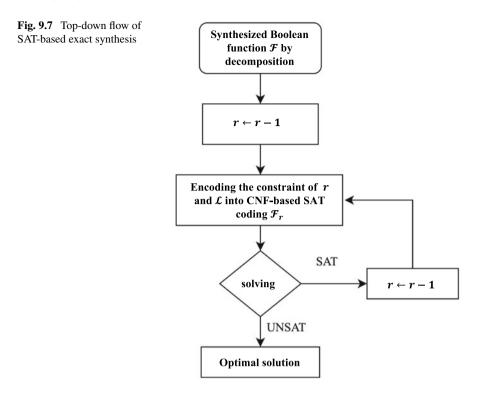

|   |                                | 9.3.3    | Exact Synthesis Algorithm Flow               | 144 |  |  |

|   |                                | 9.3.4    | SAT-Based Encoding                           | 145 |  |  |

|   |                                | 7.5.5    | SAI-Dascu Elicounig                          | 140 |  |  |

|    |       | 9.3.6              | Sequential Logic Optimization          | 149        |

|----|-------|--------------------|----------------------------------------|------------|

|    |       | 9.3.7              | Advanced Logic Optimization Techniques | 154        |

|    | 9.4   | Techno             | logy Mapping                           | 155        |

|    |       | 9.4.1              | Flow-Based and Cut-Based LUT Mapping   | 156        |

|    |       | 9.4.2              | Cut-Less LUT Mapping                   | 156        |

|    | 9.5   | AI in L            | ogic Synthesis                         | 157        |

|    | 9.6   |                    | ary and Trends                         | 160        |

|    | Refer | ences .            | -<br>                                  | 161        |

| 10 | Physi | col Imn            | lementation                            | 165        |

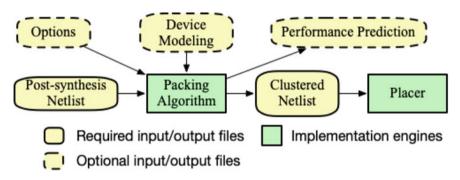

| 10 | 10.1  |                    | g                                      | 165        |

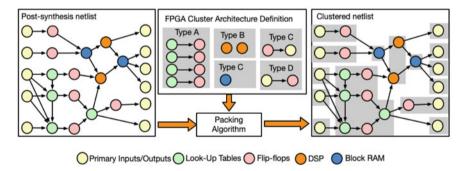

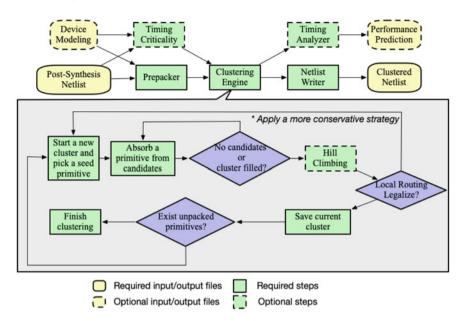

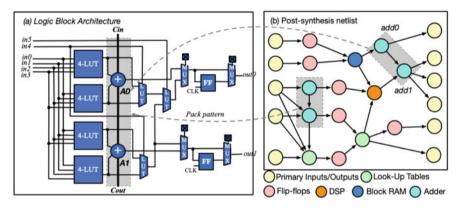

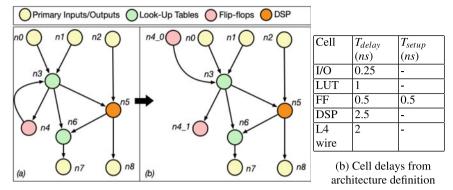

|    | 10.1  | 10.1.1             | Overview                               | 165        |

|    |       | 10.1.1             | Seed-Based Packing Algorithms          | 169        |

|    |       | 10.1.2             | Partition-Based Packing Algorithms     | 176        |

|    |       | 10.1.3             | Summary and Trends                     | 179        |

|    | 10.2  |                    | ent                                    | 180        |

|    | 10.2  | 10.2.1             | Overview                               | 180        |

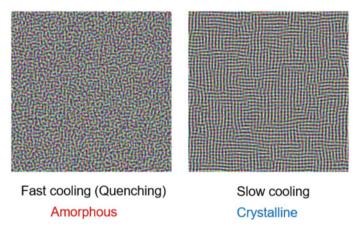

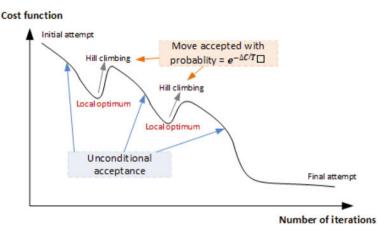

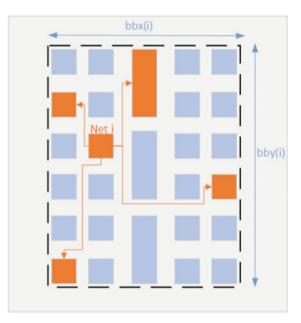

|    |       | 10.2.1             | Annealing Placement Algorithms         | 182        |

|    |       | 10.2.2             | Analytical Placement Algorithms        | 189        |

|    |       | 10.2.3             | Summary and Trends                     | 192        |

|    | 10.3  | Routing            | · · · · · · · · · · · · · · · · · · ·  | 193        |

|    | 10.5  | 10.3.1             | Overview                               | 193        |

|    |       | 10.3.2             | Negotiation-Based Routing Algorithms   | 195        |

|    |       | 10.3.3             | Summary and Trends                     | 201        |

|    | Refer |                    | · · · · · · · · · · · · · · · · · · ·  | 201        |

| 11 |       |                    |                                        |            |

| 11 |       |                    | nfiguration                            | 207        |

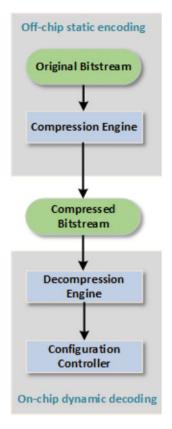

|    | 11.1  |                    | m Generation                           | 207        |

|    |       | 11.1.1             | Overview                               | 207        |

|    | 11.2  | 11.1.2<br>Diterret | Mode-Based Technique                   | 208        |

|    | 11.2  | 11.2.1             | m Compression                          | 210<br>210 |

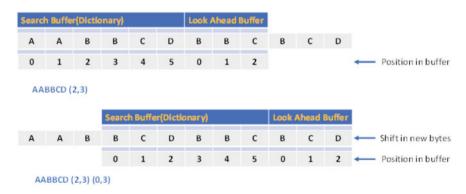

|    |       | 11.2.1             | Overview                               | 210        |

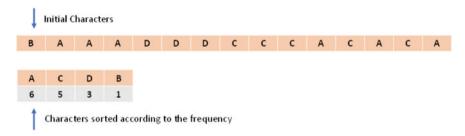

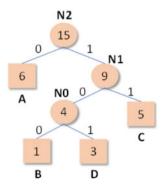

|    |       | 11.2.2             | Non-entropy Encoding                   | 211 213    |

|    | 11.2  |                    | Entropy Encoding                       | 213<br>215 |

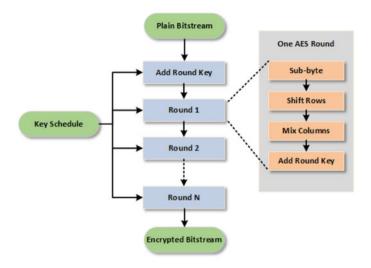

|    | 11.3  | 11.3.1             | m Encryption                           | 215        |

|    |       | 11.3.1             | Overview                               | 215        |

|    | 11.4  |                    | AES-Based Technique                    | 210        |

|    | 11.4  | 11.4.1             | am Programming                         | 217        |

|    |       | 11.4.1             | Overview<br>JTAG-Based Technique       | 217        |

|    | Dofor |                    | 1                                      | 218        |

|    | Keler | ences .            |                                        | 218        |

#### Part VI Summary and Outlook

| 12 | Summary and Outlook |                         |     |  |  |

|----|---------------------|-------------------------|-----|--|--|

|    |                     | FPGA EDA's Crossroads   |     |  |  |

|    | 12.2                | Our Book's Future Works | 226 |  |  |

# Part I Introduction

## Chapter 1 Introduction

**Abstract** Field programmable gate array (FPGA) is a typical semi-custom integrated circuit. The function of an FPGA is decided by both chip vendors and end users. Just like many other semiconductors, the design process of FPGA highly depends on Electronic Design Automation (EDA) tools. This chapter sorts out the complicated knowledge universe of FPGA technology, highlighting the EDA systems within. Due to FPGA's semi-custom characteristics, FPGA EDA is very distinctive and can be accordingly categorized into two different fields: chip design EDA and application design EDA.

#### 1.1 FPGA Hardware Brief Introduction

#### 1.1.1 FPGA Concept

FPGA is a semi-custom integrated circuit, that is, programmable units within it are pre-customized by vendors in the design house, after the device is manufactured and delivered to the end users, it can be "field"-customized for a second time to fully implement the desired functionality.

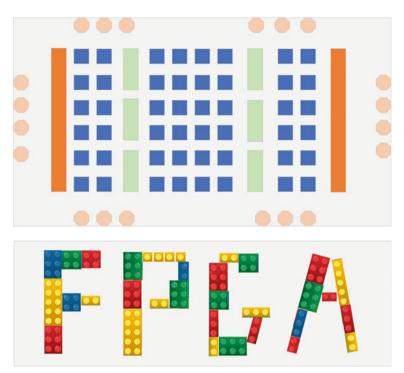

This characteristic makes FPGAs just like "lego" in the semiconductor world (Fig. 1.1), which means you can assemble (program) the pre-designed blocks (programmable units) into figures (circuit functions).

However, these "pre-design" and "assemble" tasks for FPGAs are too complicated to be carried out without computer's help; EDA is hereby introduced in to make them possible.

Fig. 1.1 FPGA-The electronic "lego" of the semiconductor world

Fig. 1.2 World's first FPGA—Xilinx XC2064

#### 1.1.2 FPGA Hardware Evolution

Xilinx Corporation (acquired by AMD in 2022) invented the first commercial FPGA– XC2064 (Fig. 1.2) in 1985. The device contains 64 programmable logic units consisting of two 3-input *Look-Up Tables* (LUTs) and an *Flip-Flop* (FF), enabling true "field" programmability for the first time. IEEE listed Xilinx XC2064 as one of the "25 Microchips that Shook the World" in 2009 [1] and inducted it into the "Chip Hall of Fame" in 2017 [2]. From that start point, FPGA has always stayed at the forefront of semiconductor technology and gradually forged a unique and complex knowledge system of itself, including FPGA chip design, FPGA chip design EDA, FPGA application design, FPGA application design EDA, FPGA foundry, FPGA assembly and testing, FPGA sales and marketing, etc. With more and more heterogeneous units are integrated into FPGAs, this knowledge system is expanding at an unprecedented speed. It is conceivable that if someone wants to run an FPGA business successfully, the first and most tricky thing to do is gathering a large group of professionals from a number of totally different fields. FPGA vendors, especially the top ones, have led the innovation for most of the time due to their strong ability to integrate supply chain resources from upstream to downstream and to maintain a diversed and interdisciplinary talent echelon.

FPGA hardware evolution can be inspected from several perspectives:

1. In terms of configuration memory

Configuration memory that stores the configuration bit data is one of the fundamental components of FPGA. Just like the material of lego toys can be various, FPGAs accordingly can be categorized into several types in terms of configuration memory:

a. SRAM (Static Random Access Memory) type

Mainstream type since FPGA was born, the configuration data should be read into the on-chip SRAM when the power is turned on. After the configuration is completed, the configuration data in SRAM will be lost (volatile), and the internal logic function of the FPGA will also disappear. SRAM-based FPGAs are reusable and low-cost, but reloading may needs an external memory device's help.

b. Antifuse type

This type of FPGA can only be programmed once by burning the fuses within and was first introduced in 1992. Although loses the flexibility of reprogramming, it greatly improves the stability. FPGAs with this structure are more suitable for applications in harsh environments, such as high vibration and strong electromagnetic radiation and other aerospace fields. Because of the fixed logic, the device powers up instantaneously and consumes less power and size than other types of FPGAs.

c. Flash type

Flash memory is non-volatile, the FPGA of this type has the flexibility of SRAM structure and the reliability of anti-fuse structure at the same time. The cost of this technology is high, but the number of transistors used and leakage current are relatively small [3]. This type of devices is also very suitable for aerospace applications [4–6].

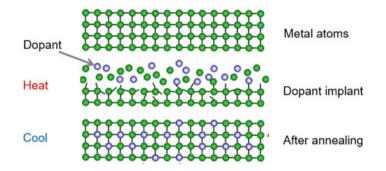

d. Emerging technology

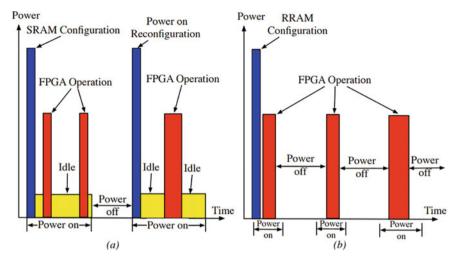

To further advance non-volatile FPGA's PPA (Power, Performance and Area), emerging device technology is actively researched in the last two decades. Resistive Random Access Memory (RRAM) [7] and Magnetoeresistive Random Access Memory (MRAM) [8] are the two representative non-volatile

Fig. 1.3 Power consumption of a volatile (SRAM) FPGA and b non-volatile (RRAM) FPGA

memory devices, which have strong potential in substituting Flash memory in FPGAs (Fig. 1.3).

Both technologies share common advantages over Flash memory in

- i. compatibility to BEoL (Back End of Line) process, leading to significantly higher area density. Unlike Flash transistors, RRAMs and MRAMs are fabricated between metal layers, no longer consume transistor area [9, 10].

- ii. low read/write voltages as well as current, being similar to nominal voltages of logic transistors. This avoids dedicated circuits for accessing memory elements, which require different process than regular transistor and force PPA overhead [9, 11].

- iii. fast read and write speed at the level of nanoseconds, which can reduce programming time and power of FPGA devices [12, 13].

Nowadays, FPGAs based on emerging technologies have attracted intensive research interests and are considered as next generation of FPGA technology (Table 1.1).

These FPGAs are suitable for:

- i. IoT (Internet of Things) applications which require both ultra-lowerpower and high-performance at the same time.

- ii. aerospace applications which require highly robust against radiationinduced soft errors[14].

We refer interested readers to [15-19].

2. In terms of component resources

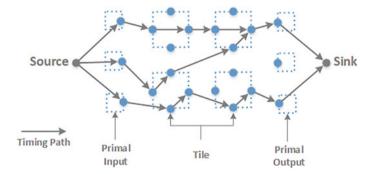

Modern FPGAs are composed of various "island-type" units and "ocean-like" interconnect resources among them. *Tile*, as the first-level sub-unit of FPGA,

| Memory type | Volatile | Programmability | Latency  | Power    | Area       | Cost      |

|-------------|----------|-----------------|----------|----------|------------|-----------|

| SRAM        | Yes      | Repeatable      | Low      | Medium   | Large      | Low       |

| Antifuse    | Non      | Once            | Very low | Very low | Very small | Very high |

| Flash       | Non      | Repeatable      | High     | Low      | Small      | Medium    |

| MRAM        | Non      | Repeatable      | Low      | High     | Small      | High      |

| RRAM        | Non      | Repeatable      | Low      | High     | Small      | High      |

Table 1.1 Comparison of FPGAs based on different programmable memory type

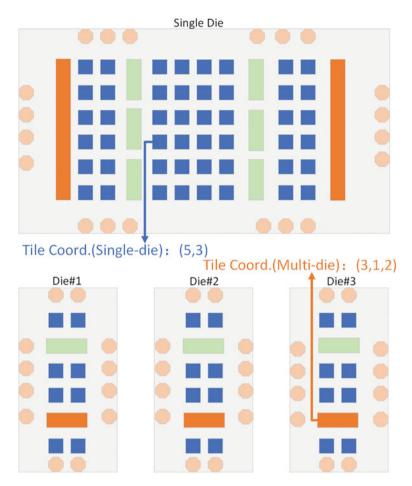

is composed of more fine-grained "*Site*" units. *Tiles* of the same type (excluding special types like I/O) are usually arranged in columns, and this layout can help approximate the distances between each general *tile* and I/O *tile*, so that there can be relatively high flexibility for physical implementation. Each *tile* has a unique address throughout the FPGA, which is typically represented by two-dimensional (for single-die) or even three-dimensional (for multi-die [20]) coordinates (Fig. 1.4).

The component resource types are rapidly enriched with the development of programmable technology. State-of-the-art FPGAs have even evolved into a hybrid device with multiple types of architectures. The current mainstream component resource types include:

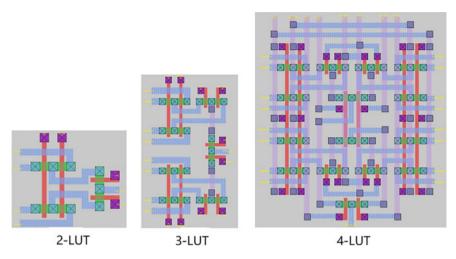

#### a. Generic Logic Tile (Spatial Computing Tile)

Generic Logic Tile (GLT) is the fundamental programmable unit distributed in the FPGA, and the site under this unit is called Generic Logic Site (GLS). GLS here is generally composed of LUT/FF, and the structure of the GLT/GLS can be various.

#### AMD GLT—CLB [21]:

Configurable Logic Block (CLB) is the main resource for AMD FPGA to implement basic sequential and combinational circuit functions (Table 1.2). Taking AMD's Versal architecture as an example, each CLB contains 4 GLSs, and each GLS contains 8 adaptive LUT6s and 16 FFs. AMD GLS has two types: SliceL (Logic) and SliceM (Memory). The latter enables the LUT under the GLS to be used as distributed memory by adding independent write addresses, write enable and clock signals. By enabling distributed memory, the maximum capacity of the chip memory is increased, and the memory usage efficiency is improved.

Intel GLT—LAB/MLAB [22]:

Logic Array Block (LAB) is the main resource for Intel FPGA to implement basic sequential and combinational circuit functions (Table 1.3). MLAB (Memory LAB) is a superset of LAB. In addition to all LAB functions, it supports dual-port SRAM up to 640 bit as a distributed memory. Taking Intel's Hyperflex architecture as an example, each LAB/MLAB contains 10 GLSs, and each GLS contains 1 adaptive LUT6 and 4 FFs. Intel GLS is called Adaptive Logic Module (ALM), and its structure is slightly different in LAB and MLAB.

Fig. 1.4 Tile coordinate systems in single-die/multi-die FPGA

| Table 1.2 AND GLI resources—versar architecture |                            |      |    |             |             |           |  |

|-------------------------------------------------|----------------------------|------|----|-------------|-------------|-----------|--|

| AMD GLT                                         | AMD GLS                    | LUT6 | FF | Carry chain | Distributed | Shift     |  |

|                                                 |                            |      |    |             | RAM         | register  |  |

| CLB                                             | 4 (2 SliceL + 2<br>SliceM) | 32   | 64 | 4           | 2048 bits   | 1024 bits |  |

Table 1.2

AMD GLT resources—Versal architecture

| Table 1.3 | Intel GLT | resources- | –HyperFlex | architecture |

|-----------|-----------|------------|------------|--------------|

|-----------|-----------|------------|------------|--------------|

| Intel GLT | Intel GLS | LUT6 | FF | Carry chain | Distributed<br>RAM | Shift<br>register |

|-----------|-----------|------|----|-------------|--------------------|-------------------|

| LAB       | 10 (ALM)  | 10   | 40 | 1           | 1                  | 1                 |

| MLAB      | 10 (ALM)  | 10   | 40 | 1           | 2048 bits          | 1024 bits         |

#### b. Input/Output Tile

Input/Output Tile (IOT), powered by groups of banks, is the interface between FPGA and the outside world. There are many types of IO in modern FPGAs, categorized into single-ended IO (LVTTL, LVCMOS, DDR, etc.) and differential IO (LVDS, LVPECL, SerDes, etc.). Single-ended signaling is the simplest and most commonly used method for transmitting electrical signals between devices. The signal is represented by a varying voltage on one wire; however, the dynamic power consumption of single-ended IO increases exponentially with the increase of clock frequency, so it is not suitable for application in high-speed circuits. Then comes the differential IO, it uses two wires for each signal (differential pair), which has better noise immunity than single-ended IO.

c. Clock Management Tile

Clock Management Tile (CMT) is a firmware resource dedicated to clock synthesis, elimination of clock skew, and clock phase and frequency adjustment in the FPGA. By programming, high precision, low jitter frequency multiplication, frequency division, duty cycle adjustment, and phase shift of the clock can be achieved. Delay Locked Loop (DLL) and Phase Locked Loop (PLL) are two common CMT implementations. DLL is based on the digital sampling method, which inserts a delay between the input clock and the feedback clock so that the rising edges of the input clock and the feedback clock are consistent. It is also called a digital phase-locked loop. The PLL, also known as an analog phase-locked loop, uses voltage to control the delay, and uses a voltage-controlled oscillator (VCO) to achieve a delay function similar to that in the DLL, also known as an analog phase-locked loop.

d. Memory

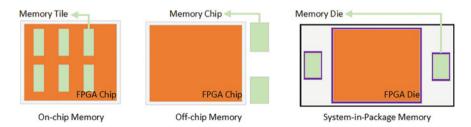

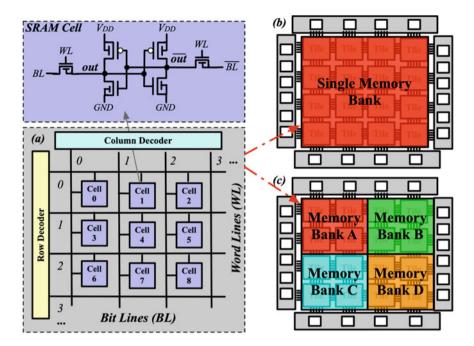

There are different types of memory for FPGAs (Fig. 1.5) listed below. On-chip memory (Memory Tile, MMT):

On-chip memory means FPGA integrates the memory tile as a hard core. Block RAM (BRAM) is a typical representative of traditional on-chip memory. This tile can be programmed as single port, simple dual port, true dual port, read-only memory or other modes, and the depth and width of the stored data can also be configured with high flexibility. The Distributed RAM configured by the look-up table is an effective supplement to the BRAM and is suitable for

Fig. 1.5 Different types of memory for FPGAs

small storage requirements. The location of the BRAM resources in the FPGA is fixed and generally distributed in columns, which may cause a long wiring delay to the general logic, the use of distributed storage can help to ease the pain.

Off-chip memory (Memory Chip):

Off-chip memory is a memory that places on the periphery of an FPGA and provides extended storage space for it. A typical representative is DDR RAM. System-in-Package memory (Memory Die):

System-in-Package (SiP) memory is a memory that integrated with general logic through an interposer to further expanding storage space. The typical representative is High Bandwidth Memory (HBM), which compactly connects stacked Dynamic Random Access Memory (DRAM) and FPGA through an interposer. This technology makes it possible for AI algorithms to be completely run on-chip, at the same time as the integration level is improved, the bandwidth is no longer limited by the number of interconnections of chip pins, so that the IO bottleneck is solved to a certain extent.

e. Scalar Computing Tile

SCT (Scalar Computing Tile), typically represented by Central Processing Unit (CPU) and Micro Controller Unit (MCU), has their unique advantages that traditional FPGA cannot achieve. Traditional FPGAs are good at parallel processing, and scalar engines are good at running control, the combination of the two can achieve a higher performance/watt ratio. Embedding SCTs in FPGA has become a common practice (e.g., ARM in AMD Zynq family/RISC-V in Microchip PolarFire family). Apart from such hard core implementations, some scalar engines are designed as soft cores (e.g., Intel's NIOS/AMD's MicroBlaze).

f. Vector Computing Tile

VCT (Vector Computing Tile), typically represented by Digital Signal Processing (DSP) unit and Graphics Processing Unit (GPU), is more efficient on processing a narrower set of parallel computing functions; however, it suffers from limited latency and efficiency due to inflexibility of memory hierarchies.

- g. Matrix Computing Tile Matrix Computing Tile (MCT) are purpose-built tiles that offer dramatic leaps in performance for AI workloads (matrix multiplication).

- h. Other Analog/ASIC Tiles Except for the tiles above, in modern FPGAs, many analog or application specific units are integrated, such as analog-to-digital/digital-to-analog conversion (ADC/DAC) units, video codec units, etc.

- i. Clock Tree Resources CTR (Clock Tree Resources) is a special set of signal paths inside the FPGA, like its vascular network. The clock signal on the clock network can ensure a relatively small signal skew, that is, make sure the time that the clock signal reaches each flip-flop is as close as possible.

- j. Interconnect Resources ICR (Interconnect Resources) provide communication channels that connect

Fig. 1.6 World's first SoC FPGA—Altera excalibur

all tiles together inside the FPGA, like its neural network. Traditional interconnect resources are controlled by programmable switches, which allow signals to switch to different paths. Modern FPGAs also use Network on Chip (NoC) interconnects that act like highways to accelerate the inner data transfer process.

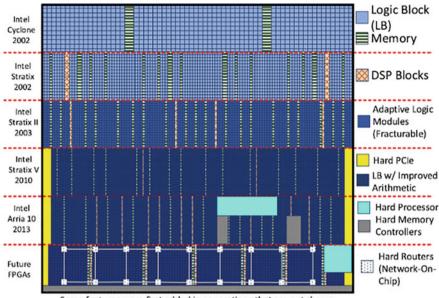

Since the first heterogeneous computing engines (ARM SCT) was integrated into FPGA by Altera (acquired by Intel in 2015) in 2000 (Fig. 1.6), the era of SoC FPGA has begun. More and more types of architectures have been successfully coupled under the same umbrella (Fig. 1.7), and in [23], FPGA architecture progression has been well reviewed. Until 2019, Xilinx finally merges nearly all popular architectures in a single chip (Versal series) and pushing adaptive SoCs to a whole new level. Here is a brief history of FPGA resource evolution (Table 1.4).

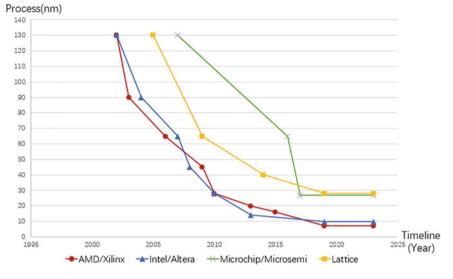

3. In terms of process technology

FPGA always pursuits the most advanced process node, since the beginning of 21st century, the big two (AMD/Xilinx and Intel/Altera) alternately lead the node shrinking race.

a. Bulk/SOI

Bulk is the traditional technology for FPGA. It is built on a standard silicon wafer. In contrast to bulk, Silicon-On-Insulator (SOI) makes use of SOI wafers, which incorporate a thin insulating layer within the substrate to suppress leakage. There are two types of SOI devices: partially depleted (PD-SOI) and fully depleted SOI (FD-SOI). Lattice (28 nm) and Quicklogic (22 nm) are on FD-SOI technology.

b. Planar/FinFET/GAAFET

Complementary metal-oxide semiconductors (CMOS) technology introduced planar transistors in the mid-20th century; however, the downsizing of planar transistors also brought numerous problems such as gate leakage currents, short channel effects, quantum tunneling leakage, variability, mobility degradation, etc. New technologies then come out to ease the pain, such as FinFET and GAAFET.

FinFET (Fin Field Effect Transistor) technology is for relatively high-end

Some features were first added in generations that are not shown.

Fig. 1.7 Increasing heterogeneity of Intel/Altera FPGAs[24]

| Resource type                     | First introduced family       | Time (year) |

|-----------------------------------|-------------------------------|-------------|

| GLT (LUT/FF)                      | Xilinx XC2000                 | 1985        |

| IOT (Basic)                       | Xilinx XC2000                 | 1985        |

| ICR (Basic)                       | Xilinx XC2000                 | 1985        |

| GLT (Carry chain/distributed RAM) | Xilinx XC4000                 | 1991        |

| MMT (BRAM)                        | Altera FLEX                   | 1995        |

| CMT (PLL)                         | Altera FLEX                   | 1996        |

| CMT (DLL)                         | Xilinx Virtex                 | 1998        |

| SCT (ARM)                         | Altera Excalibur              | 2000        |

| VCT (Fixed point DSP)             | Xilinx Virtex-II              | 2001        |

| IOT (DDR IO)                      | Xilinx Virtex-II              | 2001        |

| IOT (SerDes IO)                   | Xilinx Virtex-II              | 2001        |

| SCT (PowerPC)                     | Xilinx Virtex-II Pro          | 2001        |

| VCT (Float point DSP)             | Intel Arria10                 | 2015        |

| VCT (GPU)                         | Xilinx Zynq Ultrascale+ MPSoC | 2015        |

| Other (RF)                        | Xilinx Zynq Ultrascale+ RFSoC | 2017        |

| MMT (HBM)                         | Intel Stratix10 MX            | 2017        |

| ICR (NoC)                         | Achronix Speedster7t          | 2019        |

| MCT (AI)                          | Xilinx Versal                 | 2019        |

| SCT (RISC-V)                      | Microchip PolarFire           | 2022        |

Table 1.4 FPGA resource-type evolution history

#### 1.1 FPGA Hardware Brief Introduction

FPGAs (such as 16nm/14nm and beyond). It has a fin-shaped body – the silicon fin that forms the transistor's main body. FinFET devices display superior short-channel behavior and have considerably lower switching times, and higher current density than planar technology.

GAAFET (Gate-All-Around Field Effect Transistor) is a promising and futuristic transistor candidate to replace FinFET, since the channel width variations could cause undesirable variability and mobility loss as the fin width in a fin-FET approaches 5 nm (Fig. 1.8).

Just like planar technology, the source, gate, and drain can sit on an insulating layer (SOI) or on bare silicon (bulk). Most of the advanced Intel/AMD FPGAs (below 20 nm) are on bulk FinFET technology at the moment.

- 4. In terms of package technology

- a. Wire-bond/Flip-chip

Wire-bond is the oldest and most common assembly technology. In a wirebond FPGA, the IC is mounted to the substrate with the "active face" the face where the circuitry has been built-up. Small wires arch from the inputs and outputs ("I/Os") on the outside edges-known as the "periphery" of the IC to a specific on the substrate.

Flip-chip has emerged as the best alternative to wire bond. The defining feature of the flip-chip package is a "flipped" IC, with the active side facing downward or toward the substrate. The interconnects in a flip-chip FPGA are much shorter than wire-bond, meaning that electrical losses and heat generation will be less severe.

b. Planar/2.5D/3D

Instead of traditional planar package solutions (single die), 2.5D package integrates multiple dies on a single interposer and interconnecting those chiplets on that interposer using metal interconnect. Intel/AMD's advanced FPGA devices commonly adopted this type of technology.

True 3D package is a very advanced technology that splits FPGAs into multiple chips and stacks them. It still needs some time for true 3D FPGA to embrace mass production.

#### 1.1.3 FPGA Compares With Other Architectures

1. A prototype platform for other architectures

The coolest Bugatti sports car in the world can be built with "lego" blocks (in fact, modern automobile manufacturing is also based on modularity), just like a cutting-edge architecture being prototyped by an FPGA. Using "lego" blocks to build a car that can actually drive will face many handicaps, for example, complex engine is difficult to implement, the solution would be installing a real engine (like

Fig. 1.8 FPGA giants' technology node cadence (as of 2023)

Fig. 1.9 "Lego" Bugatti Chiron and real Bugatti Chiron

Fig. 1.10 FPGA compares with other computation architectures

embedding scalar computing tile) in it; tyres are also a problem, yet the simplest way is just put four real rubber tyres (like embedded analog circuit components) on it. This is another practice of heterogeneous integrating—put some "real car" parts in a "lego car".

Due to its hardware programmability, FPGA is an ideal prototype platform to simulate chip functions of any architectures in theory. When the shipment is not so huge (below around \$3m/400,000 pieces) or the function still needs iteration, FPGA, with zero *Non-Recurring Engineering* (NRE) cost and relatively high flexibility, is the choice (Fig. 1.9).

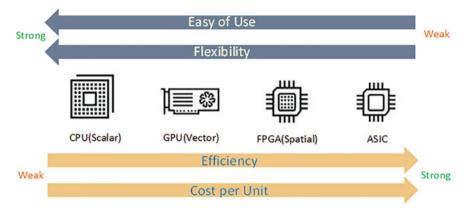

2. A computation platform with other architectures In terms of flexibility and easy of use, traditional FPGA has advantages over ASIC but cannot compete with software programmable scalar/vector architectures, however, if you look at performance and power efficiency or cost per unit, the story comes the opposite way. That's something called trade-offs (Fig. 1.10).

#### 1.2 FPGA EDA Brief Introduction

#### 1.2.1 FPGA EDA Concept

Electronic Design Automation, as its name suggests, is using computers to help electronic circuits design and therefore crowned as the "mother of chips". FPGA designs highly depend on EDA without exception.

The full design process of FPGA is divided into two stages: the chip design stage and the application design stage. The former is completed by the FPGA vendors, and

Fig. 1.11 FPGA design full flow: from vendors to users

Fig. 1.12 FPGA EDA full flow: from vendors to users

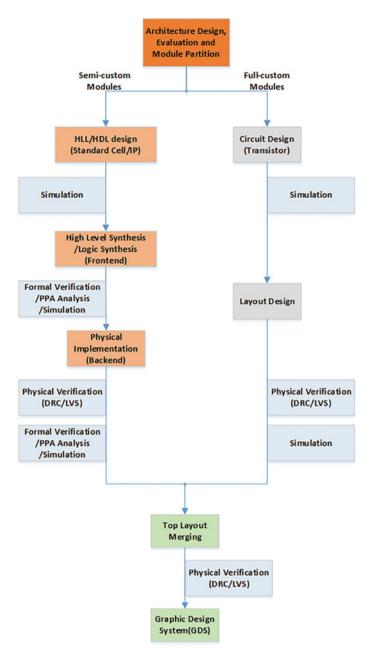

the latter is handed over to the FPGA users. Both full-custom and semi-custom design methods are adopted during the chip design. Full-custom design requires designers to complete circuit design from the bottom-level, while another design approach, semi-custom design, uses pre-designed macros to simplify the effort (Fig. 1.11).

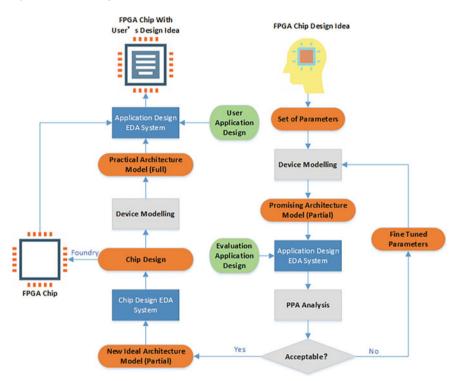

Correspondingly, FPGA EDA can also be divided into two parts: FPGA chip design EDA (to assist vendors in chip design stage) and FPGA application design EDA (to assist end users in application design stage) (Fig. 1.12). For FPGA chip design EDA, EDA vendors such as Cadence/Synopsys/Siemens provide univer-

| Tuble The Different DDT systems for neterogeneous hard wire are interetate |                                 |                                        |  |

|----------------------------------------------------------------------------|---------------------------------|----------------------------------------|--|

| Hardware architecture                                                      | Chip design EDA                 | Application design EDA                 |  |

| Spatial (Vanilla FPGA)                                                     | Virtuoso, Fusion compiler, etc. | Vivado, Quartus, etc.                  |  |

| Scalar                                                                     | Virtuoso, Fusion compiler, etc. | Keil, IAR, etc.                        |  |

| Vector                                                                     | Virtuoso, Fusion compiler, etc. | CUDA, etc.                             |  |

| Matrix                                                                     | Virtuoso, Fusion compiler, etc. | TensorFlow Compiler, PyTorch JIT, etc. |  |

| ASIC                                                                       | Virtuoso, Fusion compiler, etc. | 1                                      |  |

Table 1.5

Different EDA systems for heterogeneous hardware architecture

sal design tools, and for FPGA application design EDA, FPGA vendors such as AMD/Intel/Microchip provide proprietary tools that only serve their own chips.

For modern SoC FPGAs, the integrated heterogeneous scalar/vector/matrix computing tiles have their own application design EDA systems different from vanilla FPGAs (Spatial). Although the industry is trying to unify them altogether (Intel oneAPI and AMD Vitis), vanilla FPGA EDA technology is currently still a selfcontained system that cannot be replaced in a short period of time. The following chapters of this book mainly focus on vanilla FPGA EDA (Table 1.5).

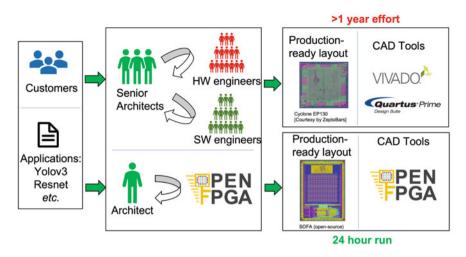

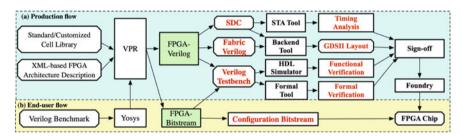

#### 1.2.2 FPGA Chip Design EDA

In FPGA chip design, full-custom method (designing based on transistors) is like "elaborately carving a painting on stones", so the performance of the chip can be maximized without wasting too much chip area; however, this design method consumes more labor and time; while semi-custom method (designing based on standard cells or IPs) runs through the classic synthesis-implementation flow and is much more quicker due to the higher level of automation, but sometimes cannot achieve the best result. Considering these trade-offs, only the integrated circuits that require extremely high performance, low power consumption and limited area will use the full-custom approach.

Figure 1.13 shows the brief flow of FPGA chip design. At the beginning of it, designers will evaluate the architecture based on the requirements and then do the module partition, deciding which modules should be designed with full-custom method and which modules should be designed with semi-custom method. After each module is finished on their own way, they are merged at the top level to form the final design.

Legacy EDA tools for FPGA chip design are abundant, and (Table 1.6) lists the most popular ones.

Fig. 1.13 Vanilla FPGA chip design EDA flow

| Frameworks      | Туре                 | Maintainer               | License    | Description                                                                                                               |

|-----------------|----------------------|--------------------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| Virtuoso        | Full-custom          | Cadence                  | Commercial | A holistic, system-based<br>solution that provides<br>functionality to do the custom<br>IC design and sign-off            |

| Fusion compiler | Semi-custom          | Synopsys                 | Commercial | RTL-to-GDSII implementation<br>system architected to address<br>the complexities of advanced<br>process node design       |

| Calibre         | 1                    | Siemens EDA              | Commercial | Well known IC sign-off<br>verification and DFM (Design<br>For Manufacturability)<br>optimization tool                     |

| OpenFPGA        | Semi-custom          | CHIPS Alliance           | MIT        | The first open-source FPGA IP<br>generator supporting highly<br>customizable homogeneous<br>FPGA architectures            |

| COFFE           | Full/Semi-<br>custom | University of<br>Toronto | MIT        | An open-source FPGA design<br>toolset for automatic FPGA<br>circuit design                                                |

| Australis       | Semi-custom          | QuickLogic               | Commercial | Built on the OpenFPGA<br>open-source framework that<br>enables rapid prototyping of<br>customizable FPGA<br>architectures |

Table 1.6

Iconic vanilla FPGA chip design EDA frameworks

Table 1.7

Iconic vanilla FPGA application design EDA frameworks

| Frameworks  | Maintainer               | License    | Description                                                                                                                                   |

|-------------|--------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| VTR         | University of<br>Toronto | MIT        | A world-wide collaborative effort to provide an<br>open-source framework for conducting FPGA<br>architecture and EDA research and development |

| F4PGA       | CHIPS Alliance           | Apache-2.0 | A Verilog-to-Bitstream EDA flow targeting commercial FPGAs                                                                                    |

| RapidWright | AMD/Xilinx               | Apache-2.0 | Provide Vivado Interface for users to build customized<br>FPGA implementations                                                                |

| Vivado      | AMD/Xilinx               | Commercial | A Classic FPGA EDA design suite that supports<br>AMD/Xilinx devices                                                                           |

| Quartus     | Intel/Altera             | Commercial | A Classic FPGA EDA design suite that supports<br>Intel/Altera devices                                                                         |

| Synplify    | Synopsys                 | Commercial | Industry standard logic synthesis tool for producing high-performance, cost-effective FPGA designs                                            |

| ModelSim    | Siemens                  | Commercial | A multi-language environment for simulation of<br>hardware description languages and includes a built-in<br>C debugger                        |

Fig. 1.14 Vanilla FPGA application design EDA flow

#### 1.2.3 FPGA Application Design EDA

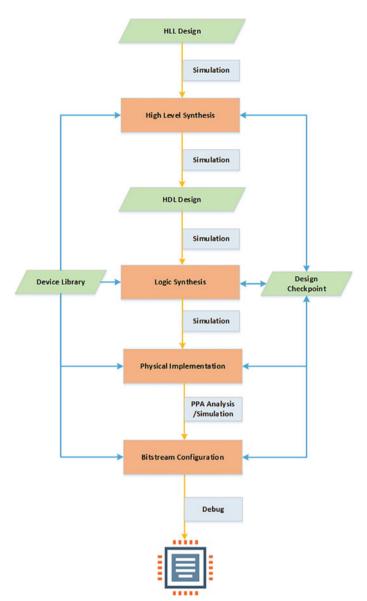

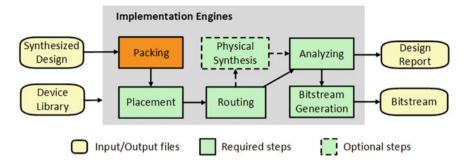

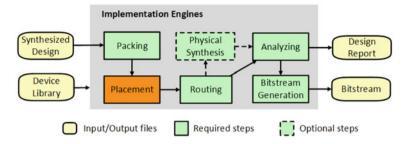

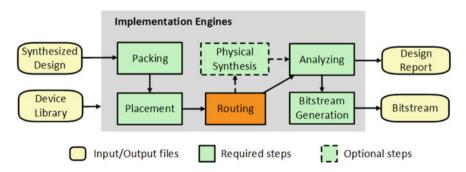

The traditional FPGA application design EDA process includes high-level synthesis, logic synthesis, physical implementation, bitstream configuration, and simulation/debugging. The FPGA device data (Device Library) and design data (Design Checkpoint) are the two major data sources for the EDA system. More specifically, high-level synthesis converts the user's high-level abstract description (High-Level Language, HLL) design into a low level hardware description (Hardware Description Language, HDL) design; logic synthesis converts the low level hardware description design into a design database that contains a design netlist composed of FPGA design units and their interconnections; physical implementation further decides how the design is physically implemented on the target FPGA; bitstream configuration converts the final implemented design into an bitstream of a specific format, and then downloads it into the target device according to the configuration protocol. After each process above is done, the simulation tools and PPA analysis tool can be invoked to sign-off the design. Simulation and debugging activities are carried out throughout the application design process to ensure that the original idea of the designer is implemented properly.

There is a lot of legacy practices constructing FPGA application design EDA flow both from industrial and academic world. Table 1.7 lists some of the most iconic frameworks (Fig. 1.14).

#### References

- 1. IEEE, 25 microchips that shook the world (2009). https://spectrum.ieee.org/25-microchips-that-shook-the-world

- IEEE, Chip hall of fame: Xilinx xc2064 FPGA (2017). https://spectrum.ieee.org/chip-hall-offame-xilinx-xc2064-fpga

- 3. M. Abusultan S.P. Khatri, Exploring static and dynamic flash-based FPGA design topologies, in 2016 IEEE 34th International Conference on Computer Design (ICCD) (2016), pp. 416–419

- N. Rezzak, J.-J. Wang, D. Dsilva, N. Jat, TID and see characterization of Microsemi's 4th generation radiation tolerant rtg4 flash-based FPGA, in 2015 IEEE Radiation Effects Data Workshop (REDW) (2015), pp. 1–6

- P.R.C. Villa, R.C. Goerl, F. Vargas, L.B. Poehls, N.H. Medina, N. Added, V.A.P. de Aguiar, E.L.A. Macchione, F. Aguirre, M.A.G. da Silveira, E.A. Bezerra, Analysis of single-event upsets in a Microsemi proasic3e FPGA, in 2017 18th IEEE Latin American Test Symposium (LATS) (2017), pp. 1–4

- J. Greene, S. Kaptanoglu, W. Feng, V. Hecht, J. Landry, F. Li, A. Krouglyanskiy, M. Morosan, V. Pevzner, A 65 nm flash-based FPGA fabric optimized for low cost and power, in *Proceedings* of the 19th ACM/SIGDA International Symposium on Field Programmable Gate Arrays (FPGA '11) (ACM, New York, NY, USA, 2011), pp. 87–96

- H.S.P. Wong, H.Y. Lee, S. Yu, Y.S. Chen, Y. Wu, P.S. Chen, B. Lee, F.T. Chen, M.J. Tsai, Metal-oxide RRAM, Proc. IEEE 100(6), 1951–1970 (2012)

- D. Apalkov, B. Dieny, J.M. Slaughter, Magnetoresistive random access memory. Proc. IEEE 104(10), 1796–1830 (2016)

- X. Tang, E. Giacomin, G.D. Micheli, P.E. Gaillardon, Circuit designs of high-performance and low-power RRAM-based multiplexers based on 4T(ransistor)1R(RAM) programming structure. IEEE Trans. Circ. Syst. I: Regul. Pap. 64(5), 1173–1186 (2017)

- B. Govoreanu, G.S. Kar, Y.Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I.P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, K. Seo, P. Hendrickx, G. Pourtois, H. Bender, L. Altimime, D.J. Wouters, J.A. Kittl, M. Jurczak, 10 × 10 nm<sup>2</sup> H<sub>f</sub>/H<sub>f</sub> O<sub>x</sub> crossbar Resistive RAM with excellent performance, reliability and low-energy operation, in 2011 International Electron Devices Meeting, Dec 2011, pp. 31.6.1–31.6.4

- X. Tang, G. Kim, P.-E. Gaillardon, G. De Micheli, A study on the programming structures for RRAM-based FPGA architectures. IEEE Trans. Circ. Syst. I: Regul. Pap. 63(4), 503–516 (2016)

- O. Turkyilmaz, S. Onkaraiah, M. Reyboz, F. Clermidy, C.A. Hraziia, J. Portal, M. Bocquet, RRAM-based FPGA for "Normally off, instantly on" applications, in 2012 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), July 2012, pp. 101–108

- J. Cong, B. Xiao, FPGA-RPI: a novel FPGA architecture with RRAM-based programmable interconnects. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(4), 864–877 (2014)

- R. Rajaei, Radiation-hardened design of nonvolatile MRAM-based FPGA. IEEE Trans. Magn. 52(10), 1–10 (2016)

- X. Tang, P.E. Gaillardon, G.D. Micheli, A high-performance low-power near-V<sub>t</sub> RRAM-based FPGA, in 2014 International Conference on Field-Programmable Technology (FPT), Dec 2014, pp. 207–214

- S. Tanachutiwat, M. Liu, W. Wang, FPGA based on integration of CMOS and RRAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(11), 2023–2032 (2011)

- Y.Y. Liauw, Z. Zhang, W. Kim, A. El Gamal, S.S. Wong, Nonvolatile 3D-FPGA with monolithically stacked RRAM-based configuration memory, in *Solid-State Circuits Conference Digest* of Technical Papers (ISSCC), 2012 IEEE International (IEEE, 2012), pp. 406–408

- Y.C. Chen, W. Wang, H. Li, W. Zhang, Non-volatile 3D stacking RRAM-based FPGA, in 22nd International Conference on Field Programmable Logic and Applications (FPL), Aug 2012, pp. 367–372

- K. Huang, R. Zhao, W. He, Y. Lian, High-density and high-reliability nonvolatile fieldprogrammable gate array with stacked 1D2R RRAM array. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(1), 139–150 (2016)

- X. Wu, 3d-IC technologies and 3d FPGA, in 2015 International 3D Systems Integration Conference (3DIC) (2015), pp. KN1.1–KN1.4

- AMD, Versal ACAP configurable logic block architecture manual. https://docs.xilinx.com/r/ en-US/am005-versal-clb/CLB-Architecture (2021)

- 22. Intel, Intel stratix 10 logic array blocks and adaptive logic modules user guide (2022). https:// www.intel.com/content/www/us/en/docs/programmable/683699/current/lab.html

- A. Boutros, V. Betz, FPGA architecture: principles and progression. IEEE Circ. Syst. Magazine 21(2), 4–29 (2021)

- S. Yazdanshenas, V. Betz, Automatic circuit design and modelling for heterogeneous FPGAs, in 2017 International Conference on Field Programmable Technology (ICFPT) (2017), pp. 9–16

# Part II FPGA Data Modeling

# Chapter 2 Device (Chip Design) Modeling

**Abstract** This chapter provides the principles and implementations of FPGA device (chip design) modeling. FPGA device information can be derived from the output of chip design data and then will become the input for application design. There are two practices in the FPGA EDA full flow that can share a common set of device models, one is for architecture exploration in the chip design stage, the other is for implementing end user's circuit in the application design stage.

#### 2.1 Device Description Levels

#### 2.1.1 Abstract Levels

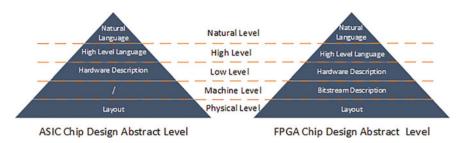

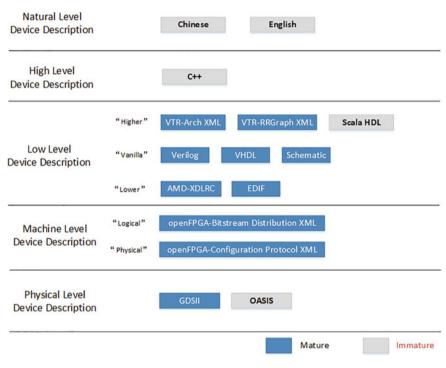

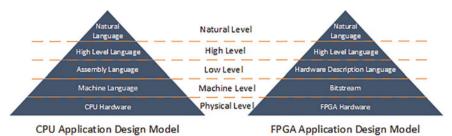

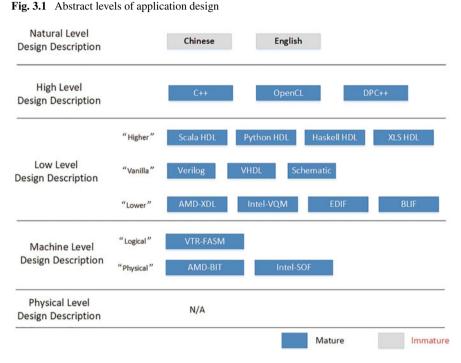

FPGA chip design is the output of the chip design EDA stage, it begins with a design description, which is quite similar to ASIC chip design. FPGA chip design can be described at different abstraction levels: natural level [1], high level [2], low level [3], machine level [4], and physical level, forming a pyramid (Fig. 2.1) from top to bottom.

FPGA device library comes from the chip design to some extent, yet is another different concept. It carries the FPGA chip design data that only will be used in the application design EDA stage. Therefore, describe an FPGA device at natural level, high level, or physical level is not yet wide spread in industry due to the immaturity of related tools, most of the existing research works about FPGA device description mainly stay at low level and machine level (Fig. 2.2).

1. Physical-Level Description

The device physical-level description refers to the layout of targeted technology, representing geometric shapes, text labels, etc. It is the final interface between chip designer and foundry. GDSII is the de facto industry standard format to carry messages at this level.

2. Machine-Level Description

The device machine-level description refers to the structure of underlying bitstream. It can be further divided into two sub-level descriptions: the "logical" description expresses each configuration bit's logical address—the correlation

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2024

K. Tu et al., FPGA EDA, https://doi.org/10.1007/978-981-99-7755-0\_2

Fig. 2.2 FPGA device description abstract levels

between bits and hardware units; the "physical" description presents each configuration bit's physical address—the bit physical organization format decided by configuration protocol.

3. Low-Level Description

The device low-level description refers to the characterization of hardware, and three sub-level descriptions are demarcated: the "vanilla" description, the "higher" description and the "lower" description.

At "vanilla" level, traditional vendor-neutral hardware descriptions (such as VHDL, Verilog, Schematic, or SPICE) are very common to represent the hard-

| Feature      | XML                                                                                                                                                 | JASON                                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format       | Format that has tags to define elements                                                                                                             | Format written in JavaScript                                                                                                                                              |

| Data storage | As a tree structure                                                                                                                                 | Like a map with key value pairs                                                                                                                                           |

| Speed        | Bulky and slow in parsing, leading to slower data transmission                                                                                      | Very fast as the size of file is<br>considerably small, faster parsing by<br>the JavaScript engine and hence faster<br>transfer of data                                   |

| File size    | Size is bulky, the tag structure makes it huge and complex to read                                                                                  | Compact and easy to read, no redundant<br>or empty tags or data, making the file<br>look simple                                                                           |

| Security     | Document Type Definition (DTD)<br>validation and external entity expansion<br>are enabled by default, making<br>structures disposed to some attacks | Safe at all times, although it might be<br>more at risk when JSONP (JSON with<br>Padding) is used since it can result in a<br>Cross-Site Request Forgery (CSRF)<br>attack |

Table 2.1 Feature comparison of XML and JASON

ware details.

At "higher" level, more abstracted hardware descriptions (such as XML, JASON) (Table 2.1) are very suitable for FPGA structure exploration in the early stage of design. Because if the promising structure is not ideal in the subsequent verification, designers can modify it at a higher level to quickly establish a new fine-tuned structure. However, description from this level may not fully reflect all special details of the hardware.

At "lower" level, more detailed hardware descriptions (such as AMD-XDLRC, EDIF) is used to specify detailed units in the FPGA device.

4. High-Level Description

The device high-level description refers to algorithmic languages (such as C++). High-level synthesis (HLS) EDA engine is needed to convert descriptions at this level into lower level.

5. Natural-Level Description

In addition to the above levels of device descriptions, industry's pursuit of higher abstraction (to a certain extent, also to reduce the labor cost of circuit design) has never stopped. The final form of device description is the language used by humans (English, Chinese, etc.). Natural language is the main tool for human communication and thinking, it is the crystallization of human wisdom. Natural language processing is also one of the most difficult problems in artificial intelligence [5].

Fig. 2.3 FPGA device description reuse levels

## 2.1.2 Reuse Levels

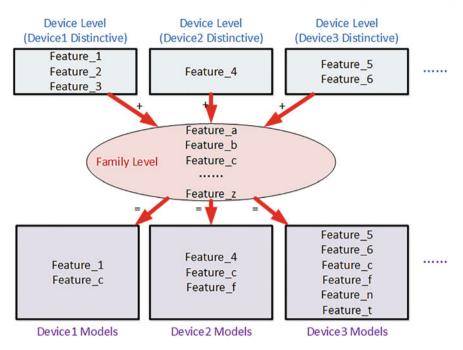

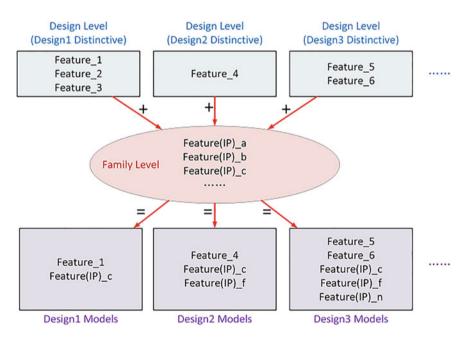

Considering the design reusability, modern FPGA vendors usually design a series of chips based on the same technology platform (process node, infrastructure features, cell libraries, etc.), which we call it "family". Under the same family, each device has a unique resource scale. Take AMD's FPGA as an example, there are dozens of devices in its Virtex-7 family that shares the same technology platform.

Considering there are common components (IPs) in an FPGA device from the same family, in order to simplify the complexity and improve the efficiency, the design features can be accordingly modeled at two levels: family level that shared by the entire family, and device level that only suitable for a specific single device (Fig. 2.3).

#### 2.2 Device Model Classifications

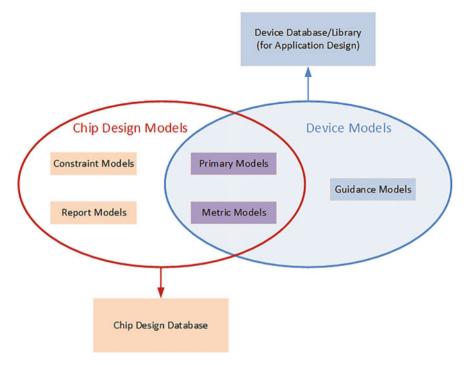

The device models of an FPGA partly come from the chip design. The "device library", built from these models, contains the device architecture-related EDA information that serves the application design flow. Device models can be categorized into

Fig. 2.4 FPGA device model classifications

several classes: primary, metric, and guidance (Fig. 2.4). When doing chip design, constraint models and report models are required, however, they are irrelevant with the device modeling.

## 2.2.1 Primary Class

The device primary models include logical resource structure model and configuration bit structure model. These models are essential inputs to application design EDA, and can be derived from the chip design process.

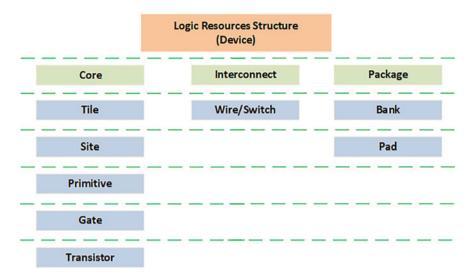

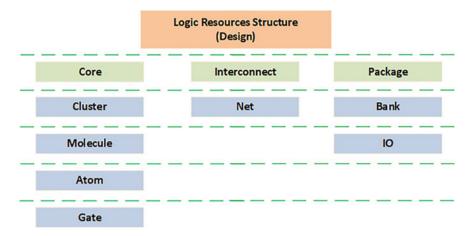

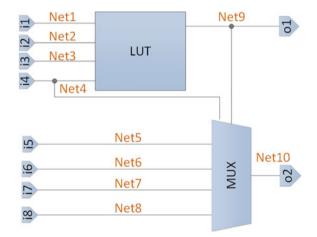

1. Logic Resource Structure (LRS) Model

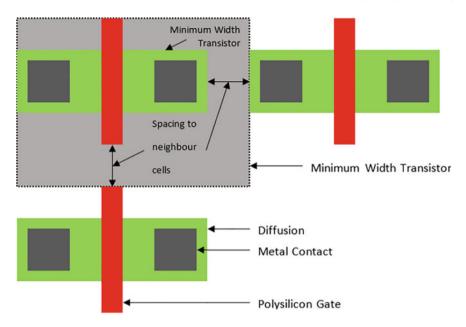

The logic resource structure of an FPGA device contains the core, the package, and the interconnect among them (Fig. 2.5).

The FPGA core has a traditional structural hierarchy: core-tile-site-primitive-gatetransistor. In chip design EDA, the full-custom method designs from the bottom transistor-level, while the semi-custom method designs from the relatively upper gate-level. In application design EDA, the situation is similar to semi-custom chip design, gate-level is the lowest noteworthy level since that is where logic synthesis

Fig. 2.5 FPGA device logical resource structure hierarchy

could possibly reach. It is worth mentioning that the design of modern clock networks could partition *tile* resources into different "regions", and some multi-chip packaged devices also define each stacked silicon as a "die", nonetheless, both these "dies" and "regions" are made of *tiles*. In order to simplify the illustration, we uses *tile* as the first-level sub-unit of a device.

The FPGA package has a much simpler structural hierarchy: package-bank-pad. A bank is a group of I/O pads that share a common resource such as one power supply or one output current reference, each group can independently support different I/O standards that can adapt to different electrical characteristics. At pad-level, pad arrangement/layout is required to make the package information intact.

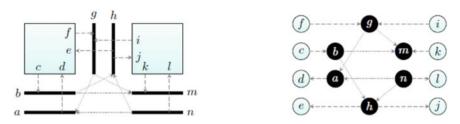

The FPGA interconnect resources organically combine all kinds of logic units together. These programmable interconnect resources can be abstracted as a network composed of wires and programmable switches. Wire is the carrier for signal transmission, and switch controls the flow direction of signals by switching on and off. They together form the device's routing architecture.

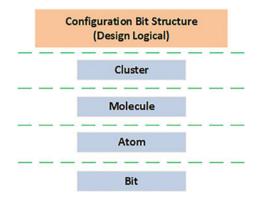

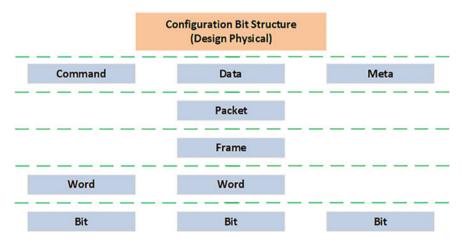

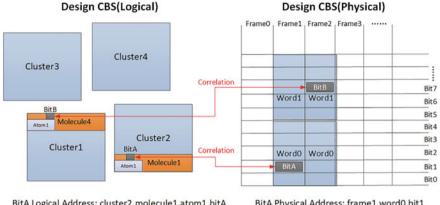

2. Configuration Bit Structure (CBS) Model

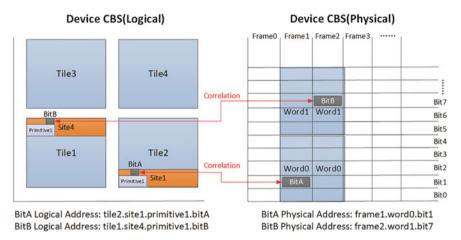

The configuration bit structure of an FPGA device can be defined from two perspectives: logical and physical.

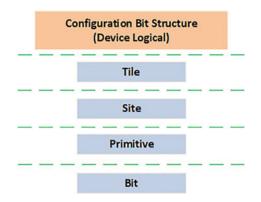

Logical CBS gives every bit a "logical address", that is, which logic resource it belongs to (Fig. 2.6).

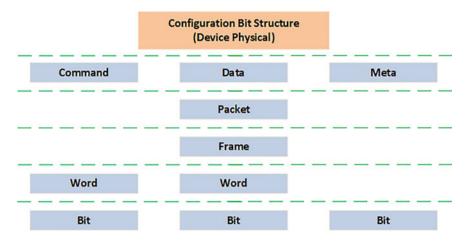

Physical CBS gives every bit a "physical address", that is, which position it lies in the final bitstream sequence according to the configuration protocol.

Configuration protocol depends on the circuitry designed to program an FPGA. It could be in different structures based on the application context, providing differ-

Fig. 2.6 FPGA device configuration bit structure hierarchy (logical)

ent trade-offs between speed and area. In industry, FPGA devices from the same family usually share the same configuration protocol. Here are some representative structures:

a. Chain-based

In this structure, configurable memories are connected in one or multiple chains and bitstream is loaded serially to program the FPGA.

b. Unit-based

The configuration memory is organized by logical units (such as *tiles* and *sites*) in which it resides, each configuration memory can be accessed by an address decoder. Due to the hierarchical structure of logical units, unit-based physical bit structure is also hierarchical.

c. Region-based

The configuration memory is organized in the form of a matrix area on the FPGA chip, and each configuration memory can be accessed through the Bit Line/Word Line address decoder.

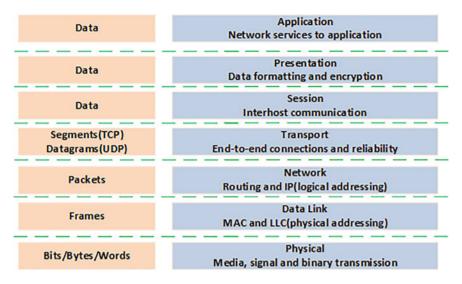

Bitstream is more than the bits to configure an FPGA, it also contains certain human-readable fields (meta) to describe those bits and an assembly-like instruction set (command) to guide the FPGA configuration process. Packet-Frame-Bit hierarchy, borrowed from networking OSI(Open Systems Interconnection) model (Fig. 2.7), is used for the configuration data:

a. Packet

Packet is the basic unit of communication between a source and a destination in a network. In the OSI model, packets are data units within the network layer.

b. Frame

Just like packets, frames are small parts of a message in the network. The main difference between a packet and a frame is the association with the OSI layers—frames are data units within the data link layer.

Fig. 2.7 Communication data in OSI model

c. Bit/Byte/Word

Configuration memory stores the data in bits at the bottom level. Each bit stores the value either 0 or 1. Each byte has 8 bits, and each word can has a different length in different systems (such as 8/16/32 bits). Registers are used to store a small piece of information (byte/word) while doing the calculations or processing the data. It is helpful to improve the performance of the system while doing the calculation or processing.

As discussed above, FPGA physical bit structure has a general hierarchy in (Fig. 2.8).

After the logical and physical structure are proper defined, the logical–physical address correlation for each bit is then established (Fig. 2.9).

## 2.2.2 Metric Class

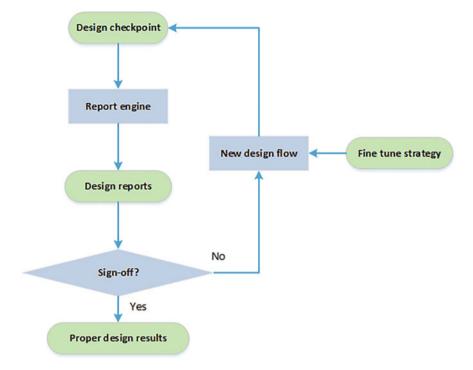

There are several metrics that must be concerned during the FPGA design process, and PPA (Power/Performance (Timing)/Area) is the most critical ones among them. In order to monitor these metrics accurately and sign off effectively, analysis is a conventional activity that every EDA system cannot get around. There are two ways to do the analysis: measurement and estimation.

Measurement can only be carried out after the FPGA chip is configured and ready to work. It is essentially a testing procedure that could achieve the most accurate analysis results, at the price of extra efforts such as time-consuming full chip design, manufacturing and external test instrumentation setups.

Fig. 2.8 FPGA device configuration bit structure level (physical)

Fig. 2.9 FPGA device configuration bit correlation

Estimation, on the other hand, can be performed before the chip design is complete or even at the very early design stage. Models are used to approximate the result, which makes estimation a less costly and fairly efficient alternative to the measurement solution.

For FPGA, there are estimations and measurements at different stages to ensure the design objectives are met (Fig. 2.10). In terms of EDA part, we only discuss the PPA models used by the estimation tasks here.

Metric models are software-based representation of the physical parameters in the FPGA. There are different statuses for metric models in the FPGA design cycle: advance, preliminary, and final. Advance models are typically available soon after the device design specifications are frozen and may change as silicon characterization

| FPGA design<br>milestone      | Initial<br>Layout | Tape            |                                              | Silicon<br>iamples                              | Volume<br>Production | User's<br>Application Design |

|-------------------------------|-------------------|-----------------|----------------------------------------------|-------------------------------------------------|----------------------|------------------------------|

| FPGA metric mode<br>available |                   | nce<br>ic model | Preliminary<br>(Post-layout)<br>metric model | Preliminary<br>(Silicon spot-ch<br>metric model | ecked)               | Final metric model           |

Fig. 2.10 FPGA metric models during the development life cycle

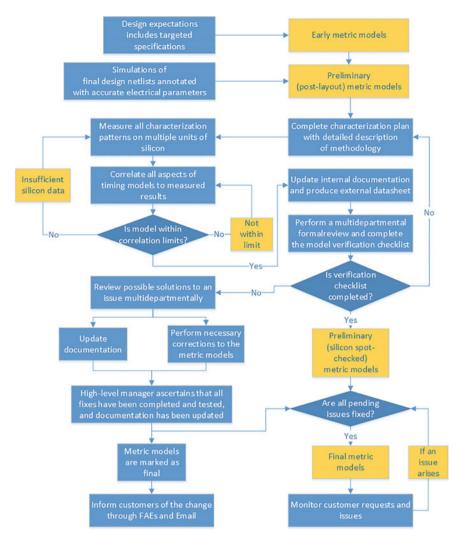

data becomes available. Preliminary models are based on early production silicon and all the units in the device are characterized. Final models correlate to production devices with thousands of designs and are not expected to change. Besides, metric models can be constructed at different abstract levels (such as transistor-level, switchlevel, gate-level, register transfer-level, high-level, etc.). Higher abstractions allow for quicker estimations, but with reduced accuracy. For large-scale FPGAs, estimations only at gate-level or lower could guarantee the sufficient accuracy, however, running at bottom transistor-level will also make calculation time intolerable. The generation of FPGA metric model is also a complicated process (Fig. 2.11) is a typical flow from Intel.

Except for how these metric models are represented in the FPGA architecture file, another important issue, which will be detailed in the following chapters— [Part. III], is how these models are properly built. Among the best practices to build these metric models, simulation/layout-based methods offer the best accuracy, while equation-based methods trade it off with efficiency (thus mostly used during architecture exploration). The main problem with power/timing model for FPGAs is that the power/timing depends on inputs and configuration bits which maintain circuit's behavior, temperature, process, voltage, etc.

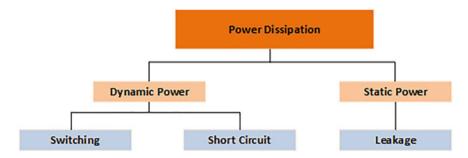

1. Power Model

Power model is prerequisite for power analysis and power-aware EDA engines [7].

a. Equation-based

In equation-based methods, power model is build by analytical calculations via predefined equations [8, 9].

b. Simulation-based

In simulation-based methods, as its name suggests, power model is obtained by simulations. The information in the model (including current and voltage values, capacitance, etc.) is different depending on the abstraction level of the simulator. SPICE is the most used transistor-level simulator [10].

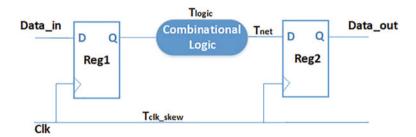

#### 2. Timing Model

Timing model is essential for timing analysis and timing-driven EDA engines.

a. Equation-based

In equation-based methods, the Elmore delay is the most frequently employed during architecture exploration [11-15].

Fig. 2.11 Typical flow of FPGA metric models generation [6]

b. Simulation-based

In industry, circuit simulator is used to get the final timing metrics. The circuit simulator (such as SPICE) extracts all electrical data, such as capacitance and resistance, and all nonlinear and linear components, to determine the expected delays.

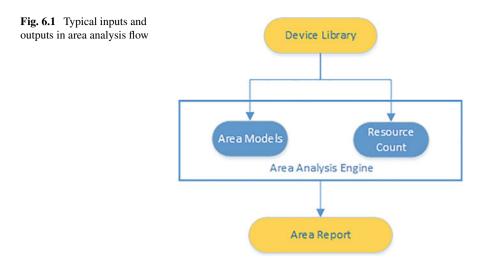

3. Area Model

Just like ASIC design, chip area is a metric that must be concerned. Advanced process nodes can shrink the area dramatically, more specific, parameters such