**Transactions on Computer Systems and Networks**

Saurabh Mani Tripathi Francisco M. Gonzalez-Longatt *Editors*

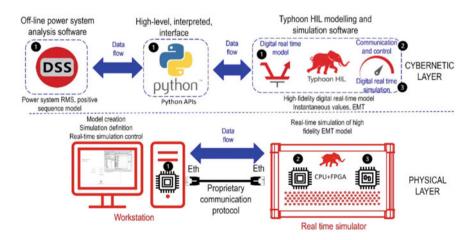

Real-Time Simulation and Hardware-in-the-Loop Testing Using Typhoon HIL

# **Transactions on Computer Systems and Networks**

#### Series Editor

Amlan Chakrabarti, Director and Professor, A. K. Choudhury School of Information Technology, Kolkata, West Bengal, India Transactions on Computer Systems and Networks is a unique series that aims to capture advances in evolution of computer hardware and software systems and progress in computer networks. Computing Systems in present world span from miniature IoT nodes and embedded computing systems to large-scale cloud infrastructures, which necessitates developing systems architecture, storage infrastructure and process management to work at various scales. Present day networking technologies provide pervasive global coverage on a scale and enable multitude of transformative technologies. The new landscape of computing comprises of self-aware autonomous systems, which are built upon a software-hardware collaborative framework. These systems are designed to execute critical and non-critical tasks involving a variety of processing resources like multi-core CPUs, reconfigurable hardware, GPUs and TPUs which are managed through virtualisation, real-time process management and fault-tolerance. While AI, Machine Learning and Deep Learning tasks are predominantly increasing in the application space the computing system research aim towards efficient means of data processing, memory management, real-time task scheduling, scalable, secured and energy aware computing. The paradigm of computer networks also extends it support to this evolving application scenario through various advanced protocols, architectures and services. This series aims to present leading works on advances in theory, design, behaviour and applications in computing systems and networks. The Series accepts research monographs, introductory and advanced textbooks, professional books, reference works, and select conference proceedings.

Saurabh Mani Tripathi · Francisco M. Gonzalez-Longatt Editors

# Real-Time Simulation and Hardware-in-the-Loop Testing Using Typhoon HIL

*Editors* Saurabh Mani Tripathi Department of Electrical Engineering Kamla Nehru Institute of Technology Sultanpur, India

Francisco M. Gonzalez-Longatt Department of Engineering Centre for Smart Grid University of Exeter Exeter, UK

Department of Electrical Engineering, Information Technology and Cybernetics University of South-Eastern Norway Notodden, Norway

ISSN 2730-7484

ISSN 2730-7492 (electronic)

Transactions on Computer Systems and Networks

ISBN 978-981-99-0223-1

ISBN 978-981-99-0224-8 (eBook)

https://doi.org/10.1007/978-981-99-0224-8

ISBN 978-981-99-0224-8

ISBN 978-981-99-0224-8

© The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2023

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

## Foreword

The story of Typhoon HIL started in 2008, when motivated by a real-life challenge to completely change the way power electronics control systems are designed and tested, Typhoon HIL's founding team embarked on a quest to bring *Hardware in the Loop* (HIL) testing for power electronics and motor drives to reality. A couple of years later, we succeeded in demonstrating the first of kind 1  $\mu$ s time step real-time HIL simulation for power electronics that set the record for the smallest time step HIL simulation by two orders of magnitude. More importantly, we proved that ultra-high fidelity HIL for power electronics is possible, and for the first time, there was a clear path towards a fully integrated *model-based design workflow* where design, testing, and system integration can be done using the same models, from start to finish, all in one unified workflow.

At the time there were many good off-line simulation software for the design and simulation of power converters. Also, there were good solutions for converter testing and validation. But the gap was HIL testing to connect model-based design with model-based testing. Indeed, it was HIL that unlocked wider acceptance of integrated and unified *Model-Based Engineering* (MBE) as the key process for the design, testing, and lifecycle maintenance of power electronics control systems. And as with any new innovation that enables radical departure from a widely accepted practice of the time, it took more than a decade until HIL became adopted as a cornerstone of control design and testing thus replacing high-power lab testing of controllers.

From day one, our vision was to develop integrated and easy-to-use MBE tools to empower control engineers developing power electronics controls, to elevate the design processes, empower teams to collaborate, thus unleashing creative energy, and radically accelerating the pace of innovation. On the one hand, we understood the importance of power electronics, and on the other hand, we were unsatisfied with the status quo in terms of design and testing tools. This nexus was further amplified by the imminent need to accelerate the transformation of our civilization's energy systems toward a 100% clean and sustainable energy future and the need to have better

testing, design and integration tools. Indeed, in the past 10+ years, power electronics converters and their applications have been driving renewable integration, energy storage proliferation, and electrification of transportation.

This first issue of the *Real-time Simulation and Hardware in the Loop Testing* serves as an impressive demonstration of both the breadth and depth of power electronics applications with particular emphasis on control design, testing, and system-level integration challenges. We believe that this book, with in-depth treatment of grid forming inverter control design, advanced protection concepts, interoperability challenges between protection and DERs, and microgrid and distribution system controls, will empower and motivate the community to push the boundaries of control design and optimization both in terms of performance, robustness, and interoperability. Furthermore, it paves the way for further exploration of machine learning and AI applications to the problem of control and coordination of the future truly cyber-physical grid.

We want to express our deepest gratitude and appreciation to all the authors for their deep, technically rigorous, and original contributions. We have been deeply inspired and genuinely amazed by the authors' creative ways of using Hardware in the Loop and real-time simulation. This has energized us to continue improving our software and hardware tools and to continue co-creating with authors and the research and development community at large.

This book will not only help the users and power electronics and power systems communities, but it will also motivate all the developers of *Model-Based Engineering* (MBE) tools for power to continue improving their solutions and processes that will further accelerate our civilization's transition to a clean energy future.

September 2022

Ivan Celanovic Co-founder and President Typhoon HIL, Inc Newton, MA, USA

## Preface

Real-time simulation is a concept that refers to the execution of a computer-based model of a physical system by matching simulation time with actual "wall clock" time to replicate the fundamental behaviour of a physical system. Nowadays, it is increasingly used by industry and academia. Real-time simulation tools have become the most important tool to validate conventional/proven and unconventional/unproven design approaches for complex energy systems. For the purpose of de-risking equipment in complex electrical systems and to provide evidence of proper functionality under a wide range of realistic dynamic conditions—safely, repeatedly and economically; the newer design approaches need to be tested stringently through in-depth simulation before deployment at large scale.

Hardware-in-the-loop (HIL) testing framework is an approach to combining realtime simulation and hardware experimentation using signal interfaces between hardware devices and real-time computational systems, allowing rigorous testing of new design approaches for electrical systems at the required complexity. In the HIL test framework, the actual controllers, as devices under test, are usually connected in a closed loop with the simulated power stage running on the real-time simulator.

The purpose of real-time simulation/HIL testing is to provide unbeatable evidence of acceptable electrical system performance (during normal, abnormal and degraded conditions) in accordance with the given functional requirements. Typhoon HIL has a successful trajectory by developing a powerful framework in the rapidly growing field of ultra-high-fidelity controller-hardware-in-the-loop (C-HIL) simulations for power electronics, micro-grids and distribution networks.

This book is an edited collection that explores the fundamental concepts of realtime simulation/hardware-in-the-loop testing using "Typhoon HIL" for complex electrical systems. This book integrates the coverage of underlying theory and acclaimed methodological approaches as well as high-value applications of realtime simulation and HIL testing—all from the perspectives of eminent researchers around the globe utilising Typhoon HIL.

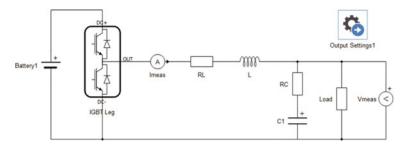

Chapter 1 highlights the critical technical aspects behind the Typhoon HIL toolchain. In addition, an example of a simple C-HIL test setup featuring an actual controller has been demonstrated to illustrate how a simple test environment can be

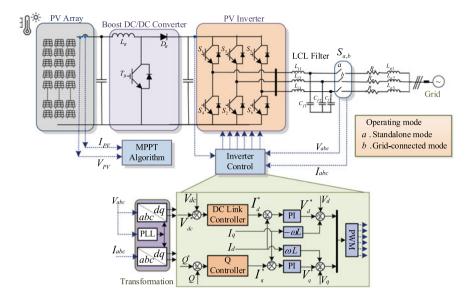

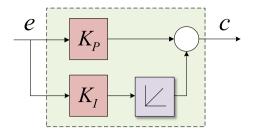

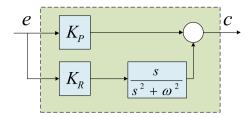

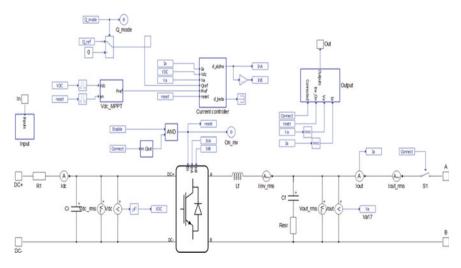

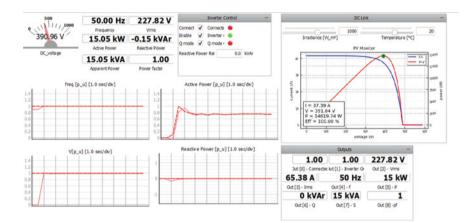

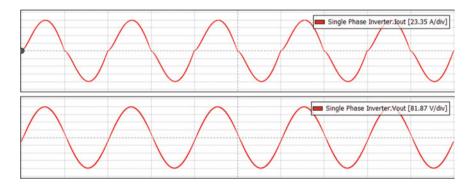

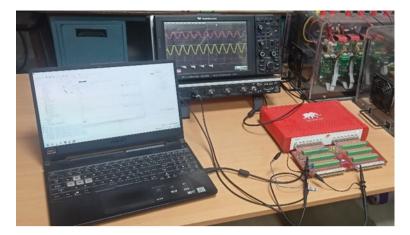

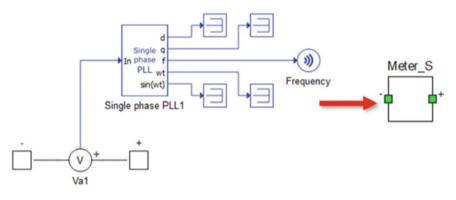

quickly built and parameterised. Chapter 2 throws light upon the importance of power electronic converters, their modelling and control functionalities in grid-connected systems. A case study for a single-phase grid-connected PV inverter simulation using the Typhoon HIL 402 device is also presented.

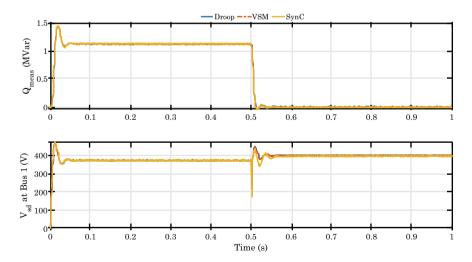

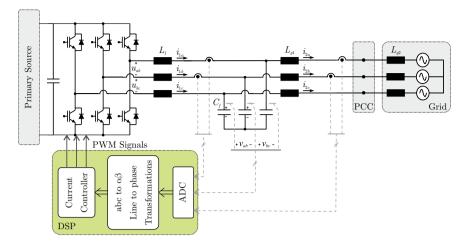

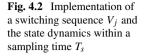

Chapter 3 presents grid forming control techniques for power electronic converters as a solution to low rotational inertia systems; the controllers have been implemented and tested using the modelling and real-time simulation framework of Typhoon HIL. Chapter 4 presents various model predictive control (MPC) strategies for grid-connected converters and describes their implementation, testing and validation using the Typhoon HIL platform.

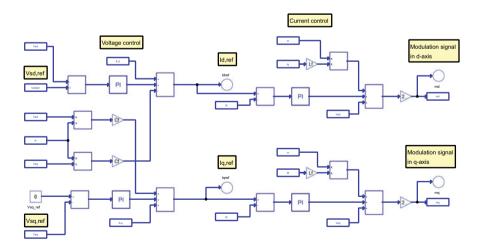

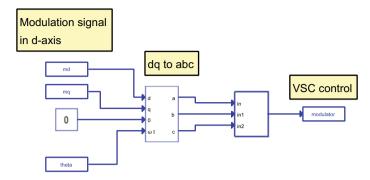

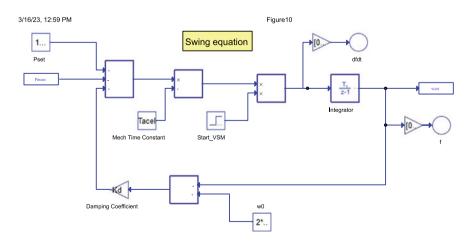

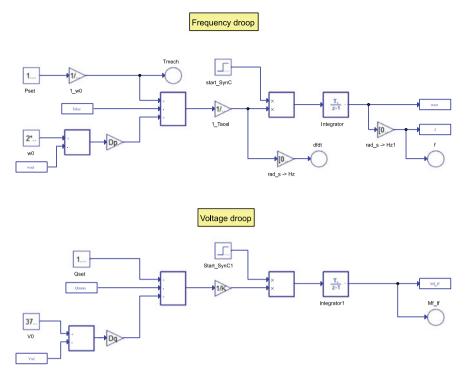

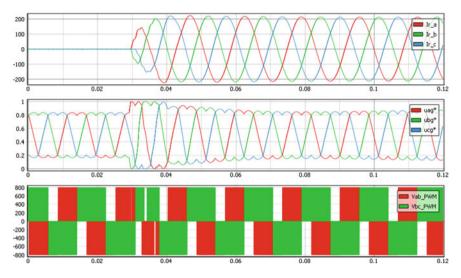

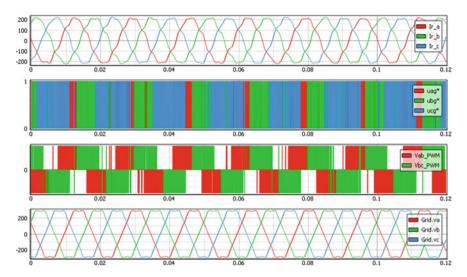

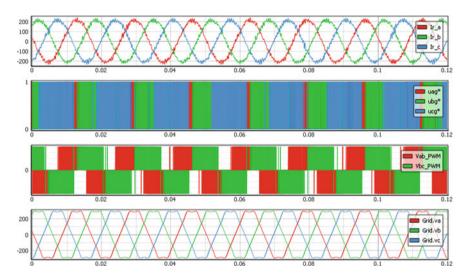

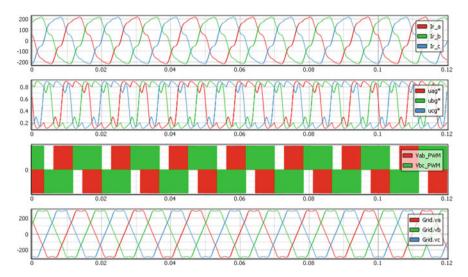

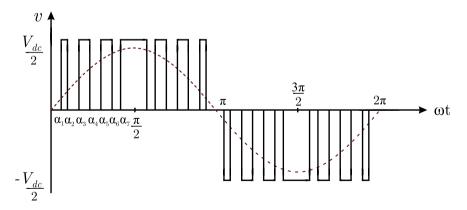

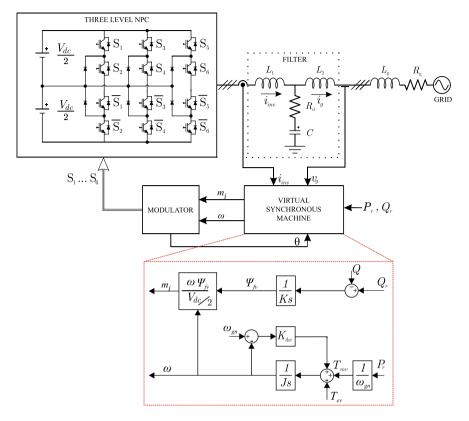

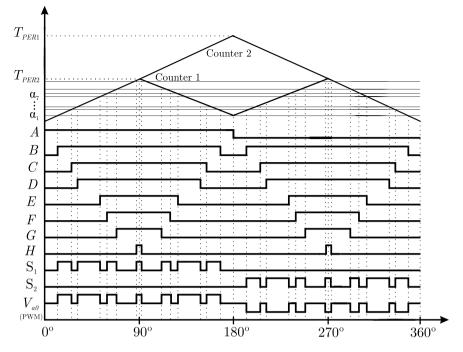

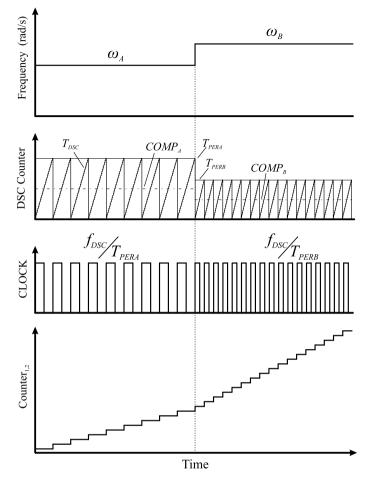

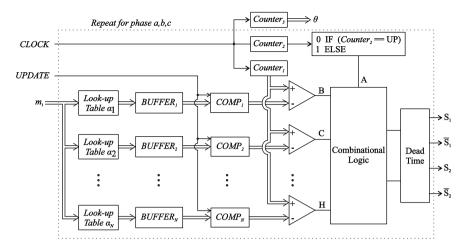

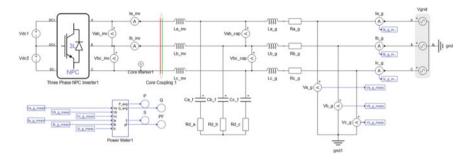

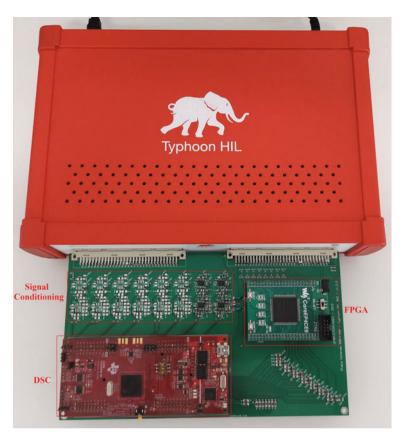

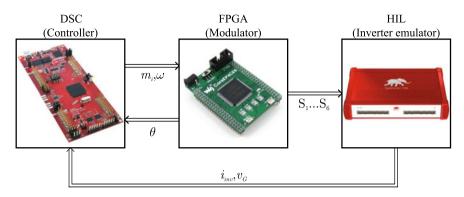

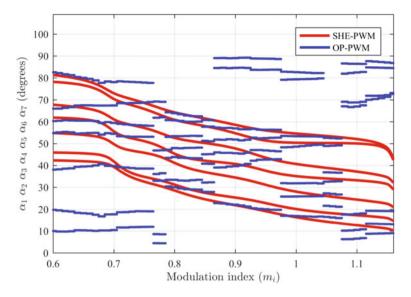

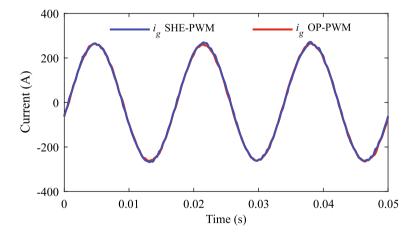

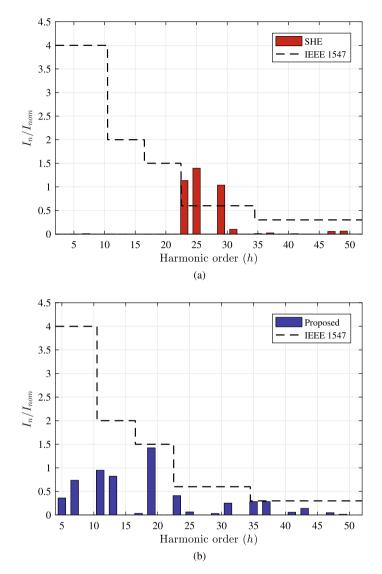

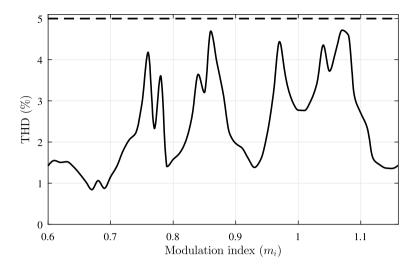

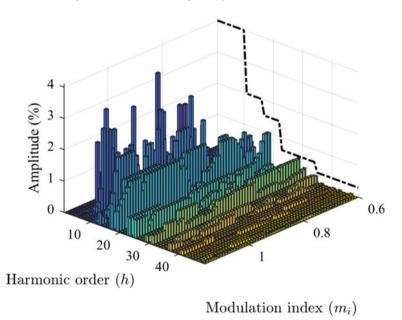

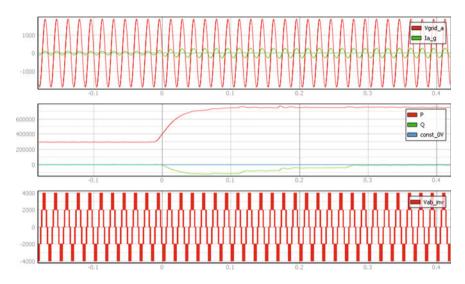

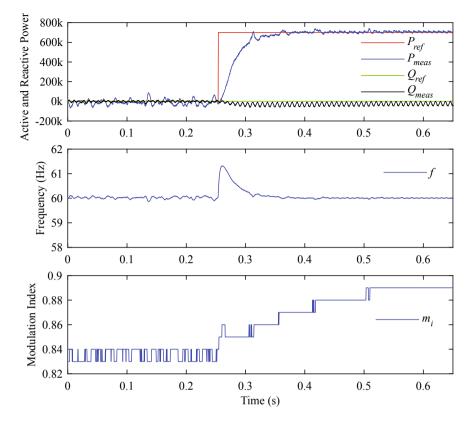

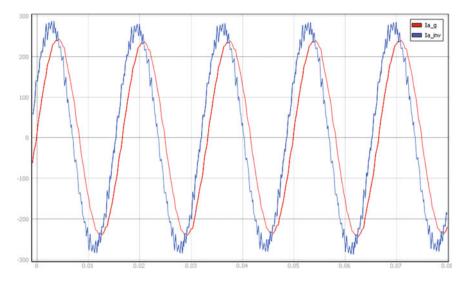

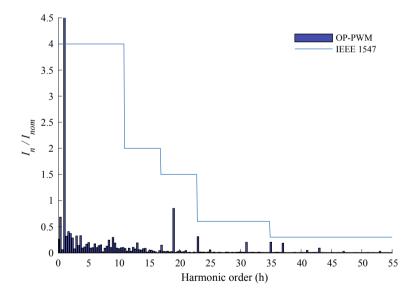

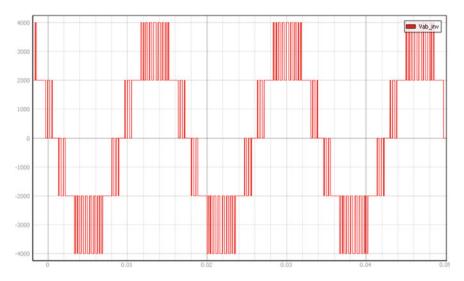

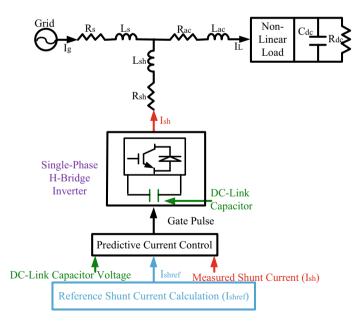

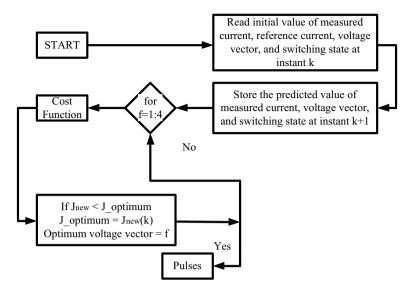

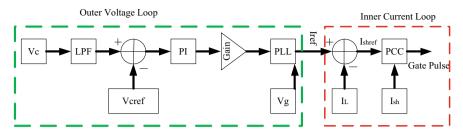

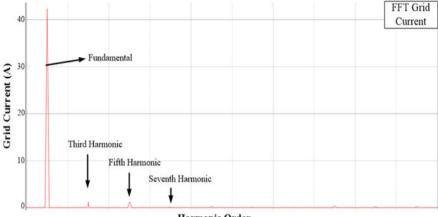

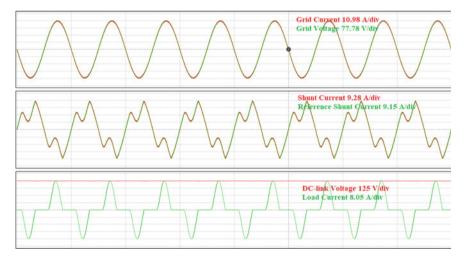

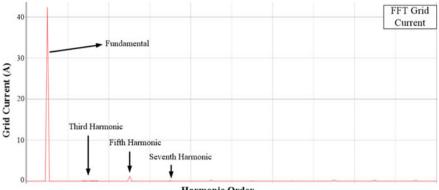

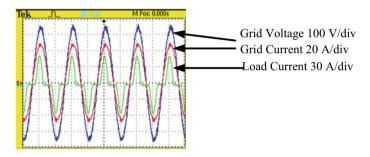

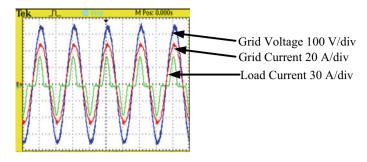

An optimal programmed pulse width modulation (PWM) strategy coordinated with the virtual synchronous machine (VSM) concept for grid-connected multilevel converters in accordance with the current harmonic content limits of the IEEE 1547 standard has been proposed in Chap. 5. In addition, the real-time operation of a grid-connected three-phase neutral point clamped converter was carried out in Typhoon HIL 402 to demonstrate the performance of the proposed approach. A non-linear predictive current control scheme for a single-phase shunt active power filter (SAPF) using selective harmonic compensation has been presented in Chap. 6. The proposed non-linear predictive current control scheme has been implemented and tested using the Typhoon HIL 402 device.

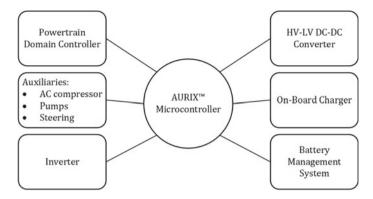

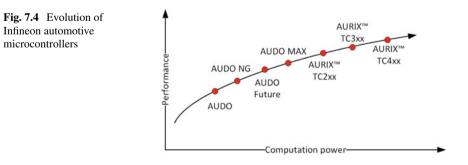

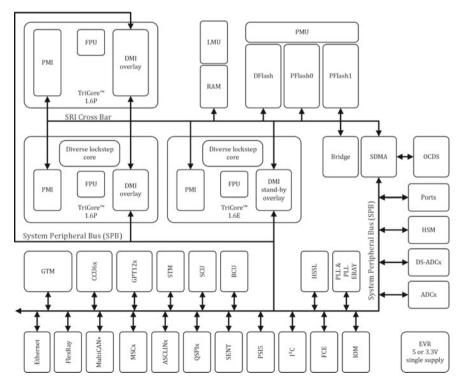

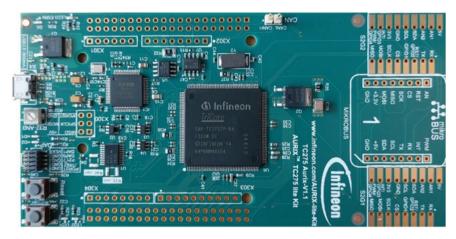

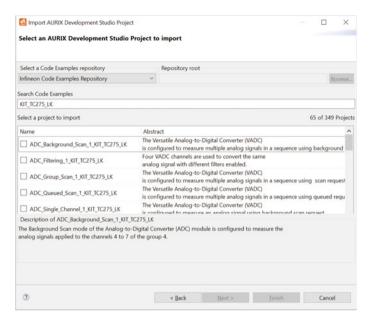

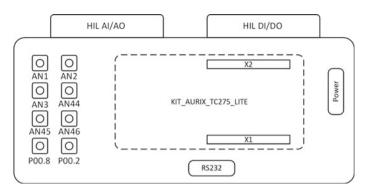

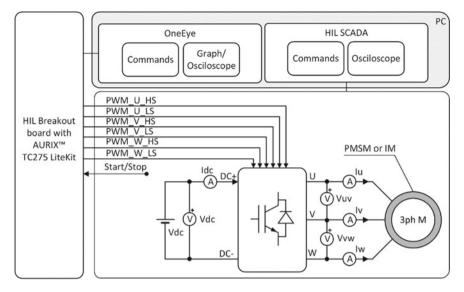

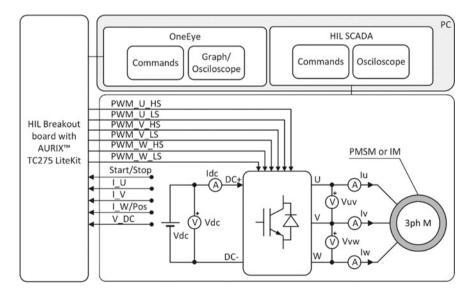

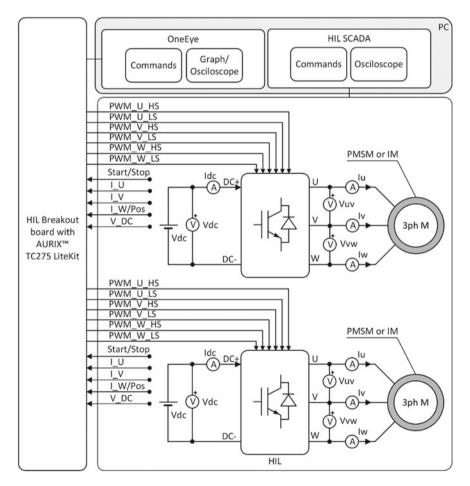

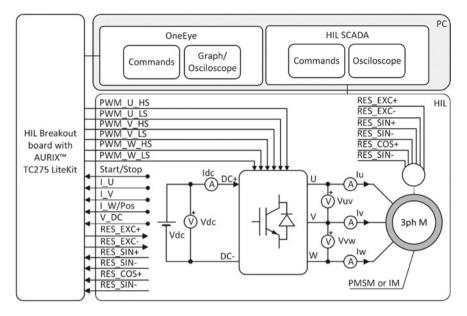

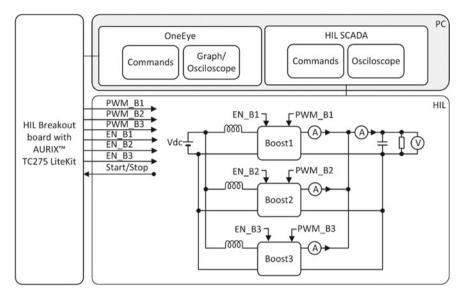

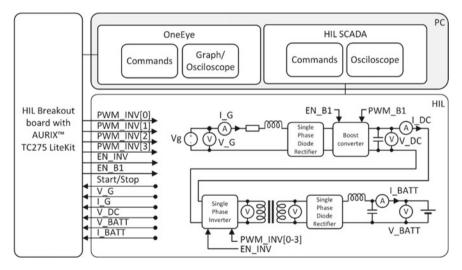

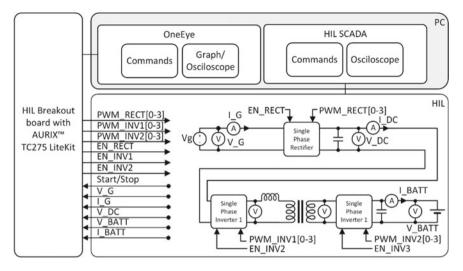

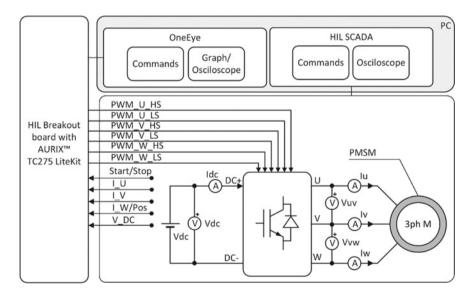

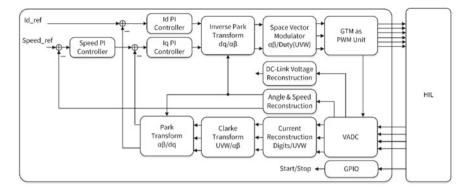

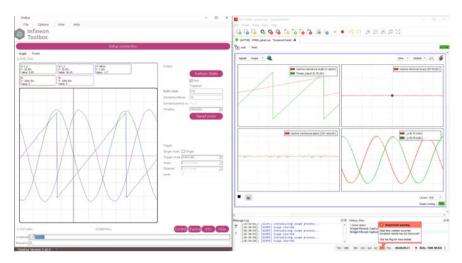

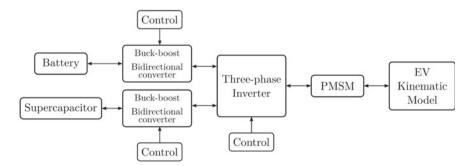

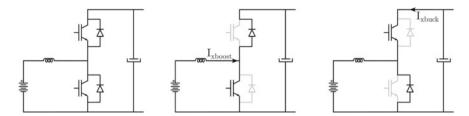

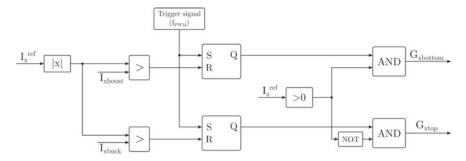

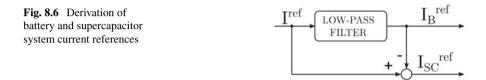

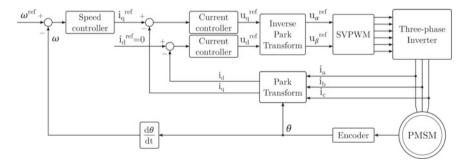

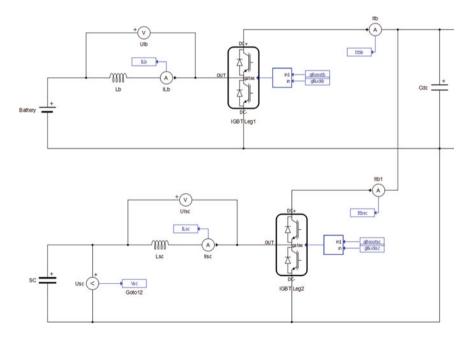

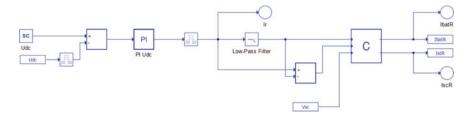

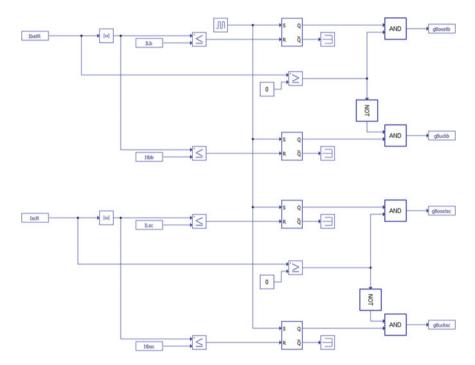

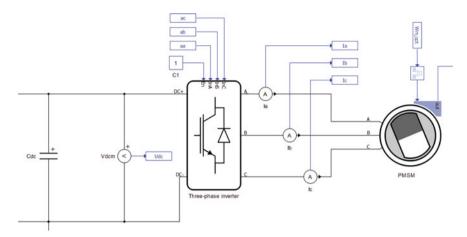

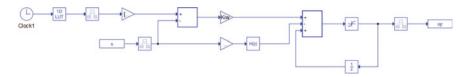

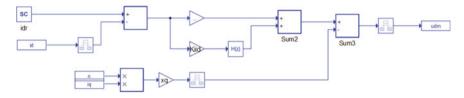

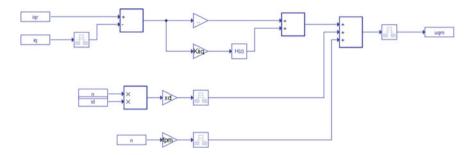

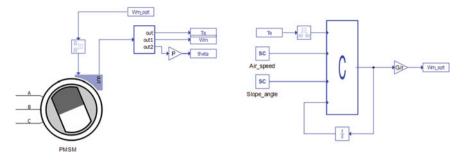

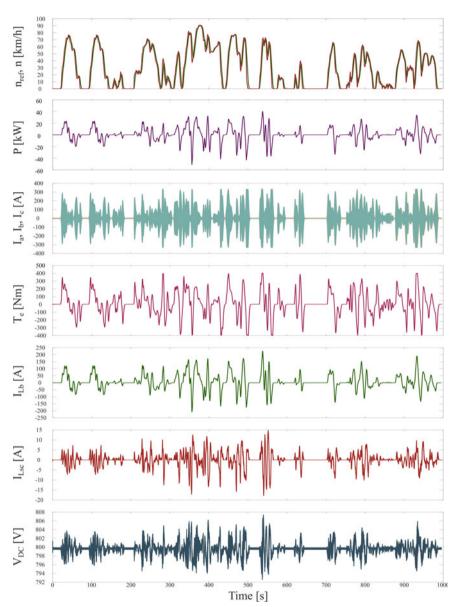

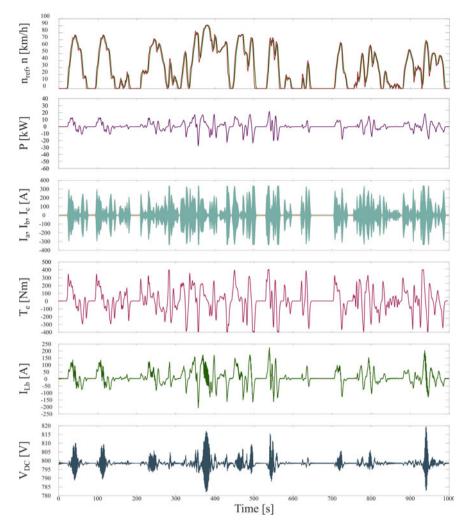

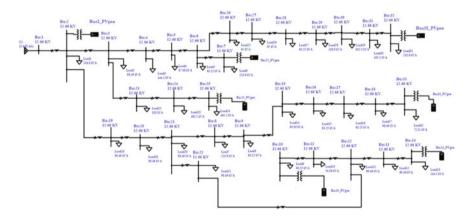

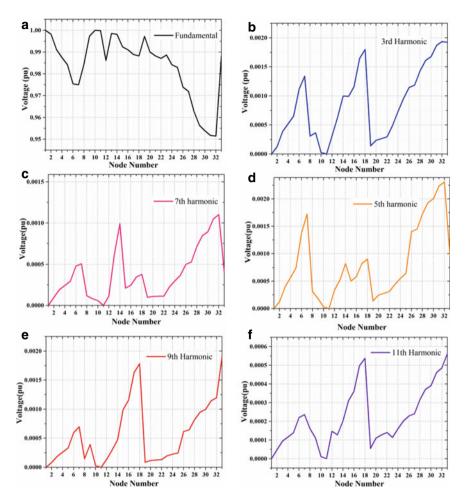

A practical experimental setup for the development and controller testing of xEV applications has been proposed in Chap. 7 by demonstrating a C-HIL setup for field-oriented control (FOC) of a permanent magnet synchronous motor (PMSM) using the Typhoon HIL 602+ simulator and AURIX<sup>TM</sup> microcontroller. Chapter 8 provides a theoretical and conceptual introduction to electric vehicle digital twins that can be used as a platform for research and development of electric vehicle pertinent technologies. In Chap. 9, the authors derive large and small signal models for primary controllers and demonstrate the effect of primary controller parameters on steady-state and transient behaviour by showing the performance of time domain simulations on the HIL. In Chap. 10, the authors have used Typhoon HIL real-time simulation platform for modelling a reconfigured IEEE-33 bus distribution system to assess the effect of diverse harmonic order frequency on network parameters and its subsequent impact on the hosting capacity of the network.

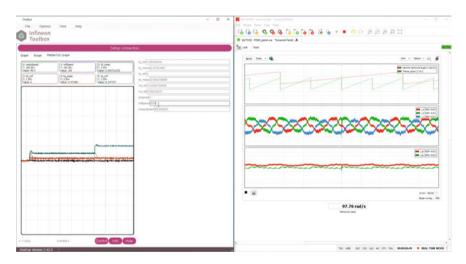

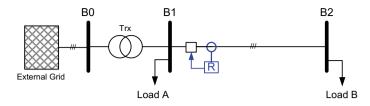

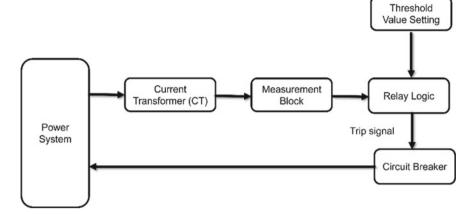

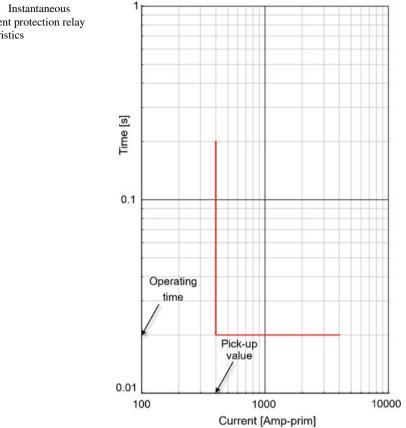

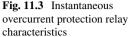

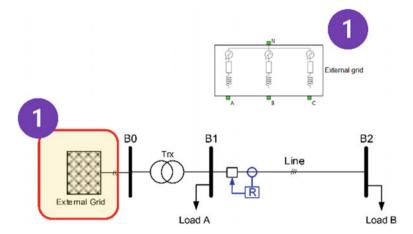

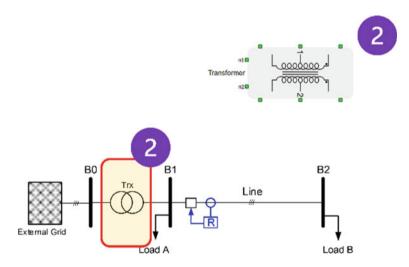

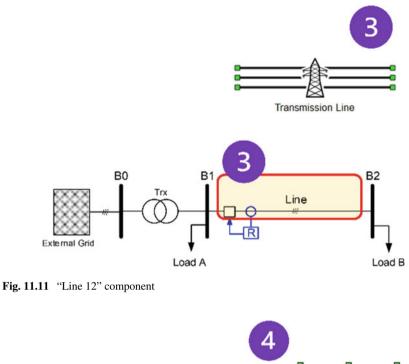

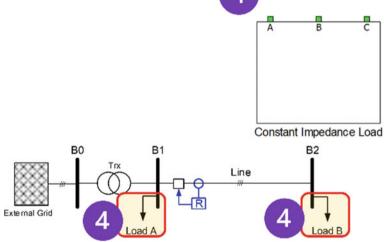

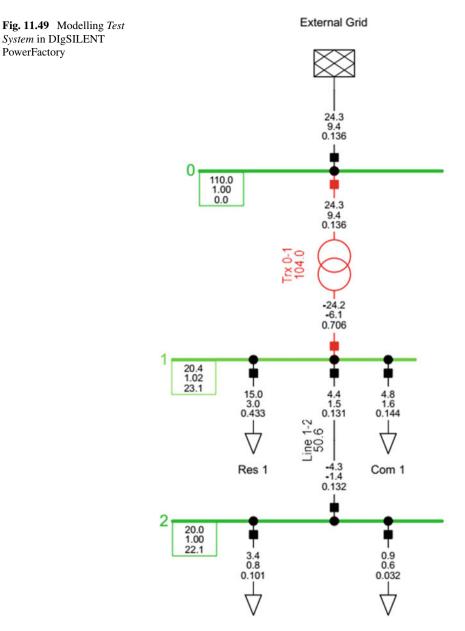

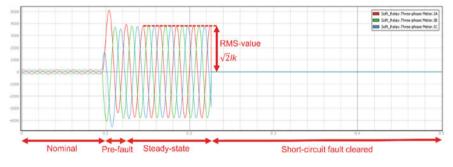

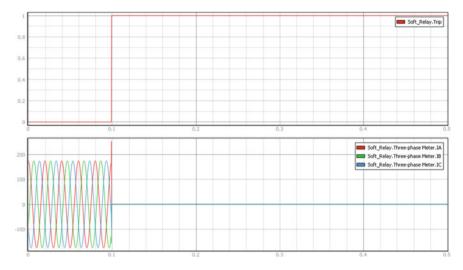

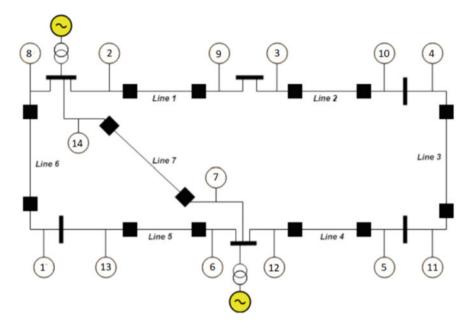

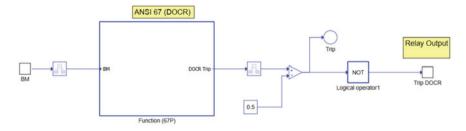

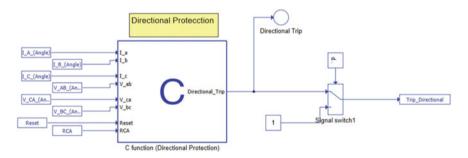

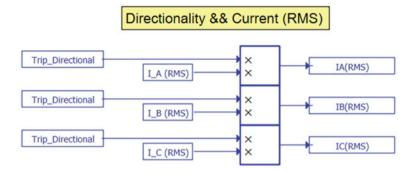

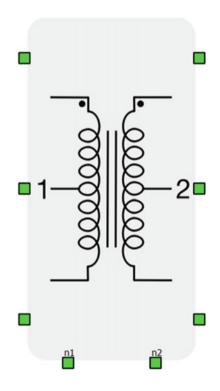

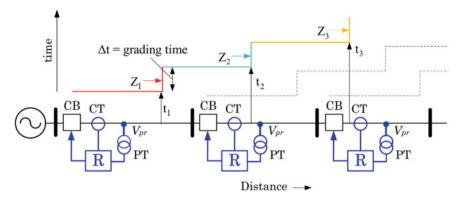

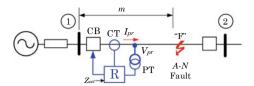

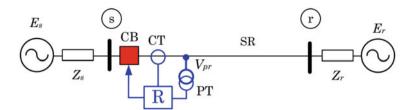

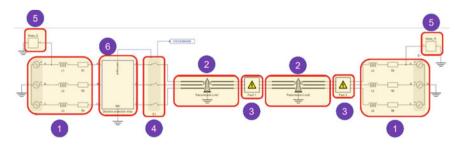

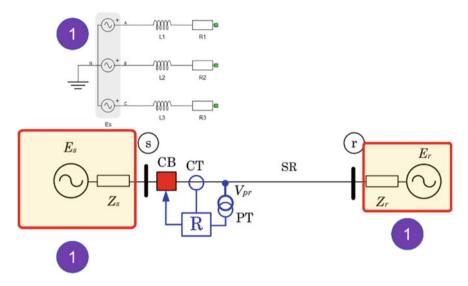

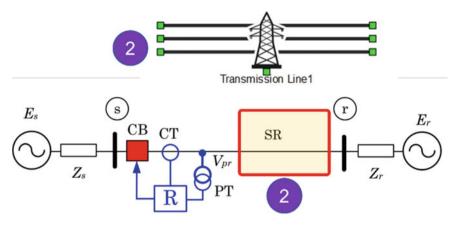

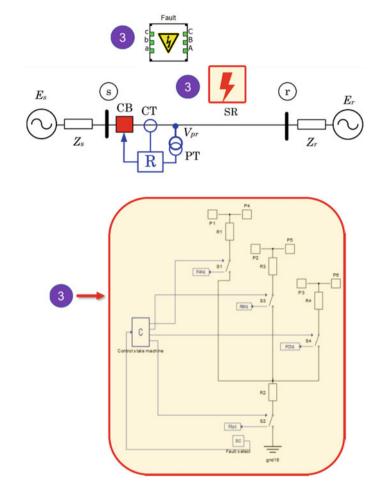

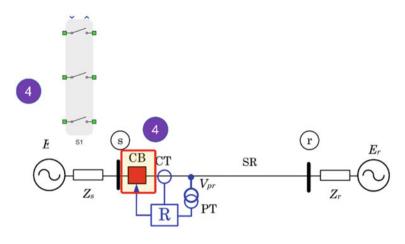

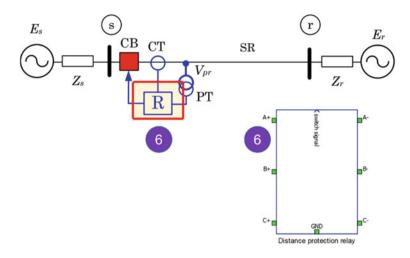

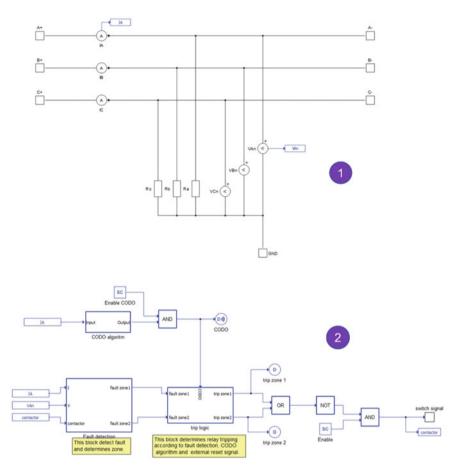

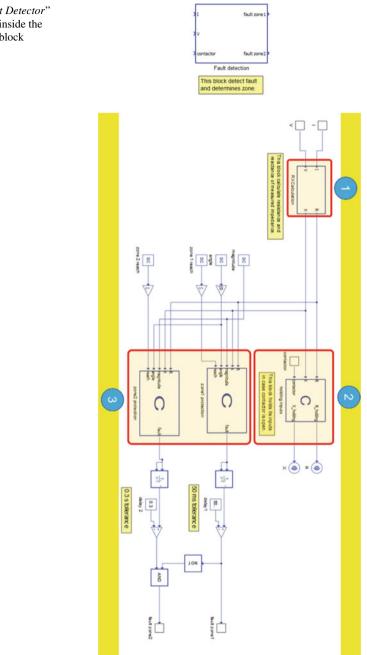

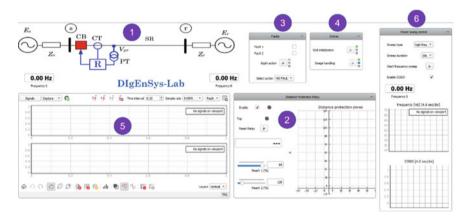

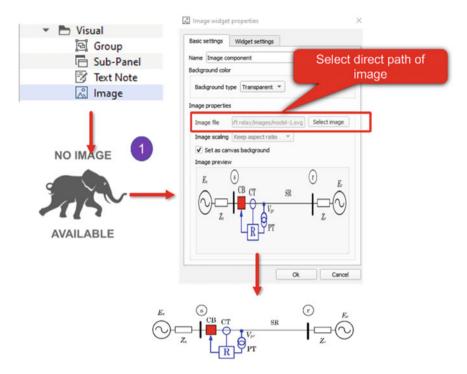

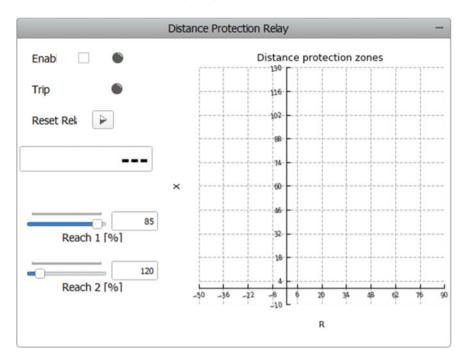

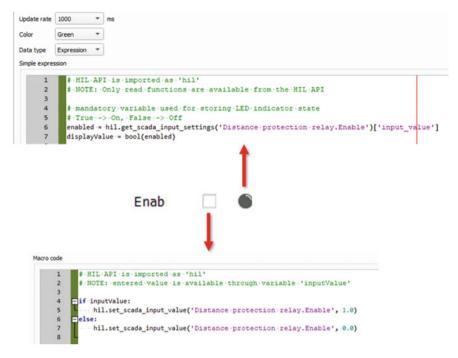

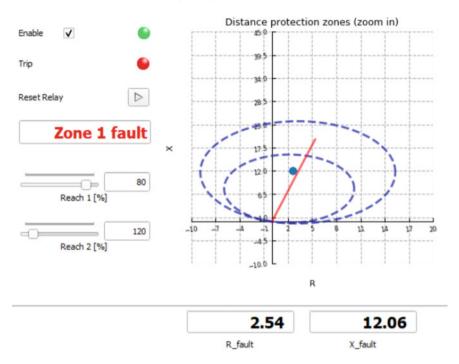

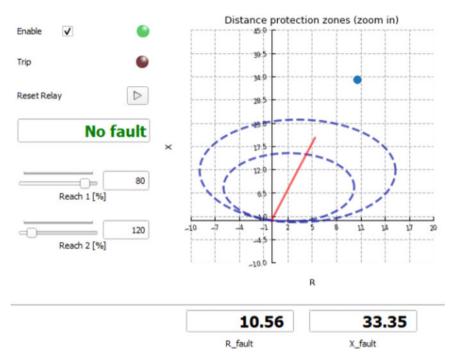

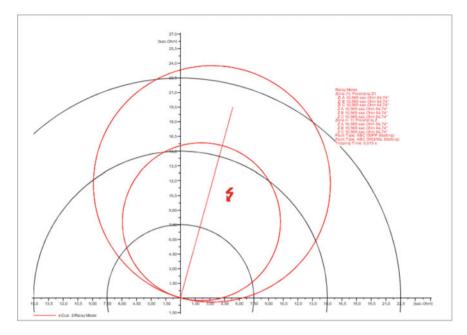

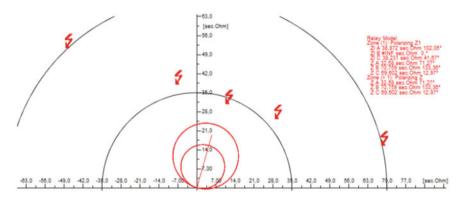

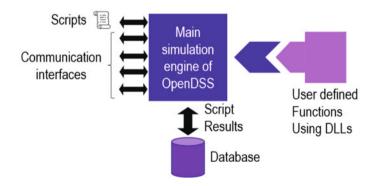

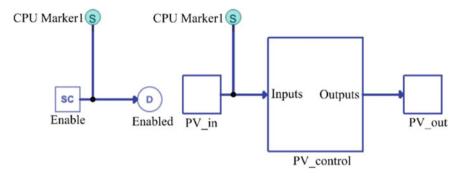

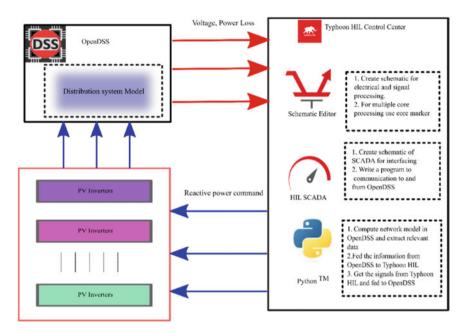

The authors of Chap. 11 systematically introduce modelling and simulation for testing purposes of non-directional over-current protection relays in Virtual HIL (VHIL) to help power engineers evaluate protective relay settings under more realistic conditions. In Chap. 12, the 8-bus transmission system is implemented under a soft real-time simulation platform that allows the determination of the sequence of operation, fault current detection capability and operating time of directional overcurrent relays under solid three-phase to ground fault conditions. In Chap. 13, a VHIL platform for line protection with distance protection relay has been developed and tested using a real-time HIL simulation validated by theory-based calculation and DIgSILENT PowerFactory software with three-phase and single-lineto-ground short-circuit fault cases. Finally, Chap. 14 proposes and demonstrates a cyber-physical co-simulation framework between Typhoon HIL and OpenDSS to solve the problem of modelling complex distribution networks.

The editors hope this book will cater to understanding and familiarity with the real-time simulation of complex electrical systems, specifically focusing on HIL modelling, simulation and testing. It will also make the readers conversant for real-time validation of the unconventional/unproven design approaches for power systems and power electronics applications using "Typhoon HIL".

Sultanpur, India Exeter, UK/Notodden, Norway Saurabh Mani Tripathi Francisco M. Gonzalez-Longatt

**Acknowledgments** The editors are grateful to all the authors for their valuable contribution to this edited book. The editors also thank all the reviewers who have generously given their time to review the chapter manuscripts. The editors thank the CEO and co-founder of Typhoon HIL, GmbH, for granting the necessary permission, and the staff of Springer Nature for their continued support throughout the press production process of this edited book.

## Contents

| 1 | Introduction to Typhoon HIL: Technology, Functionalities,and ApplicationsCaio R. D. Osório, Adrien Genic, and Sergio Costa                                                                                                                             | 1   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Control of Grid-Connected Inverter Azra Malik and Ahteshamul Haque                                                                                                                                                                                     | 29  |

| 3 | Grid-Forming Converter Control Techniques Implementation<br>in Typhoon HIL<br>Jose Miguel Riquelme-Dominguez, Hugo Mendonça,<br>and Francisco Gonzalez-Longatt                                                                                         | 51  |

| 4 | Model Predictive Control for Grid-Connected Converters<br>with Typhoon HIL<br>Daniel M. Lima, Dimas A. Schuetz, Felipe B. Grigoletto,<br>Fernanda Carnielutti, Humberto Pinheiro, Luiz A. Maccari Jr.,<br>Vinícius F. Montagner, and Caio R. D. Osório | 75  |

| 5 | Grid-Connected Multilevel Converter with Optimal<br>Programmed PWM and Virtual Synchronous Machine<br>Felipe B. Grigoletto, Dimas A. Schuetz, Jonas R. Tibola,<br>Fernanda Carnielutti, and Humberto Pinheiro                                          | 117 |

| 6 | Selective Harmonic Compensation in Active Power FilterUsing Nonlinear Predictive Current Control MethodSandeep Ojha and Rajesh Gupta                                                                                                                   | 145 |

| 7 | Development of Electric Vehicles Applications UsingAURIX™ Microcontroller and Typhoon HILIvan Todorović, Ivana Isakov, and Marko Gecic                                                                                                                 | 157 |

| 8 | Electric Vehicles Digital Twinning Using x-HIL Platforms<br>Ivan Todorović and Ivana Isakov                                                                                                                                                            | 187 |

| 9  | Microgrid Primary Controller Performance Characterization<br>Alexandre T. Pereira, Humberto Pinheiro, Márcio Stefanello,<br>Jorge R. Massing, Henrique Magnago, and Fernanda Carnielutti                         | 211 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10 | Effect of Diverse Harmonic Order Frequencies on Dynamic<br>PV Hosting Capacity Assessment in Active Distribution<br>Network: A Typhoon HIL Based Approach<br>Swati Kumari, Sourav Kumar Sahu, and Debomita Ghosh | 255 |

| 11 | Non-directional Overcurrent Protection Relay Testing UsingVirtual Hardware-in-the-Loop DeviceLe Nam Hai Pham, Raju Wagle, Francisco Gonzalez-Longatt,and Martha Nohemi Acosta Montalvo                           | 283 |

| 12 | Directional Overcurrent Relay Protection System<br>Implementation on 8-bus System Using Typhoon HIL<br>Juan David Hernández Santafé, Felipe Antonio Gómez Olaya,<br>and Paulo Manuel De Oliveira De Jesús        | 339 |

| 13 | Distance Protection Relay Testing Using VirtualHardware-in-the-Loop DeviceLe Nam Hai Pham and Francisco Gonzalez-Longatt                                                                                         | 379 |

| 14 | Cyber-Physical Co-simulation Framework Between TyphonHIL and OpenDSS for Real-Time ApplicationsRaju Wagle, Pawan Sharma, Mohammad Amin,and Francisco Gonzalez-Longatt                                            | 425 |

xii

# **Editors and Contributors**

#### **About the Editors**

Saurabh Mani Tripathi is currently an Associate Professor in electrical engineering and Founder & Coordinator of the Power & Energy Research Centre (Centre of Excellence) at Kamla Nehru Institute of Technology, Sultanpur, India. He is a recipient of the prestigious "IEI Young Engineers Award 2018–19" presented by the Institution of Engineers (India). He is also a recipient of the "Best Teachers Award 2020" presented by Dr. A.P.J. Abdul Kalam Technical University, Lucknow, India. He authored and edited several books and has published numerous research papers in various journals and conferences as well. He is a member of several professional societies such as the Institution of Engineers (India) and the International Association of Engineers. He is a Life Member of the Indian Society for Technical Education. His areas of current interest include renewable energy systems, electrical drives, real-time simulation, and hardware-in-the-loop testing.

**Francisco M. Gonzalez-Longatt** is currently a Professor in Electrical Energy Systems at the Centre for Smart Grid, University of Exeter, Founder & Leader of the DIgEnSys-Lab (Digital Energy Systems Laboratory) at the University of South-Eastern Norway, Norway, where he is an honorary full professor in Electrical Power Systems. He has been involved in several industrial research projects and consultancy worldwide. In addition, he is the author/editor of numerous books (Spanish and English) and a member of the editorial board of several leading journals. His primary research interest is digital technologies as an enabler of net-zero energy systems and smart grids.

### Contributors

Mohammad Amin Department of Electric Power Engineering, NTNU, Trondheim, Norway

Fernanda Carnielutti Federal University of Santa Maria - UFSM, Santa Maria, Brazil

Sergio Costa Typhoon HIL, Novi Sad, Serbia

**Paulo Manuel De Oliveira De Jesús** Department of Electrical and Electronical Engineering, University of the Andes, South America, Colombia

Marko Gecic Infineon Technologies AG, Neubiberg, Germany

Adrien Genic Typhoon HIL, Novi Sad, Serbia

Debomita Ghosh Birla Institute of Technology, Mesra, Jharkhand, India

Francisco Gonzalez-Longatt University of South-Eastern Norway, Porsgrunn, Norway;

Centre of Smart Grid, University of Exeter, Exeter, UK

Felipe B. Grigoletto Federal University of Pampa - UNIPAMPA, Alegrete, RS, Brazil

**Rajesh Gupta** Electrical Engineering Department, Motilal Nehru National Institute of Technology Allahabad, Prayagraj, Uttar Pradesh, India

Ahteshamul Haque Advance Power Electronics Research Lab, Department of Electrical Engineering, Jamia Millia Islamia (A Central University), New Delhi, India

Ivana Isakov Faculty of Technical Sciences, University of Novi Sad, Novi Sad, Serbia

Swati Kumari Birla Institute of Technology, Mesra, Jharkhand, India

Daniel M. Lima Federal University of Santa Catarina - UFSC, Blumenau, Brazil

Luiz A. Maccari Jr. Federal University of Santa Catarina - UFSC, Blumenau, Brazil

Henrique Magnago UFSM, Santa Maria, Brazil

**Azra Malik** Advance Power Electronics Research Lab, Department of Electrical Engineering, Jamia Millia Islamia (A Central University), New Delhi, India

Jorge R. Massing UFSM, Santa Maria, Brazil

**Hugo Mendonça** Escuela Técnica Superior de Ingenieros Industriales, Universidad Politécnica de Madrid, Madrid, Spain

Vinícius F. Montagner Federal University of Santa Maria - UFSM, Santa Maria, Brazil

Martha Nohemi Acosta Montalvo University of South-Eastern Norway, Porsgrunn, Norway

Sandeep Ojha Electrical Engineering Department, Motilal Nehru National Institute of Technology Allahabad, Prayagraj, Uttar Pradesh, India

Felipe Antonio Gómez Olaya Department of Electrical and Electronical Engineering, University of the Andes, South America, Colombia

Caio R. D. Osório Typhoon HIL, Novi Sad, Serbia

Alexandre T. Pereira UFSM, Av. Roraima, Santa Maria, Brazil

Le Nam Hai Pham University of South-Eastern Norway, Porsgrunn, Norway

Humberto Pinheiro Federal University of Santa Maria - UFSM, Santa Maria, Brazil

**Jose Miguel Riquelme-Dominguez** Escuela Técnica Superior de Ingenieros Industriales, Universidad Politécnica de Madrid, Madrid, Spain

Sourav Kumar Sahu Birla Institute of Technology, Mesra, Jharkhand, India

Juan David Hernández Santafé Department of Electrical and Electronical Engineering, University of the Andes, South America, Colombia

Dimas A. Schuetz Federal University of Santa Maria - UFSM, Santa Maria, Brazil

Pawan Sharma Department of Electrical Engineering, UiT The Arctic University of Norway, Narvik, Norway

Márcio Stefanello UNIPAMPA, Av. Tiaraju, Alegrete, Brazil

Jonas R. Tibola Federal University of Santa Maria - UFSM, Santa Maria, Brazil

Ivan Todorović Faculty of Technical Sciences, University of Novi Sad, Novi Sad, Serbia

Raju Wagle Department of Electrical Engineering, UiT The Arctic University of Norway, Narvik, Norway

# Abbreviations

| ANN     | Artificial neural network                       |

|---------|-------------------------------------------------|

| ANSI    | American national standards institute           |

| APF     | Active power filter                             |

| API     | Application programming interface               |

| ATOM    | ARU-connected timer output module               |

| BA      | Bee algorithms                                  |

| BMS     | Battery management systems                      |

| CB-PWM  | Carrier-based pulse-width modulation            |

| CC      | Control code                                    |

| CCS-MPC | Continuous control set model predictive control |

| C-HIL   | Controller hardware-in-the-loop                 |

| CMIL    | Controller-model-in-the-loop                    |

| CPU     | Central processing unit                         |

| СТ      | Current transformers                            |

| DAB     | Dual-active bridge                              |

| DE      | Differential evolution                          |

| DER     | Distributed energy resource                     |

| DFT     | Discrete Fourier transform                      |

| DI      | Digital input                                   |

| DLF     | Distribution load flow                          |

| DOCP    | Directional overcurrent protections             |

| DOCR    | Directional overcurrent relays                  |

| DSADC   | Delta-sigma analog-to-digital converter         |

| DSG     | Digital signal controller                       |

| DSO     | Distribution system operator                    |

| DSP     | Digital signal processor                        |

| DUT     | Device under test                               |

| dVOC    | Dispatchable virtual oscillator control         |

| ECU     | Electronic control unit                         |

| EES     | Electrical energy storage                       |

| EG      | Embedded generation                             |

| EV      | Electric vehicle                                                      |

|---------|-----------------------------------------------------------------------|

| FCS-MPC |                                                                       |

| FFT     | Finite control set model predictive control<br>Fast Fourier transform |

| FOC     | Field-oriented control                                                |

| FPGA    |                                                                       |

| -       | Field programmable gate array                                         |

| FRT     | Fault ride-through                                                    |

| GA      | Genetic algorithm                                                     |

| GCC     | Grid-connected converter                                              |

| GDS     | Gate drive signals                                                    |

| GTM     | General timer module                                                  |

| GUI     | Graphical user interface                                              |

| HC      | Hosting capacity                                                      |

| HEV     | Hybrid electric vehicles                                              |

| HIL     | Hardware-in-the-loop                                                  |

| HLF     | Harmonic load flow                                                    |

| HSM     | Hardware security module                                              |

| ICE     | Internal combustion engine                                            |

| IDE     | Integrated development environment                                    |

| IEEE    | Institute of electrical and electronics engineers                     |

| iLLD    | Infineon low level drivers                                            |

| IM      | Induction motors                                                      |

| IOs     | Inputs/outputs                                                        |

| LCT     | Low-carbon technologies                                               |

| LUT     | Look up table                                                         |

| LVRT    | Low voltage ride through                                              |

| MBSE    | Model-based systems engineering                                       |

| MGCS    | Microgrid control system                                              |

| MIL     | Model-in-the-loop                                                     |

| MPC     | Model predictive control                                              |

| MTU     | Memory test unit                                                      |

| NPC     | Neutral-point clamped                                                 |

| NR      | Newton-Raphson                                                        |

| OBC     | On-board chargers                                                     |

| OC      | Operational Condition                                                 |

| OpenDSS | Open distribution system simulator                                    |

| OP-PWM  | Optimal programmed pulse-width modulation                             |

| PC      | Personal computer                                                     |

| PCC     | Point of common coupling                                              |

| PCC     | Predictive current control                                            |

| PEC     | Power electronic converter                                            |

| PFC     | Power factor correction                                               |

| P-HIL   | Power hardware-in-the-loop                                            |

| PIL     | Processor-in-the-loop                                                 |

| PLL     | Phase-locked loop                                                     |

| PMSM    | Permanent magnet synchronous motor                                    |

|         |                                                                       |

| PoC                 | Point of connection                                   |

|---------------------|-------------------------------------------------------|

| PP-PWM              | Pre-programmed pulse-width modulation                 |

| PR                  | Proportional resonant                                 |

| PS                  | Power stage                                           |

| PSO                 | Particle swarm optimization                           |

| PV                  | Photovoltaic                                          |

| PVDG                | Photovoltaic distributed generation                   |

| PWM                 | Pulse-width modulation                                |

| R&D                 | Research and development                              |

| RCA                 | -                                                     |

| RMS                 | Relay characteristic angle                            |

|                     | Root-mean square                                      |

| ROCOF               | Rate of change of frequency                           |

| RTDS                | Real-time digital simulator                           |

| RTS                 | Real-time simulator                                   |

| SAPFs               | Shunt active power filters                            |

| SCADA               | Supervisory control and data acquisition              |

| SCH                 | Selective current harmonic                            |

| SCR                 | Short circuit ratio                                   |

| SG                  | Synchronous generator                                 |

| SHE                 | Selective harmonic elimination                        |

| SHE-PWM             | Selective harmonic elimination pulse-width modulation |

| SIL                 | Software-in-the-loop                                  |

| SISO                | Single-input-single-output                            |

| SMU                 | Safety management unit                                |

| SPC                 | Standard processing core                              |

| SPE                 | Sensor pattern evaluation                             |

| SPV                 | Solar photovoltaic                                    |

| SRFPI               | Synchronous reference frame proportional-integral     |

| SS                  | State space                                           |

| SVM                 | Space-vector modulation                               |

| SVM <sup>2</sup> PC | Space-vector modulated model predictive control       |

| SV-PWM              | Space vector pulse-width modulation                   |

| SynC                | Synchronverter                                        |

| TDD                 | Test-driven design                                    |

| THD                 | Total harmonic distortion                             |

| TIM                 | Timer input module                                    |

| TLM                 | Transmission line model                               |

| TOM                 | Timer output module                                   |

| TSO                 | Transmission system operator                          |

| VADC                | Versatile analog-to-digital converter                 |

| VHDL                | VHSIC hardware description language                   |

| VHIL                | Virtual hardware-in-the-Loop                          |

| VHSIC               | Very high speed integrated circuit                    |

| VOC                 | Virtual oscillator control                            |

| VSC                 | Voltage source converter                              |

|                     | -                                                     |

| VSG | Virtual synchronous generator                             |

|-----|-----------------------------------------------------------|

| VSM | Virtual synchronous machine                               |

| xEV | Any kind of vehicle that utilizes electric motor traction |

| ZOH | Zero-order hold                                           |

|     |                                                           |

# Chapter 1 Introduction to Typhoon HIL: Technology, Functionalities, and Applications

Caio R. D. Osório, Adrien Genic, and Sergio Costa

**Abstract** This first chapter provides an introduction to the hardware-in-the-loop (HIL) approach and Typhoon HIL, in particular, including a brief overview of its history, achievements, and vision. Real-time simulation challenges are introduced. Throughout the chapter, key technological aspects and functionalities behind the Typhoon HIL toolchain are discussed, highlighting how this seamlessly integrated solution enables the creation of high-fidelity models for hardware-in-the-loop-based real-time simulations and performs automated tests for dynamic and complex systems that go from single high switching frequency power electronics converters to larger microgrid systems.

**Keywords** Control validation · Hardware-in-the-loop · High-fidelity · Model-based testing · Real-time simulation · Typhoon HIL

### 1.1 Introduction

Power-electronics-based technologies are in continuous and accelerated development, leading to a significant cost reduction and increased reliability in different components and devices in the past decades. Motivated by the need to digitize, decarbonize, and decentralize electric energy systems, these advancements enabled global transformations in the energy and electrical power industries. For instance, modern power systems have evolved from a centralized generation framework with unidirectional power flow to dynamic and complex smart grids, characterized by a high penetration of distributed, intermittent renewable energy sources, energy storage systems, smart relays, and the possibility of consumers also acting as producers (e.g., prosumers). Paradigm shifts are also present in other power electronics applications, such as the growing market share of electric vehicles in the automotive industry; the burgeoning interest in more electric and environmentally friendly shipboard

C. R. D. Osório (🖂) · A. Genic · S. Costa

Typhoon HIL, Novi Sad, Serbia

e-mail: caio.osorio@typhoon-hil.com

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2023

S. M. Tripathi and F. M. Gonzalez-Longatt (eds.), Real-Time Simulation and

Hardware-in-the-Loop Testing Using Typhoon HIL, Transactions on Computer Systems and Networks, https://doi.org/10.1007/978-981-99-0224-8\_1

and airplane power systems in the marine and aerospace industries; and the advancement in high-efficiency and low-cost electric motors, electric drives, and powertrains (Liserre et al. 2010; Osório et al. 2021; Chemali et al. 2016; Rommel 2019; Xu et al. 2021).

As a common point in these applications, one can look to the presence of highly dynamical switching converters that, besides its own complexity, include additional features such as intricate digital control, protection capabilities, and advanced communication systems. As a consequence, a major engineering challenge has been to be able to design, implement, and validate, in a timely manner, high-quality and economically viable solutions that comply with multiple development and operational requirements, such as electric vehicle integration standards and grid codes (Osório 2020; Knezović et al. 2017).

In this direction, as the intricacy of controlling power electronics, microgrids, and power systems rise, the ability to reduce development time and costs is a key trait. It is not efficient to wait until advanced stages of a project to carry out tests or to wait for prototypes to be built in order to manually verify the integration of different hardware and software, as well as to assess the performance of the overall system. If this strategy is adopted, it can significantly prolong development time and cost, in addition to limiting testing flexibility due to hardware constraints and safety precautions (Dinavahi et al. 2001; Vekić et al. 2012; Khan et al. 2017).

To overcome that, and to increase the efficiency of engineering processes, hardware-in-the-loop (HIL) simulations have been increasingly used by industry and academia. In this testing framework, the device under test can be directly connected to a real-time simulation, enabling efficient closed-loop, model-based automated testing. HIL proved to be reliable and comprehensive in accelerating the development cycle by allowing testing to start early in the development process, all while improving flexibility, coverage, and security in the verification and validation process. As a testament to that, HIL tools have been used by the automotive and aerospace industries for decades, and have proven effective for testing and pre-commissioning of microgrids, shipboard power systems, validation of energy storage systems, motor drives, and other applications (Genic et al. 2017; Salcedo et al. 2019; Jonke et al. 2016; Zelic et al. 2020; Abdelrahman et al. 2018; Amin et al. 2019; Badini and Verma 2019).

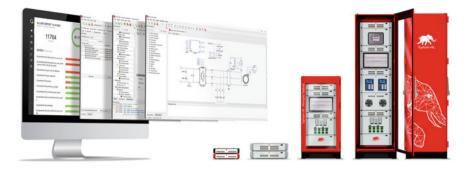

Since its foundation in 2008, Typhoon HIL has supported industry and academia by providing high-fidelity hardware-in-the-loop real-time emulators for electrical systems, with continuous development driven by extensive user feedback. By means of vertically integrated test solutions, Typhoon HIL enables model-based development, test-driven design and the development of digital twin models to assess the technical feasibility of complex systems from the early stages of development all the way to pre-certification, including verification and validation of controls, protection, the communication layer, system integration, and interoperability testing. Some Typhoon HIL devices and features of the toolchain are illustrated in Fig. 1.1.

For a better understanding of how Typhoon HIL toolchain has been recognized as a powerful solution for real-time hardware-in-the-loop simulation in different applications, throughout this chapter, technical details about the technology, methodology,

Fig. 1.1 Typhoon HIL testing solution

and functionalities are presented. It is also worth mentioning that several tutorials, videos, and knowledge-based articles are available online, detailing the features presented in this chapter (Typhoon HIL 2023, a, b).

#### **1.2 Model-Based System Engineering and HIL Testing**

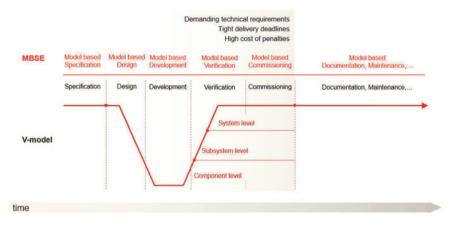

For a long time, control system testing was done manually, relying on small-scale or large full-scale power hardware. In traditional development and validation cycles, such as those following the V-model, these tests would often occur only in the verification and commissioning stage after a physical prototype has been developed. In order to meet cost, time, and quality requirements, model-based systems engineering (MBSE) has emerged as a powerful methodology. In this framework, physical systems and prototypes can be replaced by virtual models, which enable the execution of exhaustive simulations in a safe and flexible environment, saving time, and reducing costs from the specification to the commissioning and maintenance phase. A graphical representation of how MBSE can be applied to support different steps of the development cycle is shown in Fig. 1.2.

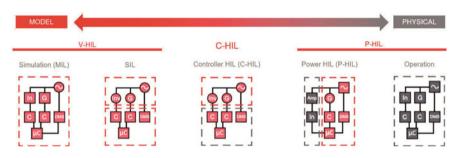

Depending on the specifications, level of abstraction, application, and device under test, different testing setups can be considered, as illustrated in Fig. 1.3. These approaches include model-in-the-loop (MIL), software-in-the-loop (SIL), controller hardware-in-the-loop (C-HIL), and power hardware-in-the-loop (P-HIL).

In the MIL and SIL approaches, both control and power stages (i.e., controller and plant) are simulated in a virtual environment (V-HIL), generally not requiring real-time execution. In the MIL approach, the controller is modeled together with the power layer, while in the SIL approach, the actual control software is considered in the simulation.

Testing setups that feature a mix of physical systems and virtual models are collectively referred to as hardware-in-the-loop (HIL). This means that some physical

Fig. 1.2 V-model: graphical representation of MBSE applied in different steps of the development cycle

Fig. 1.3 Common methodologies for model-based systems engineering

part of the system is connected to the real-time simulation, which could be part of the power hardware (P-HIL) or part of the controller hardware (C-HIL).

In the P-HIL approach, the focus is on testing power hardware. Therefore, power amplifiers can be used to link the real-time simulator to the actual power hardware device under test via analog input/output signals or communication protocols. For instance, current and voltage references can be sent from the real-time simulation to the amplifier using analog outputs, while the feedback signals of the device under test are sensed by the power amplifier, and then sent to the simulation using the real-time simulator analog inputs. As a drawback, although testing software in the presence of actual power provides very accurate results, it usually involves higher cost, lower flexibility, and the need for additional safety precautions.

On the other hand, the C-HIL approach stands out as an effective solution for testing controllers, combining high fidelity, reduced cost, high testing flexibility, and a safe environment. That is possible thanks to the advancements in computing technologies, such as discussed in Sect. 1.4, which enable the development of real-time simulation devices capable of emulating a device's power stage (physical layer)

Fig. 1.4 Concept of controller hardware-in-the-loop

with high precision, even considering demanding high switching power electronics applications.

With the C-HIL approach, the actual controller under test can be directly connected to the modeled plant in real-time simulations, allowing for closed-loop evaluation even before a prototype of the plant is available, as illustrated in Fig. 1.4. This allows for verification and validation of control hardware, software, and firmware in a realistic environment, which provides more flexibility and security than fully physical prototypes, as well as higher fidelity when compared to fully simulated environments. C-HIL also enables engineering teams to automate test cases and to perform several evaluations effortlessly, allowing discovery of performance and integration issues as soon as they arise, iteratively improving the performance of the system being developed. In a similar manner, once experimental prototypes or the actual plant are running, digital twins can be built and the C-HIL approach can be used to validate controller continuous improvements; software lifecycle maintenance; quality assurance processes; and to perform tests that can be hard to replicate, dangerous, or potentially destructive to lab equipment.

The Typhoon HIL toolchain supports all aforementioned testing scenarios, with a targeted focus on the C-HIL approach.

#### **1.3 About Typhoon HIL**

Typhoon HIL Inc. was founded in 2008 as a startup, thanks in part to the investment provided by Ray Stata, Founder of Analog Devices. Typhoon HIL today is a multinational corporation that is the current technology leader in the rapidly growing field of ultra-high-fidelity controller Hardware-in-the-Loop (C-HIL) technology. The company mission is to "Engineer and promote environmentally sustainable power technologies that scale," with the aim of laying the groundwork for building a sustainable future.

Typhoon HIL serves its customers with custom solutions comprised of fully vertically integrated software and hardware for model-based testing and development of power electronics, e-mobility, microgrids, and distribution networks. Typhoon HIL solutions aim to support its users through the entire span of their product's lifecycle,

Fig. 1.5 Typhoon HIL coverage of different market and application segments

starting from design and development, throughout validation and verification stages driven by automated testing, all the way to integration and maintenance. Engineering services provided by the company help in technology adoption, system bring-up, and scaling, to speed up project progress and success. Since its establishment, the company successfully brought to market a number of HIL products, installing over 1000 HIL systems worldwide in both industry and academia.

The company's primary R&D center in Serbia features a multidisciplinary team of experts in the fields of power electronics, signal electronics, real-time and application-specific software, computer architectures, electricity distribution, protection and control, industrial power system management, integration of distributed energy sources, and communication protocols. As a result, the Typhoon HIL environment has competences to cover multiple applications in fields such as microgrids, drives, e-mobility, battery energy storage systems, marine power systems, and so on (see Fig. 1.5 for illustration).

In addition to the corporate headquarters in Boston, MA and the main R & D center in Serbia, the company has offices in Switzerland, Brazil, Canada, France, and soon Germany. The company also works together with over 20 value-added resellers, distributors, and engineering centers worldwide which facilitate both development and production, as well as successful communication to serve the global market.

#### 1.4 Typhoon HIL Technology

When performing HIL testing, it is imperative that the simulation runs in real time; the elapsed time when running the digital model of a physical system must match exactly with the real-world time, also known as the wall-clock time. In this context, Typhoon HIL devices are high-performance computers designed and built for real-time simulation of power-electronics-based systems. This makes a HIL device an important tool for several applications where the behavior of a device should be tested before prototyping, including model-based control development, test-driven design, pre-commissioning, virtual system integration, and interoperability testing of modern power-electronics-enabled technologies. Simulations run on these devices have also proven useful when acting as a high-fidelity replica, or "digital twin," of a

power electronic device or power system, such as for replicating faults encountered by a real device in customer support applications or by creating a sandbox environment for SCADA operator control training in microgrids. But what are the challenges in performing real-time simulations?

#### Real-Time Simulation Challenges

Real-time simulation of power-electronics-based systems (e.g., microgrids, EV drivetrains, shipboard power systems) is challenging since these applications comprise switching converters that operate at ever-increasing frequencies, especially considering the advancements on the semiconductor devices. Therefore, to be able to simulate switching effects with high accuracy, very short simulation time steps are required, as well as high-resolution sampling of the switch gate drive signals (GDS), advanced processing capability, and ultralow latency. As a consequence, power electronics applications comprise complex and highly dynamic systems that are highly demanding to simulate in real time with high fidelity (Osório et al. 2021; Majstorovic et al. 2011; Pallo et al. 2017).

Real-time simulation devices run in discrete time and typically employ linear solvers with fixed time steps. To encompass the switching dynamics in efficient simulations, a piece-wise linear approach can be used. In this context, power converters can be modeled based on ideal switches, and for every switch permutation, a time-invariant linear state space model, called mode, is defined. A single mode is applied over each simulation time step, and the simulation dynamically changes among modes throughout execution. As an advantage, modeling switches as ideal do not introduce non-physical behavior, as may be the case in simulation approaches where the switches are replaced with simplified equivalents. Moreover, it is possible to pre-compute the system matrices and to store them in the solver memory, during compilation. On the other hand, since theoretically each and every semiconductor can be either conducting or open, the number of modes increases exponentially with the number of switches, thus increasing exponentially the memory capacity required (Osório et al. 2021; Majstorovic et al. 2011).

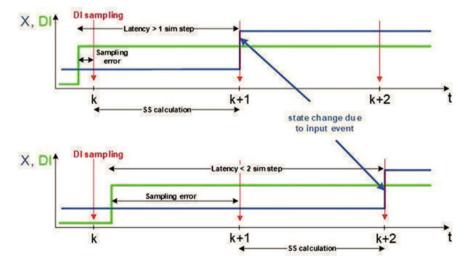

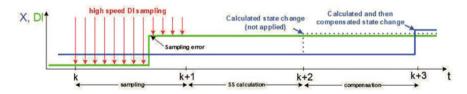

Another important challenge for real-time simulation of power electronics applications is related to the effective time resolution of the digital inputs used to drive the converters, which are usually pulse-width-modulated (PWM) signals. When an actual controller hardware is being used to generate the GDS, its clock (and therefore the time instant where its outputs are updated) is not synchronized with the simulation clock. In this context, if the sampling period of the PWM signals is equal to the simulation time step, the transitions between on and off states can only be detected at the subsequent sampling, as illustrated in Fig. 1.6. This inaccuracy in identifying the exact instant at which the transitions occur may lead to significant sampling errors, causing imprecise duty cycle detection and, therefore, inaccurate simulation results. When offline simulations are performed, this drawback can be mitigated by using variable step solvers or by reducing the simulation time step as much as necessary to make the sampling errors become negligible. However, this happens at the price of longer execution times, which is not a viable solution for real-time simulations where the model response calculation must be finished within the predefined simulation step (Lian and Lehn 2005).

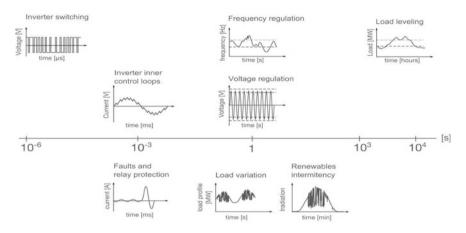

The challenges described so far focused primarily on the real-time simulation of power converters, where time constants in the order of nanoseconds are required in order to precisely reproduce switching effects and obtain accurate simulation results. On the other hand, when testing, for instance, the secondary or tertiary control layers of power systems such as microgrids, models tend to be large and simulation run times may reach days or weeks, with time constants in the order of minutes or hours. In this sense, it is possible to see that different applications present different requirements, such as high time resolution and long-term stability, which may demand different modeling approaches and processor capabilities, posing a significant challenge. A chart illustrating the wide range of time scales of interest within a microgrid application is illustrated in Fig. 1.7.

In addition to that, as mentioned before, real-time simulations are essential when real elements are present in the loop. As a consequence, the hardware-in-the-loop simulation devices must be robust and present suitable interfaces, allowing easy access to multiple inputs, outputs, and connection with a wide range of possible devices under test, including supporting the specific communication protocols those devices may use. At the same time, real-time simulations and the hardware-in-theloop testing framework aim to reduce time and costs in the development cycle, and thus must not overwhelm engineers with additional concerns. Therefore, it is important to provide a solution that, although technically advanced, is user-friendly and easy to get used to. In this context, the HIL solution should suit different application-

**Fig. 1.6** Illustration of state space (SS) calculation and the respective state (X) change due to a digital input (DI) event with sampling period equal to the simulation time step. Sampling error and latency depend on when the DI changes with respect to the simulation time step (Osório et al. 2021; Typhoon HIL 2023c)

#### 1 Introduction to Typhoon HIL: Technology, Functionalities, and Applications

**Fig. 1.7** Graph illustrating how the time scale of interest varies in a microgrid application according to the phenomenon to be observed and the objectives of the simulation (Typhoon HIL 2017)

specific systems with easily deployable preset configurations, while still providing flexibility for more experienced HIL users to develop bespoke solutions for custom applications.

Challenges for real-time simulation solutions include the following:

- Achieving very short simulation time steps and low latency to represent highly dynamic power electronics systems with accuracy.

- Reducing memory capacity requirements.

- Improving the effective PWM time resolution.

- Coping with large models and different application-specific requirements.

- Hardware with suitable interfaces and support for industry standard communication protocols.

- User friendliness, flexibility, and easy to get used to.

#### Typhoon HIL Testing Solutions

Aiming to overcome the challenges mentioned in this section, Typhoon HIL provides a vertically integrated solution, comprising of real-time simulator hardware and a dedicated software toolchain (Typhoon HIL Control Center). The technology stack is seamlessly integrated from Typhoon HIL's application-specific processors and robust numerical solver all the way to the model building interface, supervisory system, and testing automation solution, in a single easy-to-use and affordable toolchain. In the next subsections, the Typhoon HIL real-time simulator hardware and software technology is presented, as well as how they address the challenges described here.

#### 1.4.1 Typhoon HIL Real-Time Simulation Platform

Typhoon HIL simulators are hardware platforms specialized for high-fidelity realtime HIL simulations of power-electronics-based systems, which are enabled by a state-of-the-art processor design seamlessly integrated with a fully embedded compiler. As mentioned before, proper real-time simulation of power-electronics-based systems requires high-speed, low-latency, scalable, and flexible computation technologies. Typhoon HIL devices achieve that by using a programmable, applicationspecific, hybrid architecture that combines CPU (central processing unit) and FPGA (field programmable gate array) technologies, seamlessly integrated with the software toolchain.

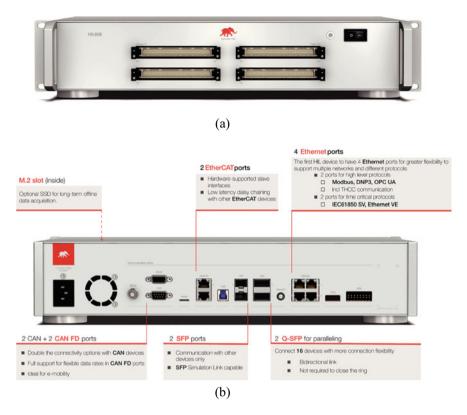

The current line-up includes two generations of devices. The third-generation devices (HIL402, HIL602+, and HIL604) support simulation steps down to 500 ns, while oversampling digital inputs with 6.5 ns resolution. These devices have proved themselves in numerous industrial applications, even in some cases with switching frequencies exceeding 100 kHz. To further improve simulation fidelity for high switching frequency applications, such as high-speed drives and DC-DC resonant converters, fourth-generation devices (HIL404 and HIL606) support even lower simulation steps, down to 200 ns, with digital input sampling resolution of 3.5 ns. More details about the current device line-up, including the number of processing cores, model capacity, time resolution, number of analog and digital inputs/outputs (IOs), and connectivity support with industry standard protocols can be seen in Fig. 1.8. In addition, it is worth noting that thanks to the modular design, multiple device units can be stacked together and paralleled, behaving as a single larger simulator.

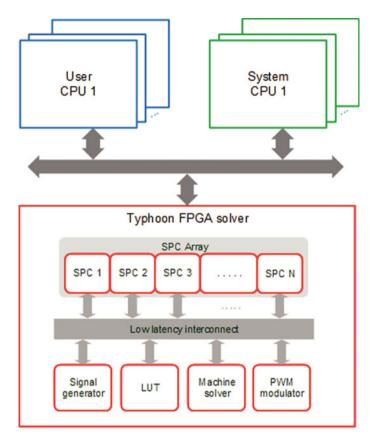

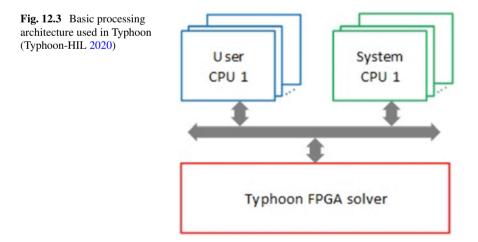

All Typhoon HIL devices share a common multi-processor architecture, which contains a proprietary multi-core FPGA solver, system CPUs, and user CPUs, as illustrated in Fig. 1.9. A summary of their functions is given as follows:

- **Typhoon FPGA Solver:** The multi-core FPGA solver is used to simulate the electrical layer of the model, optimized for time-exact simulation.

- **System CPUs:** General-purpose processors indirectly controlled by the user, typically used to simulate low dynamics phenomena of certain electrical domain components or to handle communication protocol stacks.

- User CPUs: General-purpose processors that are under direct user control, responsible for the simulation of model components that don't belong to the electrical domain, such as mechanical, thermal, and signal processing components. User CPUs can also be used for the development of controller algorithms within the model, using MIL and SIL approaches or rapid control prototyping.

|                                                      | inter a second | inen' man     |               |            |            |

|------------------------------------------------------|----------------|---------------|---------------|------------|------------|

| HIL Simulators                                       | HIL402         | HIL404        | HIL602+       | HIL604     | HIL606     |

| Processing cores (number of cores)<br>Model capacity | Up to 4        | Up to 4       | Up to 6       | Up to 8    | Up to 8    |

| Detailed converter models (1ph/3ph)                  | 8/4            | 8/4           | 12/6          | 16/8       | 16 / 8     |

| Average converter models (3ph)                       | 8              | 12            | 10            | 10         | 24         |

| Distribution network simulation                      | 4              | ~             | ~             | ~          | ~          |

| Time resolution                                      |                |               |               |            |            |

| Minimum simulation step                              | 500 ns         | 200 ns        | 500 ns        | 500 ns     | 200 ns     |

| DI sampling resolution                               | 6.2 ns         | 3.5 ns        | 6.2 ns        | 6.2 ns     | 3.5 ns     |

| 1/0                                                  |                |               |               |            |            |

| Analog I/O (per unit)                                | 16/16          | 16/16         | 16/32         | 32/64      | 32/64      |

| Digital I/O (per unit)                               | 32/32          | 32/32         | 32/32         | 64/64      | 64/64      |

| Connectivity                                         |                |               |               |            |            |

| USB                                                  | ~              | ~             | ~             | *          | ~          |

| Ethernet                                             | ~              | *             | ~             | ~          | ~          |

| CAN                                                  |                | ~             | ~             | ~          | ~          |

| RS232                                                |                | ~             | ~             | -          | ~          |

| EtherCAT                                             |                |               |               |            | ~          |

| SFP                                                  |                | *             |               |            | ~          |

| Time synchronization (PPS and IRIG-B)                |                |               |               | ~          | ~          |

| Paralleling                                          |                | Up to 4 units | Up to 4 units | Up to 16 u | Up to 16 u |

Fig. 1.8 Current Typhoon HIL devices line-up

The HIL606 device is illustrated in Fig. 1.10, where (a) illustrates the front view, highlighting the analog and digital IOs, and (b) illustrates the back view, highlighting the expanded connectivity options, which increases flexibility for multiple protocols.

#### 1.4.1.1 Multi-Core FPGA

As mentioned in the previous section, real-time emulation imposes a rigid time limitation for the calculation of model responses which is not present in offline simulations. Therefore, to achieve very short simulation time steps, computation of complex models has to be parallelized.

In this context, the Typhoon HIL multi-core FPGA solver is the key technology that enables high-fidelity real-time emulation of power-electronics-based systems. The FPGA is optimized for time-exact simulation, and thanks to its paralleled architecture and low latency connection between the processing elements, it is capable of reducing the memory requirements and of running complex models with time steps down to 200 *ns*, as shown in Fig. 1.8. Moreover, its processing blocks are tightly integrated with the input/output (IO) stage, ensuring very low and fully predictable loopback latency, which allows seamless interfacing with external controllers.

The main FPGA solver computation elements are depicted within the red box in Fig. 1.9. Their descriptions are given below:

**Fig. 1.9** Typhoon HIL device architecture, encompassing: user CPU, System CPU, and Typhoon FPGA solver with multiple Standard Processing Cores (SPCs)

- **Standard Processing Core (SPC):** Responsible for the simulation of electrical circuits consisting of linear passive elements (both constant and time-varying), converter blocks (built with ideal switches), and contactors based on ideal or non-ideal switches. Dedicated communication lines interconnect the different SPC blocks, allowing variable exchange with a single simulation step delay.

- **Signal Generator:** Built-in, runtime tunable block responsible for generating independent voltage and current sources, as well as other arbitrary waveforms synchronously and at the full simulation rate. Linear interpolation is applied if the waveform sample rate is lower than the simulation rate.

- Look-Up Table (LUT): Block used to simulate nonlinear elements such as PV panels, batteries, nonlinear passive components, and saturable transformers.

- Machine Solver: Each unit can emulate a single electrical machine model including its electromagnetic part, mechanical part, and speed measurement devices such as encoder and resolver.

Fig. 1.10 HIL606 device: a front view; b back view

• **PWM Modulator:** It consists of a multi-channel triangular PWM modulator that can be used both internally, to drive converter models built in the model, and externally, using the digital outputs. The modulator runs on the FPGA internal clock with a built-in dead time generator.

Notice that the resources available on the Typhoon HIL FPGA solver enable it to support various elements used in different electrical applications. This architecture is scalable and is used on all Typhoon HIL devices. Nevertheless, every device has a number of different configurations, which differ in number and size of the computational elements available. The user can choose the configuration in order to optimize FPGA resources for the specific application under test. For instance, time-varying elements are not supported for all configurations, while the number of signal generators or machine solvers depends on the device configuration.

The FPGA solver also provides the means for emulating switch turn-on and turnoff delays in addition to real-time calculation of semiconductor losses, enabling detailed power converter modeling even with converter blocks that consist of ideal switches. In addition, oversampling methods are available to meet the rigorous accuracy requirements for real-time simulation of high switching frequency applications. By enabling oversampling in Typhoon HIL simulations, it is possible to reach sampling periods down to 3.5 *ns* (fourth-generation devices) for all digital inputs, significantly improving the PWM resolution for higher switching frequencies. One of these methods is called Global GDS Oversampling, and it is enabled by default when you create a new model in the Schematic Editor. As illustrated in Fig. 1.11, this method is based on high-resolution PWM sampling (i.e., digital inputs are sampled several times within one simulation step), event time stamping, and error compensation. The oversampling methods used in Typhoon HIL devices and how enhancements on sampling resolution improve real-time simulation accuracy are discussed in more details in (Osório et al., 2021).

As mentioned before, another challenge is to be able to simulate with high accuracy a wide range of applications, going from unit models of power converters to larger power systems with a significant level of details. Converters are modeled using a piece-wise linear model, where the number of linear state space systems grows exponentially with the number of switches, thus exponentially increasing the memory required. The Typhoon HIL solution addresses this challenge using the parallel computing enabled by the multi-core FPGA solver. To illustrate that, consider a simulation which contains n + m = 12 switches, as illustrated in Fig. 1.12.

With 12 switches, one converter has  $2^{12}$  possible permutations, meaning that 4096 state space matrix representations would have to be stored in memory. On the other hand, by using paralleling computing and dividing the circuit equally in two SPCs (n = m = 6), each core would have  $2^6$  possible permutations, leading to 64 state space matrix representations per core, and therefore 128 in total, which represents a significant reduction in memory capacity requirements. Moreover, given that the time needed to simulate the model is a function of the size and density of state

**Fig. 1.11** Illustrative representation of the GDS Global Oversampling method. DI represents the digital input (GDS or PWM signal) and X illustrates the state change due to the input event (Osório et al. 2021; Typhoon HIL 2023c)

Fig. 1.12 Example of how circuit partitioning allows for reducing memory capacity requirements and achieving faster simulation rates

space matrix, splitting the model in different cores also allows for achieving faster simulation rates. It is worth mentioning that circuit partitioning can be done both between SPCs of a single HIL device and between multiple HIL devices. Moreover, enabling parallel computing of complex power electronics or power system models is done in a very easy and straightforward way, by using dedicated components in the Schematic Editor of the Typhoon HIL Control Center tool that will be detailed later.

#### 1.4.1.2 Embedded Compiler

The Typhoon HIL compiler is fully embedded, allowing compilation of high-fidelity models optimized for real-time execution without third-party tools and without requiring expertise in low-level programming. The compilation is fully automated and accessible through one click, converting the graphical representations built in the Typhoon HIL Schematic Editor to sets of instructions for both FPGA and CPU processors.

Throughout the compilation process, the Typhoon HIL compiler provides a detailed report, which warns about defects and possible instabilities in the circuit. It also shows how the model is distributed in the HIL devices, its processing cores, what are the resources being utilized, time utilization within the simulation step, and also sub-optimal model characteristics, providing guidance for further model optimization. An excerpt of a compiler log is shown in Fig. 1.13. In this example, it is possible to verify that the model was divided into three subcircuits, as well as the partial list of components in each SPC and the hardware utilization analysis.

#### 1.4.1.3 Hardware Interface and Accessories

Real-time simulation platforms must be flexible to enable hardware-in-the-loop simulations for various applications, which require suitable interfaces between the simulator and the large variety of possible devices under test. For that purpose, Typhoon HIL real-time simulators comprise several digital and analog inputs and outputs, as illustrated in Fig. 1.10a. Moreover, a number of dedicated interface systems are offered, which can be chosen according to key factors such as the number of signals and the signal conditioning requirements (based on the voltage and current levels of the device under test). The IO voltage levels and sample rates on Typhoon HIL devices can be easily found in the documentation (Typhoon HIL 2023e, f).

As the simplest interface possible, wires can be used to directly interface the real-time simulator with external controllers. For that purpose, Typhoon HIL offers a HIL Breakout Board, which simplifies the wiring between the control hardware and the HIL system, as shown in Fig. 1.14a. Nevertheless, note that this kind of interface requires matching of the voltage levels of the devices. As an alternative, dedicated interface boards can be used, where printed circuit boards are responsible for the signal conditioning, comprising connectors that are compatible with both the

```

Compiling model for device with id 0

PWM Modulators scheduling completed.

Circuit is divided into 3 subcircuits.

Partial list of components in subcircuit (SPC) 0:

Grid Side Converter1

Rotor Meter

Chopper

Partial list of components in subcircuit (SPC) 1:

Grid Meter

51

R1

Partial list of components in subcircuit (SPC) 2:

Tr2

Vrms grid

Vs

Communication lines scheduling completed.

Running Device specific hw utilization analysis:

Standard processing core utilization:

3 out of 6

50.0%

Signal generator utilization:

3 out of 12

25.0%

0 out of 8

Look up tables utilization:

0.0%

1 out of 2

Machine solver utilization:

50.0%

Parallel DTV Conv. Detectors utilization:

0 out of 3

0.0%

PWM channels utilization:

6 out of 12

50.0%

```

Fig. 1.13 Example compiler log

Fig. 1.14 HIL interfaces: a HIL breakout board; b HIL TI launchpad interface

real-time simulator and the device under test. As an example, Typhoon HIL offers off-the-shelf plug-and-play interface boards for Texas Instruments controllers and Launchpads, as illustrated in Fig. 1.14b.

Multiple conditioning systems packaged in a dedicated enclosure, called HIL Connect, are also offered, as illustrated in Fig. 1.15a. This approach provides great flexibility once it supports all major types of connectors, allowing the user to connect the device under test to the emulator with the exact same cables that would be used in the real system. HIL Connect systems can be customized according to particular requirements and specifications.

Fig. 1.15 HIL interfaces: a HIL connect; b Packaged interface with HIL compatible controllers

In addition to these, a selection of pre-packaged third-party device controllers with standardized, reproducible interfaces are also available. Known as HIL Compatible interfaces, these solutions are C-HIL ready, and can be connected to real-time simulators using only a set of standard cables, as illustrated in Fig. 1.15.

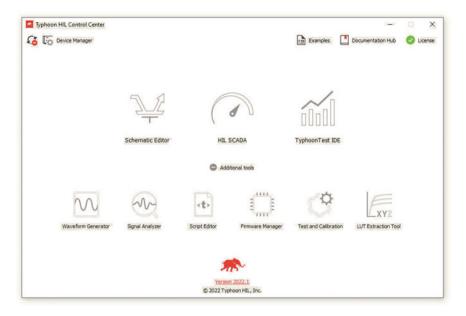

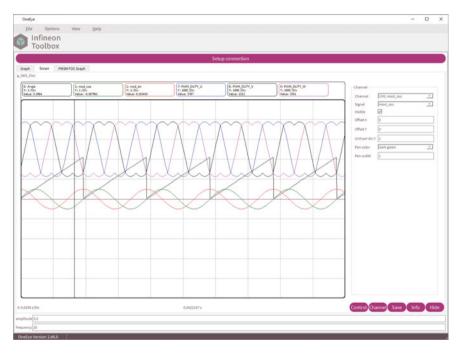

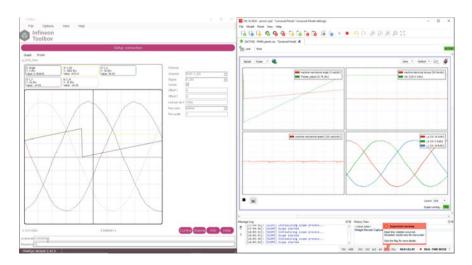

## 1.4.2 Typhoon HIL Control Center

Typhoon HIL Control Center is a fully integrated toolchain that enables users to build models, parametrize components, run HIL-based real-time simulations, and perform automated tests. This means any user can access the full potential of the developed hardware technology in an easy and straightforward way, without requiring experience in low-level programming. In addition, by means of a Virtual HIL device, the toolchain can also be used to verify real-time ready models even without controller hardware and before having an actual HIL device available, further facilitating the test-driven development process.

The initial window of the software can be seen in Fig. 1.16. The main resources include the modeling tool, the real-time graphical interface, and test development tools, as described in the following sections. If you are interested to raise your skill and knowledge of the Typhoon HIL toolchain, a HIL Fundamentals course is available on the HIL Academy platform which provides a detailed explanation and interactive demonstration of the tools described here (Typhoon HIL 2023b).

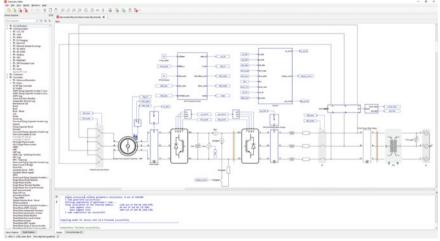

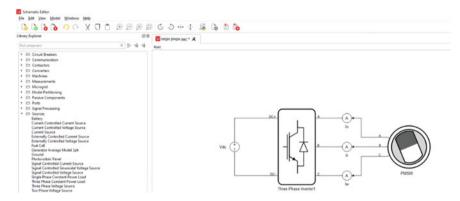

#### Schematic Editor

Schematic Editor is a software environment where real-time ready models are built and compiled using a user-friendly and intuitive interface, as illustrated in Fig. 1.17. The models can be developed from scratch, by dragging and dropping any number of the hundreds of pre-built components easily accessible using the Library Explorer tool shown in the left side of Fig. 1.17. The library includes pre-packaged converters, transformers, renewable sources, electrical machines, passive components, and oth-

Fig. 1.16 Typhoon HIL control center

Fig. 1.17 Schematic editor interface displaying a wind turbine with doubly-fed induction generator model

ers, which are optimized for fast compilation and real-time executions, in addition to being easily parametrized for different domain-specific applications.

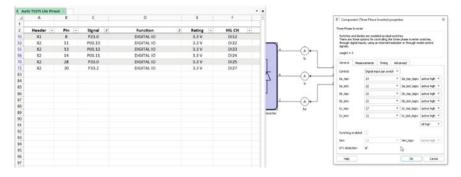

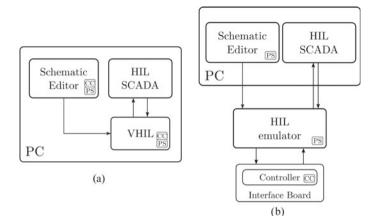

As an example, Fig. 1.18 shows a three-phase inverter component, which is part of the converters library. This component can be used in conjunction with passive and other components to build tailor-made models for custom applications. Notice

|                       | Switches an<br>There are t | nverter from libra<br>d diodes are mod<br>hree options for o<br>g an internal mode | eled as ideal | e three phas | se inverti<br>control s | er switches, t<br>ignals. | hrough dig | ptal   |

|-----------------------|----------------------------|------------------------------------------------------------------------------------|---------------|--------------|-------------------------|---------------------------|------------|--------|

|                       | General                    | Measurements                                                                       | Timing        | Losses       | Advan                   | ced                       |            |        |

|                       | Control:                   |                                                                                    | Internal m    | odulator     | •                       |                           |            |        |

|                       | Operation m                | node:                                                                              | Fixed carr    | er frequenc  | ay +                    |                           |            |        |

|                       | Carrier freq               | uency (Hz):                                                                        | 10000.0       |              |                         | Hz                        |            |        |

|                       | Carrier phas               | se offset:                                                                         | 0.0           |              |                         | deg                       |            |        |

|                       | Dead time p                | eriod:                                                                             | 5e-6          |              |                         | s                         |            |        |

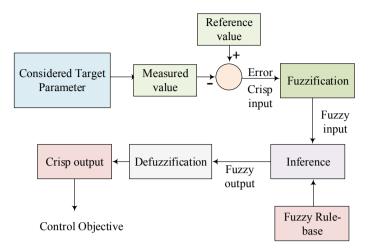

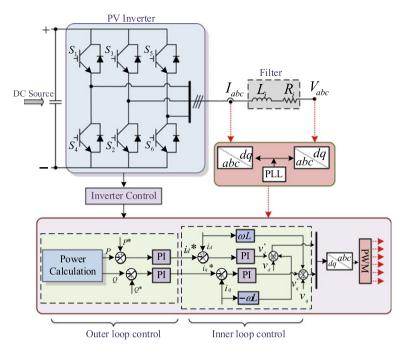

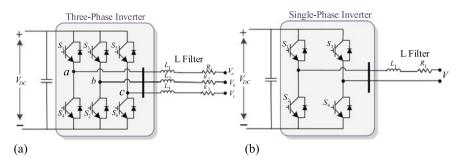

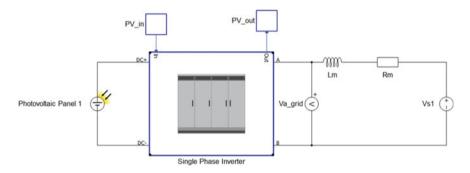

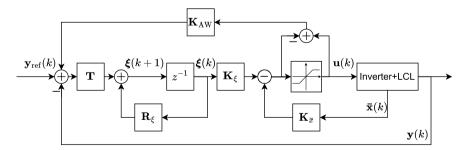

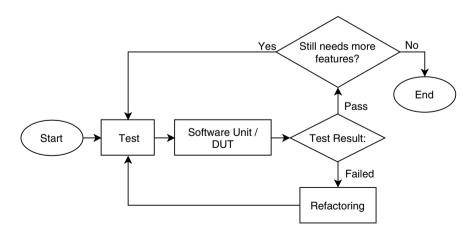

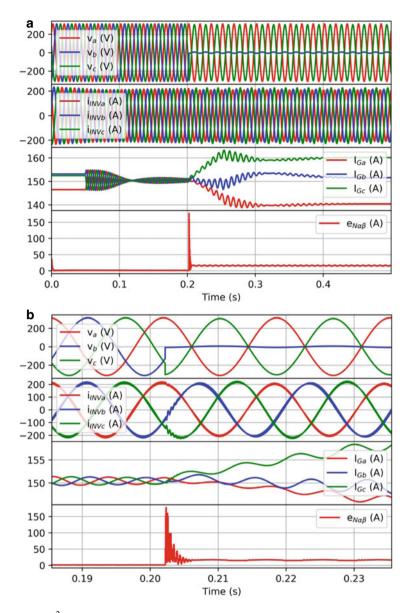

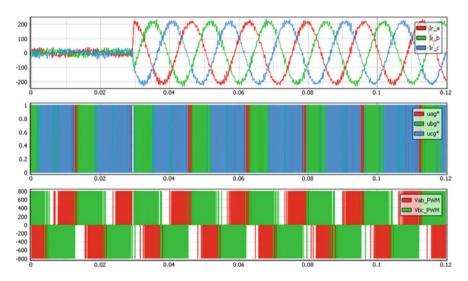

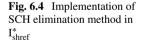

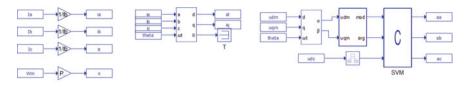

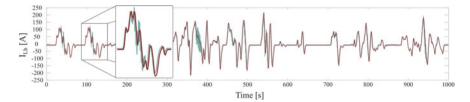

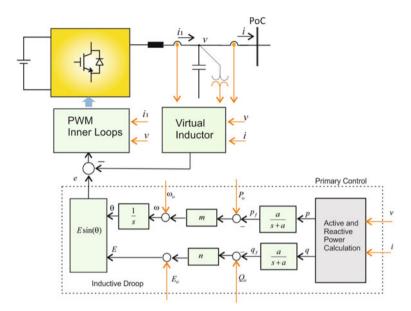

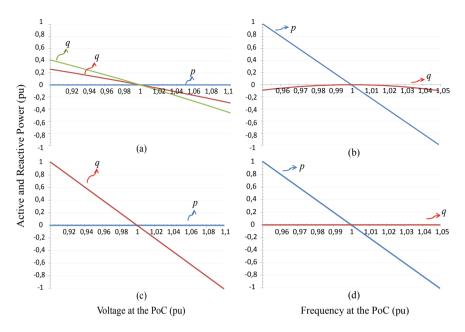

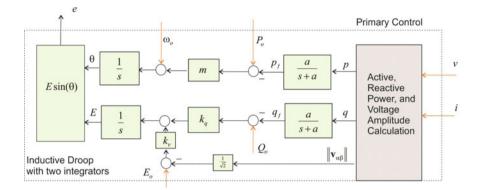

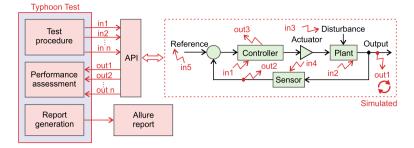

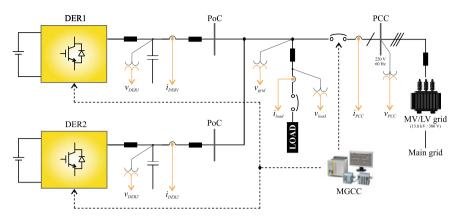

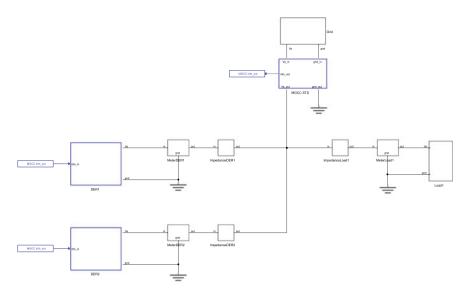

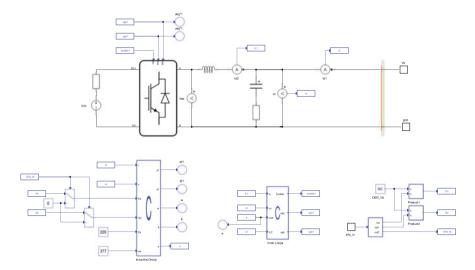

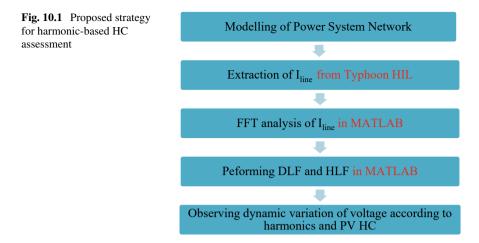

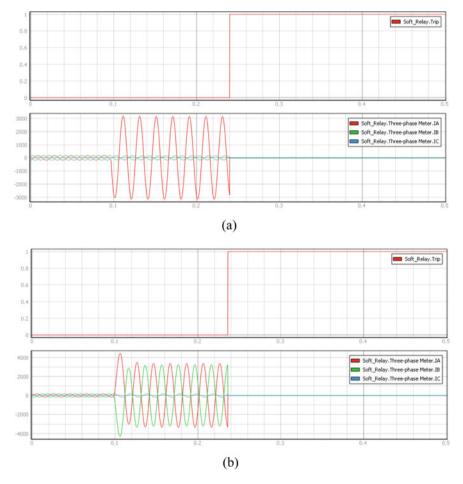

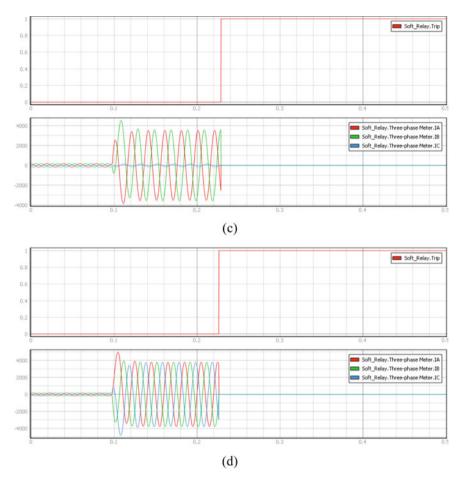

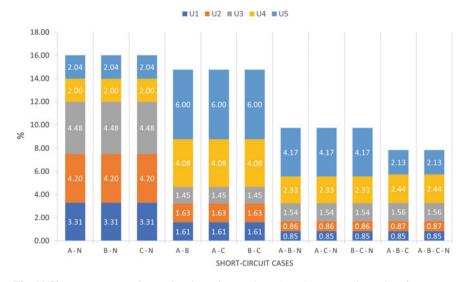

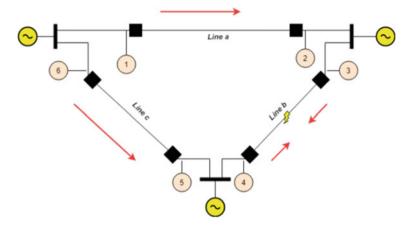

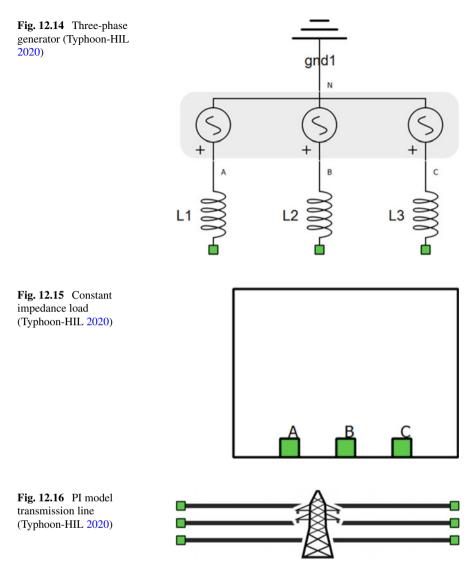

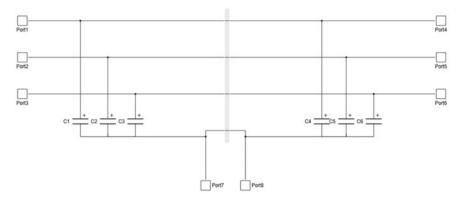

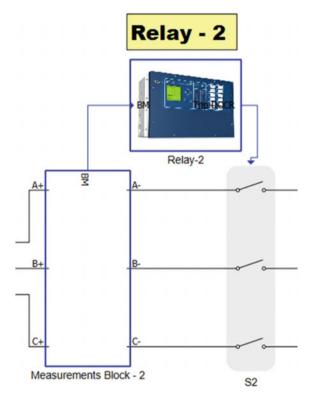

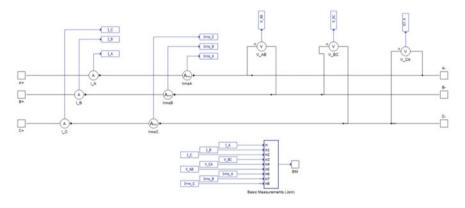

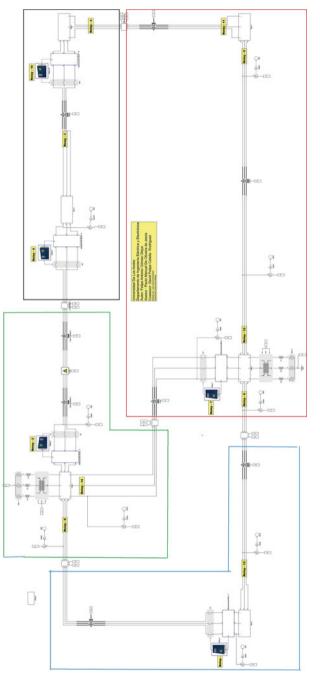

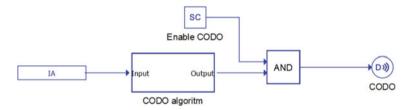

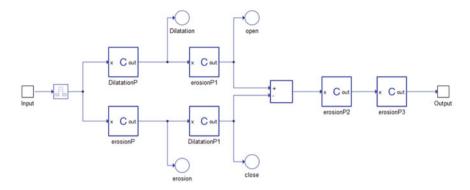

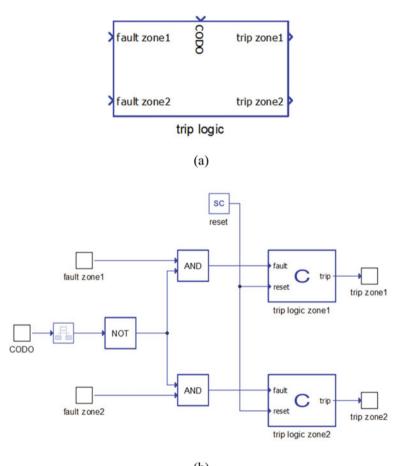

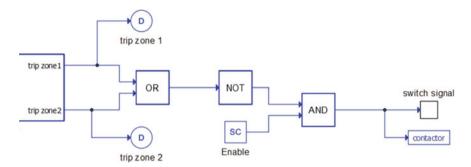

|                       | Reference s                | signal [min, max]:                                                                 | [-1.0, 1.0]   |              |                         | Load mode:                | on min     | •      |