# Design of Low-Power 10T Full Adder Circuit using DG—MOSFET at 180 nm Technology

Aakrati Agrawal, Pramod Kumar Jain, and D. S. Ajnar

**Abstract** Keeping the current scenario of digital era in outlook where devices with high portability and performance are in demand, the paper proposes a technique, i.e., double-gate MOSFET (DGFET) which holds well. This technique replaces single-gate transistor logic with double gate results in reducing problems like short channel effects in FETs. The paper includes design of 10T full adder digital logic circuit, parametric analysis such as power consumption and resistance offered. The implementation of design and simulation results has done using Cadence Virtuoso tool at 180 nm technology.

**Keywords** Double-gate FET  $\cdot$  Full adder  $\cdot$  Single gate  $\cdot$  Power consumption  $\cdot$  MOSFETs

## 1 Introduction

The most considerate predictions done in the field of microelectronics and VLSI are by Gordon Moore who described a law named Moore's law which states that "the number of transistors in a dense integrated circuit (IC) doubles about every two years." To keep following the law, the dimensions of transistor get reduced by half in a period of every three years. Since transistor is the integral component in microelectronics and VLSI that every feature and parameter is essential to look after. The prime objective of switching technologies from using BJT (bipolar transistor) to FETs (field effect transistor) and MOSFETs is improving performance parameters such as power consumption, increased speed, smaller chip area, cost reduction.

A MOSFET is a semiconductor device which is widely used in electronic devices due to various features it possess like amplification and high switching speed when

101

A. Agrawal (🖂) · P. K. Jain · D. S. Ajnar

Department of Electronics and Instrumentation Engineering, SGSITS, Indore, M.P., India e-mail: aakrati1506@gmail.com

D. S. Ajnar e-mail: dsajnar@sgsits.ac.in

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2023 V. Nath and J. K. Mandal (eds.), *Microelectronics, Communication Systems, Machine Learning and Internet of Things*, Lecture Notes in Electrical Engineering 887, https://doi.org/10.1007/978-981-19-1906-0\_8

dealing with electrical signals. It is considered as an ideal switching device which has bidirectional capability and offers low static power dissipation, high scalability, and high packing density in integrated circuits [1-8].

There are two modes of operating MOSFETs:

- (1) Depletion mode in FET

- (2) Enhancement mode in FET.

There are several types of MOSFETs but here described are two types, i.e., singlegate MOSFET and double-gate MOSFET.

#### 1.1 SG—MOSFET

A single-gate MOSFET is the basic component which has four terminals, i.e., source, gate, drain, and body. In this type of device, all four terminals operate independently and offering different functionality. Single-gate FET operates in both modes of operations, i.e., enhancement mode and depletion mode [1, 9-11].

#### 1.2 DG—MOSFET

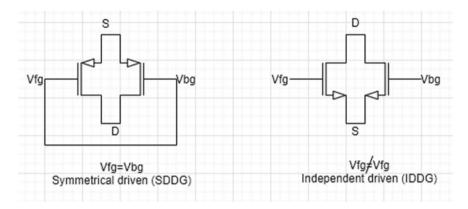

The double-gate MOSFET (DGFET) is designed using two single-gate MOSFETs that are placed in such a way the identical terminals of both the components get connected. The symbol now has two gates, i.e., front gate and back gate. These two gates can operate simultaneously also which is termed as symmetrical driven (SDDG). The gates can be operated independently by applying voltage bias to one and switching the other which is known as independent driven (IDDG) [1–5, 8, 11, 12].

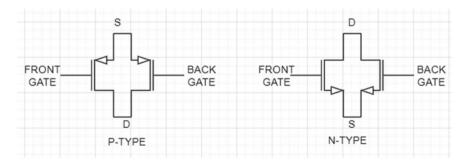

Figure 1 shows circuit symbol of p-type and n-type DG-MOSFET.

Transistors and Fig. 2 show modes of operations of double-gate transistor.

Fig. 1 Circuit symbols

Fig. 2 Operating modes

## 2 Full Adder

The efficiency of any digital device depends entirely on the internal devices and components used in designing the particular unit. As the market growing and dependency on digital devices is increasing rapidly, there is always a need to improve the performance based on some parameters such as smaller size, cost per unit, durability, and power consumption, these parameters helps a device to be more reliable and portable. Full adder is one integral unit in any digital device, i.e., microcontrollers and microprocessors in its arithmetic logic unit (ALU).

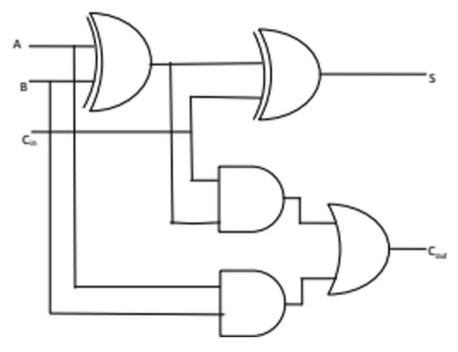

The basic block diagram using logic gates of one bit full adder is shown in Fig. 3. Figure 3 shows a combinational circuit of full adder that is used to perform arithmetic operations in ALUs. It takes three bits as inputs (A, B, Cin), performs the required mathematical operation using the gates and gives two outputs (S, Cout).

The Boolean expression for this logic is described as:

$$S = A \oplus B \oplus Cin$$

$$Cout = AB + ACin + BCin$$

For designing of full adder circuit, an additional degenerate module is required, i.e., a 5T XOR-XNOR circuit. This module helps in reducing the number of transistors thus reduces the integration size and also helps in making leakage current less with less static power dissipation.

This module uses combination of p-MOS and n-MOS transistors which takes two inputs (A, B) and give outputs (C, D).

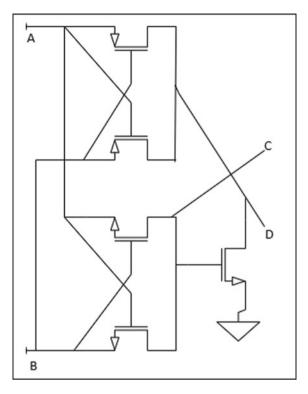

The circuit is biased with the input pulses and has a ground pin (gnd, 0 V). The schematic design of 5T XOR-XNOR module is shown in Fig. 4.

Fig. 3 One-bit full adder

The module is best suitable even where there is requirement of low-power operations since it excludes the use of voltage.

The circuit performs two operations, i.e., XOR and XNOR on the input pulses taken as *A* and *B*. This operation can be well described through its truth table that is described in Table 1.

The two signals (1-) and (0+) are degraded signals due to threshold voltage loss. In the case where both the inputs are "0," the XNOR output becomes floating which is indicated by the symbol (X). Hence, module is considered logically degenerated.

Combinations of all the inputs are not satisfied this module, but it is sufficient enough to produce the output signals (C, D) needed for the appropriate functioning of the full adder.

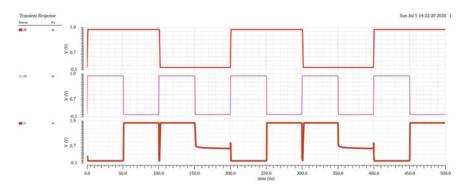

The transient response for the circuit module is recorded at 100 ns shown in Fig. 5.

### 3 Full Adder Design Using Single-Gate Transistor Logic

The designing of full adder using single-gate transistor logic is implemented by using 5T XOR-XNOR module discussed above. The output signals (C, D) taken from previous module are used as input to the other half module of single-gate full adder design circuit.

Fig. 4 5T XOR-XNOR module

Table 1 XOR and XNOR operations on the inputs A and B

| A | В | $\overline{D}$ (XNOR) | D (XOR) |

|---|---|-----------------------|---------|

| 0 | 0 | X                     | 0+      |

| 0 | 1 | 0                     | 1       |

| 1 | 0 | 0                     | 1       |

| 1 | 1 | 1-                    | 0       |

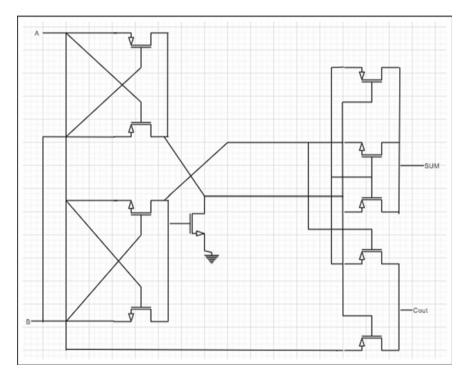

The schematic design of full adder using single-gate transistor logic is shown in Fig. 6.

The Boolean expression for the 5T XOR-XNOR module is described below [13]:

$$S = (\overline{A \oplus B})C + (A \oplus B)\overline{C}$$

$$Cout = (A \oplus B)C + (\overline{A \oplus B})A$$

The Boolean expression for SG-MOSFET-based double adder using the 5T XOR-XNOR module is described below:

Fig. 5 Transient response at 100 ns

Fig. 6 Schematic design of full adder using SG transistor

$$S = D \oplus C$$

$$Cout = D \oplus C + \overline{D} \oplus A$$

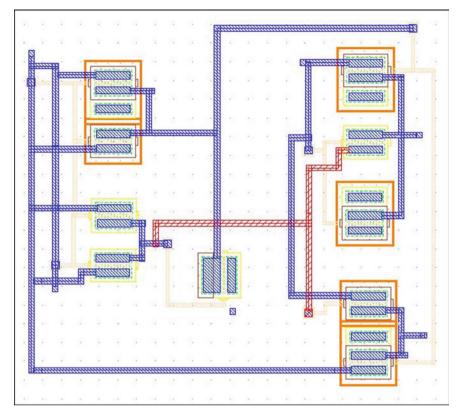

The layout design of full adder circuit using single-gate transistor logic is carried out by using Cadence Virtuoso tool at 180 nm technology, which is shown as Fig. 7.

Fig. 7 Layout design of full adder using SG transistor

All paths in all layers of the layout design are dimensioned in  $\lambda$  units, and subsequently,  $\lambda$  can be allocated an appropriate value compatible with the feature size of the fabrications process. This layout design follows layout design rules, i.e., sub-micron rules such as:

Min poly width  $(L) = 2\lambda$ Min spacing b/w poly  $= 2\lambda$ Width of contacts  $= 2\lambda$ Min metal to metal spacing  $= 3\lambda$ Min metal width  $= 3\lambda$  or  $4\lambda$ (w) Min width of diffusion  $= 6\lambda$ .

To check the correctness of design rules, design rule check (DRC) is done using Assura; it ensures that the layout passes through the rules designed for faultless fabrication followed by LVS (layout vs. schematic) that determines whether a particular circuit layout corresponds to the original schematic of the design.

## 4 Full Adder Design Using Double-Gate Transistor Logic

The designing of full adder using double-gate transistor logic (DG-MOSFET) technique is carried out by using the single-gate transistor logic design in an equivalent way. Each transistor in the circuit is configured and connected in a manner that their source terminal and drain terminal must be connected to each other. The two (front and back) gates of DG-MOSFET logic are electrically coupled which operates in symmetrical mode of operation. This mode of operation establishes connection between the terminals in a way that channel and gates get near to each other which in turn provides good control over conductance of the channel and reduces leakage.

Also, DG-MOSFET technique drastically reduces the short channel effects that occur in basic MOSFET devices which reduces the performance. This technique is preferable more since it possess better scalability even in nanometer range in digital circuits.

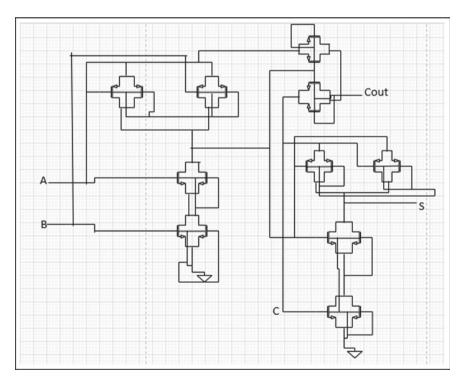

The schematic design of double-gate MOSFET-based full adder is shown in Fig. 8.

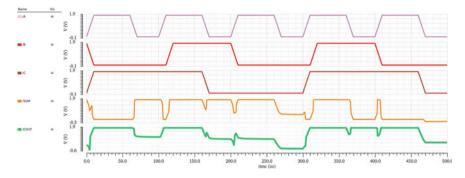

The transient response of proposed circuit is carried out using an EDA tool, i.e., Cadence Virtuoso tool at 180 nm technology which is shown in Fig. 9.

Fig. 8 Schematic design of full adder using DG-MOSFET

Fig. 9 Transient response of full adder using DG-MOSFET at 180 nm

## 5 Results and Observations

### 5.1 Average Power Consumption

The average power consumption for a CMOS circuit is described by the equation [9]:

$$P(\text{avg.}) = P(\text{dynamic}) + P(\text{leak}) + P(\text{short-circuit})$$

$$= \text{CLVddVfclk} + \text{IleakVdd} + \text{IscVdd}$$

From the above equation, it is clearly visible that the average dissipated depends upon different parameters such as current components (leakage + short-circuit), induced capacitance, and supply voltage. So, to lower the average power consumption, reducing the applied supply voltage will help. This concept will enhance the durability and overall performance of the MOSFET-based full adder circuit.

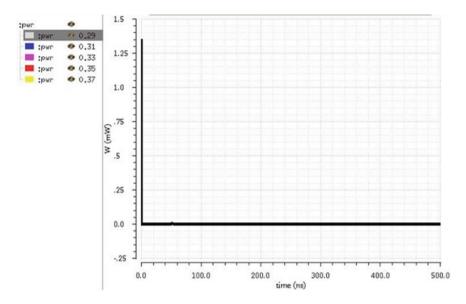

Figure 10 shows the graphical representation of power consumption against time (ns) taken at different levels of voltage, i.e., at 290, 310, 330, 350, 370 mV for double-gate MOSFET-based full adder circuit.

Figure 11 shows the numerical value of average power consumption in DG-based full adder circuit. This calculation is done using parametric analysis in EDA tool Cadence Virtuoso at 180 nm technology.

The average power consumption of double-gate MOSFET-based full adder calculated above is as follows:

$$P \text{avg}(\text{DG}) = 43.38\text{E} - 9$$

And the average power consumption of single-gate MOSFET-based full adder calculated using the same process of parametric analysis is as follows:

$$Pavg(SG) = 1.769E - 3$$

Fig. 10 Power consumption versus time in ns

| Ovt   Ovf   Ovdc   Ovs   Ocp Ovar                                                                                                                                                                                                    | Eile Edit View Icols Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | cādence |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Oit Oif Oidd Ois Oopt Omp                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| <pre>average(getData(":pur" ?result 'tran")) average(371,2E-3) average(v("/COUT" ?result "tran")) getData(":pur" ?result 'tran") getData(":pur" ?result 'tran") getData(":pur" ?result 'tran") getData(":pur" ?result 'tran") </pre> | Image: Weight of the second |         |

Fig. 11 Average power consumption

# 5.2 Variation of Power with Voltage

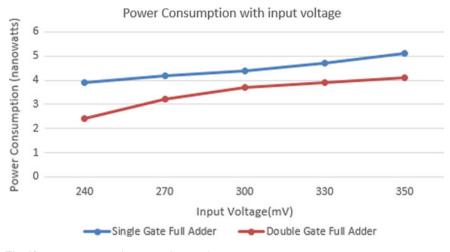

Figure 12 shows a graph of variation of power consumption with respect to input voltage of both single-gate and double-gate MOSFET-based full adder circuit.

From the graph, the percentage change in power consumption of SG and DG-MOSFET-based full adder circuit, it has been observed that the power consumption gets reduced by 22% in double gate logic circuit.

Fig. 12 Power consumption versus input voltage

## 6 Comparison Results of Parameters

| Parameters           | Conventional design | Proposed design           |

|----------------------|---------------------|---------------------------|

| Power (avg.)         | 71.4 µW (14T)       | 43.38 nW (10T)            |

| Tools and technology | Tanner EDA 13.0     | Cadence Virtuoso (180 nm) |

| Resistance           | More                | Less                      |

| Current (Ids) (µA)   | 0.018               | 0.015                     |

## 7 Conclusion

From the above observations and simulation results, it can be easily concluded that double-gate MOSFET-based full adder is way better suitable for the designing of digital devices than single-gate MOSFET based since DG based provides low power consumption, high speed, good scaling at low voltage range. These are most reliable devices that can be used for any microprocessors and other portable digital devices.

# References

- 1. Gupta SK (2011) Double gate MOSFET and its application for efficient digital circuits. In: 2011 IEEE

- Monisha A (2014) Performance and characteristic analysis of double gate MOSFET over single gate MOSFET. In: 2014 international conference on electronics and communication systems (ICECS—2014), Coimbatore

- 3. Vaddi R. Design and analysis of double gate MOSFETs for ultra low power radio frequency identification (RFID): device and circuit co-design. J Low Power Electron Appl

- 4. Moaiyeri MH, Mirzaee RF, Navi K (2009) Two new low-power and high performance full adders. J Comput 4

- Roy SM (2003) Leakage current mechanisms and leakage reduction techniques in deepsubmicron CMOS circuits. In: Proceedings of the IEEE 2003

- 6. Mishra S, Tomar SS, Akashe S (2013) Design low power l0T full adder using process and circuit techniques. In: Proceedings 7th international conference on intelligent systems and control

- 7. Lin J-F, Hwang Y-T, Sheu M-H (2012) Low power 10-transistor full adder design based on degenerate pass transistor logic. IEEE

- 8. Amara A, Parikh CD, Nagchoudhuri D (2011) A 0.7-V rail-to-rail buffer amplifier with doublegate MOSFETs. In: Faible tension faible consommation (FTFC). IEEE

- 9. Srivastava AK, Akashe S (2013) Design high performance and low power 10T full adder cell using double gate MOSFET at 45 nm technology. In: 2013 ICCCM

- Srivastava AK (2013) Comparative analysis of low power 10T and 14T full adder using double gate MOSFET at 45 nm technology. Int J Comput Appl 75(3). 0975-8887

- 11. Sharma S, Kumar P (2009) Non overlapped single and double gate SOI/GOI MOSFET for enhanced short channel immunity. J Semicond Technol Sci 9

- 12. Gupta SK, Pathak GG, Das D, Sharma C (2011) Double gate MOSFET and its application for efficient digital circuits. In: 3rd international conference on electronics computer technology (JCECT). IEEE

- 13. Sahani JK (2015) Design of full adder circuit using double gate MOSFET. In: 2015 fifth international conference on advance computing and communication technologies

- 14. Weste NHE, Harris D, Banerjee A (2011) CMOS VLSI design: a circuit and system perspective, 3rd edn. Pearson Education

- 15. Shyam Kishore G. A novel full adder with high speed low area. In: Proceedings of 2nd national conference on information and communication technology

- 16. Chiang TK (2005) A scaling theory for fully-depleted, SOI double-gate MOSFETs: including effective conducting path effect. Solid State Electron 49

- 17. Abbasalizadeh S, Forouzandeh B (2012) Full adder design with GDI cell and independent double gate transistor. In: 20th Iranian conference (ICEE), May 2012

- 18. Sharma S, Kumar P (2008) Optimizing effective channel length to minimize short channel effects in sub 50 nm single/DG SOI MOSFETs. J Semicond Technol Sci

- Srinivasa R, Scheinberg N. Short-circuit power dissipation estimation for CMOS logic gates. IEEE Trans Circuits Syst I Fundam Theory Appl 41

- 20. Colinge J-P (ed) (2008) FinFETs and other multi-gate transistors. Springer

- 21. Power-delay characteristics of CMOS adders. IEEE Trans VLSI Syst