# Analysis of Low-Power Cache Memory Design for Single Bit Architecture

161

**Reeya Agrawal**

Abstract This paper describes the analysis of low-power cache memory design for single bit architecture made up of six transistor static random access memory cell, write driver circuit, and voltage latch sense amplifier. At different values of resistance, consumption of power of cache memory design for single bit architecture has been analyzed. Process corner simulation and Monte Carlo simulation also have been done to check the robustness of the architecture. Conclusion arises that consumption of power decreases on increase in the value of resistance and 13.57  $\mu$ W consumption of power done by cache memory design for single bit static random access memory cell voltage latch sense amplifier design with 13.02  $\eta$ s.

**Keywords** Latch sense amplifier (LSA)  $\cdot$  Write driver circuit (WDC)  $\cdot$  Six transistor static random access memory (STSRAM)  $\cdot$  Voltage latch sense amplifier (VLSA)

# 1 Introduction

There are several memory elements within a system in contemporary computing systems, for example, main memory, cache memory, and register data [1–3]. With the latest development in the very large-scale integrated circuits (VLSI) technology, high-speed STSRAM is the industry's prime desire. Memory is the key component of a chip, and STSRAM is used as a cache memory because it is a fundamental part of memory that is important in data execution [4–6]. STSTRAM is a volatile memory since the information persists once the power is usable, which is essential and cannot be ignored in terms of reducing capacity in STSRAM. In an STSRAM architecture, the LSA is one of the elements of the data line. LSA is used to detect the difference in voltage at the input of the bit lines and to create a complete voltage swing at the output during the read operation [7]. Instead of having to measure or

R. Agrawal (🖂)

GLA University, Mathura, India

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2022 P. K. Chaurasiya et al. (eds.), *Technology Innovation in Mechanical Engineering*, Lecture Notes in Mechanical Engineering, https://doi.org/10.1007/978-981-16-7909-4\_15

wait for the swing voltage level, the memory will simply store '0' or '1' to save time while reading.

The demand for mobile devices and a battery-operated embedded system is growing with greater breadth as VLSI industries grow. Cache memory design for single bit architecture is a central part of memory that plays a key role in data execution, cache occupying 60% to 70% of chip region [8]. As chip consumption increases rapidly, microprocessor velocity is then decreased. One million transistors also increase and degrade the efficiency of single-chip failure rates, so the industry is working to build a low-speed and low-power memory circuit, which keeps the development of the VLSI system informed. In current high-performance microprocessors, more than half of transistors are for cache memories, and in the future, this proportion is projected to increase [9]. STSRAM is usually the option for built-in stock because it is robust in such chips in a noisy environment. The device can use necessary memory cells by integrating them in SRAMC that are the right size for system requirements. Memories time for access and power consumption are calculated primarily by the configuration of LSA. LSA is one of the most important peripheral circuits in memory systems [10].

| Year | Author                    | Features                                          | Sensing delay (ns) | Supply voltage (V) |

|------|---------------------------|---------------------------------------------------|--------------------|--------------------|

| 2002 | A Chrysanthopoulos et al. | Conventional sense amplifier                      | 7.1                | 2.5                |

| 2002 | A Chrysanthopoulos et al. | Clamped bit line<br>sense amplifier               | 0.35               | 2.5                |

| 2002 | KS. Yeo et al.            | Low-power current sense amplifier                 | 1.04               | 2.0                |

| 2002 | A Chrysanthopoulos et al. | Simple four transistor sense amplifier            | 1.85               | 2.5                |

| 2004 | Chun-lung Hsu et al.      | High-speed sense<br>amplifier                     | 0.51               | 1.8                |

| 2005 | Z. H. Kong et al.         | Ultralow-power                                    | 1.46               | 1.8                |

| 2007 | Sandeep Patil et al.      | Self-biased<br>charge-transfer sense<br>amplifier | 0.723              | 1.8                |

| 2008 | Ya-Chun Lai et al.        | Latch type sense amplifier                        | 0.33               | 1.8                |

| 2008 | Anh-Tuan Do et al.        | Fully current mode sense amplifier                | 0.38               | 1.8                |

| 2008 | Do Anh-Tuan et al.        | High-speed sense amplifier                        | 0.26               | 1.8                |

## 2 Literature Review

(continued)

| (continued) |

|-------------|

|             |

| Year | Author             | Features                    | Sensing delay (ns) | Supply voltage (V) |

|------|--------------------|-----------------------------|--------------------|--------------------|

| 2011 | Anh-Tuan Do et al. | Alpha latch sense amplifier | 0.566              | 1                  |

| 2011 | Anh-Tuan Do et al. | Decoupled sense amplifier   | 0.214              | 1                  |

## 3 Cache Memory Design for Single Bit Architecture

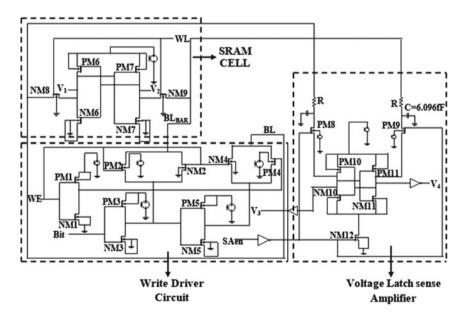

In this section, cache memory design for single bit architecture has been described with their design as shown in Fig. 1. Cache memory design for single bit architecture made up of WDC, STSRAM, and LSA [11, 12].

#### 3.1 Circuit of Write Driver

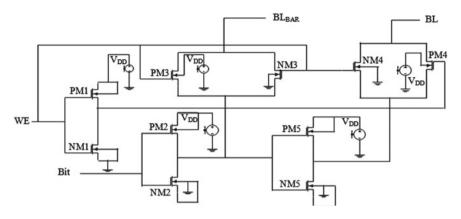

Figure 2 shows the circuit diagram of WDC. Each of the bit-lines in the STSRAM write driver circuit is quickly discharged from pre-charge stages to below the STSRAM write margin [13].

Fig. 1 Cache memory design for single bit STSRAM VLSA architecture schematic

Fig. 2 Write driver circuit schematic

The write enable (WE) signal usually activates the WDC, which uses full-swing discharge to drive the bit-line from the pre-charge level to the ground. Five  $P_{MOS}$  ( $P_{M1}$ ,  $P_{M2}$ ,  $P_{M3}$ ,  $P_{M4}$ , and  $P_{M5}$ ) as well as five  $N_{MOS}$  ( $N_{M1}$ ,  $N_{M2}$ ,  $N_{M3}$ ,  $N_{M4}$ , and  $N_{M5}$ ) are used by WDC. When allowed by WE, the input data causes one of the transistors to become  $P_{M1}$  or  $N_{M1}$  through inverters, and a strong 0 is applied by discharging BTL and BTL<sub>BAR</sub> from the pre-charge level to ground level [14].

#### 3.2 Six Transistor Static Random Access Memory Cell

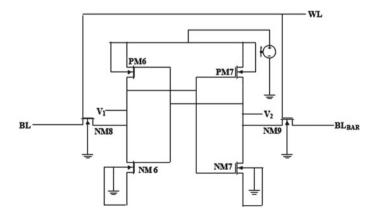

It is used for operations at low power, low voltage. Here, each bit is stored using bistable latching circuitry. Figure 3 shows the STSRAM cell schematic, the pull-up

Fig. 3 Six transistor static random access memory cell schematic

transistors are  $M_1$  and  $M_2$  ( $P_{MOS}$ ), while the driver transistors are  $M_3$  and  $M_4$  N<sub>MOS</sub>. These bit lines enhance the margin of noise. The value of measurable output voltage swings is given by differential circuitry. Logic 0 or 1 is stored as long as the power is on, but unlike DRAM cells [15, 16]; it does not need to be refreshed. In STSRAM architecture, the size of the transistors is most important for the proper operation of the transistors.

#### 3.3 Voltage Latch Sense Amplifier

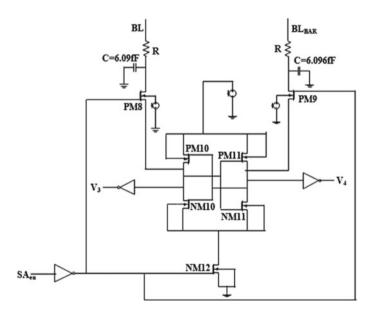

The voltage latch sense amplifier schematics developed in this work are shown in Fig. 4. Internal nodes are pre-charged via the bit-lines in this design. The architecture of the circuit runs directly via input bit lines, based on its internal nodes [17–20].

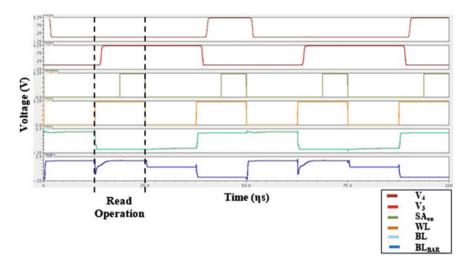

If the word line is high pulled and followed by the amplifier sensor trigger,  $NM_{12}$  is OFF, and  $PM_8$  and  $PM_9$  are ON. If the voltage difference in the bit-lines increases, the random bit in the internal nodes of the LSA varies accordingly in voltage. When the LSA signal  $SA_{EN}$  is claimed, the interlinking inverters consist of  $PM_{10}$ ,  $NM_{10}$ ,  $PM_{11}$ , and  $NM_{11}$  raise the voltage difference to the highest swing power [21–25] as shown in Fig. 5.

Fig. 4 Schematics of voltage latch sense amplifier

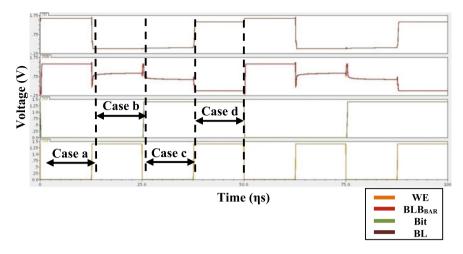

Fig. 5 WDC output waveform

## 4 Result Analysis

Figure 5 describes the output waveform of WDC, for cases arise: (a) when Bit = 0 V and WE = 0 V BTL =  $V_{DD}$  and BTL<sub>BAR</sub> =  $V_{DD}$ , (b) Bit = 0 V WE =  $V_{DD}$  so, BTL = 0 V and BTL<sub>BAR</sub> =  $V_{DD}/2$ , (c) Bit =  $V_{DD}$  WE = 0 V so, BTL = 0 V and BTL<sub>BAR</sub> =  $V_{DD}/2$  and (d) Bit =  $V_{DD}$  WE =  $V_{DD}$  so, BTL =  $V_{DD}$  and BTL<sub>BAR</sub> = 0 V.

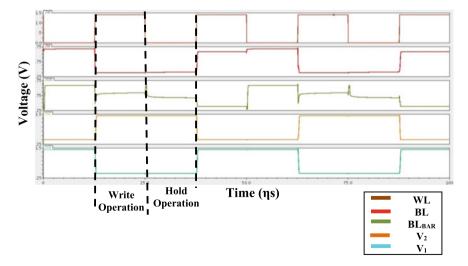

Figure 6 shows the output waveform of STSRAM which holds two operations:

Fig. 6 STSRAM cell output waveform

Fig. 7 Output waveform of VLSA

- 1. Write Operation

- 2. Hold Operation.

There are three types of transistors: (i) access transistors, (ii) pull-up transistor, and (iii) pull-down transistors. Figure 7 describes the read operation of VLSA when both  $SA_{EN} = 1$  and WL = 1 at that time sense amplifier works in read operation. Note:  $P = V^2/R$  as this voltage is constant on varying the R and analyzing the power consumption.

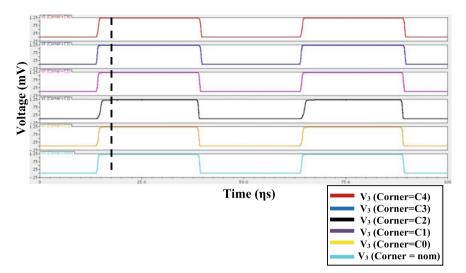

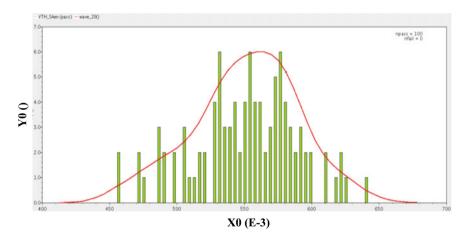

Figure 8 shows the process corner simulation of cache memory design for single bit architecture at six different corners, whereas Fig. 9 shows the Monte Carlo simulation for cache memory design for single bit architecture.

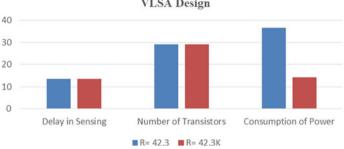

Table 1 depicts that consumption of power decreases as increase in value of resistance, whereas Fig. 10 shows the comparative analysis of different parameters of cache memory design for cache memory architecture using different values of resistance of Table 1 in form of a chart.

#### 5 Conclusion

In the proposed work, cache memory design for single bit architecture has been implemented, and on different values of resistance, different parameters of cache memory design for single bit architecture have been analyzed. To check the robustness of cache memory design for single bit architecture process corner simulation and Monte Carlo simulation also have been done. Furthermore, consumption of power of

Fig. 8 Process corner simulation

Fig. 9 Monte carlo simulation

Table 1

Analysis of different parameter of single bit SRAMC VLSA design

| S. No. | Parameters                 | Delay in sensing (ηs) | Number of transistors | Consumption of power $(\mu W)$ |

|--------|----------------------------|-----------------------|-----------------------|--------------------------------|

| 1      | $R = 42.3 \ \Omega$        | 13.50                 | 29                    | 36.57                          |

| 2      | $R = 42.3 \text{ K}\Omega$ | 13.50                 | 29                    | 14.32                          |

Different Parameter of Single Bit SRAMC VLSA Design

Fig. 10 Analysis of different parameter of single bit SRAMC VLSA design at different values of resistance

cache memory design for single bit architecture has been analyzed and the conclusion arises that consumption of power decreases on increasing resistance value (i.e., 14.32  $\mu$ W). In the future scope, this work can be implemented in form of an array.

#### References

- He, Y., Zhang, J., Wu, X., Si, X., Zhen, S., Zhang, B.: A half-select disturb-free 11T SRAM cell with built-in write/read-assist scheme for ultralow-voltage operations. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 27(10), 2344–2353 (2019)

- Fragasse, R., et al.: Analysis of SRAM enhancements through sense amplifier capacitive offset correction and replica self-timing. IEEE Trans. Circ. Syst. I Regul. Pap. 66(6), 2037–2050 (2019)

- Gupta, S., Gupta, K., Calhoun, B.H., Pandey, N.: Low-power near-threshold 10T SRAM bit cells with enhanced data-independent read port leakage for array augmentation in 32-nm CMOS. IEEE Trans. Circ. Syst. I Regul. Pap. 66(3), 978–988 (2019)

- Dounavi, H., Sfikas, Y., Tsiatouhas, Y.: Periodic aging monitoring in SRAM sense amplifiers. In: 2018 IEEE 24th International Symposium on On-Line Testing and Robust System Design (IOLTS), Platja d'Aro, pp. 12–16 (2018)

- Ahmad, S., Iqbal, B., Alam, N., Hasan, M.: Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Trans. Dev. Mater. Reliab. 18(3), 337–349 (2018)

- Reddy, B.N.K., Sarangam, K., Veeraiah, T., Cheruku, R.: SRAM cell with better read and write stability with minimum area. In: TENCON 2019–2019 IEEE Region 10 Conference (TENCON), pp. 2164–2167. Kochi, India (2019)

- Surkar, A., Agarwal, V.: Delay and power analysis of current and voltage sense amplifiers for SRAM at 180 nm technology. In: 2019 3rd International Conference on Electronics, Communication, and Aerospace Technology (ICECA), pp. 1371–1376. Coimbatore, India (2019)

- Tripti, T., Chauhan, D.S., Singh, S.K., Singh, S.V.: Implementation of low-power 6T SRAM cell using MTCMOS technique. In: Advances in Computer and Computational Sciences, Springer, Singapore (2017)

- Geetha Priya, M., Baskaran, K., Krishnaveni, D.: Leakage power reduction techniques in deep submicron technologies for VLSI applications. Int. Conf. Commun. Technol. Syst. Des. (2011)

- Sridhara, K., Biradar, G.S., Yanamshetti, R.: Subthreshold leakage power reduction in VLSI circuits: a survey. In: 2016 International Conference on Communication and Signal Processing (ICCSP), pp. 1120–1124 (2016)

- Gnana Deepika, K., Mariya Priyadarshini, K., David Solomon Raj, K.: Sleepy keeper approach for power performance tuning in VLSI design. Int. J. Electron. Commun. Eng. 6(1), 17–28 (2013). ISSN 0974-2166

- 12. Gomes Iuri, A.C., Cristina, M., Butzen Paulo, F.: Design of 16 nm SRAM architecture. In: South Symposium on Microelectronics (2012)

- Sri Harsha Kaushik, C., Vanjarlapati, R.R., Krishna, V.M., Gautam, T., Elamaran, V.: VLSI design of low power SRAM architectures for FPGAs. In: 2014 International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE), pp. 1–4 (2014)

- Choudhary, R., Padhy, S., Rout, N.K.: Enhanced robust architecture of single bit SRAM cell using drowsy cache and super cut-off CMOS concept. Int. J. Ind. Electron. Elect. Eng. 3, 63–68 (2011)

- Gajjar, J.P., Zala, A.S., Aggarwal, S.K.: Design and analysis of 32-bit SRAM architecture in 90 nm CMOS technology 03(04), 2729–2733 2016

- Agrawal, R., Tomar, V.K.: Analysis of Cache (SRAM) Memory for Core I TM 7 Processor. In: 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), p. 402 (2018)

- Vanama, K., Gunnuthula, R., Prasad, G.: Design of low power stable SRAM cell. In: 2014 International Conference on Circuit Power and Computing Technologies (ICCPCT), pp. 1263– 1267 (2014)

- Chandankhede, R.D., Acharya, D.P., Patra, P.K.: Design of high-speed sense amplifier for SRAM. In: IEEE International Conference on Advanced Communication Control and Computing Technologies, pp. 340–343

- 19. Wei, Z., Peng, X., Wang, J., Yin, H., Gong, N.: Novel CMOS SRAM voltage latched sense amplifiers design based on 65 nm Technology, pp. 3281–3282

- Wang, Y., Zhao, F., Liu, M., Han, Z.: A new full current-mode sense amplifier with compensation circuit. In: 2011 9th IEEE International Conference on ASIC, Xiamen, pp. 645–648 (2011)

- Eslami, N., Ebrahimi, B., Shakouri, E., et al.: A single-ended low leakage and low voltage 10T SRAM cell with high yield. Analog Integr Circ Sig Process (2020)

- 22. Bazzi, H., Harb, A., Aziza, H., et al.: RRAM-based non-volatile SRAM cell architectures for ultra-low-power applications. Analog Integr Circ. Sig. Proc. (2020)

- 23. Pal, S., Bose, S., Islam, A.: Design of SRAM cell for low power portable healthcare applications. Microsyst Technol. (2020)

- Shah, A.P., Vishvakarma, S.K., Hübner, M.: Soft Error hardened asymmetric 10T SRAM cell for aerospace applications. J. Electron. Test 36, 255–269 (2020)

- 25. Singh, S., Mishra, V.: Enhanced static noise margin and increased stability SRAM cell with emerging device memristor at 45-nm Technology **61**, 200–206 (2018)