**Energy Systems in Electrical Engineering**

Rohit Dhiman Rajeevan Chandel *Editors*

# Nanoscale VLSI

**Devices, Circuits and Applications**

# **Energy Systems in Electrical Engineering**

Series Editor

Muhammad H. Rashid, Florida Polytechnic University, Lakeland, USA

More information about this series at http://www.springer.com/series/13509

Rohit Dhiman · Rajeevan Chandel Editors

# Nanoscale VLSI

Devices, Circuits and Applications

*Editors* Rohit Dhiman Department of Electronics and Communication Engineering National Institute of Technology Hamirpur (HP) Hamirpur, Himachal Pradesh, India

Rajeevan Chandel Department of Electronics and Communication Engineering National Institute of Technology Hamirpur (HP) Hamirpur, Himachal Pradesh, India

ISSN 2199-8582 ISSN 2199-8590 (electronic) Energy Systems in Electrical Engineering ISBN 978-981-15-7936-3 ISBN 978-981-15-7937-0 (eBook) https://doi.org/10.1007/978-981-15-7937-0

#### © Springer Nature Singapore Pte Ltd. 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore To my revered Parents, for their affection and untiring efforts in my upbringing. Also dedicated to my wife, Anjali, and our loving daughter, Shipra Dhiman, for their precious time and patience.

-Rohit Dhiman

My loving family, Prof. Ashwani Kumar Chandel, our dear son, Ayush Chandel, and very affectionate daughter-in-law, Nilanshi. My respected mother, mother-in-law & teachers and dear students who have always been a source of my continued efforts for academic excellence.

-Rajeevan Chandel

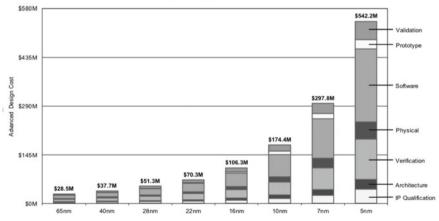

## Preface

The perpetual scaling of complementary metal-oxide semiconductor (CMOS) technology has resulted in significant performance improvements in very large-scale integration (VLSI) circuit design techniques and system architectures. According to ITRS, Intel's next-generation *i*8 billion transistor processors have set out to achieve an industry leading performance of the order of GHz. This trend is expected to continue in future also, but will require breakthroughs in the design of nanoscale VLSI and post-CMOS technologies, generally known as nanoelectronics. With the development of novel materials and nanoscale devices, research is being directed to gain better physical insights of the parameters that influence the device, circuit, and system characteristics. This book titled, Nanoscale VLSI: Devices, Circuits and Applications, is written by such researchers in the respective areas of nanoelectronic devices, integrated circuits (ICs), nanomagnetic computation, and other relevant areas. The 15 chapters of the book are classified under four parts that cover modeling, simulation, and applications of electronic, magnetic, and compound semiconductors in the nanoscale VLSI devices, circuits, and systems. This comprehensive volume eloquently presents the design methodologies for ultra-low-power VLSI design, potential post-CMOS devices, and circuits and their applications from the architectural and system perspective. The book shall serve as an invaluable reference book for the graduate students, Ph.D./M.S./M.Tech. scholars, researchers, and practicing engineers working in the frontier areas of nanoscale VLSI design of devices, circuits, systems, and their applications.

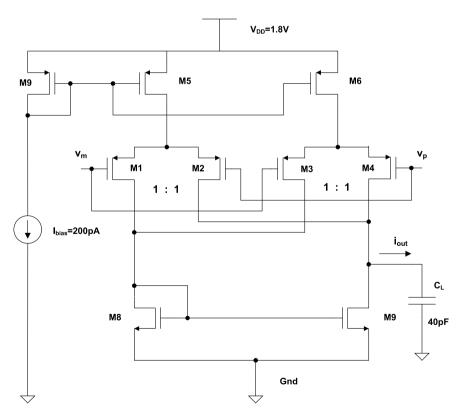

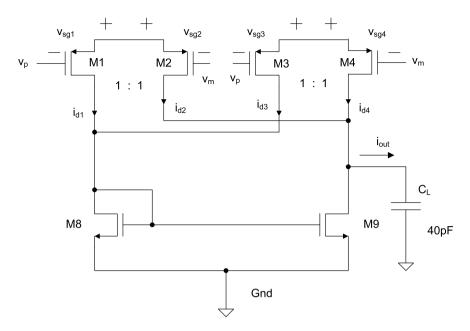

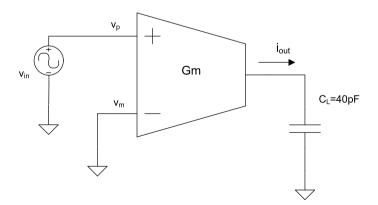

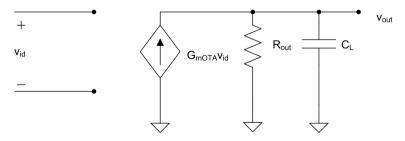

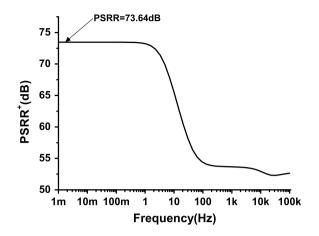

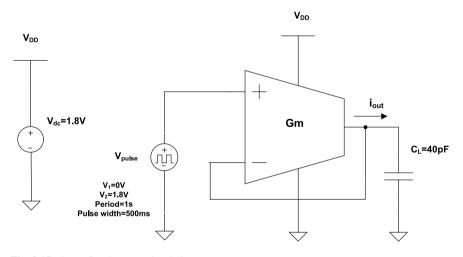

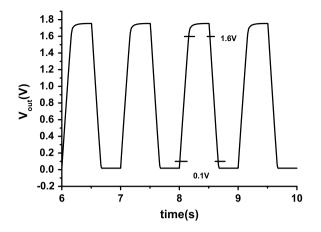

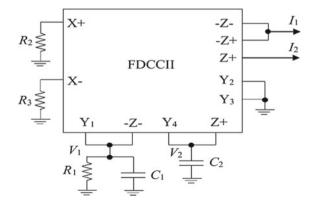

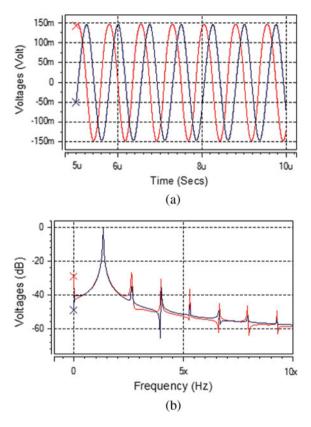

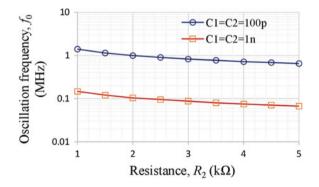

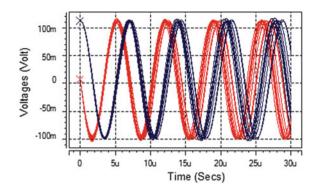

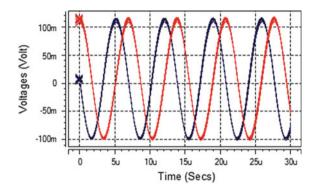

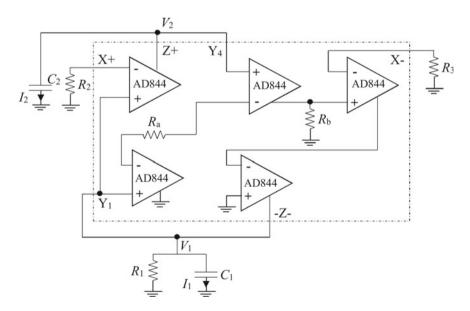

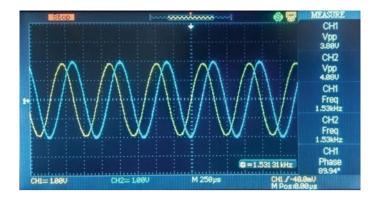

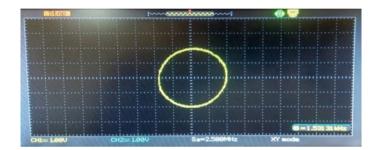

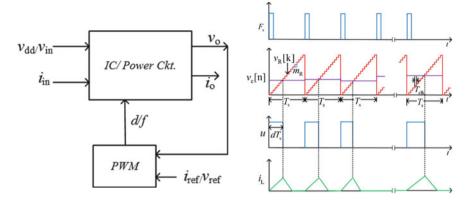

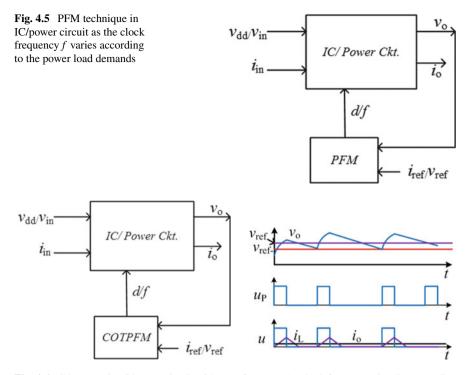

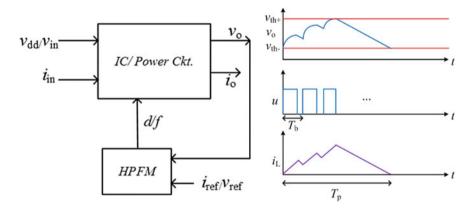

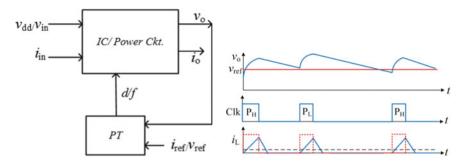

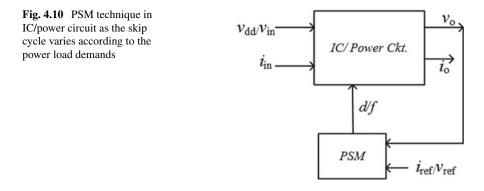

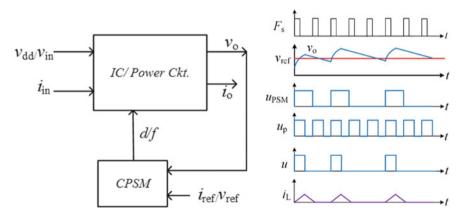

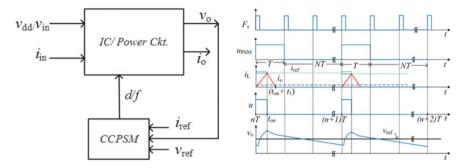

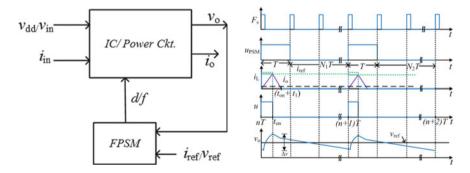

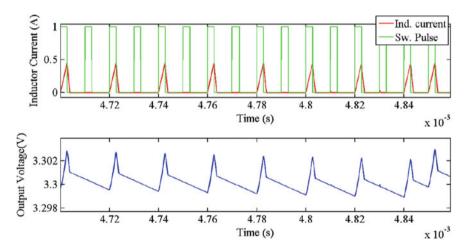

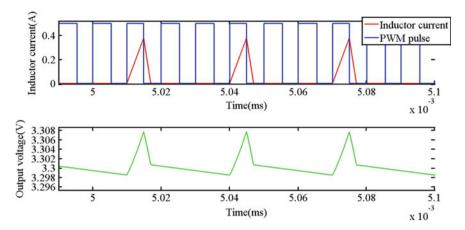

The first part of the book addresses the importance of low voltage and low power in current IC design. Chapter 1: Low-Voltage Analog Integrated Circuit Design, of the book deals with detailed insights about the low-voltage design techniques for analog ICs. In the modern ultra-low-power analog CMOS design, sub-threshold current is utilized as the driving current. Chapter 2: Design Methodology for Ultra-Low-Power CMOS Analog Circuits for ELF-SLF Applications, explores a systematic design methodology based on the inversion coefficients for the design of an operational transconductance amplifier, suitable for extreme low-frequency (ELF) regime. Chapter 3: Orthogonally Controllable Versatile Quadrature Oscillator for Low-Voltage Applications, introduces a dual-mode quadrature oscillator circuit comprising of a single fully differential current conveyor with three grounded resistors and two grounded capacitors. Practical realization of the proposed quadrature oscillator using commercially available ICs has also been illustrated. It is essential to retain power and energy efficiency in ICs over a wide range of load current and voltage. Chapter 4: Design Techniques for Low-Power Integrated Circuits, discusses pulse width modulation, pulse frequency modulation, and pulse skip modulation that result in reduced power dissipation and improved energy efficiency in power ICs.

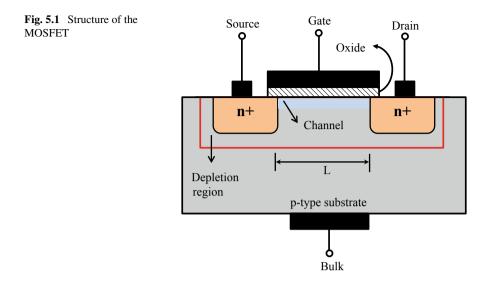

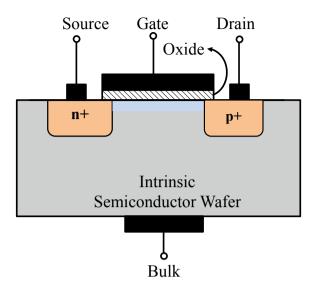

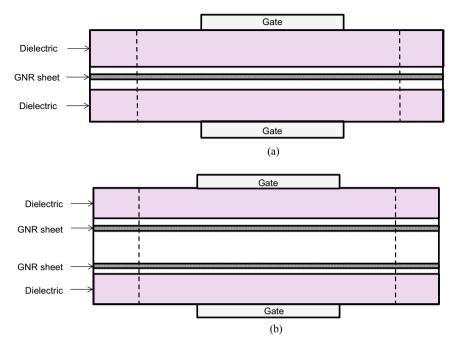

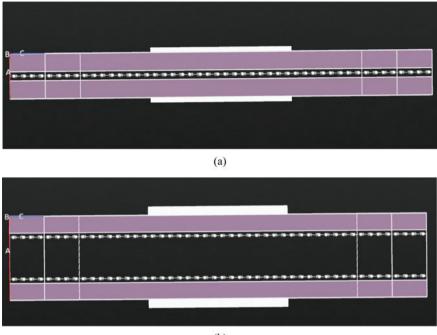

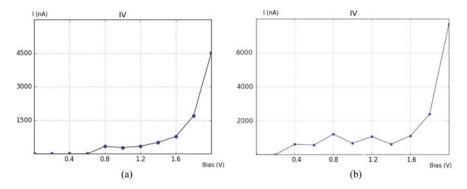

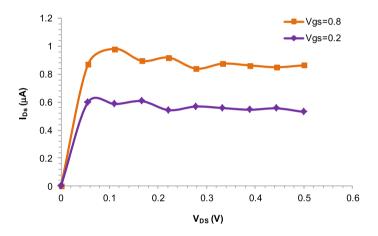

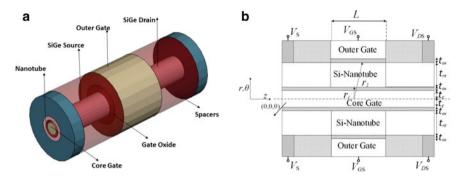

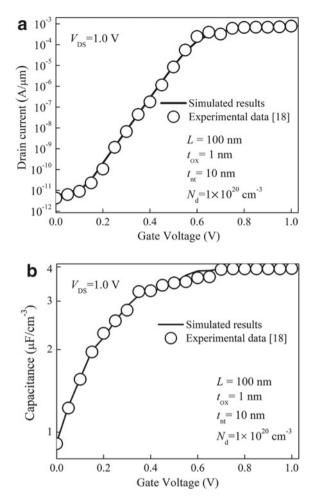

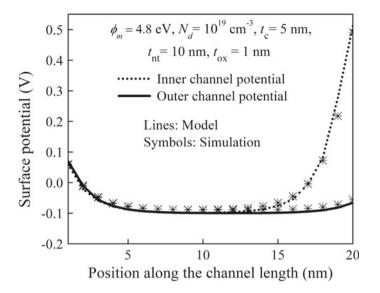

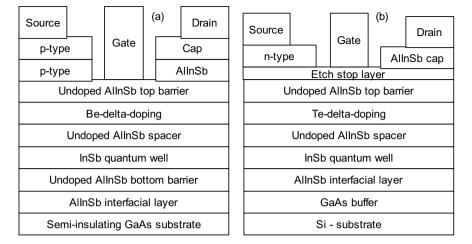

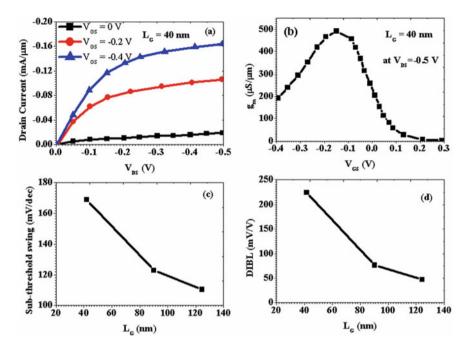

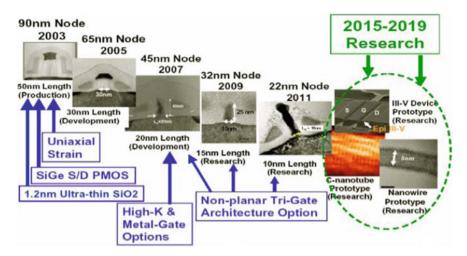

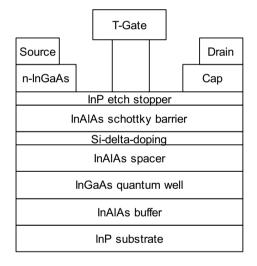

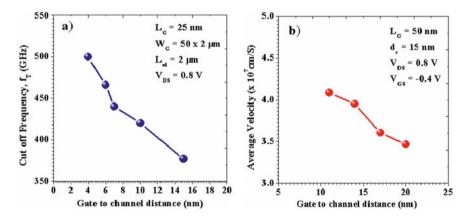

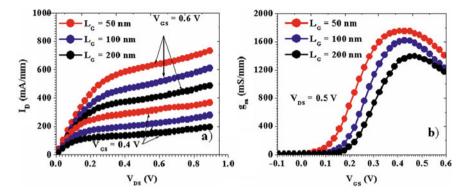

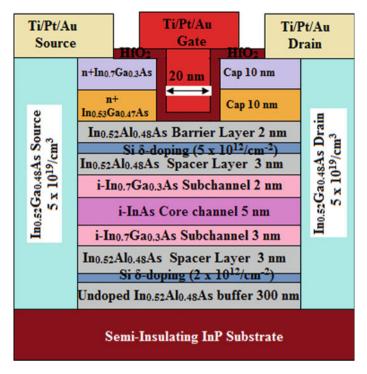

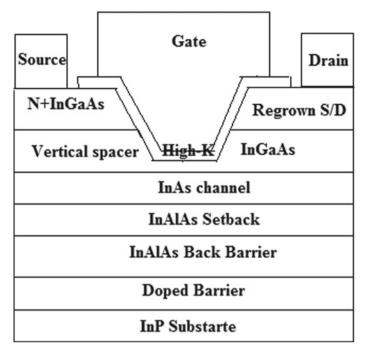

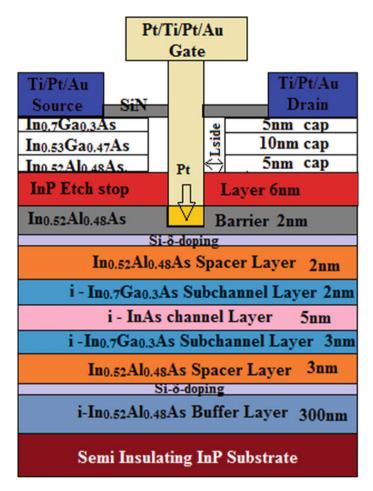

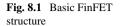

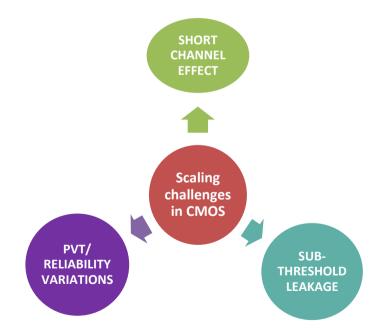

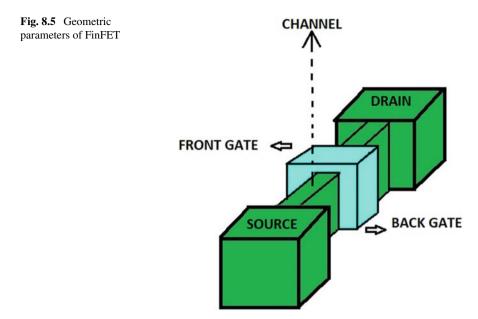

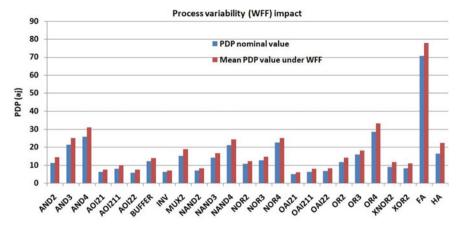

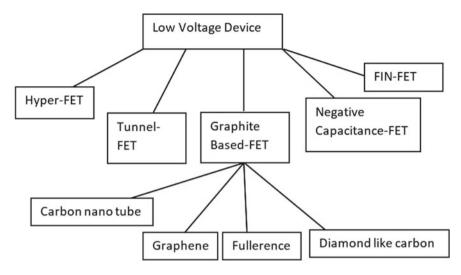

With the advancements in CMOS scaling, the power density constraint puts a limit on the number of transistors that can be simultaneously switched on. Therefore, to exploit full benefits of scaling, novel post-CMOS devices are extensively investigated and covered in the second part of the book. The application of bilayer (BL) graphene nanoribbon (GNR)-based tunnel field-effect transistor (TFET) for its potential applications in post-CMOS electronics is provided in Chap. 5: Bilayer Graphene Nanoribbon Tunnel FET for Low-Power Nanoscale IC Design. It also covers a comprehensive description of BL-GNR TFET as a potential alternative to monolayer GNR TFETs due to its high ON-state current and low sub-threshold swing. The incorporation of compound semiconductors like InAs, InGaAs, InSb, SiGe that have outstanding carrier transport properties has opened up new vistas to the device designers with faster and better device performance. The impressive potential of SiGe source/drain Si-nanotube junctionless FET for reduced short-channel effects and its threshold voltage behavior is explored in Chap. 6: A Threshold Voltage Model for SiGe Source/Drain Silicon-Nanotube-Based Junctionless Field-Effect Transistor. In Chap. 7, the architecture and electrical performance of III-V nanoscale quantum well FETs for high performance, low-power solid-state IC technology is presented. FinFET technology has seen a major increase in the adoption for use within ICs with faster and better performance. However, process variability is detrimental and can affect the performance of FinFET. Chapter 8: FinFET-A Beginning of Non-planer Transistor Era, elucidates the influence of work function fluctuations on various FinFET-based logic circuits.

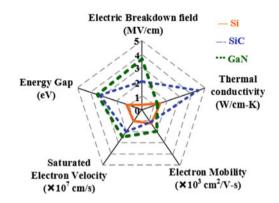

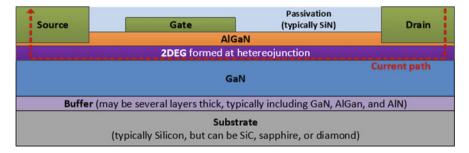

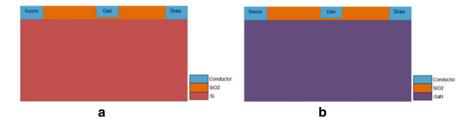

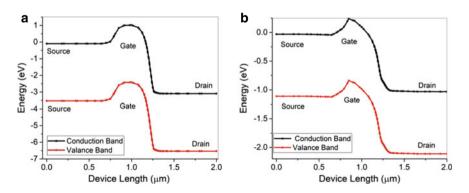

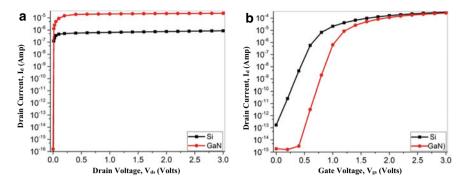

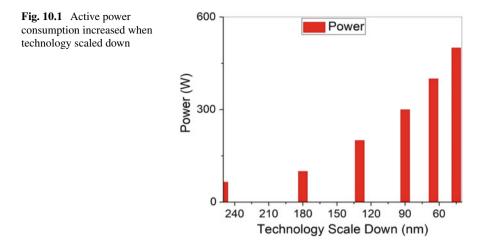

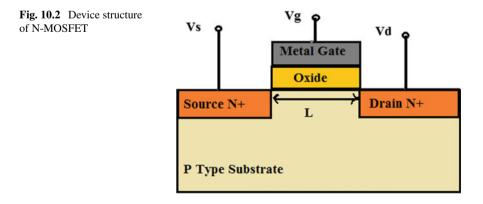

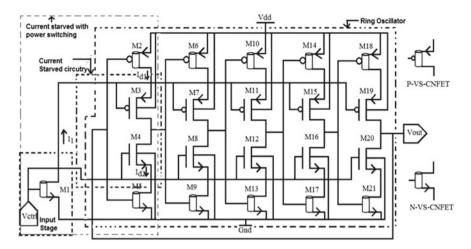

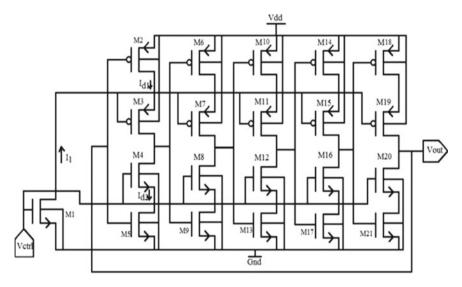

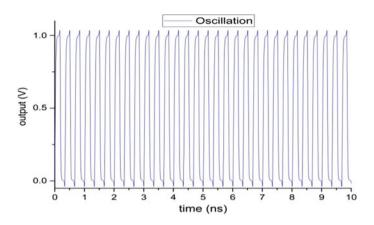

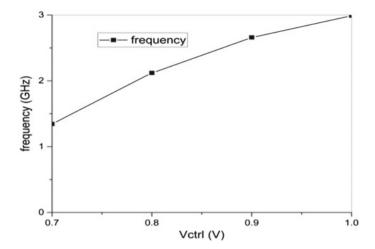

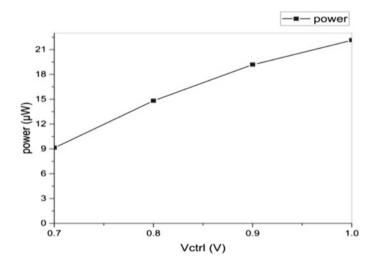

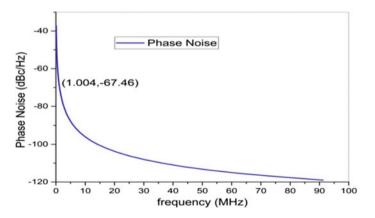

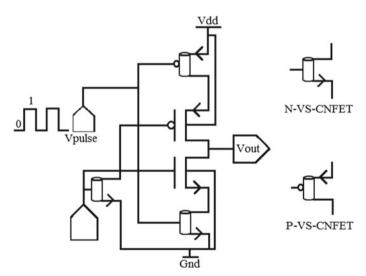

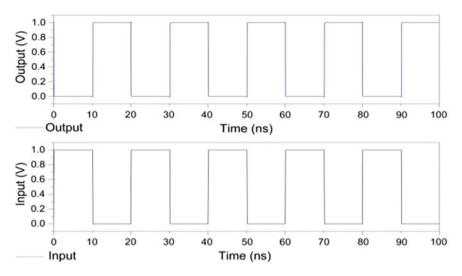

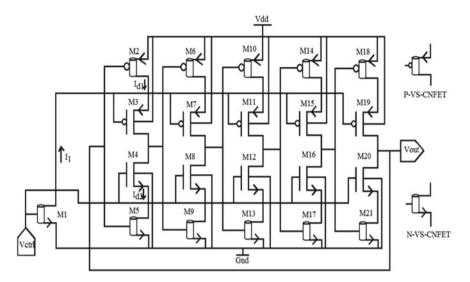

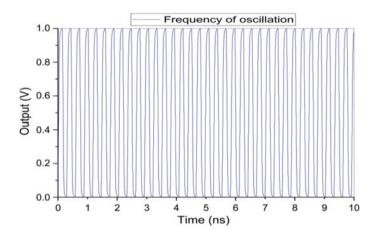

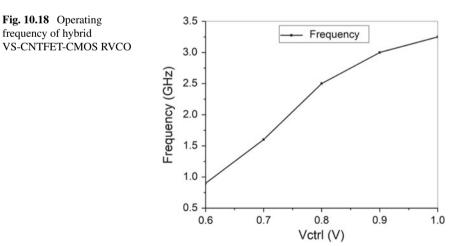

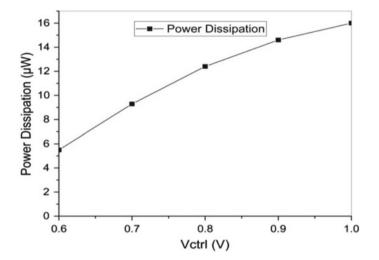

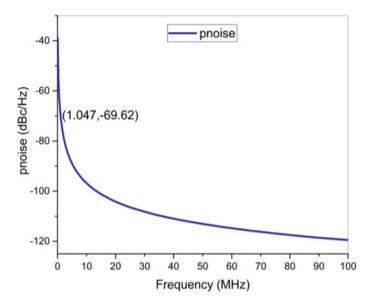

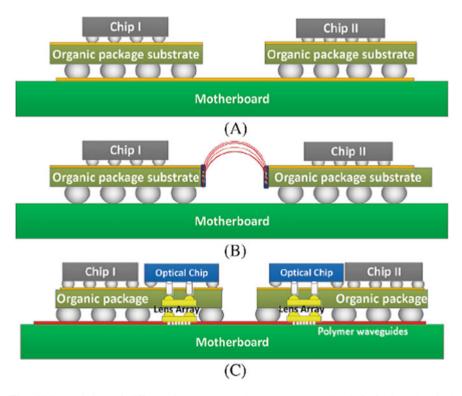

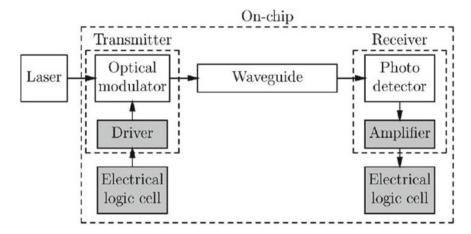

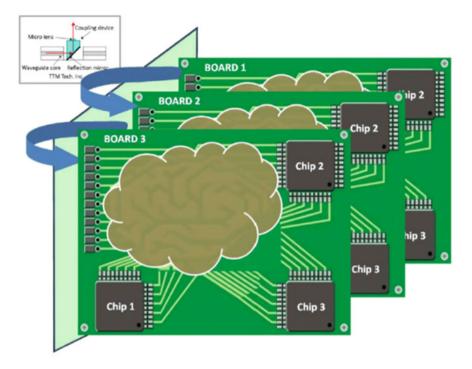

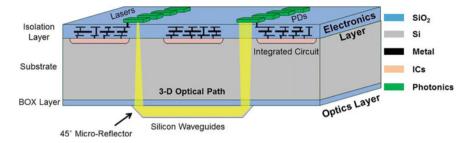

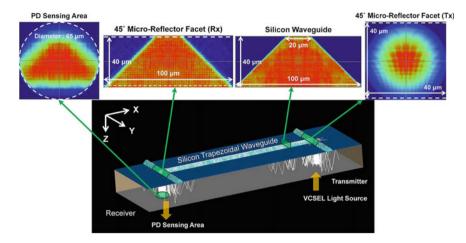

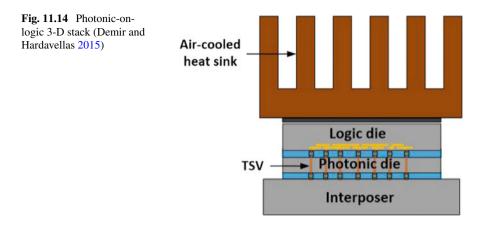

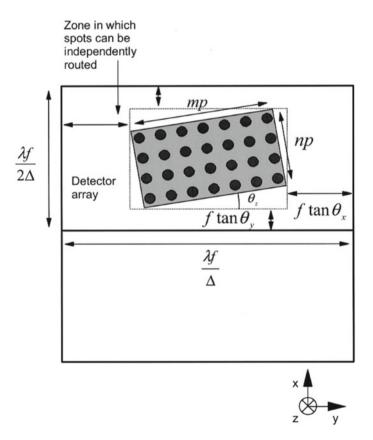

The third part of the book provides the possibilities of IC design with some emerging technologies and addresses the challenges that still need to be addressed. Recently, gallium nitride (GaN) has gained tremendous attention due to its high band gap energy and high electric breakdown voltage. This part of the book provides physical insights about the GaN technology and its design space exploration in Chap. 9, Gallium Nitride: Emerging Future Technology for Low-Power Nanoscale IC Design. Voltage-controlled oscillator (VCO) plays a significant role in the realization of phase-locked loop, radio frequency ICs, analog-to-digital converter, and other circuits. In Chap. 10: A Low-Power Hybrid VS CNTFET-CMOS Ring Voltage-Controlled Oscillator using Current Starved Power Switching Technology, a ring VCO is designed using a virtual source carbon nanotube (CNT) FET, CMOS, and current starved power switching technology. In today's sophisticated nano-era and densely packed IC designs, on-chip interconnects determine the overall performance of VLSI circuits and systems. Novel

Preface

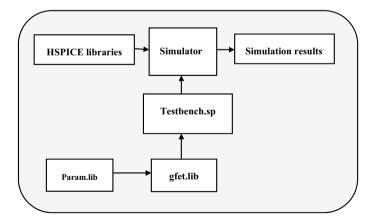

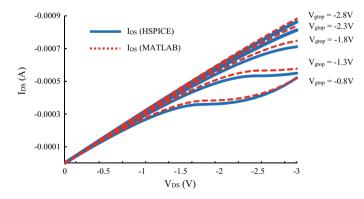

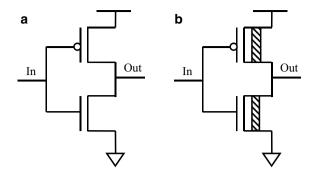

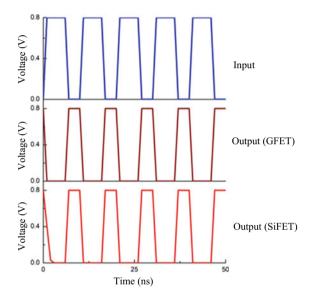

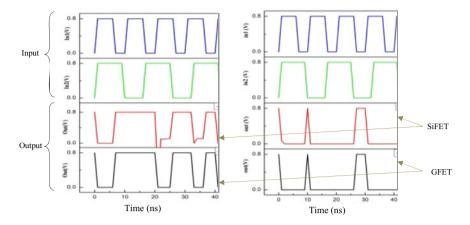

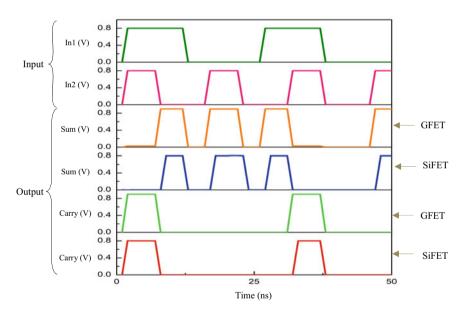

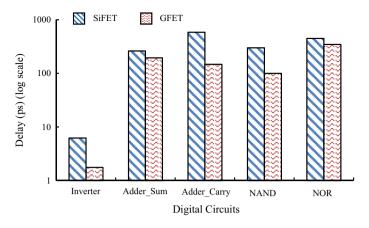

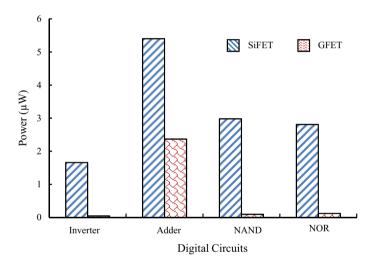

optical interconnects promise many attractive features which make these the most prominent interconnect technology in future silicon-on-insulator chips. The readers can explore some research aspects of optical interconnects in Chap. 11: Chip-Level Optical Interconnect in Electro-optics Platform, of the book. Accurate analytical modeling and simulation of graphene FET for the realization of VLSI circuits is reported in Chap. 12: Emerging Graphene FETs for Next-Generation IC Design.

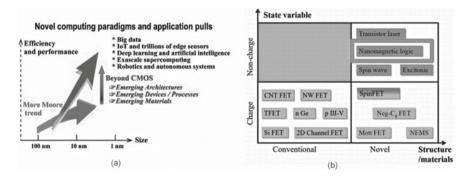

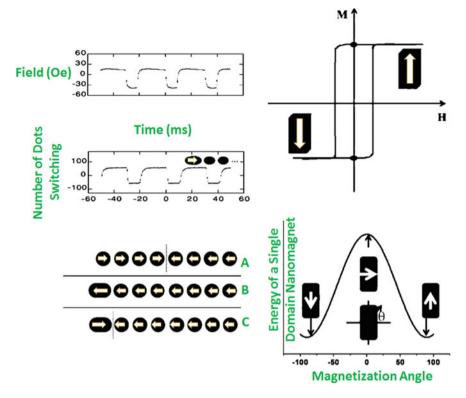

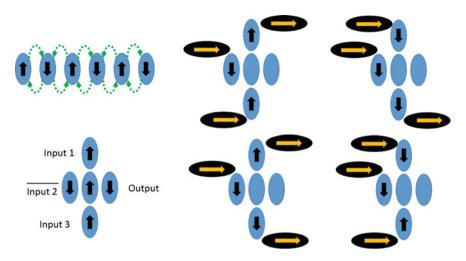

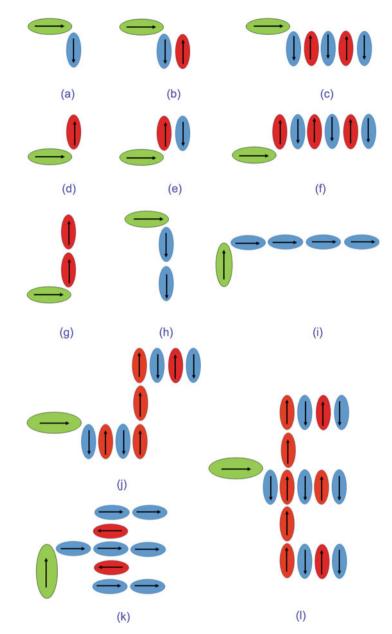

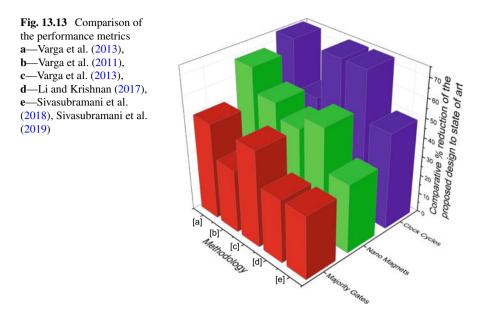

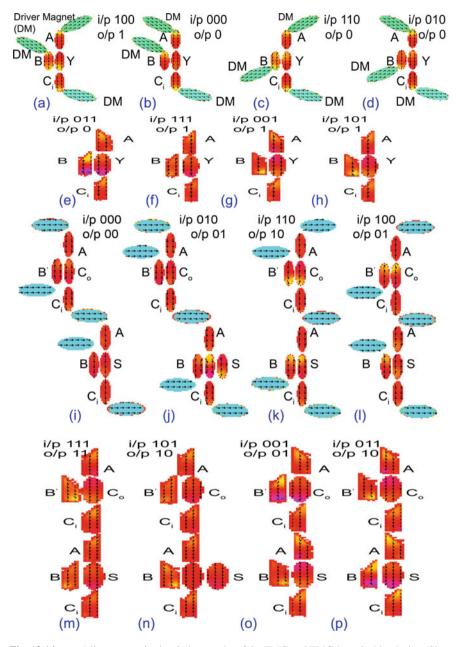

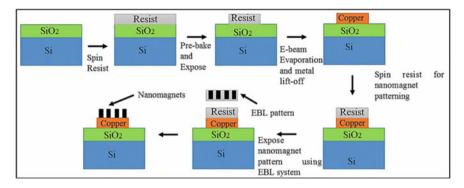

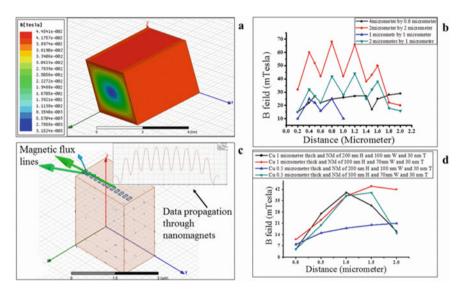

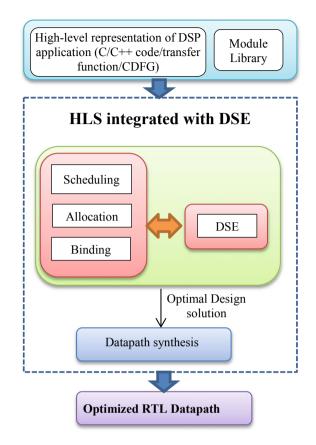

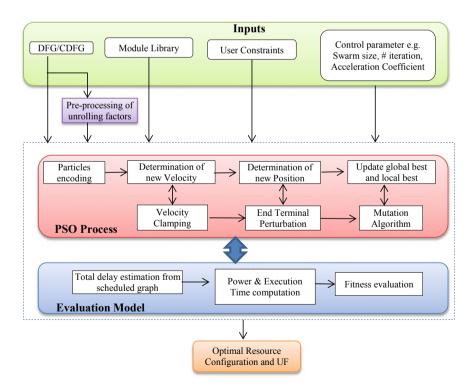

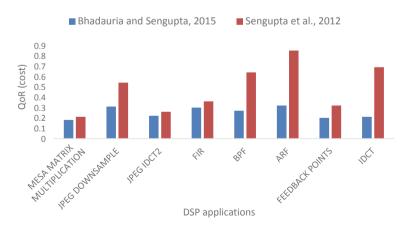

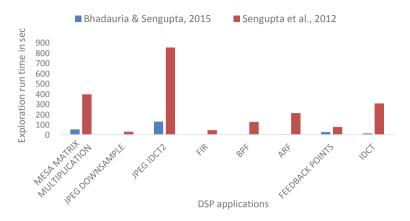

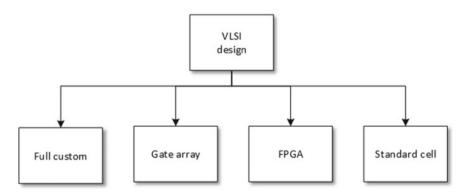

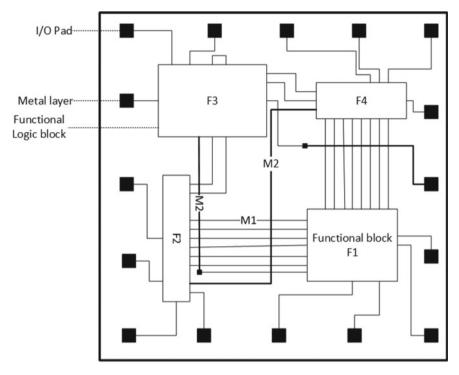

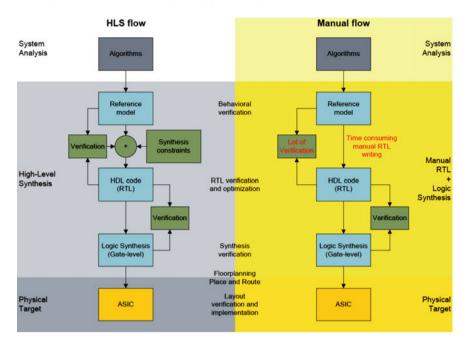

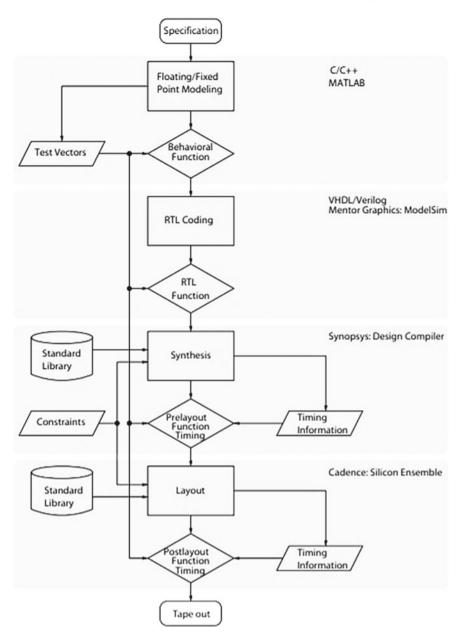

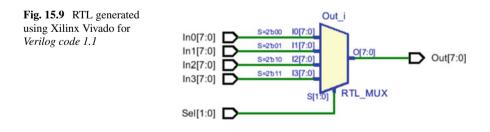

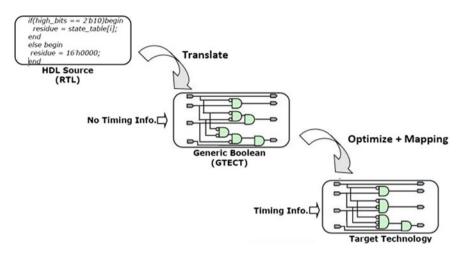

Over the years, a rapid growth has been witnessed in semiconductor industry because of the huge demand for system level designs. System level designs are prominently used for the various applications such as high-performance computing. control system, telecommunications, image and video processing, consumer electronics, and others. To address this, a holistic approach from the architectural and system perspective is required and is addressed in the last part of the book. The adverse effects of More than Moore and emerging demands of computing on the edge devices necessitate a significant improvement in the energy and area-efficient rebooting computing architecture design. Chapter 13: Power and Area-Efficient Architectural Design Methodology for Nanomagnetic Computation, discusses nanoscale architecture design and its implementation using nanomagnets. This chapter also throws light on graphene-based on-chip clocking interconnect replacing the traditional copper. The VLSI design process of digital signal processing (DSP) hardware is dependent on high-level synthesis framework that comprises of design space exploration of power and area-delay tradeoff and is addressed in Chap. 14: Design Space Exploration of DSP Hardware using Adaptive PSO and Bacterial Foraging for Power/Area-Delay Tradeoff. The part concludes with Chap. 15: Register-Transfer-Level Design for Application-Specific Integrated Circuits.

This book is a unique coverage of topics covering recent advancements in the field of post-CMOS IC design, modeling and simulation, and other potential research areas for the efficient design exploration of low voltage, low power, VLSI devices, circuits, and their applications at the system level.

Hamirpur, India

Rohit Dhiman Rajeevan Chandel

Acknowledgements We would like to express our heartfelt gratitude to the authors of the individual chapters who have devoted their significant time and contributed their expertise to shape the book. We express our sincere thanks to all the authors for their excellent insights, as we are sure that this edited volume will be a useful text to many readers interested in nanoscale VLSI devices, circuits, and their applications. We are grateful to the Editorial team of the Springer for its tremendous support through the stages of preparation and finally bringing out this book as an excellent academic treasure to its readers.

# Contents

| Part | t I Low Voltage and Low Power VLSI Design                                                                                                                     |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1    | Low-Voltage Analog Integrated Circuit Design<br>Deepika Gupta                                                                                                 | 3   |

| 2    | Design Methodology for Ultra-Low-Power CMOS Analog<br>Circuits for ELF-SLF Applications                                                                       | 23  |

| 3    | <b>Orthogonally Controllable VQO for Low-Voltage Applications</b><br>Bhartendu Chaturvedi, Jitendra Mohan, and Atul Kumar                                     | 45  |

| 4    | Low Power Design Techniques for Integrated Circuits<br>Bipin Chandra Mandi                                                                                    | 65  |

| Part | t II Modeling and Simulation for Post-CMOS Devices                                                                                                            |     |

| 5    | Bilayer Graphene Nanoribbon Tunnel FET for Low-PowerNanoscale IC DesignVobulapuram Ramesh Kumar, Uppu Madhu Sai Lohith,Shaik Javid Basha, and M. Ramana Reddy | 83  |

| 6    | A Threshold Voltage Model for SiGe Source/Drain<br>Silicon-Nanotube-Based Junctionless Field-Effect Transistor<br>Anchal Thakur and Rohit Dhiman              | 101 |

| 7    | III-V Nanoscale Quantum-Well Field-Effect Transistorsfor Future High-Performance and Low-PowerLogic ApplicationsJ. Ajayan and D. Nirmal                       | 113 |

| 8    | FinFET: A Beginning of Non-planar Transistor Era<br>Kajal and Vijay Kumar Sharma                                                                              | 139 |

| Co | nte | nts |

|----|-----|-----|

|    |     |     |

| Par | t III Emerging Technologies for Integrated Circuits                                                                                                                                          |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9   | Gallium Nitride—Emerging Future Technology for Low-Power<br>Nanoscale IC Design                                                                                                              | 163 |

| 10  | A Low-Power Hybrid VS-CNTFET-CMOS Ring<br>Voltage-Controlled Oscillator Using Current Starved Power<br>Switching Technology<br>Ashish Raman, Vikas Kumar Malav, Ravi Ranjan, and R. K. Sarin | 173 |

| 11  | <b>Chip-Level Optical Interconnect in Electro-optics Platform</b><br>Sajal Agarwal and Y. K. Prajapati                                                                                       | 203 |

| 12  | Emerging Graphene FETs for Next-Generation Integrated<br>Circuit Design                                                                                                                      | 225 |

| Par | t IV System Level Applications                                                                                                                                                               |     |

| 13  | Power and Area-Efficient Architectural Design Methodology<br>for Nanomagnetic Computation                                                                                                    | 241 |

| 14  | <b>Design Space Exploration of DSP Hardware Using Adaptive PSO</b><br><b>and Bacterial Foraging for Power/Area-Delay Trade-Off</b><br>Anirban Sengupta, Mahendra Rathor, and Pallabi Sarkar  | 271 |

| 15  | Register-Transfer-Level Design for Application-SpecificIntegrated CircuitsDilip Singh and Rajeevan Chandel                                                                                   | 295 |

### **About the Editors**

**Rohit Dhiman** received his B.Tech. in Electronics and Communication Engineering from HP University Shimla, India in 2007. He did his M.Tech. Degree in VLSI Design from National Institute of Technology (NIT) Hamirpur in 2009. He was awarded Ph.D. Degree from NIT Hamirpur in 2014. Presently Dr. Rohit Dhiman is working as an Assistant Professor in Electronics and Communication Engineering Department at NIT Hamirpur and is the author/co-author of Research Publications in International Journals and Conference proceedings of repute. He has also edited/ authored three books published by the IET and Springer. He has been awarded with the *Young Scientist Award* from the Science and Engineering Research Board, Department of Science and Technology GoI, New Delhi. He is recipient of the prestigious *Young Faculty Research Fellowship* of the Ministry of Electronics and Information Technology (MeitY), Government of India and has two sponsored research projects to his credit. His major research interest is in device and circuit modelling for low power nanoscale IC design.

Rajeevan Chandel received B.E. Degree in E&CE from Thapar Institute of Engineering and Technology (now Thapar University), Patiala, India in 1990. She is a double gold medalist of Himachal Pradesh University, Shimla in Pre-University and Pre-Engineering in 1985 and 1986 respectively. She did her M.Tech. Degree in Integrated Electronics and Circuits, from Indian Institute of Technology (IIT) Delhi in 1997. She was awarded Ph.D. Degree from IIT Roorkee, India in 2005. Dr. Chandel joined Department of E&CE, NIT Hamirpur as Lecturer in 1990, where presently she is working as Professor. Dr. Chandel has been Head of the E&CE Department twice and was formerly Dean (Research & Consultancy) at NIT Hamirpur. She has over 150 research papers in peer reviewed International Journals of repute and Conferences. She has six sponsored projects to her credit from Government of India. Currently, she is the Chief Investigator of the prestigious SMDP-C2SD project of MeitY, New Delhi. She has also edited/authored three books of IET and Springer. Her research interests are electronics circuit modelling and low power VLSI design. She is a Fellow of IETE (I) and life member of ISTE (I) and member of IEEE, ISSS and VSI.

# Part I Low Voltage and Low Power VLSI Design

# Chapter 1 Low-Voltage Analog Integrated Circuit Design

#### Deepika Gupta

**Abstract** In this chapter, we review the challenges and effective design techniques for ultra-low-power analog integrated circuits. With the miniaturization, having lowpower low-voltage mixed signal IC is essential to maintain the electric field in the device. This constraint presents bottleneck for the researchers to design robust analog circuits. Specifically, the low value of supply voltage with small technology influences many specifications of analog IC, e.g., power supply rejection, dynamic range and immunity to noise, etc. In addition, it also affects the ability of the MOS transistor to be operated in the strong inversion region. Note that with the technology reduction, power supply  $V_{DD}$  is reducing but the threshold voltage  $V_T$  is not decreasing proportionally to maintain low leakage current. However, this process reduces the overdrive voltage and limits the staking of transistors. In this case, the transistor can be made to work in weak inversion to work and reduce the power consumption. Further, reduction in  $V_{DD}$  to achieve low-power consumption causes many other circuit-related issues such as PVT variations, degradation of dynamic range, mismatching in circuits element and differential paths. There have been many design methods developed for the ultra-low-power analog ICs. In this chapter, we will discuss some of the design techniques to reduce the power consumption in analog ICs. In addition, we will also discuss the basic building blocks of analog circuits with discussed design techniques.

**Keywords** Low-voltage analog circuits · Subthreshold circuit · Bulk-driven circuit · Dynamic threshold MOS transistor · Floating gate MOS transistor

https://doi.org/10.1007/978-981-15-7937-0\_1

D. Gupta (🖂)

Department of Electronics and Communication Engineering, International Institute of Information Technology Naya Raipur, Raipur, India e-mail: deepika@iiitnr.edu.in

<sup>©</sup> Springer Nature Singapore Pte Ltd. 2020

R. Dhiman and R. Chandel (eds.), *Nanoscale VLSI*, Energy Systems in Electrical Engineering,

#### 1.1 Introduction

Owing to the rapid miniaturization of electronic circuits, the low-power consumption has become essential in the battery operated systems like wearable health monitoring devices, cellphones, tablets, etc. In these handheld devices, low-power consumption is crucial to maintain the high battery life. Low-power consumption even becomes more crucial for small systems such as Internet of things (IoT) and smart cards, which require batteryless operation. To reduce the power consumption for a electronic system, active cooling can be used. However, they are bulky, may create noise in circuit and are expensive (Svensson 2015). In addition, other logic families such BiCMOS can be used for better performance of electronic circuits with low voltage but at the cost of manufacturing expenses (Svensson 2015). Also, some cuttingedge alternatives such as solar power, fuel cells and RF power may be used to have low-power application in integrated circuits (Zimmer et al. 1989). However, the lowvoltage levels of these power sources must be handled very carefully for the proper operations of an integrated circuit (IC). Therefore, there is an increasing demand for the development of sophisticated design techniques to improve the low-power performance of IC (Zhiyuan et al. 2017).

Further, we know that any electronic system is made from both analog and digital component. So, the power needs for both must be understood well to optimize the power of whole system. Importantly, power-aware designs for digital systems are very well known these days. In 1990, researchers Chandrakasan et al. (1992) and Liu and Svensson (1993) started the analysis of power in digital circuits. Due to those efforts, the power consumption for a digital circuit can be summarized in a single equation

$$P = \frac{1}{2} \alpha f C_{\rm L} V_{\rm DD}^2$$

where  $\alpha$  is the probability for output to change its logic in one clock cycle or the switching activity,  $C_{\rm L}$  is the switched capacitance, f is the clock frequency, and  $V_{\rm DD}$  is the supply voltage. However, finding such single equation for power consumption of analog IC is quite difficult. Indeed, some researchers have reported the power analysis for the analog circuits, but it is not as systematic as digital circuits (Vittoz 1980, 1990; Bult 2000; Annema et al. 2005). Recently, few researchers have also started focusing on power conscious design for wireless networks (Abidi et al. 2000; Nilsson and Svensson 2014).

Nowadays, analog IC design techniques are required to aim at attaining higher speed with large dynamic range. It is to note that the circuit capacitances contributed from intrinsic capacitance and interconnect parasitic capacitance strongly influence the speed and bandwidth of analog circuits. With scaling, interconnect capacitance starts dominating over the other and simply reducing the size of transistor will not proportionally improve the circuit bandwidth and speed (Rajput and Jamuar 2002). This occurs due to aggressive transistor size scaling as compared to interconnect. Therefore, scaling in analog design may provide higher packing density but there is no significant advantage for speed optimization.

The speed, bandwidth and dynamic range for analog circuits depend largely on the power consumption. For any analog IC design, the power consumption has three main components:

- Continuous charging and discharging of circuit capacitances result in the dynamic power consumption.

- Biasing currents for MOS transistor cause static power consumption in circuit.

- Power consumption due to the flow of current when both PMOS and NMOS transistors are in the ON state is the short-circuit power consumption.

The net power consumption in a circuit can be given as the sum of the power consumptions due to reasons mentioned above. Note that for analog circuits, similar to the digital counterpart, the total power consumption is directly proportional to the supply voltage (Svensson and Wikner 2010). Therefore, to minimize net power consumed by the analog circuit, the obvious way to reduce it would be to operate the circuits at low supply voltages. Also, the reduction of parasitic capacitances can also help in minimization of power consumption in analog circuits.

#### **1.2** Challenges in Low-Voltage Design

Working with low voltage can be a general solution for low-power operation of analog circuits. However, the low-voltage levels available at input of an analog circuit degrade the performance metrics such as bandwidth, voltage swing and dynamic range. In this section, we will review some challenges faced while designing of the low-voltage analog circuits.

#### 1.2.1 Supply Voltage Scaling

To match with the current scaling scenario, the supply voltage available for analog circuit has been scaled down aggressively. Importantly, due to the lower supply voltage at scaled technology, the available voltage headroom for the MOS transistor operation has reduced. Note that the lower-voltage headroom for MOS transistor degrades the voltage swing and the dynamic range for analog circuits. Further, the scaling of technology also leads to the higher density on chip, increasing the power dissipation per unit area on substrate. As the substrate is able to handle only specific amount of heat, the power consumption with increased density has to reduce for maintaining the proper operation.

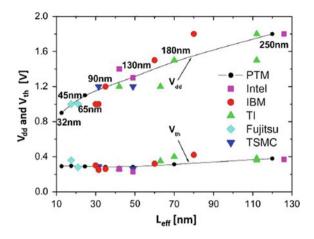

Scaling of the MOS transistor threshold voltage can be adapted to mitigate the effect of low-voltage levels and to increase the voltage swing in scaled analog circuits. However, the reduction of threshold voltage of MOS transistor is quite less significant over the years compared to the scaling scenario of supply voltage, as shown in Fig. 1.1 (Zhao and Cao 2006). From figure, it is clear that the supply voltage is

**Fig. 1.1** Threshold voltage ( $V_T$ ) and supply voltage ( $V_{dd}$ ) scaling trend versus effective channel length ( $L_{eff}$ ) Zhao and Cao (2006)

scaling very rapidly compared to the threshold voltage. This results in poor ON/OFF characteristics of MOS transistor with degraded voltage swing in analog circuits. Apart from this, due to scaling, the ICs are allowed to operate at high frequency with lower-power consumption. However, for analog circuits, some specific amount of current may be needed to maintain the performance of the circuit with scaling of supply voltage. This may result to an insignificant increment in power consumption. So, one can say, direct reduction of supply voltage and scaling may not reduce the power consumption proportionally in analog circuits. Therefore, some innovative design techniques must be used to overcome the supply voltage scaling limitation and to reduce power consumption in analog IC design.

#### **1.2.2** Transistor Inversion

The cutting-edge fabrication processes pose numerous limitations to low-voltage analog IC design. Importantly, it causes severe constraints on the level of inversion in a MOS transistor. Generally, a MOS transistor is considered to have zero current, hence no channel inversion when its turn on voltage  $V_{GS}$  is less than the  $V_T$  of the MOS transistor. On the other hand, current flows through the MOS transistor for  $V_{GS} > V_T$  and channel is said to be strongly inverted (Sedra and Smith 2011). However, in real transistor, such a sudden transition from OFF state to ON is not possible. Therefore, all the transistors have some smaller amount of channel inversion even for  $V_{GS} < V_T$ . This region of inversion is called as the weak region of inversion of MOS transistor (Ueno et al. 2009). In strong inversion region, the conducting channel of MOS device is fully formed above  $V_T$ , whereas in weak inversion region it is only available partly below  $V_T$ . Note that a MOS transistor shows different behavior in strong and weak

inversion region. For strong inversion region, the transistor exhibits a square law characteristics, whereas exponential characteristics are observed in weak inversion (Swanson and Meindl 1972).

In conventional analog IC with higher technology nodes, transistor operates in strong inversion region. However, the modern CMOS technology needs significantly lower supply voltage to minimize the high electric field within the small devices. As the reduction of threshold voltage is quite unreasonable compared to the supply voltage scaling for scaled devices (Zhao and Cao 2006), this results in voltage headroom reduction and limits the available turn on voltage for MOS transistor. So, it gets difficult to operate the MOS transistor in strong inversion region with the small input voltage. Furthermore, low-voltage operation with scaled technology also restricts the number of stacked transistors in the circuit which need to be operated in saturation region or strong inversion region (Keane et al. 2008). Here, the stacked transistors in analog circuits need the minimum supply voltage to increase in order to achieve strong inversion. However, for low-voltage operation, the transistors can be operated in weak inversion region of MOS transistor operation at the cost of bandwidth (BW) and area, as will be explained later in this chapter.

#### 1.2.3 Device Models

The optimized low-voltage analog IC design requires minimum consumption of power and/or silicon area while meeting all performance specification such as speed, bandwidth and dynamic range. The unconventional inversion modes of MOS transistor can be explored to achieve this goal in scaled technologies. While operating MOS transistor extremely into the weak inversion and strong inversion, often it will not provide a good trade-off between frequency response, power consumption and silicon area for analog IC design. So to operate the MOS transistor/circuit over unconventional inversion region of MOS operation, one needs innovative design techniques and new accurate simulation models of MOS devices. The MOS transistor model should be able provide single equation solution over the all available inversion regions. The charge-based EKV model can be a very suitable example of a MOS simulation model to be used in all inversion regions of transistor operations (Enz et al. 2018). In EKV model, the smallest number of core parameters is needed for the accurate behavioral modeling of transistor. Particularly, charge-based EKV model is beneficial for the analysis of analog circuits because it allows the analysis with simple calculations over different inversion regions. Hence, developing new device simulation models specific for analog circuit design is crucial.

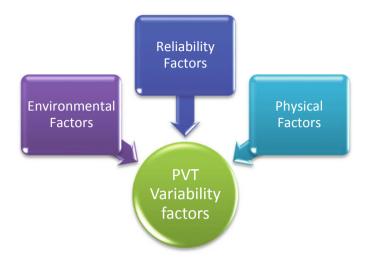

#### 1.2.4 PVT Fluctuations

Owing to the miniaturization of semiconductor devices, it is very difficult to make sure the fixed geometrical dimensions, various doping profiles, thickness of dielectric region during fabrication of MOS transistor. Due to these physical structural fluctuations of MOS transistor, various electrical parameters of analog IC such as parasitic of chip interconnects and threshold voltage get affected (Onabajosilva and Martinez 2012; Chang et al. 2017). As a result, the performance of circuit deteriorates. In addition, aging also affects the performance of analog IC. Also, aging in circuits results in a long-term slow variations in device performance, causing an organized error. Further, these effects are also described by negative bias temperature instability (NBTI) (Schroder 2007).

These days designed ICs have to deal with industrial real-time problems and take requirements into account. Hence, the analog ICs are also needed to be able to handle temperature variations according to the industry standards in a very wide range. When these ICs are used with such wide range of temperature, some electrical MOS transistor/circuit parameter may get affected (Hosticka et al. 1985). These variations may result in another systematic error in the performance of analog ICs. These variations must be handled very carefully while designing low-voltage analog ICs.

Furthermore, as we know that with low-voltage circuit design, scaling of threshold voltage is not significant compared to the supply voltage. Therefore, very small voltage headroom is available with advanced ICs. However, this voltage headroom problem becomes even more worse with the temperature and other physical variations. In addition, the drain current ( $I_D$ ) of the MOS transistor shows the extreme temperature sensitivity with the supply voltage scaling (Wolpert and AmpaDdu 2012). So, for MOS transistor, as the voltage scales, the temperature sensitivity of drain current increases. Importantly, for low-voltage IC design, temperature sensitivity of  $I_D$  increases significantly if the supply voltage scales below 500 mV.

#### 1.2.5 Dynamic Range

These days, the fabrication technology available with miniaturization also limits the dynamic voltage range of analog ICs, hence affecting the signal-to-noise ratio (SNR). Here, the dynamic range is defined as the ration between maximum supply voltage swing and noise signal voltage. Importantly, for analog ICs, the noise signal voltage is limited by the thermal noise. The behaviors of thermal noise are inverse of the bias current. Hence, the expression of dynamic range of analog IC can be given as

$$\mathrm{DR} = \frac{(V_{\mathrm{DD}} - 2V_{\mathrm{sat}})^2}{\alpha/I}$$

Here,  $V_{\rm DD} - 2V_{\rm sat}$  shows the full signal swing, I represent the bias current and  $\alpha$  is the constant. Therefore, the dynamic range of any analog circuit is the function of bias current (Baschirotto et al. 2009).

Hence, it can be inferred that rail-to-rail operation and differential representation of signals can be used to improve dynamic range of analog IC at the cost of circuit complexity and high-voltage operation.

#### 1.2.6 Mismatching

Differential path and circuit element layout mismatching strongly affect the proper operation of high-performance analog ICs. Therefore, any deviation, either random or systematic creating mismatch, is crucial for the production and reliability of the circuit. Interestingly, the input offset voltage in operational amplifier is an example of mismatching consequences in analog circuits. One can note that input offset voltage is an important parameter while designing an amplifier and affects its other AC/DC specification. Moreover, the performance degradation of analog circuits even becomes poorer for low supply voltages. Many critical parameters of amplifier get degraded due to both mismatch and supply restriction. Therefore, suitable layout techniques should be used to avoid effects of mismatch in analog ICs.

Owing to the different circuit requirement and to overcome the design challenges mentioned above, low-voltage analog IC requires completely different design techniques from the high-voltage counterpart. This generates a requirement for some innovative design techniques to be adapted for the low-voltage analog circuits. One such technique can be the use of current levels for the operation of analog circuits. This current mode technique furnishes a better replacement for low-voltage highperformance analog circuit design. In this case, voltage levels existing at different nodes become irrelevant. In the next section of this chapter, we will review some design techniques for low-voltage analog ICs.

#### **1.3 Low-Voltage Design Techniques**

As discussed earlier, while designing a low-voltage circuit, crucial parameters to consider are the noise voltage level and the reduction in threshold voltage of transistor. Better noise immunity can be achieved with the MOS transistor of high threshold voltage but at the cost of voltage headroom. Here, lower threshold voltage of transistor may result in higher-voltage headroom but poorer noise immunity, hence lower SNR. These days, the scaling of threshold voltage is limited to the noise floor level. Any reduction below this may introduce sufficient noises in circuit operation. Here, to overcome the limitation of threshold voltage scaling with valid noise performance, efficient design techniques are needed for low-voltage operation of analog ICs. Now, we will review some of the low-voltage design techniques available in the literature for analog circuits.

#### 1.3.1 Subthreshold Circuits

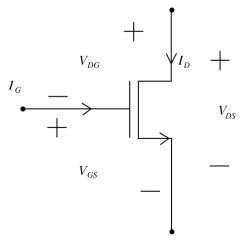

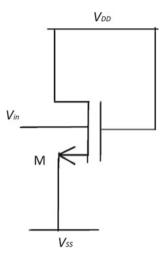

As already discussed, the operating region of MOS transistor is important to decide various parameters of analog IC design. We know that operation of transistor in weak inversion region allows the designer to work with low supply voltages, hence low-power consumption in analog IC design. Whereas, the strong inversion region of MOS transistor operation can make circuit to work with good frequency response. We know that for a MOS transistor when  $V_{GS}$  is greater than  $V_T$  (i.e., strong inversion region), drain current flows and the MOS transistor is said to be ON. The considered MOS transistor model with all terminal voltages is shown in Fig. 1.2.

The drain current in strong inversion region can be given as (Shah 1964)

$$I_{\rm DS} = (K'W/L)[(V_{\rm GS} - V_{\rm T}) - V_{\rm DS}/2]V_{\rm DS}$$

Further, according to above expression  $V_{GS}$  less than  $V_T$ , no current flows through the MOS transistor and it is considered to be OFF. However, in reality, a very small amount of current flows through the MOS transistor for  $V_{GS}$  less than  $V_T$  due to weak channel inversion. The operating region of MOS transistor with weak channel inversion is called as the subthreshold region of operation. In subthreshold region of MOS transistor operation, the current is exponentially proportional to the applied voltage (Ueno et al. 2009; Shah 1964; Geiger et al. 1990) and is given as follows:

$$I_{\rm DS} = \frac{2K_{\prime}W}{L} \left(\frac{nkT}{qe}\right)^2 \exp \frac{q(V_{\rm GS} - V_{\rm T,nmos})}{nkT}$$

Here, *n* represents the subtreshold slope factor. Its value typically lies between 1.2 and 2. Further, *q*,  $V_{T,nmos}$ , *k*, *T* represent electronic charge, threshold voltage

Fig. 1.2 MOS transistor model

of considered NMOS transistor, Boltzmann constant and temperature, respectively. Note that the MOS transistor has lower saturation voltage (approximately 100 mV) in subthreshold region. Hence, large voltage swing can be achieved at low supply voltages. Specifically, this technique for low-voltage analog design is very effective to achieve proper operation of cascaded MOS transistors.

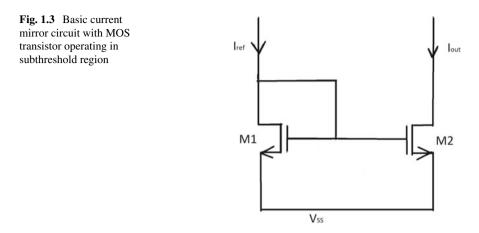

Figure 1.3 shows the design of current mirror circuit with subthreshold MOS transistors. This seems as a conventional current mirror, however the MOS transistors are being operated in subthreshold region. Hence, one will obtain the similar characteristics as with the conventional current mirror. Nevertheless, the value required for the input voltage will be small compared to the conventional counterpart to get the analog IC working. In addition, the input voltage to the circuit can further be reduced using other low-voltage design technique, discussed later in this chapter.

Other than the advantages of MOS transistors in subthreshold region in analog IC, it suffers from poor frequency response and linearity for  $V_{\text{DS}} < 3V_{\text{th}}$ . Here,  $V_{\text{th}}$  represents the thermal voltage and is equal to  $\frac{KT}{q}$ . Additionally, the leakage current due to reverse-biased drain and source with substrate is not negligible as compared to the drain current.

#### 1.3.2 Bulk-Driven MOS Transistor

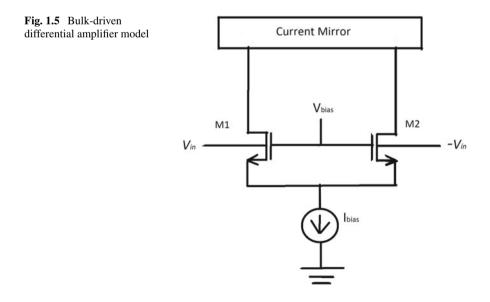

A. Guzinsky first introduced bulk-driven (BD) MOS transistors as active element (Guzinski et al. 1987) for the input differential pair. Many other works have been published depicting the advantages of BD technique on the performance of low-voltage operation of MOS transistor (Guzinski et al. 1987; Blalock et al. 1998; Sinencio and Andreou 1999). The primary purpose was to get low transconductance  $(g_m)$  to achieve improved linearity of MOS amplifier. In general, for MOS transistor to process any data, some current must flow through the drain terminal of transistor.

Fig. 1.4 Bulk-driven MOS transistor model

In conventional general operation of MOS transistor, this current is obtained when the applied bias at the gate terminal of MOS transistor becomes greater than the threshold voltage of the transistor. However, to reduce the required input voltage to turn ON the MOS transistor (or to avoid necessity of higher-voltage headroom) in BD technique, the MOS transistor is biased in saturation mode so that it can flow a continuous current and the input is applied to the bulk contact, as shown in Fig. 1.4. Clearly, it is understood that the drain current ( $I_D$ ) of a traditionally connected MOS transistor is governed by gate to source voltage  $V_{GS}$ ; whereas in BD approach, it is controlled by bulk to source voltage  $V_{BS}$ .

A close observation of BD MOS transistor suggests its resemblance with junction field-effect transistor (JFET). Here, the bulk contact plays the role of the gate terminal of virtual JFET and controls the current of MOS transistor. Hence, one can understand that with BD approach, MOS transistor works as a depletion transistor. So, it can also work with positive, negative and zero bias voltages. The advantages of the bulk-driven approach can be summarized as follows:

- The depletion characteristics of BD MOS transistor significantly minimize the need of overcoming the threshold voltage of the transistor. This increases the voltage headroom and improves the low-voltage performance of MOS transistor.

- This allows the MOS transistor to be used with lower supply voltages.

- BD approach is suitable to be used with current CMOS technology.

However, the BD approach forces the MOS transistor to have an isolated bulk terminal; hence, fabrication becomes complex. Other drawbacks of the BD approach can be listed as follows:

• The transconductance  $(g_m)$  of the MOS transistor with BD technique is quite smaller than the  $g_m$  of conventional counterpart. This affects the bandwidth offered

by the IC employing BD MOS transistors. The bandwidths of BD and conventional MOS transistors are related as follows:

$$f_{\rm T,BD} = \frac{n}{3.8} f_{\rm T,conventional}$$

Here, n is the ration of body transconductance  $(g_{\rm mb})$  and the transconductance  $(g_{\rm m})$ . As the  $g_{\rm mb}$  of BD transistor can be 3–4 times lower than its  $g_{\rm m}$  (generally n has value from 0.2 to 0.4), hence BD transistor has poorer frequency response than the conventional.

- Bulk-driven MOS transistors have higher input capacitance in comparison with the conventional MOS counterpart.

- The BD approach depends significantly on process technology. Therefore, the P well process can only result in the fabrication of N-channel BD MOS transistor.

- BD MOS transistors are highly prone to the latch up effect.

The example of BD MOS transistor-based analog circuit is shown in Fig. 1.5. It is a differential amplifier having their body terminal tied to the input voltage (Guzinski et al. 1987; Blalock et al. 1998; Rajput and Jamuar 2001; Sinencio and Andreou 1999). The gate terminal of transistors M1 and M2 is connected to a fixed supply voltage to ensure their working in saturation region. Note that the range of common mode input voltage  $V_{\text{CM}}$  of a conventional differential amplifier is limited due to the need to high threshold voltage.

So, when the BD MOS transistors are used, rail-to-rail input common mode voltage range can be obtained due to its operation in saturation mode. Hence, sufficient voltage headroom can be obtained for the operation of differential amplifier with the supply voltage as low as 0.6 V. Also, BD MOS transistors in differential amplifier

allow the circuit to achieve linear transconductance with respect to the differential inputs. Therefore, BD MOS transistor aids for the design of low-voltage analog IC.

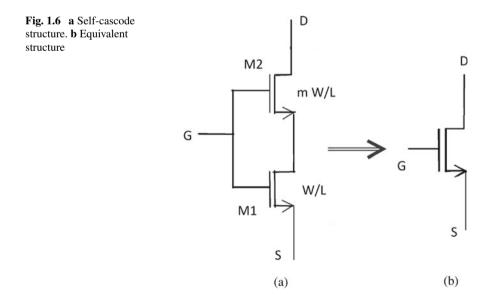

#### 1.3.3 Self-cascode Structure

With the scaling of technology, the output resistance of the MOS transistor is also reducing. One must note that high output resistance of MOS transistor is needed to achieve high gain in analog circuits. Hence, short channel MOS transistors are not able to provide sufficient large gain in analog IC design. The cascode structure can be general solution to have high gain with the scaled technologies (Sinencio and Andreou 1999). However, due to the biasing structure used in cascode, this method results in decreased output voltage swing. Hence, these structures cannot be used in low-voltage design techniques. To overcome this limitation and to achieve both high gain and voltage swing, self-cascode arrangement of two transistor can used, as shown in Fig. 1.6.

In self-cascode structure, the two transistors M1 and M2 can be considered as a single equivalent transistor with same gate voltage  $V_G$ . As the gate biasing is same, hence the structure is called as the self-cascode structure. Here, with self-cascode structure, the effective channel length of the equivalent MOS transistor is comparatively large than the M1 or M2, minimizing the effect of channel length modulation of MOS transistor on analog IC performance. Here, the lower transistor M1 acts as the resistor whose value depends on the input voltage. Hence, the self-cascode structure increases the output resistance and consequently gain. It also reduces the effect of

Miller's capacitance on the transistors gates. This approach has a strong application in the low-voltage analog circuit design. It enables the low-voltage analog circuits to operate with larger-voltage headroom (Bhardwaj and Rajput 2009; Baek et al. 2013).

If both the transistors, i.e., M1 and M2 have same aspect ratio, transistor M1 operates in linear region and M2 operates in saturation region. Hence, the equivalent transistor will not achieve the desired operation. The optimized performance of analog circuit with self-cascode structure is obtained when the W/L ratio of MOS transistor M2 is kept larger compared to the M1. In this case, the equivalent transistor will be completely in the saturation region. As the saturation voltages for transistor M1 and M2 are already small, there is no appreciable change in the drain to source saturation voltage of equivalent transistor and individual transistor M1 and M2. In self-cascode arrangement, the saturation voltage for equivalent transistor can be given as  $V_{\text{DSAT}} = V_{\text{DSATM1}} + V_{\text{DSATM2}}$ . Hence, the self-cascode structure does not need high compliance voltage at output nodes.

Further, the transconductance of equivalent transistor can be given as  $\frac{g_{m2}}{m}$ , where  $g_{m2}$  is the transconductance of MOS transistor M2. Here, m can be given as  $\frac{(W/L)_{M1}}{(W/L)_{M1}}$ . The output resistance of the equivalent MOS transistor is observed proportional to the parameter *m*. Moreover, note that the self-cascode structure operates at a very lower-power supply compared to the regular cascode structure. So the main advantage of self-cascode structure is to provide low-voltage operation with high gain. Moreover, the analog circuits design with self-cascode approach can be found in various literature (Baek et al. 2013; Xu et al. 2016).

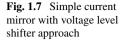

#### 1.3.4 Level Shifter Approach

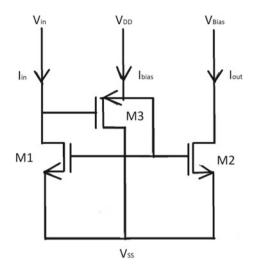

The voltage level shifting is a technique to operate analog circuits with low input voltages. Importantly, a MOS transistor can be either operating in saturation region of operation or in the subthreshold region (Ismail and Fiez 1994; Rajput and Jamuar 2001; Johns and Martin 1997). Generally, this technique uses resistors in the circuit to shift the input common mode voltage to the region of operation of input differential amplifier (Carillo et al. 2000). Figure 1.7 is representing simple current mirror circuit based on the level shifter approach (Rajput and Jamuar 2002).

We can recall that the input current in a conventional current mirror circuit is given as  $K' \frac{W}{2L} (V_{GS1} - V_T)^2$ . Here, parameter k', W, L,  $V_{GS}$ ,  $V_{th}$  have their conventional meaning. Hence, the input voltage for conventional CM must be greater than the  $V_T$ voltage of the input MOS transistor. However, from Fig. 1.7, one can observe that the input voltage for a CM based on voltage level shifter approach is  $V_{GS1} - V_{GS3}$ . Therefore, with voltage level shifter approach, input voltage restriction to be greater than  $V_T$  can be relaxed. Consequently, level shifter approach is beneficial to design low-voltage analog IC. Also, this approach allows analog IC to have higher bandwidth at low voltage. Apart from this, rail-to-rail operation can be obtained both at input and output with level shifter approach.

Offset current ( $I_{offset}$ ) in the output MOS transistor M2 for no input current is the main drawback of voltage level shifting approach. The effect of  $I_{offset}$  becomes significant on the circuit performance when the input current  $I_{in}$  is of the same order as the  $I_{offset}$ . For such circuits, the range of operation is decided by the value of  $I_{offset}$ . In addition, voltage level shifter approach uses high number of MOS transistor for lowvoltage analog IC design. As a result, this approach increases the power dissipation in the circuit.

#### 1.3.5 Floating Gate MOS Transistor

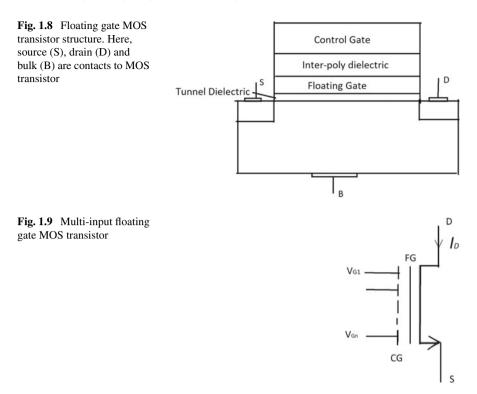

Floating gate MOS transistors are popular for their application in digital circuit as memory element. Also, sometimes another dielectric layer known as charge trap layer can be used in place of FG as digital memory element (Gupta and Vishvakarma 2016). Further, these FG MOS transistors are becoming popular in analog IC design as adaptive circuit element and as capacitive-biased analog memory element. The structure of floating gate MOS transistor is very similar to the conventional transistor. The only difference lies in the polysilicon/metallic isolated floating gate (FG) between the main control gate and the conductive channel. Here, the main control gate and floating gate are not connected physically. However, they are connected electrically due to the capacitively coupled structure at gate.

Further, the FG MOS transistor has this ability to tune its threshold voltage according to the circuit needs; hence, these devices are also getting accepted by community for low-voltage analog circuit design. Dynamic threshold voltage reduction with FG MOS transistor allows it to be used with low-voltage supply. Many structures have been proposed for this purpose (Villegas and Barnes 2003; Wang et al. 2006; Yan

and Sanchez-Sinencio 2000; Cunha et al. 1998). One such structure is shown in Fig. 1.8. Here, a high voltage is applied to the control gate of the MOS transistor. This voltage causes a high electric field at tunnel dielectric which attracts the channel electron to the control gate. These electrons while traveling to the control gate get trapped at the floating gate. Note that the amount of electrons at floating gate decides to the threshold voltage of the FG MOS transistor. Specifically, amount of charge at floating gate can be changed by several ways such as ultraviolet radiations, hot electrons and Fowler–Nordheim tunneling. Further, the discharging of FG MOS transistor is quite difficult due to the dielectric between FG and channel/control gate of the transistor. Note that FG MOS transistor can retain this FG charge for several years with variation as low as 2% on room temperature.

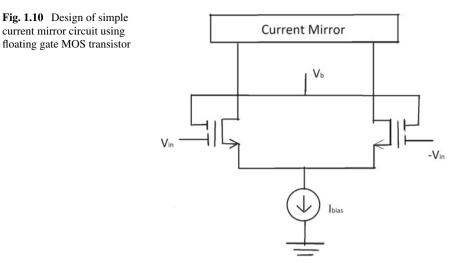

Furthermore, a FG is considered to have no accumulated charge for low-voltage application. Therefore, a multi-input FG MOS transistor as shown in Fig. 1.9 is used by the researchers for low-voltage analog IC design with FG MOS transistor (Mehrvarz et al. 1996). Here, the control gates array is formed over a single FG polysilicon layer. All the control gates are given voltages (i.e.,  $V_{G1}$ ,  $V_{G2}$ ...  $V_{Gn}$ ) such that the total charge at the floating gate is conserved. Hence, the FG MOS transistor can be used with low-voltage supply voltage with dynamic threshold voltage characteristics.

Figure 1.10 shows the two input FG MOS transistor (Rajput and Jamuar 2002) in simple current mirror circuit. Here, a DC voltage is applied to the one gate, and the signal is applied to the another gate. For this multi-input FG MOS transistor,  $V_{\rm T}$  adjust automatically for  $V_{\rm T,new}$ . The value of  $V_{\rm T,new}$  is given as

$$V_{\rm T,new} = \frac{V_{\rm T} - V_{\rm b} K_1}{K_2}$$

where  $K_1 = \frac{C_{G1}}{C_{Total}}$  and  $K_2 = \frac{C_{G2}}{C_{Total}}$ . Here,  $C_{G1}$  and  $C_{G2}$  are the capacitance between floating gate and control gate for two inputs and  $C_{Total}$  is the total capacitance between (i) control gates and floating gates (ii) floating gate and drain terminal (iii) floating gate and source terminal (iv) floating gate and bulk terminal (Rajput and Jamuar 2002).

Importantly, by careful selection of fixed DC voltage  $V_b$ ,  $K_1$  and  $K_2$ , the  $V_{T,new}$ will be less than  $V_T$ . Therefore, smaller new threshold voltage can be obtained for MOS transistor. In addition, the overall transconductance of multi-input FG structure results in smaller transconductance from the single input counterpart as  $g_{m,overall} = K_2g_m$ . Here,  $g_{m,overall}$  is the transconductance of multi-input FG MOS transistor and  $g_m$  is the transconductance for single input counterpart. Clearly,  $g_{m,overall}$  has reduced from  $g_m$  by a factor of  $K_2$ . Moreover, the FG MOS transistor also presents smaller output impedance and smaller output conductance than the MOS transistor working at the same biasing condition. Therefore, one can conclude that the multi-input FG transistors can be used to design low-power analog electronic design.

However, as FG MOS transistor results in only low output resistance, hence only low gain circuits are possible with this technique. Also, the fabrication of additional gate results in increased fabrication cost and sets up complexity compared to the conventional technology.

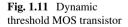

#### 1.3.6 Dynamic Threshold Voltage MOS Transistor

With the scaling trends of current CMOS design, the dynamic threshold (DT) technique was proposed. In fact, DT MOS transistor technique for low-voltage analog IC design is derived from the BD MOS transistor (Mehrvarz et al. 1996; Assaderaghi et al. 1994). The only difference lies in the biasing condition. In DT MOS transistor, gate and bulk electrodes are tied together and the biasing is applied dynamically. Schematic of DT MOS transistor is shown in Fig. 1.11. As the gate and bulk terminal are tied together, hence there is no need to operate the MOS transistor above the cut-in voltage (i.e., 0.7 V) of P-N junction between source/drain and substrate. This results in dynamic reduction of threshold voltage of MOS transistor. Hence, the DT MOS transistor, potential at any point in the conductive channel is governed by both gate and bulk voltage. As a result, high overall transconductance  $g_m + g_{mb}$  is achieved with this technique.

Furthermore, the main difference between DT and BD technique lies in the input capacitance and maximum transit frequency. The maximum transit frequency for DT MOS transistor can be given as follows:

$$f_{t(DT)} = \frac{g_{m} + g_{mb}}{2\pi (C_{GS} + C_{BD} + C_{GS} + C_{BS})}$$

Here,  $g_m$ ,  $g_{mb}$ ,  $C_{GD}$ ,  $C_{BD}$ ,  $C_{GS}$  and  $C_{BS}$  are parameters related to the DT MOS transistors. Here, one can note that as the transconductance of DT MOS transistor is larger than the conventional counterpart; hence, the former provides higher transit frequency as compared to the later. Hence, DT MOS transistor not only allows circuit to work at low voltage but also it provides better frequency response.

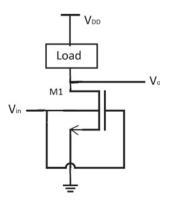

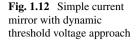

Furthermore, Fig. 1.12 is representing a simple current mirror circuit with DT MOS technique. Clearly, the gates and bulks of two transistors are tied together. Here, the voltage between the bulk/gate and source terminal controls both the transistors together dynamically (Metaj et al. 2017).

#### 1.3.7 Low-Voltage Analog Cells

Any analog IC can be thought as a collection of many sub-circuits. These sub-circuits can be called as analog cells. In fact, the properties possessed by these analog cells largely determine the overall performance of an analog IC. Hence, if these circuits can be designed to operate at a low voltage, then the analog IC consisting these analog cells would automatically operate at low voltage. This technique has been used in the design of various low-voltage analog circuits (Sanchez-Sinencio 2000; Rajput and Jamuar 2001). For an instance, a low-voltage current mirror circuit can be used to design a low-voltage analog circuit (Yan and Sanchez-Sinencio 2000; Sanchez-Sinencio 2000).

#### 1.4 Conclusion

In this chapter, the analysis of analog circuits is presented at low supply voltage. This chapter also covers different issues that may affect the designing of analog circuit at low voltage such as supply voltage scaling and transistor inversion modes. Also, some techniques are discussed to overcome these design issues.

#### References

- Abidi A, Pottie G (2000) Kaiser W (200) Power-conscious design of wireless circuits and systems. Proc IEEE 88(10):1528–1545

- Annema AJ, Nauta B, van Langevelde R, Tuinhout H (2005) Analog circuits in ultradeep-submicron CMOS. IEEE J Solid-State Circuits 40(1):132–143

- Assaderaghi F, Sinitsky D, Parke S, Bokor J, Ko PK, Hu C (1994) A dynamic threshold voltage MOSFET (DT-MOS) for ultra-low voltage operation. In: IEDM Technical Digest, pp 809–812

- Baek KJ, Gim JM, Kim HS, Na KY, Kim NS, Kim YS (2013) Analogue circuit design methodology using self-cascode structures. Electron Lett 49(9)

- Baschirotto A, Chironi V, Cocciolo G, DAmico S, De Matteis M, Delizia P (2009) Low power analog design in scaled technologies. In: Proceedings of topical workshop electron particle physics. France, pp 103–110

- Bhardwaj K, Rajput SS (2009) 1.5V high performance OP AMP using self cascode structure. IEEE Student Conference on Research and Development (SCOReD), https://doi.org/10.1109/ SCORED.2009.5443054, 16-18 Nov.2009

- Blalock BJ, Allen PE, Rincon-Mora GAR (1998) Designing 1-V Op amps using standard digital CMOSTechnology. IEEE Trans Circuits Syst II 45(7):769–780

- Bult K (2000) Analog design in deep sub-micron CMOS. In: Proceeding 26th European solid-state circuits conference (ESSCIRC), pp 126–132

- Carillo JFD, Ausin JL, Torelli G et al (2000) 1-V rail-to-rail operational amplifiers in standard CMOS technology. IEEE J Solid-State Circuits 35(1):33–44. https://doi.org/10.1109/4.818918

- Chandrakasan A, Sheng S, Brodersen R (1992) Low power CMOS digital design. IEEE J Solid-State Circuits 27(4):473–484

- Chang J, Chen Y, Chan W et al (2017) A 7nm 256Mb SRAM in high-k metal-gate finFET technology with write-assist circuitry for low-VMIN applications. In: Proceedings of the IEEE international solid-state circuits conference, pp 206–208

- Cunha AIA, Schneider MC, Montoro CG (1998) An MOS transistor model for analog circuit design. IEEE J Solid-State Circuits 33(10):1510–1519. https://doi.org/10.1109/4.720397

- Enz C, Chicco F, Pezzotta A (2017) Nanoscale MOSFET modeling-part 1: the simplified EKV model for the design of low-power analog circuits. IEEE Solid-State Circuits Magazine 9(3):26– 35

- Geiger RL, Allen PE, Strader NR (1990) VLSI Design Techniques for Analog and Digital Circuits. Mc-Graw Hill, New York

- Gupta D, Vishvakarma SK (2016) Improved short channel characteristics with long data retention time in extremely short channel NAND flash device. IEEE Trans. Electron Dev 63(2):668–674

- Guzinski A, Bialko M, Matheau JC (1987) Bodydriven differential amplifier for application continuousime active-C filter. Eur Conf Circuit Theo Des

- Hosticka BJ, Dalsab KG, Krey D, Zimmer G (1985) Behavior of analog MOS integrated circuit at high temperatures. IEEE J Solid-State Circuits sc-20(4):871–874

- Ismail M, Fiez T (1994) Analog VLSI signal and information processing. McGraw-Hill, New York Johns DA, Martin K (1997) Analog integrated circuit design. Wiley, New York

- Keane J, Eom H, Kim T-H, Sapatnekar S, Kim C (2008) Stack sizing for optimal current drivability in subthreshold circuits. IEEE Trans Very Large Scale Integr (VLSI) Syst 16(5):598–602

- Liu D, Svensson C (1993) Trading speed for low power by choice of supply and threshold voltages. IEEE J Solid-State Circuits 28(1):10–17

- Mehrvarz HR, Kwok CY (1996) A novel multi-input floating-gate MOS four-quadrant analog multiplier. IEEE J Solid-State Circuits 31(8):1123–1131

- Metaj R, Stopjakova V, Arbet D (2017) Design techniques for low voltage analog integrated circuits. J Electr Eng 68(4):245–255

- Nilsson E, Svensson C (2014) Power consumption of integrated low power receivers. IEEE J Emerging Sel Top Circuits and Systems 4(3):273–283

- Onabajosilva M, Martinez J (2012) Analog circuit design for process variation-resilient systemson-a-chip. Springer Science & Business Media,

- Rajput SS, Jamuar SS (2001) Design techniques for low voltage analog circuit structures. NSM 2001/IEEE, Malaysia, November 2001

- Rajput SS, Jamuar SS (2001) Low voltage high performance ccii for analog signal processing applications. ISIC2001, Singapore

- Rajput SS, Jamuar SS (2001) Low voltage, low power high performance current mirror for portable analogue and mixed mode applications. Proceedings of IEE circuits devices and systems 148(5):273–278

- Rajput SS, Jamuar SS (2002) Low Voltage Analog CIRCuit Design Techniques. IEEE Circuits and Syst Mag 2(1):24–42

- Sanchez-Sinencio E (2000) Low voltage analog circuit design techniques. IEEE Dallas CAS workshop

- Schroder DK (2007) Negative bias temperature instability: What do we understand? Microelectron Reliab 47(6):841–852

- Sedra AS, Smith KC (2011) Microelectronic CIRCuits. Oxford Univ. Press, Oxford, U.K

- Shah CT (1964) Characterization of the metal oxide semiconductor transistors. IEEE Trans Electron Dev 11(7):324–345

- Sinencio ES, Andreou AG (ed) Low voltage/low power integrated circuits and systems-low-voltage mixed-signal circuits. IEEE Press (1999). Online ISBN 9780470545065

- Svensson C (2015) Towards power centric analog design. IEEE Circuits Syst Magz 15(3):44-51

- Svensson C, Wikner J (2010) Power consumption of analog circuits: a tutoria. Analog Integr Circuits Sig Proc 65(2):171–184

- Swanson RM, Meindl JD (1972) Ion-implanted complementary MOS transistors in low-voltage circuits. IEEE J. Solid-State Circuits Sc-7(2):146–153

- Ueno K, Hirose T, Asai T, Amemiya Y (2009) A 300 nW, 15 ppm/-C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J Solid-State Circuits 44(7):2047– 2054

- Villegas ER, Barnes H (2003) Solution to trapped charge in FGMOS transistors. Electronics Lett 39(19):1416–1417

- Vittoz E (1980) Micropower IC. Proc IEEE Eur Solid-State Circuits Conf 2:174-189

- Vittoz E (1990) Future of analog in the VLSI environment. In: Proceeding IEEE international symposium circuits and systems, vol 2, pp 1372–1375

- Wang A, Calhoun BH, Chandrakasan AP (2006) Sub-threshold design for ultra low-power systems, 1st edn. Springer Science+Business Media, New York (USA). ISBN 0-387-33515-3

- Wolpert D, AmpaDdu P (2012) Managing temperature effects in nanoscale adaptive systems. Springer, New York. ISBN 978-1-4614-0748-5

- Xu D, Liu L, Xu S (2016) High DC gain self-cascode structure of OTA design with bandwidth enhancement 52(9):740–742

- Yan S, Sanchez-Sinencio E (2000) Low voltage analog circuit design techniques: a tutorial. In: Proceedings of the IEICE transactions on fundamentals of electronics, communications and computer sciences, vol 83, No 2, pp 179–196. ISSN: 0916-8508

- Zhao W, Cao Y (2006) New generation of predictive technology model for sub-45 nm early design exploration. IEEE Trans Electron Devices 53(11):2816–2823

- Zhiyuan C, Law MK, Mak PI, Martins RP (2017) A single-chip solar energy harvesting IC using integrated photodiodes for biomedical implant applications 11(1):44–53

- Zimmer G, Esser W, Fichtel J, Hosticka B, Rothermel A, Schardein W (1989) BiCMOS: technology and circuit design 20(1-2):59–75

# Chapter 2 Design Methodology for Ultra-Low-Power CMOS Analog Circuits for ELF-SLF Applications

Soumya Pandit

Abstract For extreme low-frequency (ELF) and super low-frequency (SLF) applications like biomedical applications (brain wave signal processing and braincomputer interface circuits), seismic signal processing applications, submarine communication applications, ultra-low-power dissipation of the electronic circuits is the most essential criterion. With the scaling of CMOS technology in the nanoscale, the contribution of leakage power becomes very significant compared to any other sources of power dissipation like switching power, bias power, etc. Subthreshold leakage current is an important component of all sources of leakage current. In modern design methodology for ultra-low-power analog circuits, this component of leakage current has been made use of for design purpose. The physics of the MOS transistor in the subthreshold region or weak inversion region is different from that when the transistor operates in the strong inversion region. Therefore, a good understanding of this physics is important for ultra-low-power design. Compact models play significant role in modern design methodologies. This chapter briefly discusses compact model for MOS transistor operating in the weak inversion region. Inversion coefficient-based design methodology for ultra-low-power analog circuits is discussed in detail. Implementation of the design methodology is then exemplified by a complete design of operational transconductance amplifier, operating in the extreme low-frequency region. Application areas of the design methodology are also discussed.

**Keywords** Extreme low frequency (ELF)  $\cdot$  Drain-induced barrier lowering (DIBL)  $\cdot$  Operational transconductance amplifier (OTA)  $\cdot$  Subthreshold current  $\cdot$  Super low frequency (SLF)  $\cdot$  Transconductance

R. Dhiman and R. Chandel (eds.), *Nanoscale VLSI*, Energy Systems in Electrical Engineering,

https://doi.org/10.1007/978-981-15-7937-0\_2

S. Pandit (🖂)

Centre of Advanced Study, Institute of Radio Physics and Electronics, University of Calcutta, Kolkata, India e-mail: sprpe@caluniv.ac.in

<sup>©</sup> Springer Nature Singapore Pte Ltd. 2020

#### 2.1 Introduction

The fundamental idea behind the evolution of a transistor device stems from the concept of controlled switch, where the device operates in two states: OFF state and ON state. In the ON state, the device acts as short circuit by forming a direct path between the input and the output terminals. On the other hand, in the OFF state, the device acts as open circuit, where there does not exist any direct path between the input and the output terminals. For a metal-oxide-semiconductor (MOS) transistor, the two terminals through which the current flows are referred to as source and drain terminals. On the other hand, the controlling terminal is referred to as gate terminal (Pandit 2015). The transfer of resistance from very low (short-circuit condition) to very high (open-circuit condition) is achieved by applying voltage signal to the gate terminal. The controllability of the gate terminal over the flow of current, therefore, plays very significant role in this transfer process. The power dissipation during the OFF state is therefore very small, owing to some non-ideal leakage current. This physics of MOS transistor appears to be fine, when the geometry of the transistor is large. However, with scaling down of the feature size of the transistor, the gate terminal looses its control over the current flow (Pandit 2018). Even in the OFF state, significant amount of current starts flowing between the source and the drain terminals. In other words, leakage current becomes an important concern to scaled down MOS transistor, and the behavior of a MOS transistor becomes more like a resistor compared to a switch. Therefore, in scaled technology, the design of integrated circuits (ICs) becomes a challenging task. It requires good understanding of the physics of MOS transistor in the OFF state, the various sources of leakage current components, necessary modeling of those.

#### 2.2 Physics of MOS Transistor Operating in the Weak Inversion Mode/OFF State

#### 2.2.1 Concept of OFF State of a MOS Transistor

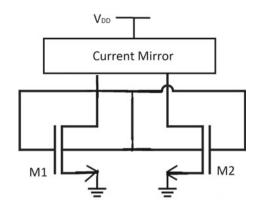

The concept of OFF current of a MOS transistor can be explained with reference to Fig. 2.1, which shows the typical variation of drain current ( $I_D$ ), measured in logarithmic scale, of a MOS transistor versus the gate-to-source voltage ( $V_{GS}$ ). The transistor OFF current is measured when the gate voltage is zero. From Fig. 2.1, the OFF currents are measured to be 5.91 and 0.96 pA at  $V_{DS} = 1.8$  V and 50 mV, respectively. Thus, we see that the OFF current depends upon the magnitude of the drain voltage applied to the transistor. Apart from this, the OFF current of a MOS transistor also depends upon several other factors such as threshold voltage, physical dimensions of the channel, doping profile of the channel, depth of the source/drain junction and thickness of the gate oxide. The conduction current that flows between the drain and the source terminals of a MOS transistor, when the gate voltage is below

Fig. 2.1 The  $I_D$  versus  $V_{GS}$  characteristics of a MOS transistor for  $L = 0.18 \,\mu\text{m}$ ,  $W = 0.36 \,\mu\text{m}$

the threshold voltage is referred to as subthreshold leakage current. Another major component of leakage current is the reverse diode leakage currents at the transistor drain. Apart from these two major components, there are several other sources of leakage current in a nanoscale MOS transistor. These are tunneling current into and through the gate oxide, leakage current due to injection of hot carriers from substrate to gate oxide, gate-induced drain leakage current and punch through current. A comprehensive overview of various sources of leakage current in a nanoscale MOS transistor is provided in Roy et al. (2003). In this section, we discuss the subthreshold leakage current which critically affects the OFF current of scaled integrated circuits. The subthreshold leakage current is often referred to as weak inversion current, especially by the analog designers.

#### 2.2.2 Subthreshold Leakage Current/Weak Inversion Current

When a MOS transistor operates in a condition where the effective gate voltage  $(V_{\text{GS}} - V_T)$  is quite low, i.e.,  $(V_{\text{GS}} - V_T < \approx -2nU_T)$ ,  $n \approx 1.4$  and  $U_T \approx 26 \text{ mV}$  at room temperature, the inversion charge is much less than the depletion charge and the flow of drain current is primarily due to diffusion of minority carriers (Pandit 2013). The weak inversion mode is defined by the condition  $\Phi_F \le \psi_s \le 2\Phi_F$ , where  $\psi_s = 2\Phi_F = 2\frac{k_BT}{q} \ln \left(\frac{N_A}{n_i}\right)$  is the surface potential at strong inversion and  $N_A = N_{\text{sub}}$  is the uniform substrate concentration. Under this condition, the behavior of a MOS transistor is similar to that of a bipolar transistor, where source terminal acts as emitter, substrate acts as base, and drain acts as the collector terminal.

In VLSI circuit simulation, compact models play very significant role. Compact models of a circuit element are simple mathematical description of the behavior of that circuit element that are used for computer-aided analysis and design (Saha 2016). The two compact models most widely used in semiconductor industries are Berkeley short channel IGFET (BSIM) model and Enz-Krummenacher-Vittoz (EKV) model. The weak inversion/subthreshold operation of a MOS transistor is very effectively modeled in both of the compact models. The weak inversion drain current is modeled as follows Saha (2016).

$$I_{\rm DS} = \mu_n C'_{\rm ox} \frac{W}{L} \left(n-1\right) U_T^2 \exp\left(\frac{V_{\rm GS} - V_T}{nU_T}\right) \left[1 - \exp\left(-\frac{V_{\rm DS}}{U_T}\right)\right]$$

(2.1)

where  $U_T = \frac{k_{\text{BT}}}{q}$  is the thermal voltage,  $n = 1 + \frac{C_{\text{dm}}}{C_{\text{ox}}}$  is the subthreshold swing factor,  $\mu_n$  is the surface mobility of the electrons,  $C'_{\text{ox}}$  is the oxide capacitance per unit area, W and L are the effective channel width and length of the MOS transistor, respectively, and  $V_T$  is the threshold voltage. The weak inversion drain current, as approximated from EKV model, using source as the reference terminal is given by Enz and Vittoz (2006)

$$I_{\rm DS} = 2n\mu_n C'_{\rm ox} U_T^2 \left(\frac{W}{L}\right) \exp\left(\frac{V_{\rm GS} - V_T}{nU_T}\right)$$

(2.2)

While writing (2.2), we assume that the drain–source voltage  $V_{\rm DS}$  exceeds its saturation value,  $V_{\rm DSat}$ . In the weak inversion mode, the saturation value of drain–source voltage is  $\approx 4U_T$ .

The transconductance of a MOS transistor operating in weak inversion mode is defined as

$$g_m(WI) = \frac{I_{\rm DS}}{nU_T} \tag{2.3}$$

The transconductance efficiency is, therefore, written as

$$\frac{g_m}{I_{\rm DS}}(WI) = \frac{1}{nU_T} \tag{2.4}$$

It may be noted that the transconductance and the transconductance efficiency of a MOS transistor operating in the weak inversion mode neither depend upon the geometry of the transistor device, nor on the process parameters.

#### 2.2.2.1 Drain-Induced Barrier Lowering

As noted from the preceding discussion, the drain current in the weak inversion mode exponentially depends upon the overdrive voltage. Therefore, with the reduction of threshold voltage, by some means, the weak inversion drain current changes significantly. The weak inversion drain current increases with the application of the high

drain bias, through the reduction of threshold voltage. The dependence of threshold voltage of a MOS transistor on the drain bias is referred to as drain-induced barrier lowering.

When the transistor is in the OFF state, a potential barrier (in the p-type region) prevents the electrons to flow from the source to the drain, for an n-channel MOS transistor. With the application of gate-to-source voltage, this barrier reduces and eases the conduction of the electrons. For long channel MOS transistor, such barrier lowering is controlled by the potential applied on the gate terminal, and the drain bias does not have any role over it. However, for a short channel MOS transistor, the drain and the source fields penetrate deeply into the middle of the channel, which lowers the potential barrier between the source and the drain. The result of this is that even at lower gate voltage, the carriers can overcome the barrier between the source and the channel. In other words, the threshold voltage of a short channel MOS transistor reduces from its long channel value. With application of high drain bias to a short channel MOS transistor, the barrier height is further lowered, resulting in further decrease of the threshold voltage. This phenomenon is called drain-induced barrier lowering Pandit et al. (2014).

The threshold voltage model for a short channel MOS transistor is modeled as

$$V_T = V_{T0} - \Delta V_T \tag{2.5}$$

where  $V_{T0}$  is the long channel threshold voltage and  $\Delta V_T$  is the amount of the reduction of threshold voltage due to short channel effect and  $\Delta V_T$  is given by Saha (2016), Pandit et al. (2014)

$$\Delta V_T = \theta_T \left( L \right) \left[ 2 \left( \psi_{\rm bi} - \psi_s \right) + V_{\rm DS} \right] \tag{2.6}$$

Here  $\theta_T(L)$  is the short channel effect coefficient depending on the channel length and is given by

$$\theta_T(L) = \frac{1}{2\cosh\left(\frac{L}{l_t}\right) - 2} \tag{2.7}$$

#### 2.3 Theoretical Formulation of the Design Methodology

#### 2.3.1 All Region Drain Current Model of a MOS Transistor

In the strong inversion mode, the drain current for an n-channel MOS transistor (NMOS) is proportional to the square of the effective gate voltage ( $V_{GS} - V_{Tn}$ ) and is written as Enz and Vittoz (2006)

$$I_{\rm DS} = \frac{1}{2} \left( \frac{\mu_n C'_{\rm ox}}{n} \right) \left( \frac{W}{L} \right) (V_{\rm GS} - V_{\rm Tn})^2 \tag{2.8}$$

The strong inversion mode occurs at high effective gate voltage  $(V_{\rm GS} - V_{\rm Tn}) > 225 \,\mathrm{mV}$ . An unified expression for the drain current interpolated from weak through strong inversion is written as

$$I_{\rm DS} = 2n\mu C'_{\rm ox} U_T^2 \left(\frac{W}{L}\right) \left[\ln\left(1 + e^{\frac{V_{\rm GS} - V_{\rm TR}}{2nU_T}}\right)\right]^2$$

(2.9)

$$=2n\mu C_{\rm ox}' U_T^2 \left(\frac{W}{L}\right) \left[\ln\left(1+e^{\nu}\right)\right]^2 \tag{2.10}$$

The effective gate voltage is normalized to  $2nU_T$  and is represented by the factor  $\nu$ . It may be noted that the velocity saturation component is omitted here. This is based on the assumption that for ultra-low-power operation, the supply voltage should also be very small and the drift velocity would not therefore saturate with the applied electric field. Small values of  $\nu$  characterize the weak inversion mode. Also  $\ln (1 + e^{\nu}) \approx e^{\nu}$ . Therefore, we arrive at the weak inversion drain current expression. On the other hand, large values of  $\nu$  characterize the strong inversion mode. Further,  $\ln (1 + e^{\nu}) \approx \nu$  and we get back the expression for the drain current operating in the strong inversion mode.

# 2.3.2 Inversion Coefficient Definition

The inversion coefficient (IC) factor provides a numerical identity factor characterizing the inversion status of a MOS transistor. For IC < 0.1, the transistor operates in the weak inversion mode, for 0.1 < IC < 10, the transistor operates in the moderate inversion mode, and for IC > 10, the transistor operates in the strong inversion mode.

The transition current is defined as Binkley (2008)

$$I_{S} = 2n\mu C_{OX}' U_{T}^{2} \frac{W}{L} = I_{0} \cdot \frac{W}{L}$$

(2.11)

The traditional inversion coefficient is defined as Binkley (2008)

$$IC = \frac{I_D}{I_S} = \left[ \ln \left( 1 + e^{\frac{V_{GS} - V_{Ta}}{2nU_T}} \right) \right]^2 = \left[ \ln \left( 1 + e^{\nu} \right) \right]^2$$

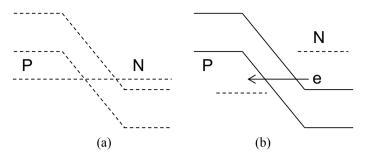

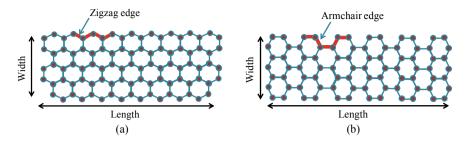

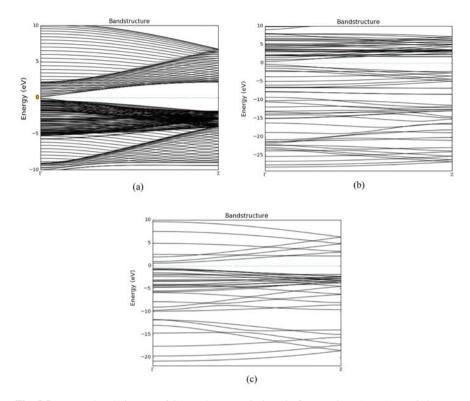

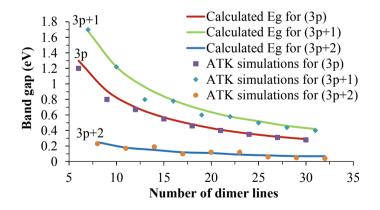

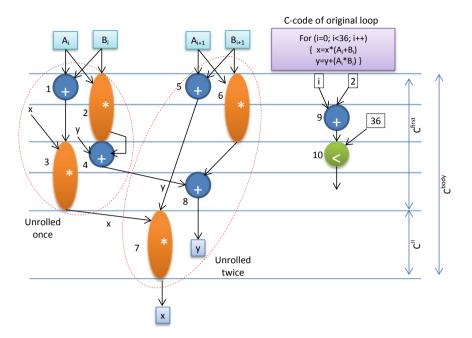

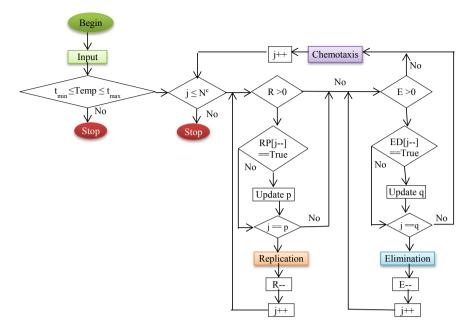

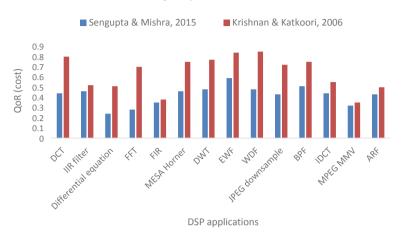

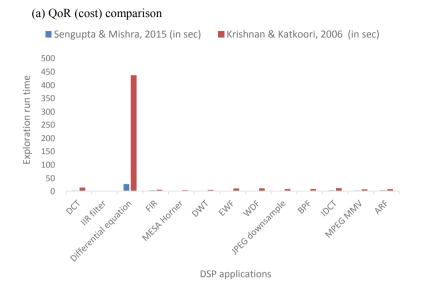

(2.12)