# Reducing Number of Switches in Multilevel Inverter Using Diode Clamped and H-Bridge Inverters

Karanam Deepak, M. Rama Prasad Reddy, K. Jaya Sree and P. Partha Saradhi Reddy

**Abstract** The multilevel inverters (MLI) are having more features to usage. In existing methods like diode clamped MLI and H-Bridge MLI, more number of switches are using compared to proposed MLI. So, a new method of 35-level MLI topology is a combination of diode clamped and cascaded multilevel inverters. In this method using the less number of switches and their pulse generating circuit. So, thereby ensuring the switching loss, reducing size and installation cost also less. So, the new proposed technology is well designed for renewable applications (RA) like PV cell and wind energy systems. Comparing to the other existing inverters, the switch count is very less. The results are validating by using MATLAB/Simulink design.

**Keywords** Multilevel inverters (MLI) • H-Bridge MLII (HMLI) • Diode clamped MLI (DCMLI) • Photovoltaic cell (PV) cell • Renewable applications (RA)

## 1 Introduction

Power electronics' switches play a vital responsibility in the electrical power conversions. Another advantage of MLI is control of the output power and uses in take out power commencing renewable energy applications like PV cell as well as wind power generation systems [1]. The conversion of DC to AC is possible to need inverter. In an electrical power, inverter is basic circuit that converts DC into AC. This conversion is important because AC is more useful in our daily applications. Conventional diode clamped and H-Bridge inverters having more switches compared to proposed system [2].

P. Partha Saradhi Reddy

K. Deepak  $(\boxtimes) \cdot M.$  Rama Prasad Reddy  $\cdot$  K. Jaya Sree

G. Pullaiah College of Engineering and Technology, Near Venkayapalle, Pasupula Village, Nandikotkur Rd, Kurnool, AP 518002, India

Guru Nanak Institute of Technology, Ibrahimpatnam, Telangana, India

<sup>©</sup> Springer Nature Singapore Pte Ltd. 2020

H. S. Saini et al. (eds.), *Innovations in Electrical and Electronics Engineering*, Lecture Notes in Electrical Engineering 626, https://doi.org/10.1007/978-981-15-2256-7\_20

In present years, consumption of electric power is rapidly increasing day by day. So, the demand of electrical energy is increased. Since the greenhouse production are mostly consumes. The main reasons caused by the renewable resources a fast development in find another and a renewable resource has attained a major interest in research area to eliminate the lack of fossil fuels and also decreases the global warming [3]. Therefore, the renewable energy sources have to turn into a difficult field, and so many researchers have to focus on the renewable energy sources. So, this paper mainly focuses on to generate novel sustainable, normal wealth and environmental approachable natural renewable energy resources.

In present, earth for the most part of environmental renewable energy sources can be used DC energy in environment such as solar system. In electrical power transmission systems is in AC and not all of the AC loads like machines, etc. are uses the DC power supply as their power sources. So, many applicants need an AC power as the main power source. Therefore, in this reason, we need conversion of energy DC into AC power [4].

MLI is a power electronic apparatus which converting direct current power supply to alternate power supply. In previous conventional systems, inverter is used to two-level inverter and is implemented using a few semiconductor switches. In present days, rapid increases the growth of industry and also introduces the high power applications devices which reaches the megawatt levels. So, the two-level inverter is not able of usage of high power applications. So, in this paper, introduce a more number of levels inverter like multilevel expand into an essential to overcome the short of existing two-level inverters and economically elevated power loads. Moreover, these reason multilevel inverters are designed to substitute the existing two-level inverters to grow high-quality power quality, and switching losses is less and capable of high voltage systems [5].

The most important scope of MLIs is to generate the multilevel output voltages with switching losses is very less. Comparing to the existing methods, the multilevel inverter has so many advantages. The advantages are: (1) The MLI inverter can be produced regular method voltage so the strain of the motor reduces. (2) MLI draws the input current with less distortion. (3) MLI can operate at both higher and lower switching frequency; it means, at lower switching, frequency having low switch losses and efficiency is high. (4) MLI reduces the total harmonic distortions (THD) [6]. This paper includes the performances of two types of MILIs, and they are diode clamped inverter along with cascaded H-Bridge multilevel inverter. So, our proposed method is combination of diode clamped and H-Bridge circuits. The operation of the circuit and principle operation is discussed in the following secessions.

The theory of multilevel inverter is to generate multilevel inverter output voltages with very less switching losses and harmonic distortions. In this proposed method the first, second diode clamped multilevel inverter (DCMI) and third one is the proposed MLI having combination of CHMI and DCMI. So, the proposed MLI applied for low power systems mainly photovoltaic systems. This paper describes many sections. Sect. 1 contains the introduction part of the MLI and Sect. 2 contains the background work of the DCMI and background work of the CHMI. Section 3 mentions the proposed MLI principle operation and explanation. Section 4 contains the simulation results of the proposed MLI.

### 2 Background Work

The MLI general structure is toward making a sinusoidal voltage since of more than few voltage levels frequently achieve from capacitor voltage sources. Multilevel inverter has so many applications because of MLI having low THD and very low commutation loses. MLI develops into an efficient and valuable resolution for amplifying power and AC load also reduced.

The multilevel inverters are divided into below categories: They are (1) cascaded type MLI, (2) diode clamped type MLI, (3) Flying capacitor type MLI.

This paper discusses cascaded MLI and diode clamped type multilevel inverters. Compare to the diode clamped MLI and cascaded MLI, cascaded MLI is having the simplest arrangement.

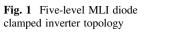

### 2.1 Diode Clamped Type MLI (DCMI)

In largest parts generally use MLI method, that is, the diode clamped MLI (DCMI), and diode is used for clamping device. It can be used as clamp the DC voltage. So it attains the steps in the output voltage sources. Accordingly, the most important theory of this MLI is diode that is used for the power strategy voltage strain.  $V_{dc}$  is the DC voltage of apiece switch plus apiece capacitor. The No. of levels (N) inverters we need total (N - 1) no. of voltage source, and switching devices are need 2(N - 1) and the diodes are  $(N - 1) \times (N - 2)$  diodes. After the increasing of the no. of voltage level, the superiority of the output AC voltage is increased and the waveform of the voltage has become nearer to a sinusoidal waveform.

Figure 1 shows the five-level DCMLI. DC bus voltage having the four capacitors,  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$ . In a DC bus voltage of the  $V_{dc}$ , the apiece of capacitor voltage is  $V_{dc}/4$  and the each device voltage strain will be partial and  $V_{dc}/4$  is single capacitor voltage stage-level throughout clamp the diodes. The switches of the MLI are  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S'_1$ ,  $S'_2$ ,  $S'_3$  and  $S'_4$ . If the voltage output level is  $V_{dc}/2$ , then the switches can be conducted at  $S_1-S_4$  next to the similar point. In an apiece voltage point, four switches conduct at a time. And the maximum output voltage level will get on partially of the DC source. So it is the main disadvantage of the DCMI. In this difficulty can be this difficulty preserve be solving by using a two times voltage supply or CHMLI two DCMLIs (Fig. 2).

Fig. 2 Single-phase cascade multilevel inverter topology

| Table 1   Five-level DCMLI     switching state table | <i>V</i> 0      | <i>S</i> <sub>1</sub> | <i>S</i> <sub>2</sub> | <i>S</i> <sub>3</sub> | $S_4$ | $S'_1$ | $S'_2$ | <i>S</i> ' <sub>3</sub> | $S'_4$ |

|------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-------|--------|--------|-------------------------|--------|

|                                                      | $V_{\rm dc}/2$  | 1                     | 1                     | 1                     | 1     | 0      | 0      | 0                       | 0      |

|                                                      | $V_{\rm dc}/4$  | 0                     | 1                     | 1                     | 1     | 1      | 0      | 0                       | 0      |

|                                                      | 0               | 0                     | 0                     | 1                     | 1     | 1      | 1      | 0                       | 0      |

|                                                      | $-V_{\rm dc}/4$ | 0                     | 0                     | 0                     | 1     | 1      | 1      | 1                       | 0      |

|                                                      | $-V_{\rm dc}/2$ | 0                     | 0                     | 0                     | 0     | 1      | 1      | 1                       | 1      |

The five-level DCMLI amount produced voltage levels ought to the similar voltage significance. The switching operations can survive taken in a way that output voltage THD will become as low as possible. The switches arrangement of the MLI is into four pairs  $(S_1, S'_1), (S_2, S'_2), (S_3, S'_3), (S_4, S'_4)$ . The sequence of the switches as specified in Table 1. The state Condition 1 means that switch ON position and 0 means switch OFF position.

The following steps are the five-level DCMLI output voltage in this circuit as follows:

- The output voltage  $V_0 = 0$ , then the upper switches of  $S_3$ ,  $S_4$  and the lower switches  $S'_1$  and  $S'_2$  are in ON state.

- And the output voltage  $V_0 = V_{dc}/4$ , then the switches of upper switches are  $S_2$ ,  $S_3$ ,  $S_4$  and lower switch  $S'_1$  is in ON state.

- And the output voltage  $V_0 = V_{dc}/2$ , the switches of S1,  $S_2$ ,  $S_3$ ,  $S_4$  the entire upper switches in turn ON position.

- And the negative output voltage of  $V_0 = -V_{dc}/4$ , the switch of upper side  $S_4$  and the lower side switches  $S'_1$ ,  $S'_2$  and  $S'_3$  are in turn ON position.

- Another negative output voltage of  $V_0 = -V_{dc}/2$ , and all the switches of the lower position in turned ON position.

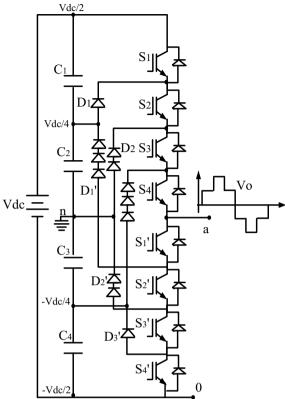

#### 2.2 Cascade H-Bridge Multilevel Inverter (CHMI)

The cascade MLI having no. of H-Bridge inverter units with separate DC source and each H-Bridge unit is connected in series. And the H-Bridge produces  $+V_{dc}$ , 0 and  $-V_{\rm dc}$  voltage levels is connecting the input DC source to output AC side of dissimilar combination of the four switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$ . And the H-Bridge of each output is coupled in series. So, the synthesize output voltage waveform is nothing but a summation of all of the individual H-Bridge outputs. By linking enough number of H-Bridges in cascade and with suitable modulation format, almost sinusoidal output voltage waveform can be synthesized.

The output voltages in number of levels having phase voltage (2s + 1) and line voltage (4s + 1) correspondingly. And s is nothing but a number of H-Bridges per phase. In a three H-Bridges, five bridges and seven H-Bridges per phase require seven levels, nine levels, respectively. The representative waveform created by seven-level CMLI. And the magnitude of the AC output phase voltage is the sum of the voltages created by H-Bridges.

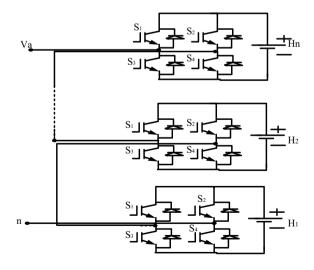

### **3** Proposed Concept

Figure 3 shows the multilevel inverter topology. The proposed circuit is the combination of H-Bridge and diode clamped inverter. Here, H-Bridge inverter can be used as alternating signal model like it gives the negative and positive polarities and in diode clamped inverter circuit having the capacitors also. So, the capacitor voltages are added and subtracted the operating power switches to generate the (N = 2n + 1 = 35) level output voltage waveform.

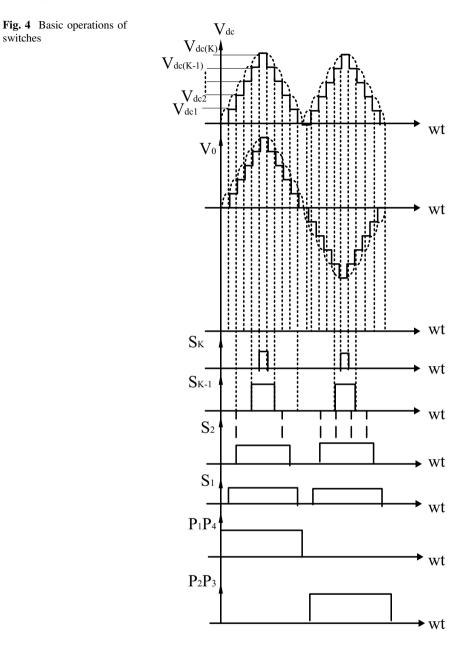

And the basic operation of the main circuit is working principle of the topology as shown in Fig. 4. In this diagram,  $V_{dc}$  bus is the DC input voltage, and  $V_o$  is the output AC voltage,  $V_{01}$  is the fundamental voltage of  $V_o$ . In this proposed circuit having the So-S17 switches of the diode clamped inverters and another four

switches are power switches P1–P4 is giving signals of the H-Bridge inverters. And, the H-Bridge four power switches are operated at fundamental frequency of the output voltage.

The proposed circuit having the total four switches of H-Bridge and seventeen diode clamped switches is used to generate output of N = 35-level voltage waveform. And also using the n capacitors and n diodes can be used to produce the output of overall very less switch count than an existing method.

### **4** Simulation Results

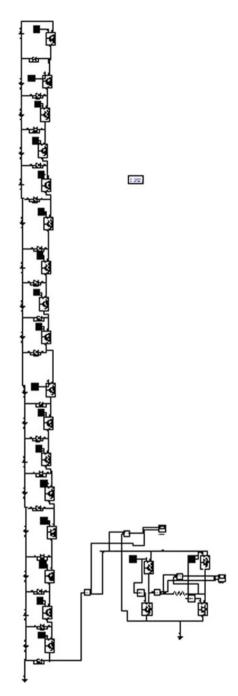

Figure 5 shows the proposed MLI topology Simulink diagram. The output waveform of the staircase voltage waveforms for k different DC sources and its amplitude is  $V_{dc}$  and the equation is as follows:

$$V_0(t) = \frac{4V_{\rm dc}}{\pi} \sum_{n=1,3,5,\dots,\infty}^{\infty} \left[\cos(n\alpha_1) + \cos(n\alpha_2) + \dots + \cos(n\alpha_k)\right] \frac{\sin(n\omega_0 t)}{n}$$

(1)

The magnitude of the Fourier transform coefficients can be calculated as follows

$$V_n = \frac{4V_{\rm dc}}{n\pi} \left[\cos(n\alpha_1) + \cos(n\alpha_2) + \dots + \cos(n\alpha_k)\right]$$

(2)

In applied equations of the (1) and (2) are the proposed 35-level MLI topology are studied. The output of the MLI generates 220 V AC voltage waveform so we have to measure a DC bus voltage of the 340 V.

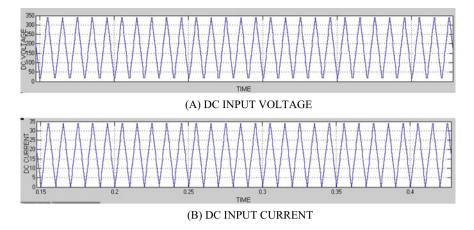

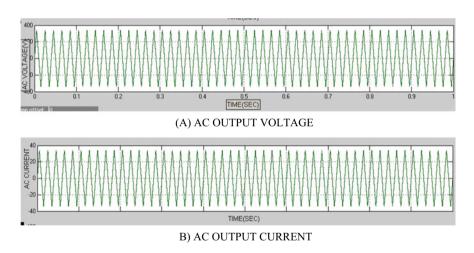

Figures 6 and 7 show the simulated input waveforms of DC bus (A) voltage and (B) current of a 35-level multilevel inverter and simulated output waveforms of AC bus (A) voltage and (B) current of a 35-level multilevel inverter of the proposed MLI topology and the operating frequency of the proposed topology is 50 Hz.

Table 2 is the comparison of different multilevel inverter topologies power switches count. This evaluation obviously demonstrates the superiority of our proposed MLI structure

The voltage rating is high in cascaded H-Bridge MLI topology because this MLI using four switches. It should be pointed that the four switches used in the H-Bridge of our topology require a large voltage rating. These unlike switches are used in the conventional MLI topologies. Then all the conventional method switches having low voltage rating. The cost of the switch increases of its same low voltage rating and the driving circuits are frequently remaining the similar. So based on that, an important benefit in provisions of cost and easy functioning is still obtainable by our proposed MLI topology.

Fig. 5 Simulink diagram of the proposed concept

Fig. 6 The simulated input waveforms of DC bus, **a** voltage and **b** current of a 35-level multilevel inverter

Fig. 7 The output waveforms of AC bus, a voltage and b current of a 35-level multilevel inverter

| Table 2 Comparison of different types of MLI topologies | S.<br>No | Circuit                  | No. of power switches used |  |  |  |

|---------------------------------------------------------|----------|--------------------------|----------------------------|--|--|--|

|                                                         | 1.       | Diode clamped MLI        | 34                         |  |  |  |

|                                                         | 2.       | Cascaded H-Bridge<br>MLI | 68                         |  |  |  |

|                                                         | 3.       | PROPOSED MLI             | 21                         |  |  |  |

### 5 Conclusion

A new 35 MLI topology is proposed. The proposed method of 35-level multilevel inverter topology is combination of diode clamped and cascaded multilevel inverters. The proposed MLI is the better choice for renewable source applications like photovoltaic applications because proposed circuit having separate input DC sources is offered. This paper explains the operation and working principle of the proposed MLI topology. A complete study of efficiency and practical performance is still necessary to totally confirm the advantages of this new proposed MLI circuit.

### References

- 1. J. Rodriguez, J.S. Lai, F.Z. Peng, Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. **49**(4), 724–738 (2002)

- M. Malinowski, K. Gopakumar, J. Rodriguez, M.A. Perez, A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 57(7), 2197–2206 (2010)

- M. Kavitha, A. Arunkumar, N. Gokulnath, S. Arun, New Cascaded H-Bridge Multilevel Inverter Topology with Reduced Number of Switches and Sources. Final year students/Dept. of EEE/DR.S.J.S Paul Memorial College of Engineering &Technology/Pondicherry/India, vol 2, issue 6. ISSN: 2278-1676, pp 26–36 (2012)

- 4. N.B. Zahari, *Cascaded H-Bridge Multilevel Inverter [CHMLI]*. A Proposal Submit in Biased Fulfilment of the Obligation for Bachelor of Degree in Electrical & Electronics Engineering (Electrical) Faculty of Electrical Engineering University of Teknologi Malaysia (2013)

- A. Parkash, S.L. Shimi, S. Chatterji, *Harmonics Elimination in Cascade Multilevel Inverters* Using Newton-Raphson and Genetic Algorithm. Department of Electrical Engineering, National Institute of Technical Teachers' Training and Research, Chandigarh-160019, India (2014)

- Description of Multi Level Inverters and Advantages of MLI. https://www.elprocus.com/ multilevel-inverter-types-advantages/