Advances in Intelligent Systems and Computing 732

# Sunil Kumar Muttoo Editor

# System and Architecture

Proceedings of CSI 2015

# Advances in Intelligent Systems and Computing

Volume 732

#### Series editor

Janusz Kacprzyk, Polish Academy of Sciences, Warsaw, Poland e-mail: kacprzyk@ibspan.waw.pl

The series "Advances in Intelligent Systems and Computing" contains publications on theory, applications, and design methods of Intelligent Systems and Intelligent Computing. Virtually all disciplines such as engineering, natural sciences, computer and information science, ICT, economics, business, e-commerce, environment, healthcare, life science are covered. The list of topics spans all the areas of modern intelligent systems and computing such as: computational intelligence, soft computing including neural networks, fuzzy systems, evolutionary computing and the fusion of these paradigms, social intelligence, ambient intelligence, computational neuroscience, artificial life, virtual worlds and society, cognitive science and systems, Perception and Vision, DNA and immune based systems, self-organizing and adaptive systems, e-Learning and teaching, human-centered and human-centric computing, recommender systems, intelligent control, robotics and mechatronics including human-machine teaming, knowledge-based paradigms, learning paradigms, machine ethics, intelligent data analysis, knowledge management, intelligent agents, intelligent decision making and support, intelligent network security, trust management, interactive entertainment, Web intelligence and multimedia. The publications within "Advances in Intelligent Systems and Computing" are primarily proceedings of important conferences, symposia and congresses. They cover significant recent developments in the field, both of a foundational and applicable character. An important characteristic feature of the series is the short publication time and world-wide distribution. This permits a rapid and broad dissemination of research results.

#### Advisory Board

Chairman

Nikhil R. Pal, Indian Statistical Institute, Kolkata, India e-mail: nikhil@isical.ac.in

#### Members

Rafael Bello Perez, Universidad Central "Marta Abreu" de Las Villas, Santa Clara, Cuba e-mail: rbellop@uclv.edu.cu

Emilio S. Corchado, University of Salamanca, Salamanca, Spain e-mail: escorchado@usal.es

Hani Hagras, University of Essex, Colchester, UK e-mail: hani@essex.ac.uk

László T. Kóczy, Széchenyi István University, Győr, Hungary e-mail: koczy@sze.hu

Vladik Kreinovich, University of Texas at El Paso, El Paso, USA e-mail: vladik@utep.edu

Chin-Teng Lin, National Chiao Tung University, Hsinchu, Taiwan e-mail: ctlin@mail.nctu.edu.tw

Jie Lu, University of Technology, Sydney, Australia e-mail: Jie.Lu@uts.edu.au

Patricia Melin, Tijuana Institute of Technology, Tijuana, Mexico e-mail: epmelin@hafsamx.org

Nadia Nedjah, State University of Rio de Janeiro, Rio de Janeiro, Brazil e-mail: nadia@eng.uerj.br

Ngoc Thanh Nguyen, Wroclaw University of Technology, Wroclaw, Poland e-mail: Ngoc-Thanh.Nguyen@pwr.edu.pl

Jun Wang, The Chinese University of Hong Kong, Shatin, Hong Kong e-mail: jwang@mae.cuhk.edu.hk

Sunil Kumar Muttoo Editor

# System and Architecture

Proceedings of CSI 2015

*Editor* Sunil Kumar Muttoo Department of Computer Science University of Delhi Delhi India

ISSN 2194-5357

ISSN 2194-5365

(electronic)

Advances in Intelligent Systems and Computing

ISBN 978-981-10-8532-1

ISBN 978-981-10-8533-8

(eBook)

https://doi.org/10.1007/978-981-10-8533-8

Library of Congress Control Number: 2018932994

#### © Springer Nature Singapore Pte Ltd. 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. part of Springer Nature

The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

## Preface

The last decade has witnessed remarkable changes in IT industry, virtually in all domains. The 50th Annual Convention, CSI-2015, on the theme "Digital Life" was organized as a part of CSI@50, by CSI at Delhi, the national capital of the country, during December 02–05, 2015. Its concept was formed with an objective to keep ICT community abreast of emerging paradigms in the areas of computing technologies and more importantly looking at its impact on the society.

Information and Communication Technology (ICT) comprises of three main components: infrastructure, services, and product. These components include the Internet, infrastructure-based/infrastructure-less wireless networks, mobile terminals, and other communication mediums. ICT is gaining popularity due to rapid growth in communication capabilities for real-time-based applications. New user requirements and services entail mechanisms for enabling systems to intelligently process speech- and language-based input from human users. CSI-2015 attracted over 1500 papers from researchers and practitioners from academia, industry and government agencies, from all over the world, thereby making the job of the Programme Committee extremely difficult. After a series of tough review exercises by a team of over 700 experts, 565 papers were accepted for presentation in CSI-2015 during the 3 days of the convention under ten parallel tracks. The Programme Committee, in consultation with Springer, the world's largest publisher of scientific documents, decided to publish the proceedings of the presented papers, after the convention, in ten topical volumes, under ASIC series of the Springer, as detailed hereunder:

- 1. Volume # 1: ICT Based Innovations

- 2. Volume # 2: Next Generation Networks

- 3. Volume # 3: Nature Inspired Computing

- 4. Volume # 4: Speech and Language Processing for Human-Machine Communications

- 5. Volume # 5: Sensors and Image Processing

- 6. Volume # 6: Big Data Analytics

- 7. Volume # 7: Systems and Architecture

- 8. Volume # 8: Cyber Security

- 9. Volume # 9: Software Engineering

- 10. Volume # 10: Silicon Photonics & High Performance Computing

We are pleased to present before you the proceedings of Volume # 7 on "Systems and Architecture." The title "Systems and Architecture" covers the most important, pervasive, top-level, strategic inventions, decisions, and their associated rationales about the overall structure and associated characteristics and behavior. It provides an understanding of the architectures of our computing systems. The title also assists the readers to help them and plan the selection of a processor for a particular project.

Computer Architecture refers to those attributes of a system visible to a programmer. Computer Organization refers to the operational units and their interconnections that realize the architectural specifications. It is a blueprint and functional description of requirements and design implementations for the various parts of a computer, focusing largely on the way by which the central processing unit (CPU) performs internally and accesses addresses in memory. It addresses the challenge of selecting and interconnecting hardware components to create computers that meet functional, performance, and cost goals. It details how a set of software and hardware technologies standards can interact to form a computer system or platform. It refers to how a computer system is designed. The title "Systems and Architecture" also deals with the various innovations and improvements in computing technologies to improve the size, capacity, and performance of modern-day computing systems. This volume is designed to bring together researchers and practitioners from academia and industry to focus on extending the understanding and establishing new collaborations in these areas. It is the outcome of the hard work of the editorial team, who have relentlessly worked with the authors and steered up the same to compile this volume. It will be useful source of reference for the future researchers in this domain. Under the CSI-2015 umbrella, we received over 100 papers for this volume, out of which 32 papers are being published, after a rigorous review processes, carried out in multiple cycles.

On behalf of organizing team, it is a matter of great pleasure that CSI-2015 has received an overwhelming response from various professionals from across the country. The organizers of CSI-2015 are thankful to the members of *Advisory Committee, Programme Committee, and Organizing Committee* for their all-round guidance, encouragement and continuous support. We express our sincere gratitude to the learned *Keynote Speakers* for support and help extended to make this event a grand success. Our sincere thanks are also due to our *Review Committee Members* and the *Editorial Board* for their untiring efforts in reviewing the manuscripts, giving suggestions and valuable inputs for shaping this volume. We hope that all the participated delegates will be benefitted academically and wish them for their future endeavors.

Preface

We also take the opportunity to thank the entire team from Springer, who have worked tirelessly and made the publication of the volume a reality. Last but not least, we thank the team from Bharati Vidyapeeth's Institute of Computer Applications and Management (BVICAM), New Delhi, for their untiring support, without which the compilation of this huge volume would not have been possible.

Delhi, India December 2017 Sunil Kumar Muttoo

# The Organization of CSI-2015

#### **Chief Patron**

Padmashree Dr. R. Chidambaram, Principal Scientific Advisor, Government of India

#### Patrons

Prof. S. V. Raghavan, Department of Computer Science, IIT Madras, Chennai Prof. Ashutosh Sharma, Secretary, Department of Science and Technology, Ministry of Science of Technology, Government of India

#### **Chair, Programme Committee**

Prof. K. K. Aggarwal, Founder Vice Chancellor, GGSIP University, New Delhi

#### Secretary, Programme Committee

Prof. M. N. Hoda, Director, Bharati Vidyapeeth's Institute of Computer Applications and Management (BVICAM), New Delhi

#### **Advisory Committee**

Padma Bhushan Dr. F. C. Kohli, Co-Founder, TCS

Mr. Ravindra Nath, CMD, National Small Industries Corporation, New Delhi

Dr. Omkar Rai, Director General, Software Technological Parks of India (STPI),

New Delhi

Adv. Pavan Duggal, Noted Cyber Law Advocate, Supreme Court of India

Prof. Bipin Mehta, President, CSI

Prof. Anirban Basu, Vice President-cum-President Elect, CSI

Shri Sanjay Mohapatra, Secretary, CSI

Prof. Yogesh Singh, Vice Chancellor, Delhi Technological University, Delhi

Prof. S. K. Gupta, Department of Computer Science and Engineering, IIT Delhi

Prof. P. B. Sharma, Founder Vice Chancellor, Delhi Technological University, Delhi

ix

Mr. Prakash Kumar, IAS, Chief Executive Officer, Goods and Services Tax Network (GSTN)

Mr. R. S. Mani, Group Head, National Knowledge Networks (NKN), NIC, Government of India, New Delhi

#### **Editorial Board**

A. K. Nayak, CSI

A. K. Saini, GGSIPU, New Delhi

R. K. Vyas, University of Delhi, Delhi

Shiv Kumar, CSI

Anukiran Jain, BVICAM, New Delhi

Parul Arora, BVICAM, New Delhi

Vishal Jain, BVICAM, New Delhi

Ritika Wason, BVICAM, New Delhi

Anupam Baliyan, BVICAM, New Delhi

Nitish Pathak, BVICAM, New Delhi

Shivendra Goel, BVICAM, New Delhi

Shalini Singh Jaspal, BVICAM, New Delhi

Vaishali Joshi, BVICAM, New Delhi

# Contents

| A Mathematical AI-Based Diet Analysis and Transformation<br>Model                                                                                  | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| L. K. Gautam and S. A. Ladhake                                                                                                                     | 1  |

| Energy Efficient Measures for Sustainable Development<br>of Data Centers                                                                           | 9  |

| Analysis on Multiple Combinations of Series–Parallel Connections of<br>Super Capacitors for Maximum Energy Transferring to Load in<br>Minimum Time | 21 |

| Pankaj R. Sawarkar, Akhilesh A. Nimje and Praful P. Kumbhare                                                                                       |    |

| Design and Simulation of OTA Using 45 nm Technology                                                                                                | 35 |

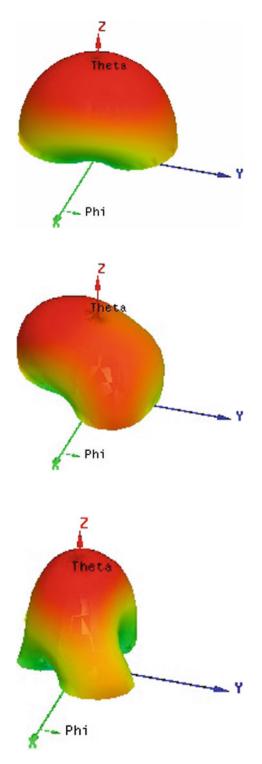

| <b>Design and Analysis of Microstrip Patch Antenna Using DRAF</b><br>Lohini Walia, Gaurav Walia and Umesh Pal Singh                                | 43 |

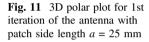

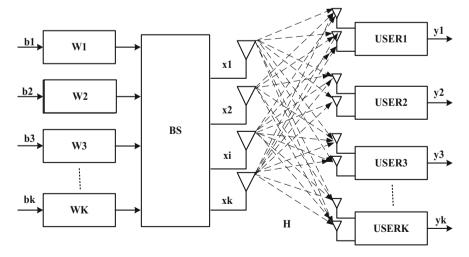

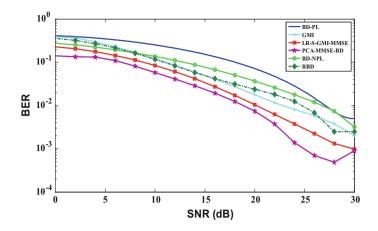

| Principal Component Analysis-Based Block Diagonalization<br>Precoding Algorithm for MU-MIMO System<br>S. B. M. Priya and P. Kumar                  | 53 |

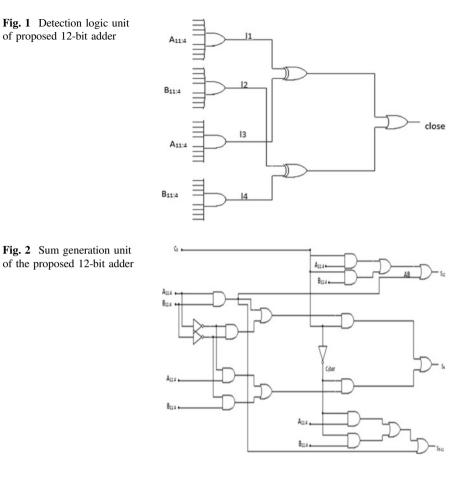

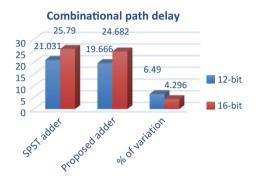

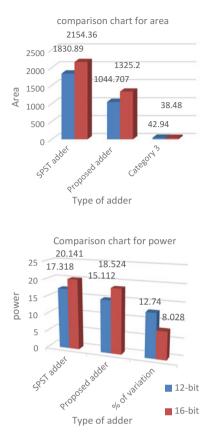

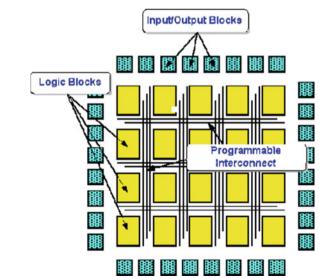

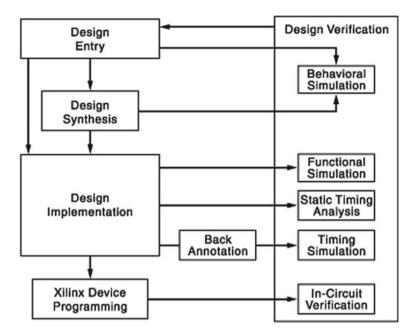

| Low-Power High-Performance Multitransform Architecture Using<br>Run-Time Reconfigurable Adder for FPGA and ASIC<br>Implementation                  | 63 |

| A Review of Dynamic Scheduling Algorithms for Homogeneous<br>and Heterogeneous Systems<br>Mahfooz Alam, Asif Khan and Ankur K. Varshney            | 73 |

| Effective Information Retrieval Algorithm for Linear Multiprocessor<br>Architecture                                                                | 85 |

| Design of Energy-Efficient Random Access Memory Circuit Using<br>Low-Voltage CMOS and High-Speed Transreceiver Logic-I I/O<br>Standard on 28 nm FPGA                                                                             | 95  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tarun Agrawal and Vivek Srivastava         Stub Series Terminal Logic-Based Low-Power Thermal-Aware         Vedic Multiplier Design on 40-nm FPGA                                                                                | 107 |

| Arushi Aggarwal, Bishwajeet Pandey, Sweety Dabbas, Achal Agarwal and Siddharth Saurabh                                                                                                                                           |     |

| LVCMOS-Based Low-Power Thermal-Aware Energy-Proficient<br>Vedic Multiplier Design on Different FPGAs<br>Arushi Aggarwal, Bishwajeet Pandey, Sweety Dabbas, Achal Agarwal<br>and Siddharth Saurabh                                | 115 |

| Timing Constraints-Based High-Performance DES Design andImplementation on 28-nm FPGAVandana Thind, Sujeet Pandey, D. M. Akbar Hussain, Bhagwan Das,M. F. L. Abdullah and Bishwajeet Pandey                                       | 123 |

| Input-Output Standard-Based Energy Efficient UART Design on90 nm FPGARashmi Sharma, Bishwajeet Pandey, Vikas Jha, Siddharth Saurabhand Sweety Dabas                                                                              | 139 |

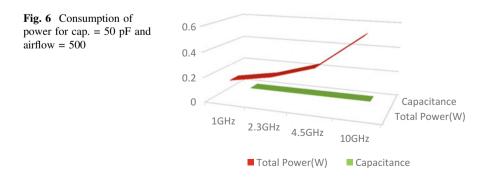

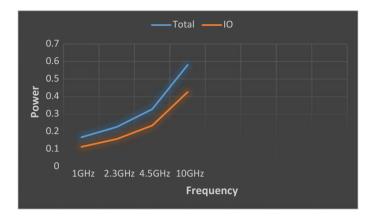

| <b>Different Configuration of Low-Power Memory Design Using</b><br><b>Capacitance Scaling on 28-nm Field-Programmable Gate Array</b><br>Inderpreet Kaur, Lakshay Rohilla, Alisha Nagpal,<br>Bishwajeet Pandey and Sanchit Sharma | 151 |

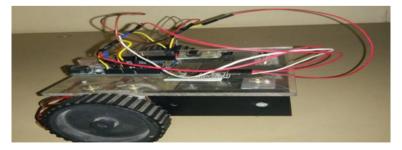

| Ardudroid Surveillance Bot<br>Himanshu Verma, Gaurav Verma, Jaswanth Yarlagadda, Ashish Sharma<br>and Sandeep Banarwal                                                                                                           | 163 |

| <b>Development of Cross-Toolchain and Linux Device Driver</b>                                                                                                                                                                    | 175 |

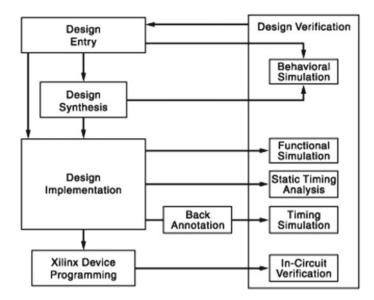

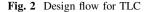

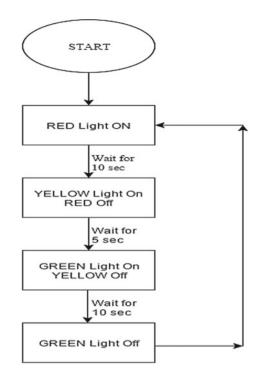

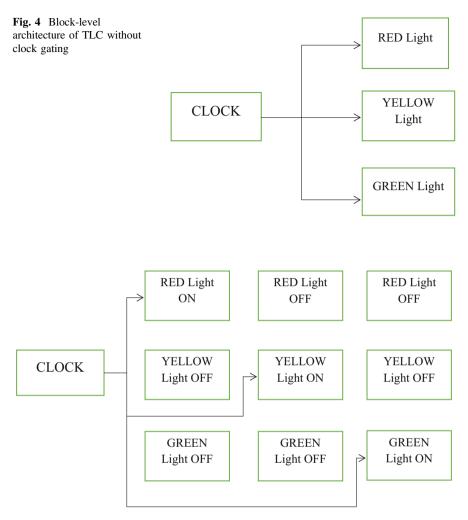

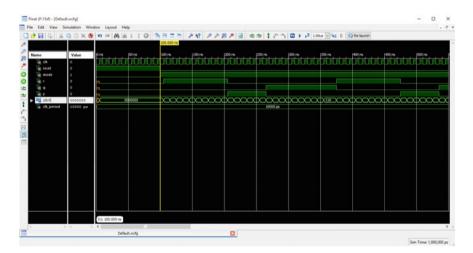

| Design and Implementation of a Green Traffic Light Controller<br>on FPGA Using VHDL<br>Saumil Sachdeva, Sarthak Chowdhury, Sushant Shekhar<br>and Gaurav Verma                                                                   | 187 |

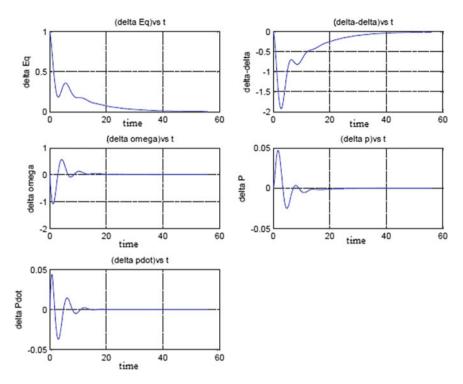

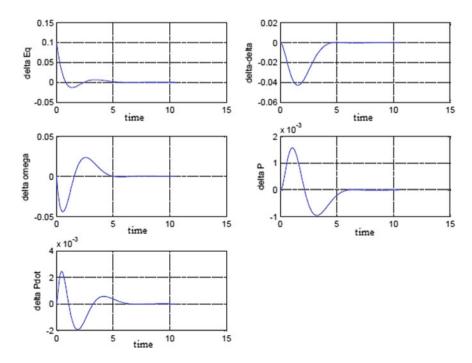

| Suboptimal Controller Design for Power System Model                                                                                                                                                                              | 193 |

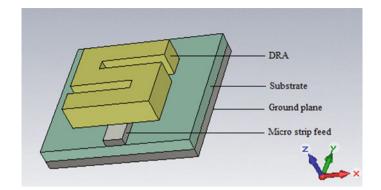

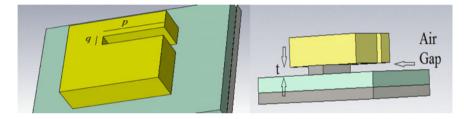

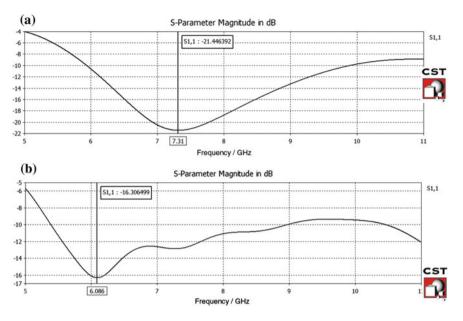

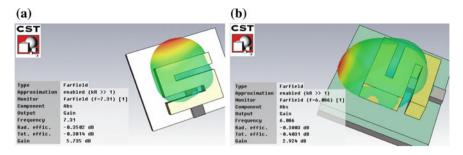

| Designing and Simulation of S-Shaped Dielectric Resonator<br>Antenna with Air Gap<br>Ranjana Singh and Amit Kumar                                                                                                                | 201 |

Contents

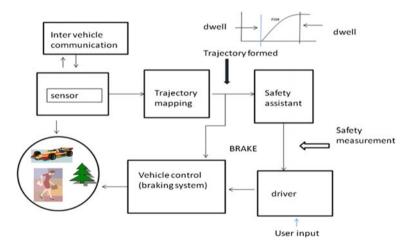

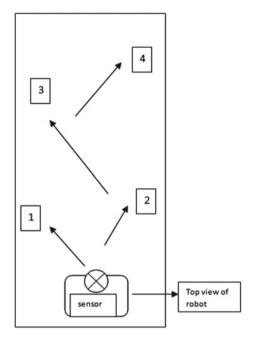

| <b>Trajectory Generation for Driver Assistance System</b> Rupali Mathur, Deepika Rani Sona, Rashmi Ranjan Das and Praneet Dutta                                                                                                       | 209 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

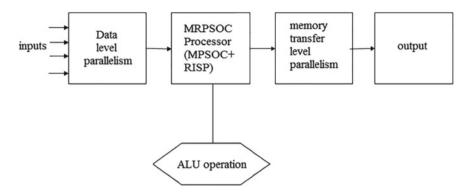

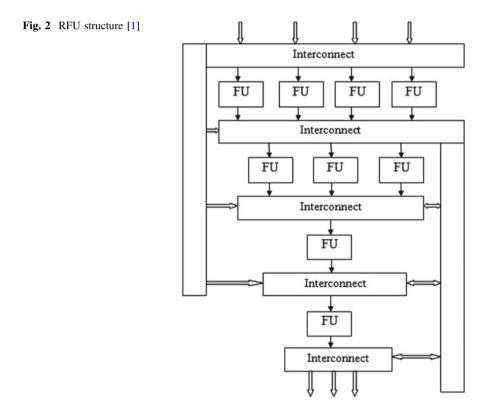

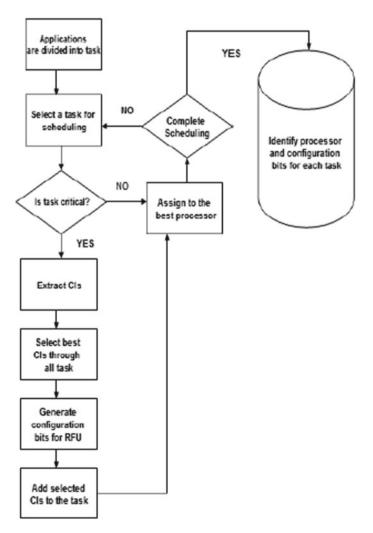

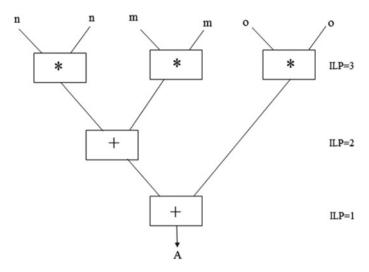

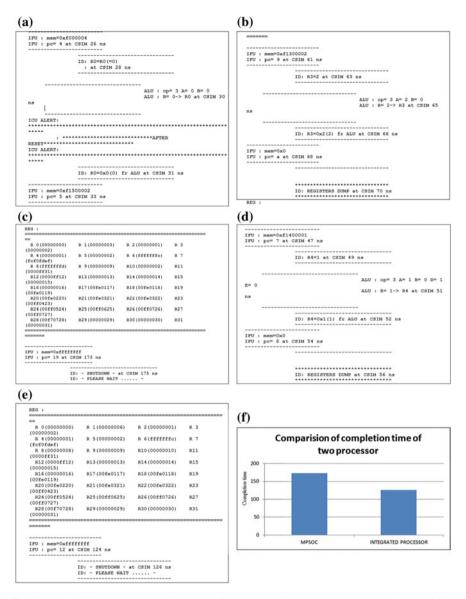

| Performance Enhancement of MRPSOC for Multimedia<br>Applications                                                                                                                                                                      | 219 |

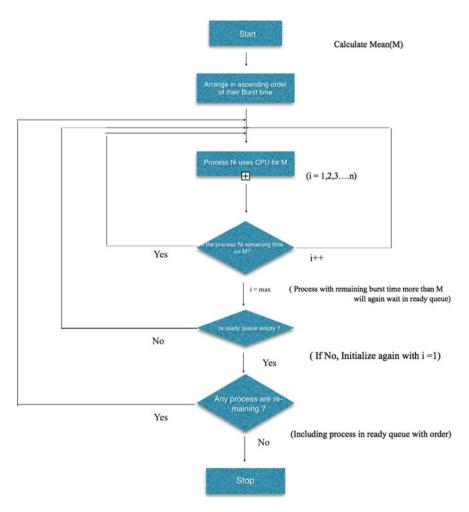

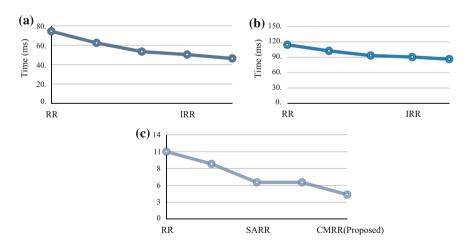

| A New CPU Scheduling Algorithm Using Round-robin and<br>Mean of the Processes<br>N. Sujith Kumar Reddy, H. Santhi, P. Gayathri and N. Jaisankar                                                                                       | 231 |

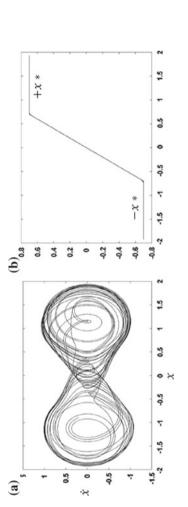

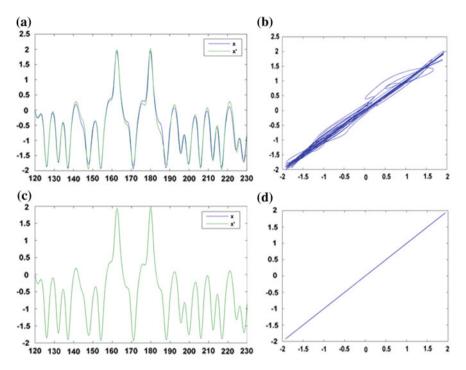

| Synchronization of Two Chaotic Oscillators Through<br>Threshold Coupling<br>A. Chithra and I. Raja Mohamed                                                                                                                            | 241 |

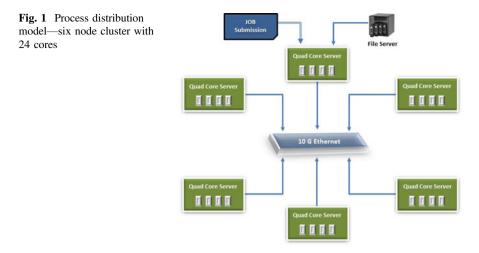

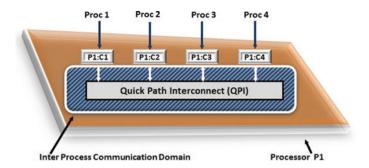

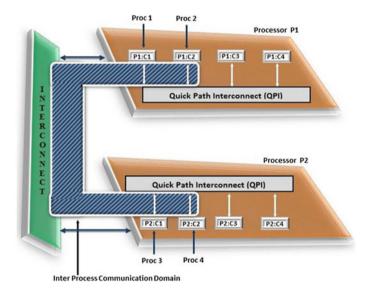

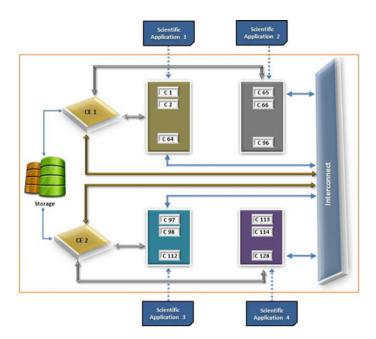

| L3C Model of High-Performance Computing Cluster for<br>Scientific Applications<br>Alpana Rajan, Brijendra Kumar Joshi and Anil Rawat                                                                                                  | 249 |

| <b>Design and Development of Digital Energy Meter on FPGA</b><br>Kautilya Pachorie, Surabhi Agrawal, Varun Maheshwari,<br>Bhagwan Das Devulapalli and A. K. Saxena                                                                    | 261 |

| Design of a Hypothetical Processor Using Re-configurableLogic in VHDLRavinder Nath Rajotiya                                                                                                                                           | 275 |

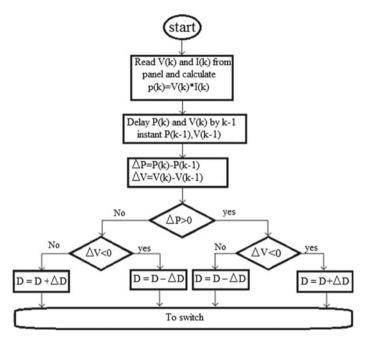

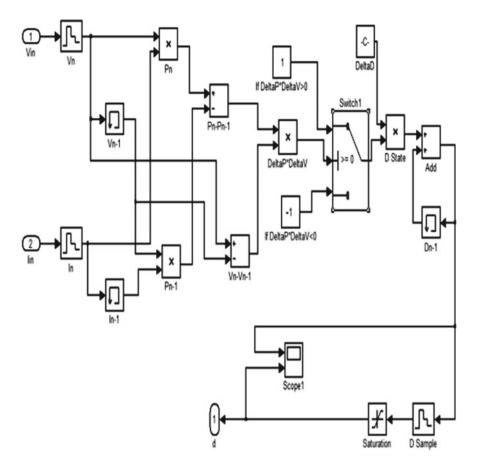

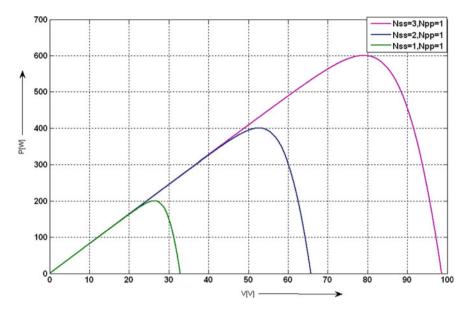

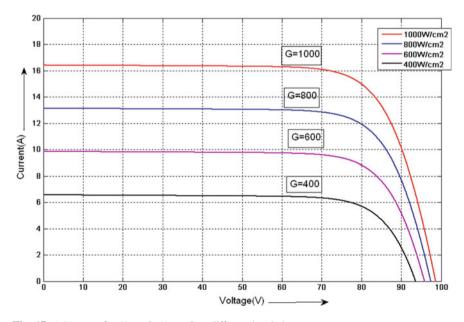

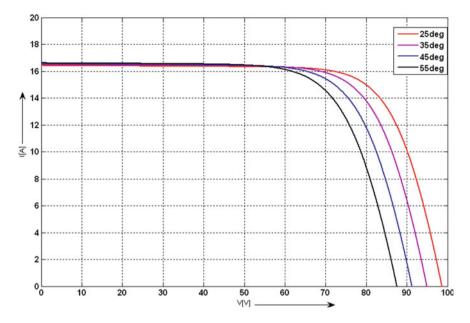

| Aspects Involved in the Modeling of PV System, Comparison<br>of MPPT Schemes, and Study of Different Ambient Conditions<br>Using P&O Method<br>Mohammed Aslam Husain, Asif Khan, Abu Tariq, Zeeshan Ahmad Khan<br>and Abhinandan Jain | 285 |

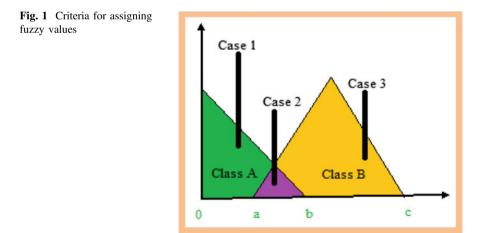

| A Novel Approach for Data Classification Using Neutrosophic<br>Entropy                                                                                                                                                                | 305 |

| SDN Layer 2 Switch Simulation Using Mininet and<br>OpenDayLight<br>Vipin Kumar Rathi and Karan Singh                                                                                                                                  | 319 |

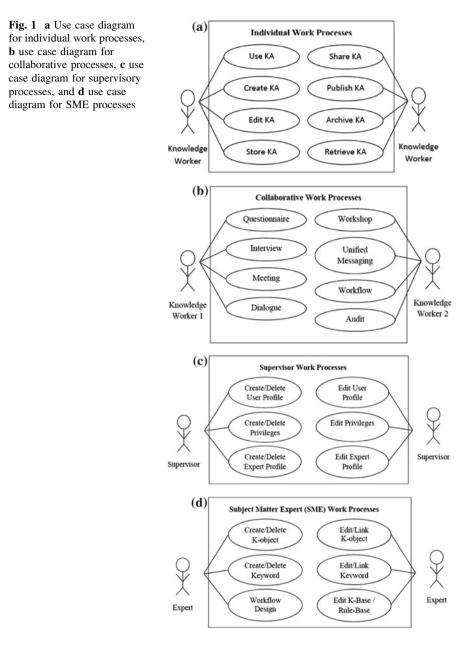

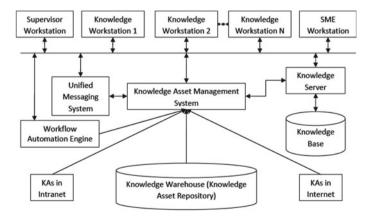

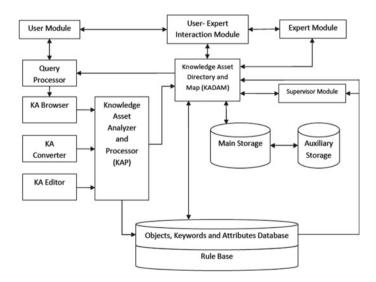

| An Architectural Design for Knowledge Asset ManagementSystemH. R. Vishwakarma, B. K. Tripathy and D. P. Kothari                                                                                                                       | 329 |

## **About the Editor**

**Prof. Sunil Kumar Muttoo** is working as a Professor and Head of the Department of Computer Science, University of Delhi. He completed his M.Sc., M.Phil., Ph.D. at the University of Delhi and his M.Tech. (Computer Science and Data Processing, CSDP) at the Indian Institute of Technology Kharagpur (IIT-KGP). He is involved in research in the field of steganography and digital watermarking. He has published more than 60 papers in international/national journals and conference/ workshop proceedings. He has more than 30 years of teaching and research experience.

# A Mathematical AI-Based Diet Analysis and Transformation Model

L. K. Gautam and S. A. Ladhake

Abstract Inadequacies in nutritional intake can be considered as a major source of adverse effects on the growth and health of individuals in India. A proper balanced diet is essential from the very early stages of life for proper growth, development, to remain active and to reduce the risk of diseases. For those with diabetes, a proper diabetes diet is crucial which depends upon their energy requirements. So a need has been identified to develop educational software which should perform the routine task of analyzing, optimizing, and transforming diet by considering their energy requirements and medical problems. The different nutritional values present in a diet are generally affected by imprecision, which can be represented and analyzed by fuzzy logic. For diet balancing, a metaheuristic local search algorithm is proposed which works in a local search space recording the history of search to make it more effective and optimized. These proposed methods will help users to improve their nutritional intakes by providing detail analysis of their food intake, by providing an optimized diet plan and by suggesting possible changes to make their diet suitable according to their energy requirements.

**Keywords** Energy evaluation • Fuzzy interval • Tabu search • Mathematical AI model

#### 1 Introduction

Inadequacies in nutritional intake can be considered as a major source of adverse effects on the growth and health of individuals in India. The common nutritional problems in India are malnutrition, low birth weight, chronic deficiency in adults, and diet related noncommunicable diseases [1, 2]. To maintain health and increase

L. K. Gautam (🖂) · S. A. Ladhake

© Springer Nature Singapore Pte Ltd. 2018

Sipna College of Engineering and Technology, Amravati, Maharashtra, India e-mail: leenakgautam@gmail.com

S. A. Ladhake e-mail: sladhake@yahoo.co.in

S. K. Muttoo (ed.), *System and Architecture*, Advances in Intelligent Systems and Computing 732, https://doi.org/10.1007/978-981-10-8533-8\_1

life expectancy and to decrease the frequency of cardiovascular diseases, one has to improve its dietary habits which is based on the nutrition values. Thus, a need has been identified to develop educational software which will monitor and perform the daily task of analyzing, optimizing, and correcting the user's diet at home.

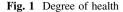

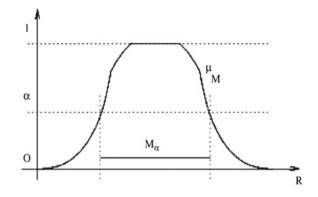

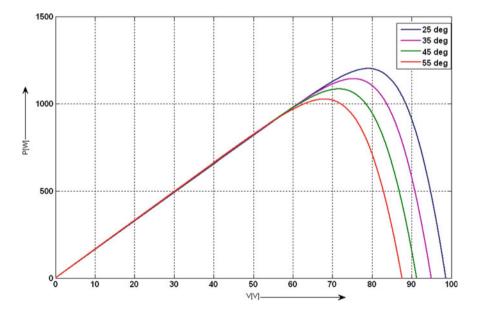

The nutrition intake can be appropriately evaluated and described by employing fuzzy sets and fuzzy arithmetic. Wisram [3] evaluated the nutritional intake status assessment by comparison of intake with the official recommendation for that person. Figure 1 shows the degree of health when varying the intake of one essential nutrient and holding the rest of the diet constant at an optimal level [3].

The work proposed in this paper focuses on the development of interactive AI-based mathematical functionality as an effective solution to support continuous nutritional management. Firstly, we will discuss the general problem statement, and then, the criteria for energy evaluations are described in Sects. 4, and 5 defines some preliminaries on fuzzy sets and fuzzy interval. The background of tabu search is discussed in Sect. 6, and finally, the integration of all these sections, i.e., a proposed work is described in Sect. 7.

#### 2 Problem Statement

A problem exists regarding the inaccurate values of nutrients in foods because the approximate amounts of nutrients available in a certain food are normally known, but there is always a question of their exact amounts. There is often a problem of imprecision with the nutrient values, i.e., their exact amount [4, 5]. This problem may increase if only partial information is available especially for industrially processed foods, but for precisely packed foods (for instance Cheese, Butter, oil, rice, biscuits, etc.), we can obtain the nutrients value precisely. For other foods, for instance vegetables and fruits (banana, apple, etc.), nutrients values varies in a large range, depending on size, growing conditions, freshness, etc.

All this values, i.e., precise and imprecise, have to be stored in a database, and a computer then needs to operate on these values. It should be able to compare these values and should perform all the arithmetic operations [1, 4, 5].

#### **3** Energy Requirements and Its Evaluation

The amount of each nutrient needed for an individual depends upon his/her age, body weight, and physiological status which can be calculated in terms of energy [2].

RDA recommends that energy requirement must be assessed in terms of energy expenditure rather than in terms of energy intake.

i.e. Total Energy Expenditure = Predicted Body Mass Ratio

$$\times$$

Physical activity level (PAL) (1)

Physical activity ratio values for activities performed in a day can be aggregated over that period to yield the physical activity level (PAL). A detailed table of PAR values for different activities is available in the FAO/WHO/UNU 2004 report [2].

#### 3.1 Nutrients Consideration

The primary macronutrients which are important and are considered are protein, fats, and carbohydrates which are converted into energy in different quantities, i.e., 1 g of protein contribute 17 kJ of energy, 1 g of fat constitute 37 kJ of total energy, 1 g of carbohydrates contribute 17 kJ and 1 g of dietary fiber contribute 8 kJ where 1 kJ = 0.239 kcal [3].

#### 4 Fuzzy Arithmetic and Computation

#### 4.1 Preliminaries

In this section, we review the fundamental notions of fuzzy set theory.

**Fuzzy Interval. Definition 1.** A fuzzy interval is a fuzzy set [6] of real numbers, written *M*, having membership function  $\mu_M$ .

$$\forall \alpha \in [0, 1] M_{\alpha} = \{r | \mu_M(r) > = \alpha \text{ (the a-cut of } M) \text{ is a closed interval.} (2)$$

support  $S(M) = \{r j \mu_M(r) > 0\}$  is the largest membership area of *x* (*x* cannot take a value outside *S*(*M*)), whereas the kernel  $M = \{r | \mu_M(r) = 1\}$  is the set of the most plausible values for *x*, also called modal values, and membership function is unimodal and upper semicontinuous [6].

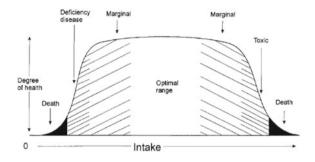

**Fuzzy Computation**. Extension principle [7, 8] is used for performing basic arithmetic operations on trapezoidal fuzzy numbers. Let M and N be two fuzzy

trapezoidal intervals  $(\underline{m}_1, \underline{m}_1, \alpha_1, \beta_1)$  and  $(\underline{m}_2, \underline{m}_2, \alpha_2, \beta_2)$ , respectively. Addition and subtraction on *M* and *N* is given by [7, 8] (Fig. 2).

$$M + N = (\bar{m}_1 + \underline{m}_2, \bar{m}_1 + \bar{m}_2, \alpha_1 + \alpha_2, \beta_1 + \beta_2) M - N = (\bar{m}_1 - m_2, \bar{m}_1 - \bar{m}_2, \alpha_1 + \beta_2, \beta_1 + \alpha_2)$$

(3)

#### 5 Tabu Search Background

Classical methods encounter great difficulty in solving hard optimization problems.

In several cases, we need a modified heuristic approach which provides a solution very close to optimality that tackles the difficult problems at hand and improves the computing time of local search techniques. The metaheuristic approach called tabu search (TS) was proposed by Fred Glover in 1986 to overcome local optima, which is now dramatically changing our ability to solve problems of practical significance [9, 10].

Tabu is an intelligent search process which incorporates adaptive memory and responsive exploration (an intelligent search) [11, 10]. Tabu search can be applied directly to many kinds of decision problems, without the need to transform them into mathematical formulations.

#### 6 Proposed Work

The proposed AI-based mathematical model comprises three modules, viz. analysis module which helps the user to know the nutrients present in the selected diet and its amount. The second module is an optimized module, which gives the perfect diet planner considering the user's medical problem, and lastly the transformation module which can make small changes in the user's diet to make it well balanced while considering the requirements and possible medical problems.

#### 6.1 Diet Analysis Module

A record for each patient is created which contains his/her physical parameters, level of physical activity, and possible medical problems. Considering these entire parameters, energy requirement is calculated by considering Eq. (1). The user is then allowed to choose a food present in a hierarchy and enter the portion for evaluation which gives the correct assessments and suggestions. This evaluation is done by using fuzzy interval which is trapezoidal mentioned in Sect. 4.1. After computing the total energy, it is compared with the prescribed norms, in order to assess whether it is compatible. Let norms and data, represented by the possibility distributions *P* and *D*, respectively. Degree of possibility of matching and degree of necessity of matching are given by N(P, D) and  $\pi(P, D)$

$$\pi(P,D) = \sup \min(\mu_p(\mu), \mu_d(\mu)), N(P,D) = 1 - \pi(P,D)$$

(4)

The result of which is displayed to the user by using interfacing techniques.

#### 6.2 Optimization Module

The food database consists of some diet plan based on different energy requirement prescribed by nutritionist. This diet plans gives total say n combinations. A measurement of appropriate energy and nutrient intake with a respect to the recommendations, or optimal intake, is evaluated by metaheuristic search logic which is further displayed in decreasing order. Optimization solutions provide assistance in the selection of a better diet plan. This module is adaptive in nature as it enhances its diet combinations from transforming module and increasing its efficiency.

#### 6.3 Diet Transformation Module

This module aims at telling the user how he/she may modify his/her diet to make it according to his/her energy requirements and adapted to his/her possible medical problems. It is indeed a difficult task for the user to perform certain modification in their diet to make it well balanced as modifying the weight of a food, for instance, often leads to have the transformation of several nutrients modified at the same time. The diet provided by the user generates a state space which can be solved by applying minimum transformation using an algorithm. Let us assume that for each diet m in "generated diets," the following is known:

- The minimum cost of transformation from the initial diet *m* to noted *g*;

- An estimation of the cost to transform m to its closest solution g.

#### **Proposed Transformation Algorithm 1.**

```

Consider the initial diet m

searchList is empty.

While the stopping criteria is not satisfied do

Check the value of meal according to energy

requirement .Generate diet m's neighbors by applying

transformations Operations by considering history and

constraints. (i.e. m') Then compute evaluation term f = g+h(goal

amount)

m - > m'

Update the search list.

End and return the best solution met.

```

From the above mention algorithm, a specific diet plan is generated by evaluating the required energy requirement and by applying small changes.

#### 7 Concluding Discussion

The AI-based mathematical model for diet optimization and transformation solves the common nutritional problems of public health problems in India using fuzzy arithmetic and a search space metaheuristic algorithm.

Imprecision of data is represented by fuzzy sets, whereas fuzzy arithmetic provides all the necessary computations on these values, which are then compared with the prescribed values present in a database and can be shown to the user by using suitable interfacing techniques. A diet optimization module discussed in Sect. 6.2 gives best diet plan available according to the user's energy requirements. The contents of the daily diet BLSD (breakfast, lunch, snacks, and dinner) are already stored in the database which can be selected on the basis of constraints, preserving their eating practices by using local search metaheuristic algorithm. Finally, the proposed transformation algorithm balances the diet by developing the state space, considering the needs of user and applying minimum possible changes.

For the future, we intend to deal with optimizing diet, based on cost (price) as an additional objective function. It would enlarge the state space of metaheuristic search algorithm and would greatly help in finding more optimized solution.

#### Declaration

The consent from patient is not required in this paper as no patient is physically involved in this study (or during analysis). The data collected during this study are from right resources.

L. K. Gautam

#### References

- 1. Buisson, J.C.: Nutri Educ, a nutrition software application for balancing meals, using fuzzy arithmetic and heuristic algorithm. Artif. Intell. Med. 42, 213–227 (2008)

- 2. Indian Council of Medical Research: Nutrient requirement and recommended dietary allowances for Indians. National Institute of Nutrition (2010)

- 3. Dietary Guidelines of Indians: National Institute of Hyderabad (2010)

- Buisson, J.C.: Knowledge development expert systems and their application in nutrition. Knowledge based systems—techniques and applications. Academic Press, New York, pp. 37–65 (2000)

- 5. Buisson, J.C., Garel, A.: Balancing meals using fuzzy arithmetic and heuristic search algorithms. IEEE Trans. Fuzzy Syst. **2003**(11), 68–78 (2003)

- 6. Zadeh, L.A.: Fuzzy sets as a basis for a theory of possibility. Fuzzy sets Syst

- 7. Zadeh, L.A.: Fuzzy sets. Inf. Control 8, 338-353 (1965)

- 8. Zimmermann, H.J.: Fuzzy set theory and applications. Academic Publisher (2001)

- BoussaïD, I., Lepagnot, J., Siarry, P.: A survey on metaheuristics. Inform. Sci. 237, 82–117 (2013)

- 10. Glover, F., Laguna, M.: Tabu Search. Kluwer Academic Publishers, Boston (1997)

- 11. Bluma, C., Puchingerb, J., Raidlc, G.R., Roli, A.: Hybrid metaheuristics in combinatorial optimization: a survey. Appl. Soft Comput. **11**, 4135–4151 (2011)

# **Energy Efficient Measures for Sustainable Development of Data Centers**

Taniya Aggarwal, Saurabh Khatri and Anu Singla

**Abstract** Information technology (IT) industry today has become the most immense and developing industry of this era. With the growing demands of networking, storage, multimedia, computation, communication, and information, there is a need felt for setting up and maintaining the data centers. Data centers now are the biggest consumers of energy of the IT industry. The energy cost is the most driving factor of data centers. In extend to investment and maintenance price, energy efficient methods and equipment should be implemented in data centers to accomplish the overall progress of the IT sector. Energy management in these centers not only reduces the operating cost of data centers but also reduces emergence of power generation. This paper gives a comprehensive overview about the energy consumption in the data centers and provides energy efficient techniques that would contribute to the continuous and sustainable development.

**Keywords** Data center • Energy efficiency • Virtualization • Computer room air conditioners • Blade servers • Operation and maintenance

S. Khatri

A. Singla

Chitkara University Research and Innovation Network, Chitkara University, Chandigarh, Punjab, India e-mail: anu.singla@chitkara.edu.in

© Springer Nature Singapore Pte Ltd. 2018

T. Aggarwal (🖂)

School of Computer Sciences, Chitkara University, Chandigarh, Punjab, India e-mail: taniyaaggarwal223@gmail.com

School of Mechanical Engineering, Chitkara University, Chandigarh, Punjab, India e-mail: khatri.sbh@gmail.com

S. K. Muttoo (ed.), *System and Architecture*, Advances in Intelligent Systems and Computing 732, https://doi.org/10.1007/978-981-10-8533-8\_2

#### 1 Introduction

There have been the biggest changes in infrastructure of information technology (IT) mainly due to social media, cloud, mobility, greater computing capacity, and big data. The IT business has flourished enormously in last two decades. The rapid growth of IT activities and business has resulted in establishment of large number of data centers. Data centers are the dedicated physical and virtual IT infrastructures used by organizations to support their businesses. Data centers consist of servers, storage equipment, and networking systems. These systems are used to run application software, store, process and serve data to the client.

A data center generally requires substantial backup power supply systems, cooling systems, excessive network connections, and some policy-concerned security systems for running the organization's key applications. Energy consumption of data centers has increased manifolds. Resources reveal that if complete data centers become a nation, it will be attributed as twelfth largest user of electricity internationally. The processors, server power supplies, other server components, storage and communication equipment account for almost 52% of total consumption of a data center [1]. It has become imperative to incorporate green IT technologies in data centers [2]. The motive may be:

- Reduction in energy bills.

- Increase in business profitability and sustainability.

- Optimal utilization of hardware resources with extended useful life.

- Reduce maintenance requirements and less chances of downtime.

- Less carbon emission.

To identify site infrastructure and design topologies of different data centers, a four tiered scale is adopted (a brief provided in Table 1). Tier 4 is the most robust infrastructure for data center.

| No. of<br>tier | Redundancy<br>of capacity<br>components | No. of power<br>distribution paths<br>serving IT equipment | Example                                                                                                        |

|----------------|-----------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Ι              | No                                      | Single non-redundant                                       | Computer room with one UPS,<br>generator, and HVAC cooling system.<br>No redundancy of any system<br>component |

| II             | Yes                                     | Single non-redundant                                       | Similar to Tier I. Redundant capacity components are provided in addition                                      |

| III            | Yes                                     | Multiple                                                   | Similar to Tier II. But IT equipment is supplied with two distinct UPSs                                        |

| IV             | Yes                                     | Multiple                                                   | Multiple paths provided to supply IT<br>equipment. Back power support is<br>provided by redundant generators   |

Table 1

Data center tiers [6]

Energy Efficient Measures for Sustainable ...

The paper is divided into eight sections. Section 1 provides introduction of data centers while Sect. 2 discusses the energy consumption in data centers. Sections 3 and 4 provide the scope of energy conservation by adopting energy efficient technologies and or by efficient operation and maintenance. Conclusions are drawn in Sect. 7, and the future scope is presented in Sect. 8.

#### 2 Scope of Energy Efficient Technologies and Techniques in Data Centers

The 2% of global CO<sub>2</sub> emissions come from IT industry as reported in [3]. Data centers contribute one-fourth of the total CO<sub>2</sub> emission by IT and are growing at a faster pace. Many data centers are consuming far more energy than they need to in relation to the service they provide. This statement can be witnessed by the fact that initial setup of data center costs is only 5% of the total cost of its working for the period of nearly 15–20 years and energy being the major part of it.

Overall energy ingesting in data centers is the sum of energy consumed by several units in operation. A significant management of energy is possible with the reduction of energy usage of each unit and synchronizing the overall setup.

The paper presents the four elementary components of data centers including electrical system, cooling system, IT system and operation and maintenance of the data centers [4]. Section 3 explains the energy management for electrical system, and Sect. 4 sums up the cooling processes and the measures to be taken for energy efficient cooling process. The information for energy management of IT equipment and peripherals is carried out in Sect. 5 while energy efficient operational and maintenance strategies are discussed in Sect. 6.

#### **3** Energy Saving in Electrical System

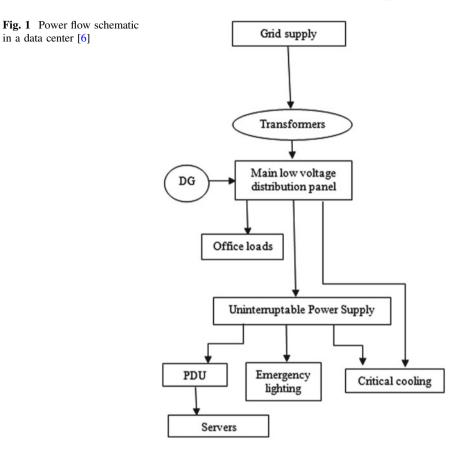

The electrical systems installed in data centers need to be of high efficiency benchmarks that minimize transmission and heat loses. Developing IT industry has increased the total power requirement of data centers by 5%. In this electronic age, backup and retrieval of data are invaluable. The power consumed varies for every data center and depends on the building design and its architecture. The power flow schematic in a data center is shown in Fig. 1.

The major components, their description, and energy efficiency measures are listed in Table 2.

#### 4 Cooling System

Cooling system plays an important role in effective working of data centers. Cooling system consumes 35–40% of the total power consumption. There is large potential of energy saving by adopting energy efficient technologies in cooling systems

Cooling system processes can be divided in two parts:

- A. Conventional method (room cooling technique)

- B. Contemporary method

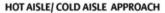

Contemporary method is quite preferable energy efficient system. In this mechanism, racks are arranged in such a way that inlet face toward cold aisle gets cold air from rack and the hot air leaving rack does not go toward the outlet of other racks. Pipes flow through perforated tiles. Perforated tiles and even perforated doors can reduce energy consumption up to 83%. The working of instruments is temperature sensitive. Any increase in operating temperature limits can lead to shut

| Equipment                                       | Description                                                                   | Energy efficient measures                                             |

|-------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| DG sets                                         | Used as power backup                                                          | Steady load conditions and air filtration                             |

| Transformers                                    | Used for stepping up/down voltage                                             | Use K-20 over K-1 or K-13<br>transformers                             |

| Transient voltage<br>surge suppressor<br>(TVSS) | Save sensitive electronic device<br>from voltage fluctuations                 | Must be installed with every<br>PDU                                   |

| Uninterrupted<br>power supply<br>(UPS)          | Save data and devices during instable power                                   | Optimize UPS for maintaining load more than 40%                       |

| Power distribution<br>unit (PDU)                | Distribute power to IT loads                                                  | Optimizing the load on PDU systems                                    |

| Advanced power<br>strip                         | Divides power and provides<br>networking between cabinets and<br>server racks | Regular monitoring and maintenance                                    |

| Cabling                                         | Transmit power to all the units                                               | Maintaining them at high<br>voltage, hence low current and<br>heating |

Table 2 Components of electrical system

Fig. 2 Hot aisle/cold aisle configuration [6]

down of system. So this operation needs to be performed with high precision. The configuration of hot aisle and cold aisle is shown in Fig. 2.

Components of cooling system:

A. *Chilling unit*—Chilling unit is used to transfer energy from one surface to other. Chilling unit used in cooling system can be of different types. Table 3 shows the brief energy efficient strategies for direct expansion system and chilled water system:

| Savings observed in direct expansion system | Traditional approach | With aisle<br>containment (%) | With integrated<br>CAC (%) |

|---------------------------------------------|----------------------|-------------------------------|----------------------------|

|                                             | -                    | 21                            | 33                         |

| Saving observed in chilled water system     | -                    | 15                            | 28                         |

Table 3 Savings observed with cold aisle containment (CAC) unit implementation [6]

- B. *Water pumping unit*—Water pumping unit is used in cooling systems with water cooling chillers to pump water. Some energy efficient measures are as follows:

- Installation of high efficiency pumps

- Entire area utilization in cooling towers

- Reducing pressure of chilled water supply

- Annual checking and calibration of the condenser water supply temperature sensors.

- C. *Precision air conditioner (PAC)*—Working of cooling system under the prescribed temperatures is of utmost importance. Adoption of PAC helps in attaining this by precisely managing heating, cooling, and ventilation requirements of system.

- D. *Air distribution system*—Air distribution system is responsible for distribution of cold air to data center and then recovery of hot air. The process of distributing air to system in itself contains potential to save a lot of energy. Energy efficient techniques which can be implemented are

- Taking cold air closer to heat source.

- Installing rack with low self-weight.

- Use of efficient economizers lower the energy usage intensity by 13%.

- Installation of temperature and humidity sensors for monitoring air intake conditions.

#### 5 IT Equipment

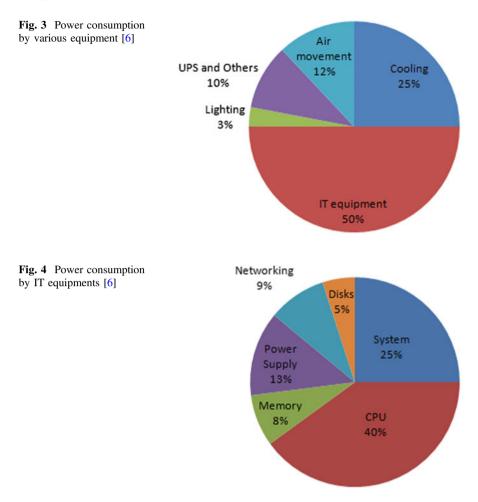

To achieve the maximum efficient output, energy efficient IT equipment should be selected keeping the purchase cost aside. The power flow and the consumption by various equipments in typical data center are shown in Fig. 3.

The breakup of power consumed by IT equipments is shown in Fig. 4.

The energy efficient technologies and techniques for IT equipment are discussed below:

A. Energy efficient server—Blade servers:

Though servers are the most space consuming units but are also the main driving unit of IT sector. Computing servers continuously consume power for running I/O resources, buses, disks, and memory etc. [5]. Most of the servers run below 20% utilization but consume full power [6]. The internal cooling systems can be improved by using variable speed fans in place of constant speed fan for cooling, thereby saving energy. The new energy efficient technologies are developed. Blade server follows modular infrastructure that converges server, storage, and network structure [7]. It speeds up the operations performed which results in speedy delivery of applications and services running in physical and virtual environments. The modular design optimizes the use of

physical space and energy consumption. It enhances the energy efficiency and performance of data center [1]. Blade servers in comparison with power edge rack servers consume around 10% less energy [1].

B. Server virtualization:

The data centers contain a large number of servers, but workload is distributed to a few only keeping the remaining servers idle. The unutilized expensive hardware resources not only consume power and but also require cooling arrangements and periodic maintenance. Power consumption of servers depends on the activity performed. A low-end server may consume nearly half the peak power during idle conditions [8]. It is important to decommission or repurpose the idle servers [9]. Virtualization of servers offers energy savings. Server virtualization increases resource utilization and reduces energy costs by partitioning physical servers into numerous multiple virtual servers. Each virtual server runs its own operating system and applications. The virtual servers run efficiently and reduce energy costs by 10–40% [1]. The application of dynamic reallocation of virtual machines to real-world cloud data centers minimizes energy consumption [10].

- C. Following technologies may improve the data center efficiency [11]:

- *Multi-core processors*: Servers with multi-core processors are able to perform multiple tasks simultaneously in a short span of time reducing power and heat up by 40%.

- Chip-level cooling: In this approach, heat is moved away from the chip.

- Installing new servers over outdated ones may save the energy by 5%.

- Technique of high server density should be adopted.

- 4–5% of total power is consumed by storage systems. This consumption can be reduced by using efficient storage thin chips and by reducing redundancy of data.

A comprehensive power usage study of workloads of data centers is provided in [8].

#### 6 Operation and Maintenance in Data Center

After the designing of data center, operation and maintenance play the major role. The extreme usage of energy can be reduced to lower levels by performing following jobs:

- A. Training of officials and involving operation team in designing—Training officials working in data center easily help in bringing energy requirements of load low. By involving operation team in designing, energy in data center can be managed efficiently with help of designing considerations.

- B. Regular metering—Metering different parameters at appropriate positions can help in getting information about status of energy usage thus helping in analyzing the performance of system.

- C. Housekeeping—A regular housekeeping should be maintained for smooth working in data centers. Clean and dust-free environment would result in better heat transfer from equipment and thus minimize its chances of failure. It would also lead to energy saving.

- D. Lighting design—Light in building has a lot of potential in saving energy. Some measures are:

- Automation of different lighting systems can lead to reduction of electricity up to 14%.

- Task-oriented lighting system shall be used.

- Using of LED lights instead of conventional bulbs.

- Regular maintenance of lighting system (cleaning etc.).

- E. Routine audits—Energy audit data centers regularly so that performance can be regularly checked.

- F. Preventive maintenance—A preventive maintenance would lower the chances of any breakdown of the system, but it should be scheduled at appropriate time.

- G. Efficient storage techniques—A lot of energy in data center is wasted due to improper and unskilled management of storage system. A large numbers of copies of stored data should be avoided, and storage technique should be well enough to avoid usage of extra disk and drive.

Reference [12] has proposed efficient power management architecture for hardware and software in data center. The energy wastage due to variation in demand for IT services asks for power efficient configuration. The different principles of energy management system are presented in [13]. Authors of [5] have proposed energy efficient methodology named DENS based on data center network and traffic characteristics to manage energy consumption in data centers.

#### 7 Conclusion

After studying and analyzing about the energy consumption in data centers, it can be said that on applying little efficient pathways, huge amount of energy can be conserved. Different units have different methods by which energy can be managed. The electrical supply transmission should be carried at high voltage, and optimizing loads on UPS and PDU can reduce energy consumption. Cooling consumes considerable energy in data center. This load can be reduced by using contemporary methods for direct expansion and chilled water system. IT equipment is the largest consumer of energy in data center. Using low power multi-core processors and server virtualization can reduce power wastage. Operation and maintenance team can play a leading role by focusing on some points like better housekeeping, monitoring, and auditing which can help in improving energy efficiency.

#### 8 Future Scope

The increasing energy loads in data centers can be snapped by the continuous evolvement of energy efficient technologies. Operating temperatures needs to be lowered in data centers for efficient operations. Liquid cooling has tremendous potential in cooling servers and appliances more effectively than air conditioning. Adoption of green cloud computing techniques as discussed in [14] and virtualized environment may improve the storage and power efficiency of servers.

#### References

- 1. Energy Logic: Reducing Data Center Energy Consumption by Creating Savings that Cascade Across Systems. A White Paper, Emerson Network Power, Columbus, Ohio (2008)

- Koutitas, G., Demestichas, P.: Challenges for energy efficiency in local and regional data centers. J. Green Eng. 1–32 (2010)

- 3. Data Centre Energy Efficient Design Guide, Sustainable Energy Ireland. Available at http:// www.seai.ie/Your\_Business/Large\_Energy\_Users/Special\_Initiatives/Special\_Working\_Groups/ Data\_Centre\_Special\_Working\_Group\_SpinI/Data%20Centre%20Energy%20Efficient%20 Design%20Guide.pdf

- Chong, F.T., Heck, M.J.R., Ranganathan, P., Saleh, A.A.M., Wassel, H.M.G.: Data center energy efficiency: improving energy efficiency in data centers beyond technology scaling. Design & Test, IEEE 31(1), 93–104 (2014)

- Kliazovich, D., Bouvry, P., Khan, S.U.: DENS: data center energy-efficient network-aware scheduling. In: Green Computing and Communications (GreenCom), 2010 IEEE/ACM International Conference on & International Conference on Cyber, Physical and Social Computing (CPSCom), pp. 69–75, 18–20 Dec 2010

- 6. Energy Efficiency Guidelines and Best Practices in Indian Data Centres. Published by Bureau of Energy Efficiency (BEE), Ministry of Power, Government of India

- 7. Report, FEMP Best Practices Guide for Energy-Efficient Data Center Design. National Renewable Energy Laboratory, 2010, Revised Mar 2011

- Fan, X., Weber, W.-D., Barroso, L.A.: Power provisioning for a warehouse-sized computer. In: ISCA'07, San Diego, California, USA, 9–13 June 2007

- 9. Cole, D.: Data center energy efficiency-looking beyond PUE, No Limits Software, White Paper, #4 (2011)

- Beloglazov, A., Buyya, R.: Energy efficient allocation of virtual machines in cloud data centers. In: 2010 10th IEEE/ACM International Conference on Cluster, Cloud and Grid Computing (CCGrid), pp. 577–578, 17–20 May 2010

- 11. Five Strategies for Cutting Data Center Energy Costs through Enhanced Cooling Efficiency. Emerson Network Power and Liebert Corporation (2007)

- Raghavendra, R., Ranganathan, P., Talwar, V., Wang, Z., Zhu, X.: No "power" struggles: coordinated multi-level power management for the data center. In: ASPLOS'08, Seattle, Washington, USA, 1–5 Mar 2008

- Dumitru, I., Fagarasan, I., Iliescu, S., Said, Y.H., Ploix, S.: Increasing energy efficiency in data centers using energy management. In 2011 IEEE/ACM International Conference on Green Computing and Communications (GreenCom), pp. 159–165, 4–5 Aug 2011

- Buyya, R., Beloglazov, A., Abawajy, J.: Energy-efficient management of data center resources for cloud computing: a vision, architectural elements, and open challenges. In: Proceedings of the 2010 International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA 2010), Las Vegas, USA, 12–15 July 2010

# Analysis on Multiple Combinations of Series–Parallel Connections of Super Capacitors for Maximum Energy Transferring to Load in Minimum Time

Pankaj R. Sawarkar, Akhilesh A. Nimje and Praful P. Kumbhare

**Abstract** High farad values of ultra capacitors (UCs) are associated with very large current during charging. This paper proposes numerous switching configurations within ultra capacitor units supplying energy to load in efficient way. This reconfiguration dealt with series–parallel connections with reference of load voltage maximum and minimum limit. By using proper switching, 99% of stored energy can be delivered to load in minimum time. In normal case, only 73% stored energy could be utilized by load. Proposed scheme shows that operation will become faster, i.e., 57.67–75.68%.

Keywords Super capacitor · Charging · Discharging · Reconnection

#### 1 Introduction

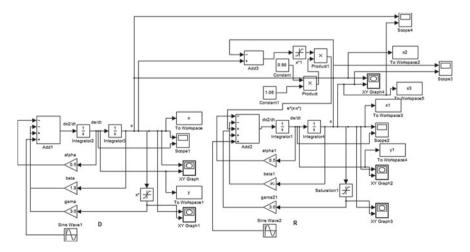

For good performance of battery, such hybrid systems required fixed current charger and separation of battery during the process. This has been described by Jeong et al. [4]. Economical solution has been suggested by Chen and Lai [3] by using microprocessor unit switching over take place from constant current charging to constant voltage charging in electric vehicle application drive required high starting current and during regenerative braking involve high rates of discharging current. Chau and Chan [2] have reported that, which did not required voltage feedback or current feedback [1, 5]. Reconfiguration within ultra capacitor bank for reducing charging current. Simulation of MATLAB Simulink and results were

P. R. Sawarkar  $(\boxtimes) \cdot A$ . A. Nimje  $(\boxtimes) \cdot P$ . P. Kumbhare

Electrical Engineering, Guru Nanak Institute of Engineering and Technology, Nagpur, India

e-mail: pankaj.sawarkar@gmail.com

A. A. Nimje e-mail: nimjeakhilesh29@gmail.com

P. P. Kumbhare e-mail: praf369@gmail.com

© Springer Nature Singapore Pte Ltd. 2018

S. K. Muttoo (ed.), *System and Architecture*, Advances in Intelligent Systems and Computing 732, https://doi.org/10.1007/978-981-10-8533-8\_3

confirmed by mathematical calculation, which indicate that during charging process using similar reconfiguration charging current can be reduced. It shows that charging time can be reduced to 330 from 480 s in constant current charging method and it is 31.35% faster. In constant voltage method, charging time reduced to 96 from 120 s and the process is 20% faster [7]. Time required to extract energy reduces to 72% in typical cases of discharging. Advantages of fast operation during charging using similar reconfiguration have also been pointed out. Typically, 20–30% faster operations are expected. The proposed reconfiguration has an additional advantage of extracting about 72% of the energy stored by the capacitor, in this reduced time period reported by Sawarkar et al. [6].

#### 1.1 Proposed Scheme

This scheme is suggesting the use of number of capacitors for required faradays value. These capacitors will connected series and parallel for buildup required voltage level. As soon as load voltage will reduce to minimum operating voltage of load then connections of capacitors will be change in another set of series–parallel connection. This process will continue till all the capacitors connected in series. This paper has analyzed different cases which are tabled below.

| Case no.     | Capacitance $\times$ no. of units | Total capacitance (F) |

|--------------|-----------------------------------|-----------------------|

| Basic scheme | $32F \times 1$                    | 32                    |

| Case 1       | $16F \times 2$                    | 32                    |

| Case 2       | $8F \times 4$                     | 32                    |

| Case 3       | $4F \times 8$                     | 32                    |

Analysis is done on each case separately with percentage of energy transfer, time required, etc.

#### 1.2 Basic Scheme

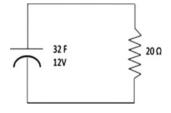

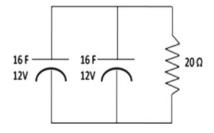

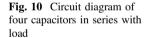

In this case, a single unit of pre-charged super capacitor is connected to the load. The capacitance of capacitor is of 32F and load resistance is of 20  $\Omega$  (Fig. 1).

Fig. 1 Series R-C circuit

It will be series R–C circuit and time constant will be equal to 640 s. This capacitor is pre-charged at voltage 12 V. Enc is the energy available in capacitor which can be calculated by

$$Enc = \frac{1}{2}CV^2 = 2304 J$$

(1)

Time required to reducing capacitor voltage from 12 V to zero will be 2560 s. (2)

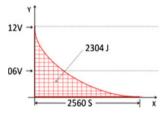

Figure 2 shows voltage with respect to time.

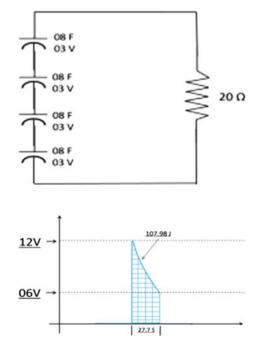

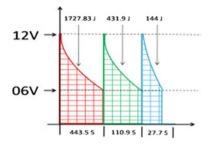

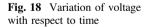

Above scheme will deliver 2304 J to load, i.e., 100% energy in 2560 s. If system is having lower voltage cutoff limit, then some percentage of energy will not supply to load. This voltage cutoff limit is considered as 6 V. The energy supplied to the load will be 1727.83 J in 443.5 s and unutilized energy will be 576.17 J which is calculated in case-1. Following graph shows variation of load voltage with system lower voltage limit.

From the above following statement can be done

$$Total time = 443.52 \,s. \tag{3}$$

Total Energy supplied to load in

$$V_L > 6 \text{ V}$$

is 1727.83 J (4)

Percentage of energy supplied to load in  $V_L > 6 \text{ V}$  is  $\left(\frac{1727.83}{2304}\right) \times 100$ = 74.99% (5)

Percentage of time utilized

$$\left(\frac{443.52}{2560} \times 100\right) = 17.32\%$$

(6)

Refer Fig. 3 for graphical representation of voltage with respect to time.

**Fig. 2** Graphical representation of voltage with respect to time

Fig. 3 Variation of voltage with respect to time

#### 2 Case-1

In this case, two units of 16F 12 V pre-charge capacitor are used. The voltage cutoff limit is 6 V which is discussed in 1.1 and 1.2.

#### 1.1

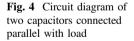

Pre-charged capacitors are connected in parallel to load up to 6 V (Fig. 4).

Time required for reducing capacitor voltage from 12 to 6 V will be

$$6 V = 12 V(e^{-t1/RC}) = 12(e^{-t/640})$$

i.e.  $t_1 = 443.52 s.$  (7)

In 443.52 s energy supplied to load will be

$$E = 7.2 \int_{0}^{443.52} e^{-2t/640} dt = 1727.83 J$$

(8)

Refer Fig. 4 the lower limit of voltage cutoff is 6 V. During this period, energy supplied to load is 1727.83 J from Eq. (8). In 443.5 s from Eq. (7) energy remains in capacitor will be

$$(2304 - 1727.83) = 576.17 \,\mathrm{J}.\tag{9}$$

Remaining 576.17 J can be utilized only if  $V_L > V/2$ , this can be done by connecting capacitors in series discussed in 1.2.

Analysis on Multiple Combinations ...

1.2

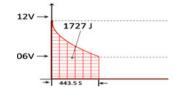

After 1.1 configuration connection will be change to series connection shown in Fig. 5.

Equivalent capacitance will be 8F, energy available will be

$$Enc = \frac{1}{2}CV2 = 576 \, J \tag{10}$$

Time constant of the circuit will be  $20 \times 8 = 160$  s. (11)

Time required for reducing capacitor voltage from 12 to 6 V will be  $t_2 = 110.9$  s (12)

Then energy supplied to load in  $t_2$  s will be

$$E = 7.2 \int_{0}^{110.9} e^{-2t/160} dt = 431.99 J$$

(13)

Figure 6 shows the graphical representation of voltage with respect to time in above case.

In operation described in 1.2, load is disconnected at load voltage becomes 6 V. Again energy remains in capacitor will be

$$2304 - 1727.83 - 431.99 = 144.18 \,\mathrm{J} \tag{14}$$

This 144.18 J cannot be utilized by load due to load voltage limit.

Time required for 100% energy supplied will be  $4 \times 20 \times 8 = 640$  s. (15)

#### 1.3

From 1.1 and 1.2

Total time =

$$443.5 + 110.9 = 554.4$$

s. (16)

Total Energy supplied to load in  $V_L > 6$  V is 1727 + 431.9 = 2158 J (17)

Percentage of energy supplied to load in  $V_L > 6 \text{ V is}\left(\frac{2158}{2304}\right) \times 100 = 93.66\%$ (18)

Percentage of time utilized

$$\left(\frac{554.4}{2560} \times 100\right) = 21.65\%$$

(19)

Total time consumed for 100% energy drained is 443.5 + 640 = 1083.5 s (20)

Figure 7 shows the variation of voltage in 1.1 and 1.2.

**Fig. 7** Graphical representation of voltage with respect to time

#### 3 Case-2

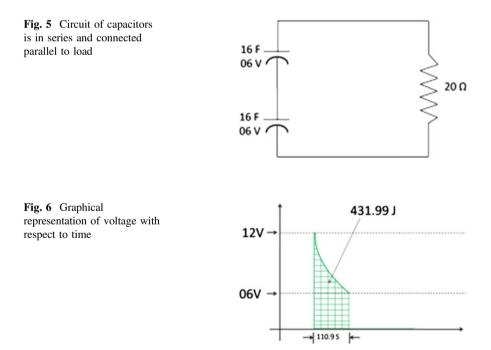

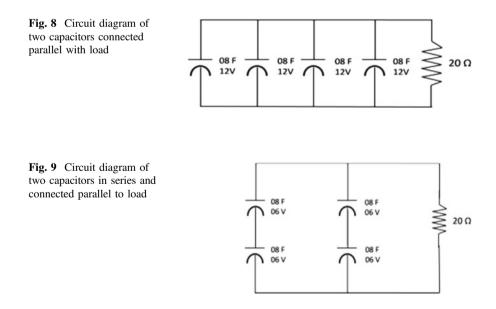

In this case, 8F capacitance 12 V pre-charge capacitor is used. The capacitors connected are discussed in 2.1, 2.2, and 2.3.

#### 2.1

Charged capacitors are connected in parallel to load up to load voltage becomes 6 V shown in Fig. 8.

From Eq. (7),  $t_1 = 443.52$  s and from Eq. (8) 1727.83 J will supplied to load. Refer Fig. 3. Energy remains in capacitor will be 576.17. J from Eq. (9). Remaining 576.17 J can be utilized by connecting capacitors in connection discussed in 2.2.

#### 2.2

After 2.1 configurations, connection will be changed as two capacitors will be connected in series and such two combinations will be connected in parallel with load shown in circuit diagram (Fig. 9).

From Fig. 9 Equivalent capacitance will be 8F, energy = 576 J, time constant =  $20 \times 8 = 160$  s. From Eq. (12)  $t_2 = 110.9$  s. From Eq. (13) energy supplied is 110.9 s will be 431.99 J. In operation described in 2.2, load is disconnected at load voltage becomes 6 V. Again energy remains in capacitor will be 144.18 J from Eq. (14) remaining 144.18 J can be utilized by applying configuration discussed in 2.3.

2.3

After 2.2 configurations, all capacitors will be connected in series shown in the Fig. 10.

Equivalent capacitance will be 2 F. Energy available will be 144 J (21)

Time constant of the circuit will be  $(\mathbf{R} \times \mathbf{C}) = 20 \times 2 = 40 \,\mathrm{s}.$  (22)

Time required for reducing capacitor voltage to 6 V will be  $t_3 = 27.7$  s. (23)

Then energy supplied to load in 27.7 s. will be

$$E = 7.2 \int_{0}^{27.7} e^{-2t/40} dt = 107.98 J$$

(24)

Figure 11 shows the graphical representation of voltage with respect to time in above case.

In operation described in 2.3, load is disconnected at load voltage becomes 6 V. Again energy remains in capacitor will be

$$2304 - 1727.83 - 431.99 - 107.98 = 36.29 \,\mathrm{J} \tag{25}$$

This 36.29 J cannot be utilized by load due to load voltage limit.

Time required for 100% energy supplied will be  $4 \times 20 \times 2 = 160$  s. (26)

**Fig. 11** Graphical representation of voltage with respect to time

Fig. 12 Graphical representation of voltage with respect to time

# **2.4** From 2.1, 2.2, and 2.3

Total time =

$$443.5 + 110.9 + 27.7 = 582.2 \,\mathrm{s.}$$

(27)

Total Energy supplied to load in  $V_L > 6$  V is 1727 + 431.9 + 107.98 = 2267.71 J (28)

Percentage of energy supplied to load in  $V_L > 6 \text{ V is}\left(\frac{2267.71}{2304}\right) \times 100 = 98.42\%$ (29)

Percentage of time utilized

$$\left(\frac{582.2}{2560} \times 100\right) = 22.73\%$$

(30)

Total time consumed for 100% energy drained is 443.5 + 110.9 + 160 = 714.4 s. (31)

Figure 12 shows the variation of voltage in 2.1, 2.2, and 2.3.

#### 4 Case-3

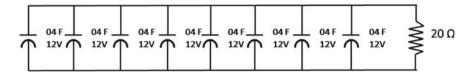

In this case, 4F capacitance 12 V pre-charge capacitor is used. The connections are discussed in 3.1, 3.2, and 3.3.

#### 3.1

Charged capacitors are connected in parallel to load up to load voltage becomes 6 V as shown in circuit diagram (Fig. 13).

From Eq. (7)  $t_1 = 443.52$  s. From Eq. (8) energy supplied to load in 443.52 s will be 1727.83 J. Refer Fig. 3. During this period energy supplied to load is 1727.83 J from Eq. (8). Time required is 443.5 s. From Eq. (7) energy remains in

Fig. 13 Circuit diagram of eight capacitors connected parallel with load

capacitor will be 576.17 J from Eq. (9). Remaining 576.17 J can be utilized by connecting capacitors in connection discussed in 3.2.

#### 3.2

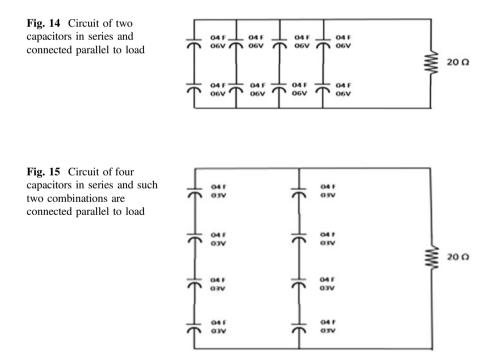

After 3.1 configurations connection will be changed as shown in Fig. 14.

Equivalent capacitance will be 8F. Energy available will be Enc  $=\frac{1}{2}CV^2 = 576$  J.

Time constant of the circuit will be  $(R \times C) = 20 \times 8 = 160$  s. From Eq. (12) time required for reducing capacitor voltage from 12 to 6 V will be  $t_2 = 110.9$  s. From Eq. (13) energy supplied to load in 110.9 s will be 431.99 J. Refer Fig. 6. Again energy remains in capacitor will be 144.18 J from Eq. (14). Remaining 144.18 J can be utilized by applying configuration discussed in 3.3.

#### 3.3

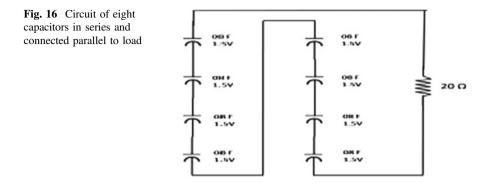

After 3.2 configurations four capacitors will be connected in series and such two branches are connected in parallel to load shown in Fig. 15.

Equivalent capacitance will be 2F. Energy available will be Enc 144 J time constant of the circuit will be 40 s. Time required for reducing capacitor voltage from 12 to 6 V will be, i.e.,  $t_3 = 27.7$  s. Then energy supplied to load in 27.7 s will be E = 107.98 J. Refer Fig. 11 by connecting capacitors in configuration as discussed in 3.4.

#### 3.4

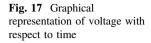

After 3.3 configurations connection is as shown in following circuit diagram (Fig. 16).

Equivalent capacitance will be 0.5 F. Energy available will be Enc = 36 J (32)

Time constant of the circuit will be  $(R \times C) = 20 \times 0.5 = 10$  s. (33)

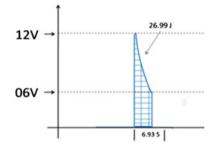

Time required for reducing capacitor voltage from 12 to 6 V will be

$$6 = 12(e^{-t/10}), t_4 = 6.93 \,\mathrm{s.} \tag{34}$$

Then energy supplied to load in 27.7 s will be  $E = 7.2 \int_{0}^{6.93} e^{-2t/10} dt = 26.99 J$ (35)

Figure 17 shows graphical representation of voltage with respect to time in above case.

Remaining 9.3 J will be unutilized due to  $V_L > V/2$  condition. Time required for 100% energy consumed will be

$$4 \times 20 \times 0.5 = 40 \,\mathrm{s.}$$

(36)

**3.5** From 3.1, 3.2, 3.3, 3.4

Total time of discharge

$$= 589.09 \,\mathrm{s.}$$

(37)

Total Energy supplied to load in

$$V_L > 6$$

V is = 2294.79 J (38)

Percentage of energy supplied to load in  $V_L > 6 \text{ V is}\left(\frac{2294.79}{2304}\right) \times 100 = 99.60\%$ (39)

Percentage of time utilized

$$\left(\frac{589.09}{2560} \times 100\right) = 23.01\%$$

(40)

Total time consumed for 100% energy drained is = 622.15 s. (41)

Figure 18 shows the variation of voltage in 3.1, 3.2, 3.3, 3.4.

#### 4.1

Tables 1 and 2 show consulate result obtained in all cases.

Analysis on Multiple Combinations ...

| Case | No. of<br>capacitors<br>used | Capacitance, time in seconds, energy supplied |                           |                         |                          |

|------|------------------------------|-----------------------------------------------|---------------------------|-------------------------|--------------------------|

|      |                              | Circuit 1                                     | Circuit 2                 | Circuit 3               | Circuit 4                |

| 0    | 01                           | 32F, 443.5 s,<br>1727.83 J                    | NA                        | NA                      | NA                       |

| 1    | 02                           | 32F, 443.5 s,<br>1727.83 J                    | 8F, 110.95 s,<br>431.99 J | NA                      | NA                       |

| 2    | 04                           | 32F, 443.5 s,<br>1727.83 J                    | 8F, 110.95 s,<br>431.99 J | 2F, 27.7 s,<br>107.98 J | NA                       |

| 3    | 08                           | 32F, 443.5 s,<br>1727.83 J                    | 8F, 110.95 s,<br>431.99 J | 2F, 27.7 s,<br>107.98 J | 0.5F, 6.93 s,<br>26.99 J |

Table 1 Variation of Capacitance, Time & Energy in each case

Table 2 Energy supplied to load, Percentage of energy supplied to load, Percentage of time utilise, percentage of faster operation

| Case | No. of<br>capacitors<br>used | Total energy<br>supplied to load<br>during<br>Vl > 6 V (J) | % of energy<br>supplied to load<br>during<br>Vl > 6 V (%) | % of time<br>utilized by load<br>during<br>Vl > 6 V (%) | % of<br>faster<br>operation<br>(%) |

|------|------------------------------|------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|------------------------------------|

| 0    | 01                           | 1727.83                                                    | 74.81                                                     | 17.32                                                   | 00.00                              |

| 1    | 02                           | 2159.7                                                     | 93.73                                                     | 21.65                                                   | 57.67                              |

| 2    | 04                           | 2267.71                                                    | 98.42                                                     | 22.73                                                   | 72.09                              |

| 3    | 08                           | 2294.79                                                    | 99.60                                                     | 23.01                                                   | 75.68                              |

#### 5 Conclusion

Series–parallel reconnections lead to faster processes during exchange of energy in case of multiple capacitors. It deserves attention for applying to industrial system. In industrial applications for ride-through applications in drives, and applications as short duration UPS, super capacitor banks are used. It is necessary work on prototypes', to conclude the quantitative advantages of the proposed scheme, when implemented for real-life strategic applications. Super capacitor is used for driving load with above proposed method. It is conforming that basic case to case-3 percentage of energy supplied to load during Vl > 6 V is increasing, i.e., (74.81–99.60%). Percentage of time utilized by load during Vl > 6 V is also increasing order, i.e., (17.32–23.01%), and operation will become more faster as case goes on increasing, i.e., (57.67–75.68%).

#### References

- Kotsopoulos, A., Duarte, J.L., Hendlix, M.A.M.: A converter to interface ultra-capacitor energy storage to a fuel cell system. Dept. of Electrical Engineering, Technical University of Eindhoven. The Netherlands, IEEE, 4–7 May, vol. 2, pp. 827–832 (2004)

- Chan, M.S.W., Chau, K.T., Chan, C.C.: Effective charging method for ultra capacitors. J. Asian Electric Vehicles 3(2), 771–776 (2005)

- Chen, B.Y., Lai, Y.S.: New digital-controlled technique for battery charger with constant current and voltage control without current feedback. IEEE Trans. Ind. Electron. 59(3), 1545– 1553 (2012)

- Jeong, I.W., Kim, L.S., Guse, G.I., Rim, G.M.: Design of 35 kJ/s 25 kV capacitor charging power supply for pulsed power systems. In: IEEE Conference of the IEEE Industrial Electronics Society Busan, Korea, vol. 3, pp. 2860–2863, 2–6 Nov 2004

- 5. Shin, D., Kim, Y., Seo, J., Chang, N.: Battery-super capacitor hybrid system for high-rate pulsed load applications. In: EDAA, pp. 1–4, 14–18 Mar 2011

- Sawarkar, P.R., Tarnekar, S.G., Bodkhe, S.B.: Improvement in energy transactions in ultra capacitor banks by series/parallel re-connection. Int. J. Electr. Eng. 5(5), 641–652 (2012)

- Sawarkar, P.R.: Reduction in charging current of super capacitor by series parallel connection. Int. J. Innov. Sci. Eng. Technol. 2(4), 1015–1020 (2015)

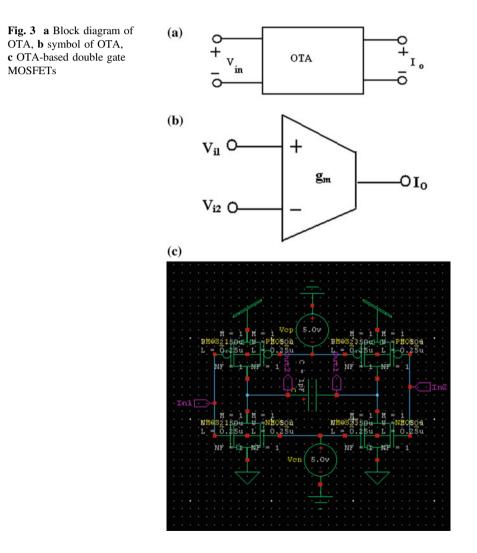

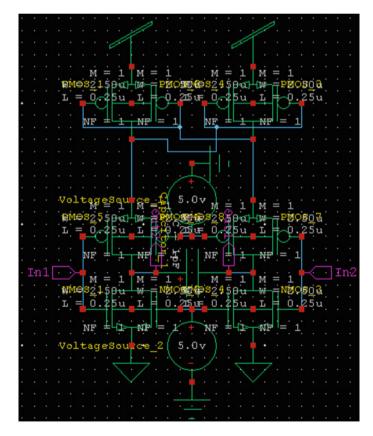

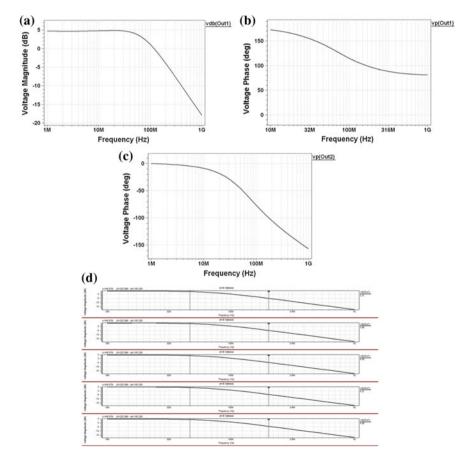

# Design and Simulation of OTA Using 45 nm Technology

Amit Sharma, Sansar Chand and Navneet Gill

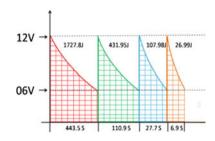

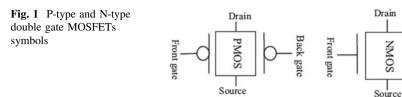

**Abstract** OTA is very popular in electronics industry due to its large number of applications. Double gate MOSFETs are strong contenders for nanoscale region due to its better control over SCEs. In this paper, emphasis is to design low power, better phase margin OTA using double gate MOSFETs. The simulations are done at 45 nm technology.

**Keywords** Analog tunable circuits  $\cdot$  Gain  $\cdot$  Low supply voltage Phase margin  $\cdot$  DG MOSFETs  $\cdot$  OTA

#### 1 Introduction

Electronics devices based on silicon is large as like—laptops, palmtops, cellular, and many more. Due to great dealing out of silicon-based devices, silicon has made system on chip possible. A low power and voltage design to recompense increasing number of devices on chip is aimed. With the breach of 90 nm, silicon industry has moved to nanoarea to according to ITRS [1]. There are number of problems arises due scaling in conventional bulk CMOS device like SCE's [2, 3], threshold voltage, non-scaling of vertical dimensions. These problems degrade the performance and

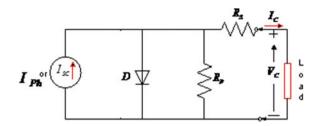

A. Sharma (🖂)