Lecture Notes in Electrical Engineering 471

Jaume Anguera Suresh Chandra Satapathy Vikrant Bhateja K. V. N. Sunitha *Editors*

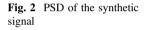

# Microelectronics, Electromagnetics and Telecommunications

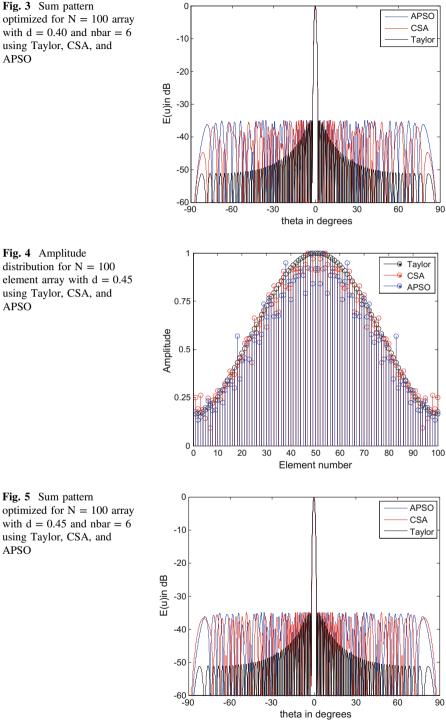

Proceedings of ICMEET 2017

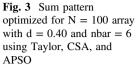

# Lecture Notes in Electrical Engineering

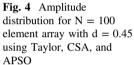

#### Volume 471

#### **Board of Series editors**

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Haibin Duan, Beijing, China Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Bijaya Ketan Panigrahi, New Delhi, India Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Haitao Wu, Beijing, China Junjie James Zhang, Charlotte, USA

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

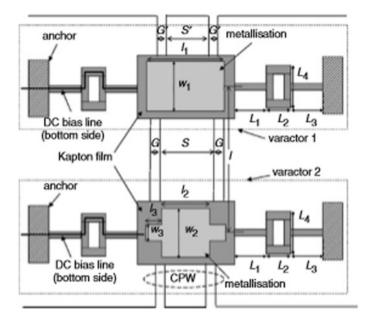

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

More information about this series at http://www.springer.com/series/7818

Jaume Anguera · Suresh Chandra Satapathy Vikrant Bhateja · K. V. N. Sunitha Editors

# Microelectronics, Electromagnetics and Telecommunications

Proceedings of ICMEET 2017

*Editors* Jaume Anguera Department of Electronics and Telecommunication Ramon Llull University Barcelona Spain

Suresh Chandra Satapathy Department of Computer Science and Engineering PVP Siddhartha Institute of Technology Vijayawada, Andhra Pradesh India Vikrant Bhateja Department of Electronics and Communication Engineering SRMGPC Lucknow, Uttar Pradesh India

K. V. N. SunithaBVRIT Hyderabad College of Engineering for WomenHyderabad, Andhra PradeshIndia

ISSN 1876-1100 ISSN 1876-1119 (electronic) Lecture Notes in Electrical Engineering ISBN 978-981-10-7328-1 ISBN 978-981-10-7329-8 (eBook) https://doi.org/10.1007/978-981-10-7329-8

Library of Congress Control Number: 2017960919

#### © Springer Nature Singapore Pte Ltd. 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

# Preface

This volume contains high-quality research papers presented at the third International Conference on Microelectronics, Electromagnetics and Telecommunications (ICMEET) held in Departments of Electronics and Communication Engineering of BVRIT Hyderabad College of Engineering for Women, Hyderabad, Telangana, India, during September 9-10, 2017. ICMEET aims to bring together academic scientists, researchers, and research scholars to discuss the recent developments and future trends in the fields of microelectronics, electromagnetics, and telecommunication. Previous editions of the conference were held in GITAM University (2015), Visakhapatnam, and Raghu Institute of Technology (2016), Visakhapatnam. ICMEET received a total of 325 submissions for LNEE series of the conference. Each paper was peer-reviewed by at least two members of the Program Committee. Finally, a total of 94 papers were accepted for publication in this proceeding. ICMEET was technically supported by IETE student forum and IE student chapter. Several special sessions were offered by eminent professors in many cutting-edge technologies. Several eminent researchers and academicians delivered talks addressing the participants in their respective field of proficiency. Topic on evolutionary optimized power control methodologies and mitigation of H<sub>2</sub>S from hydrothermal power plant has been discussed by Naeem M. S. Hannoon, Professor, Technology of University, Mara, Malaysia. A thorough discussion on MEMS and NEMS was made by Prof. Sanket Goel from BITS Pilani, Hyderabad campus.

We would like to express our appreciation to the members of the Program Committee for their support and cooperation in this publication. We are also thankful to the team from Springer for providing a meticulous service for timely production of this volume. Our heartfelt thanks to our Chairman Sri Vishnu Raju K. V. garu and other management members of Sri Vishnu Educational Society for extending wholehearted support to host this in their campus. Special thanks to all guests who have honored us by their presence on the inaugural day of the conference. Our thanks are due to all special session chairs, track managers, and reviewers for their excellent support. Last, but certainly not the least, our special thanks go to all the authors who submitted papers and all the attendees for their contributions and fruitful discussions that made this conference a great success.

Barcelona, Spain Vijayawada, India Lucknow, India Hyderabad, India September 2017 Jaume Anguera Suresh Chandra Satapathy Vikrant Bhateja K. V. N. Sunitha

# **Organizing Committee**

#### **Chief Patrons**

Sri K. V. Vishnu Raju, Chairman, Sri Vishnu Educational Society Sri Ravichandran Rajagopal, Vice-Chairman, Sri Vishnu Educational Society

#### Patrons

Dr. S. Ramakumar, Director, Sri Vishnu Educational SocietyDr. Srinivasan Sundarrajan, Director, Sri Vishnu Educational SocietyDr. K. V. N. Sunitha, Principal, BVRIT Hyderabad College of Engineering for Women

#### **Program Coordinator**

Dr. J. Naga Vishnu Vardhan, HOD-ECE, BVRIT Hyderabad College of Engineering for Women

#### **Special Session Chairs**

Dr. Sudheer Kumar Terlapu, Vishnu Group, Bhimavaram Dr. P. S. R. Chowdary, RIT, Vizag Dr. V. V. S. S. Sameer Chakravarthy, RIT, Vizag

#### Conveners

Dr. Seetaiah Kilaru, BVRIT Hyderabad College of Engineering for Women

#### **Co-Conveners**

Dr. Anwar Bhasha Pattan, BVRIT Hyderabad College of Engineering for Women Mrs. Praveena M., BVRIT Hyderabad College of Engineering for Women

#### **Proceedings Committee**

Dr. M. Parvathi, Professor, BVRIT Hyderabad College of Engineering for Women V. Hindumathi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

A. Radha, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

#### **Technical Program Committee**

S. Madhavi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

R. Shylaja, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

P. Prashanth, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

G. Siva Sankar Varma, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

## **Organizing Committee**

R. Priyakanth, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

K. Mahesh Babu, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

R. Sridevi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

G. Rama Lakshmi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

#### **Publicity Committee**

K. Suneela, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

K. Brunda Devi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women Mr. P. Raj Bhagath, Assistant Professor, Raghu Institute of Technology

#### **Finance Committee**

A. Radha, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

V. Hindumathi, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

Siva S. Sinthura, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

G. Drakshayani, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

#### **Hospitality Committee**

Y. Anil Kumar, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

N. M. Saikrishna, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

P. Rajesh Kumar, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

D. Venkata Siva Prasad, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

M. Venkatesh, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

#### **Transportation Committee**

Y. Anil Kumar, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

K. Mahesh Babu, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

N. M. Sai Krishna, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

G. Siva Sankar Varma, Assistant Professor, BVRIT Hyderabad College of Engineering for Women

#### International And National Advisory Committee

Prof. Jaume Anguera, Universitat Ramon Llull, Spain Dr. Ashwin Kumar, Carnegie Mellon University Dr. Vannet Agarwal, Purdue University Dr. Krishnaswami Hari Srihari, State University of New York Dr. Alison Carrington, Staffordshire University Dr. A. K. Raviteka, Drenden Institute of Technology, Germany Dr. Narasimhasarma N. V. S., NIT Warangal Dr. Adithya K. Jagannatham, IIT Kanpur Dr. Syed Nazeemuddin, IIT Hyderabad Dr. M. B. Srinivas, BITS Pilani, Hyderabad Dr. L. Pratap Reddy, JNTU Hyderabad Dr. M. Madhavi Latha, JNTU Hyderabad Dr. D. Srinivasa Rao, JNTU Hyderabad Dr. M. Asha Rani, JNTU Hyderabad Dr. B. N. Bhandari, JNTU Hyderabad Dr. T. Satya Savithri, JNTU Hyderabad Dr. B. Lakshmi, NIT Warangal Dr. P. Naveen Kumar, Osmania University D. Rama Krishna, Osmania University Dr. B. Rajendra Naik, Osmania University Dr. R. Hemalatha, Osmania University Dr. Sai Dhiraj Aruma, Samsung R&D Institute, Bangalore Dr. G. Sasibhushana Rao, Andhra University Dr. P. G. Krishna Mohan, JNTU Hyderabad (Retd) Dr. K. Padmapriya, JNTU Kakinada Dr. Zinka Sreenivasa Rao, BITS Pilani Dr. I. A. Pasha, BVRIT Narsapur, Hyderabad Dr. Amit Acharya, IIT Hyderabad Mrs. N. Mangala Gowri, JNTU Hyderabad

#### **Panel of Reviewers**

Prof. Vikranth Bhateja Prof. Suresh Chandra Satapathy Dr. Elsa Macias Lopez Dr. Abdul Ella Hassanien Prof. P. Mallikarjuna Rao Dr. Santoshi Ganala Prof. P. Satish Rama Chowdary

## Dr. V. V. S. S. Sameer Chakravarthy

- Dr. Ashish Singh

- Dr. Sudheer Kumar Terlapu Dr. T. Venkateswara Rao

| A DCT-CS Watermarking Method for Monochrome<br>and Color Image                                                                                       | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| D. Susmitha and S. M. Renuka Devi                                                                                                                    | 1  |

| Intelligent Counter System for Generating Attendance<br>N. Edna Elizabeth, T. K. Gowthaman, J. Joannes Sam Mertens<br>and P. Likhitta Dugar          | 11 |

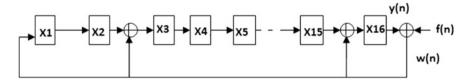

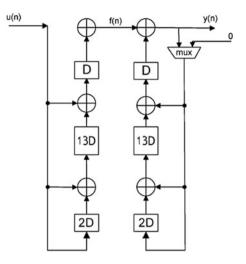

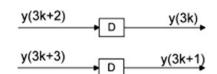

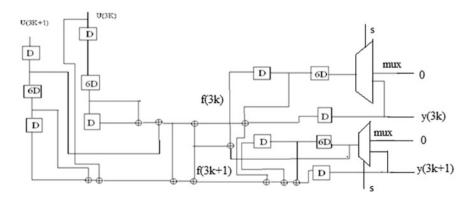

| High-Throughput VLSI Architectures for CRC-16 Computationin VLSI Signal ProcessingR. Ashok Chaitanya Varma and Y. V. Apparao                         | 23 |

| Etch Time Optimization in Bulk Silicon MEMS Devices Using a Novel         Compensation Structure         J. Grace Jency, M. Sekar and A. Ravi Sankar | 33 |

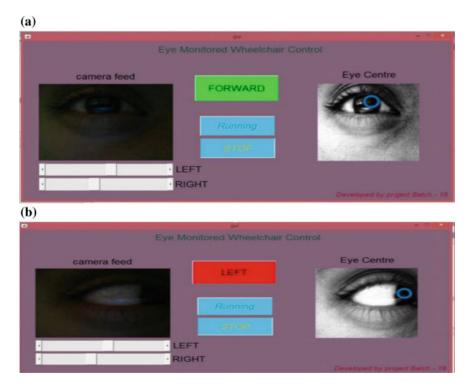

| Eye Monitoring Based Motion Controlled Wheelchair for<br>QuadriplegicsQuadriplegicsRaju Veerati, E. Suresh, Adithya Chakilam and Sai Priya Ravula    | 41 |

| <b>Design and Analysis of Spherical Inverted-F Antenna Cavity Model</b> Parisa Jwalitha and G. Sambasiva Rao                                         | 51 |

| Performance of Ternary Sequences Using Adaptive Filter                                                                                               | 63 |

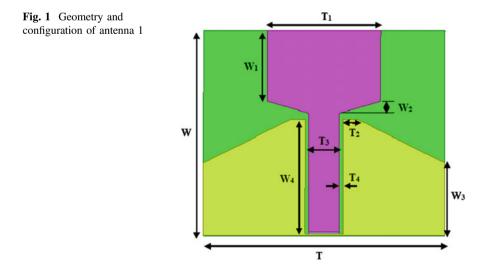

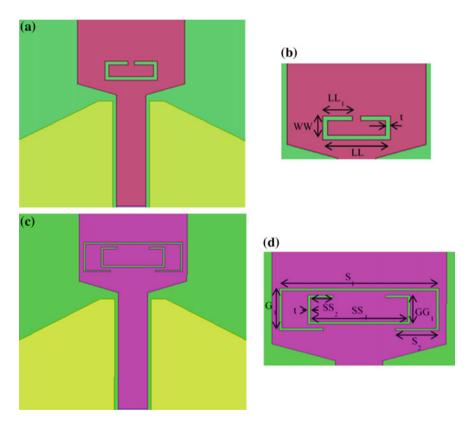

| Effects of Square- and Rectangular-Shaped Slots Kept Over the<br>Microstrip Antenna<br>Parsha Manivara Kumar, Nalam Ramesh Babu and Lam Ravi Chandra | 75 |

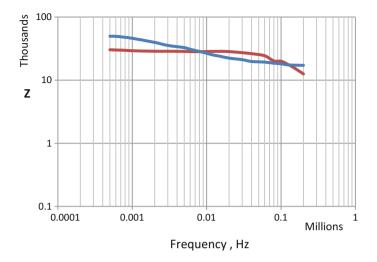

| Quality Monitoring of Water Through Electromagnetic Sensor<br>Sheetal Mapare and G. G. Sarate                                                        | 87 |

| Contents |

|----------|

| Contents |

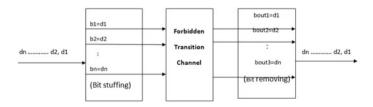

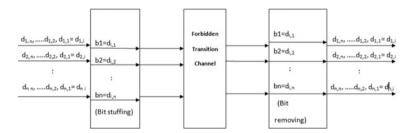

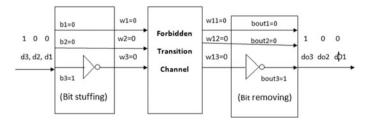

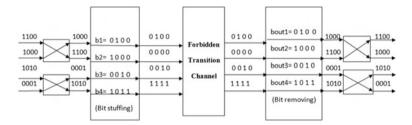

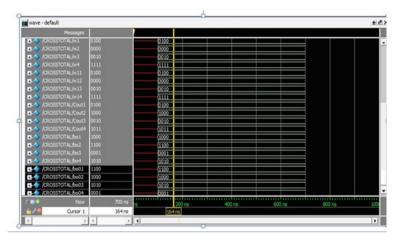

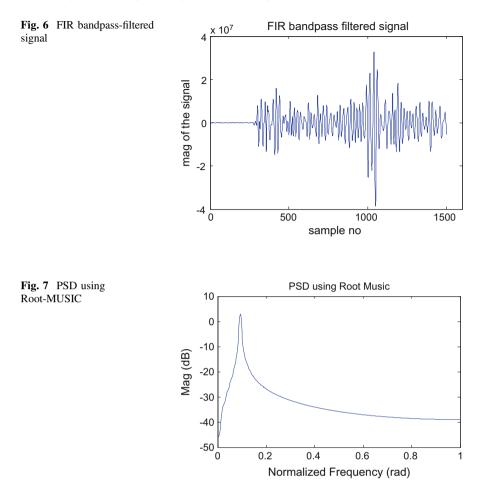

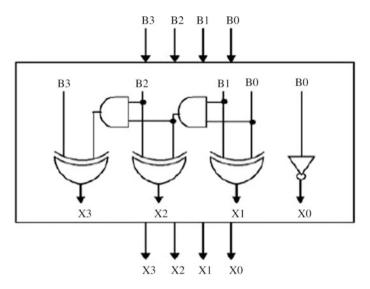

| Design and Implementation of Low-Power Memory-Less CrosstalkAvoidance Codes Using Bit-Stuffing AlgorithmsBattari Obulesu and P. Sudhakara Rao                                                               | 95  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

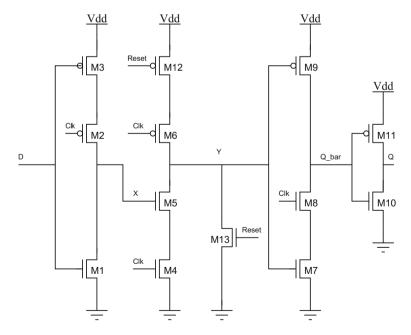

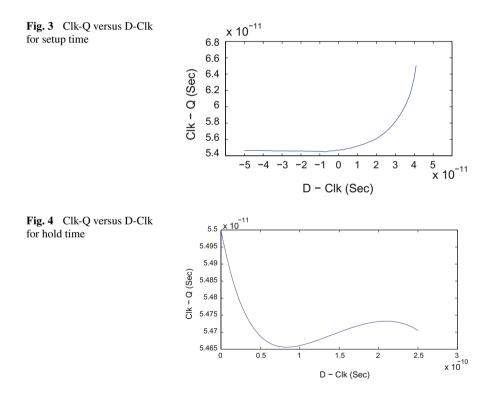

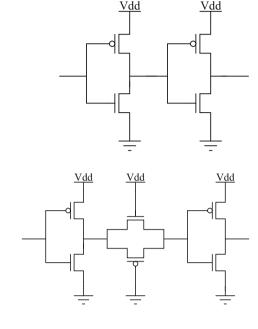

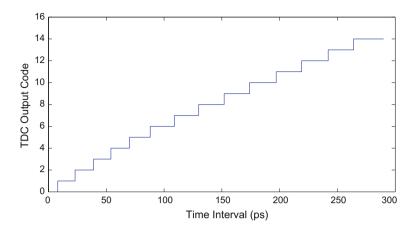

| <b>180-nm 20 ps Resolution 0.29 LSB Single-Shot Precision Vernier</b><br><b>Delay Line Based Time-to-Digital Converter</b><br>R. S. S. M. R. Krishna, Debashis Jana, Sanjukta Mandal<br>and Ashis Kumar Mal | 105 |

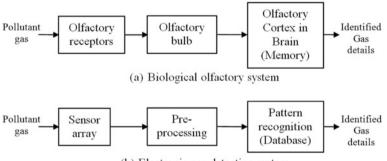

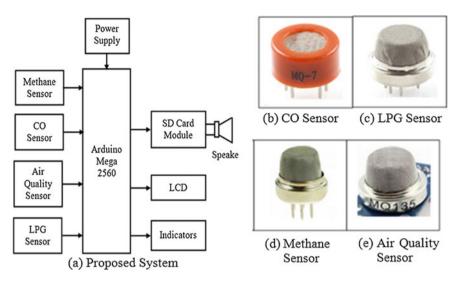

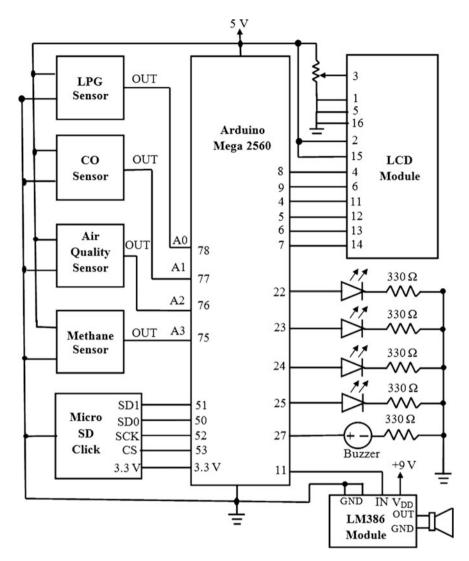

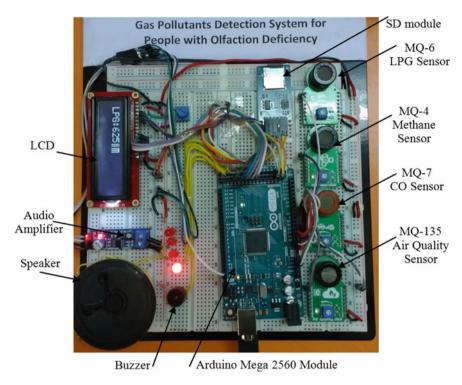

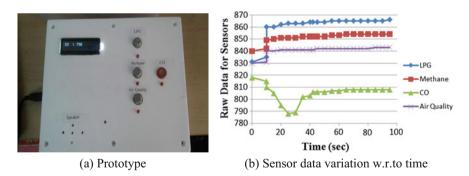

| Low-Cost Portable Gas Pollutants Detection System for People with<br>Olfactory Impairment<br>Pushpa Kotipalli, Jyothi Chinta and M. Mohan Varma                                                             | 117 |

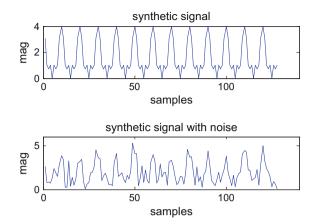

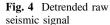

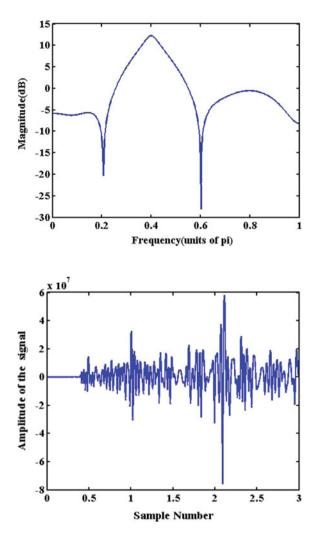

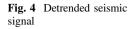

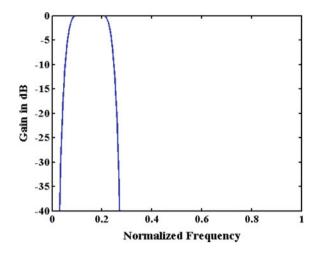

| Seismic Signal Processing by Using Root-MUSIC Algorithm<br>G. Pradeep Kamal, B. L. Prakash and S. Koteswara Rao                                                                                             | 127 |

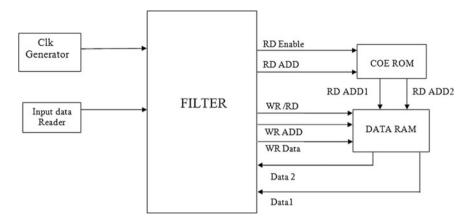

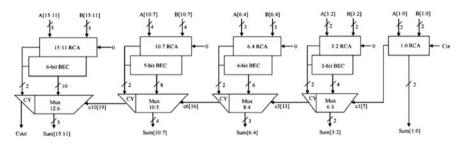

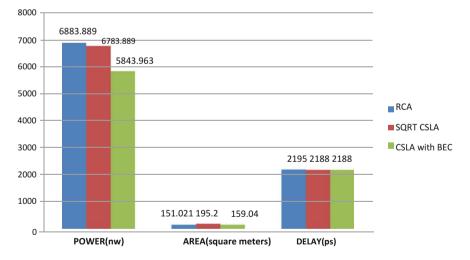

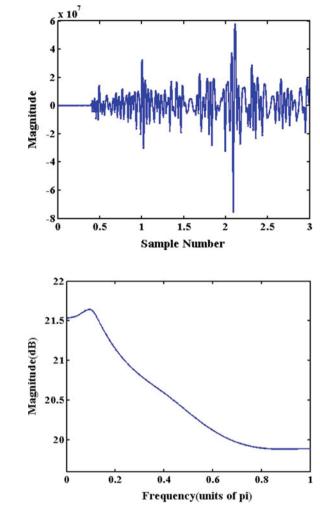

| Low-Power and Area-Efficient FIR Filter Implementation Using<br>CSLA with BEC<br>M. Sumalatha, P. V. Naganjaneyulu and K. Satya Prasad                                                                      | 137 |

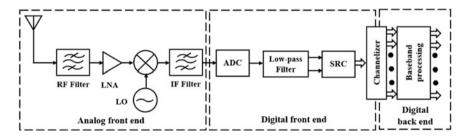

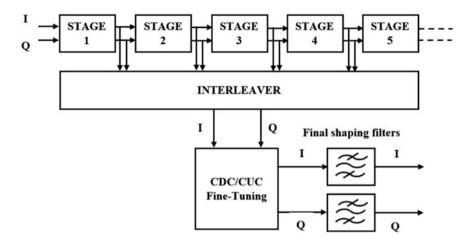

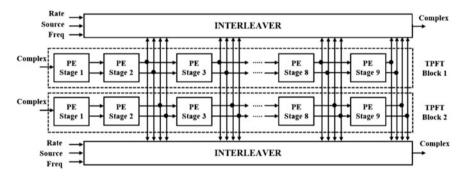

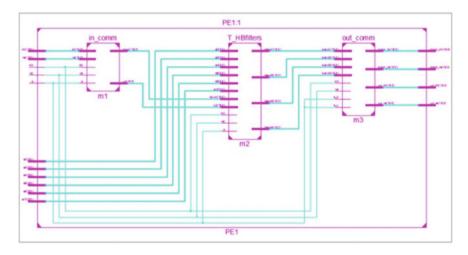

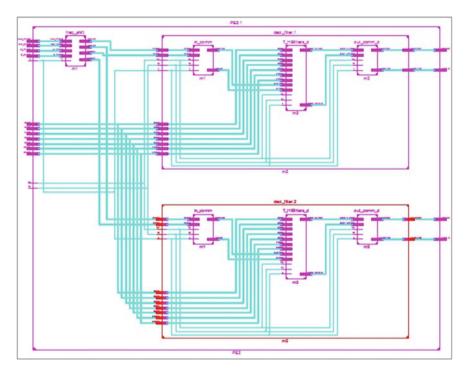

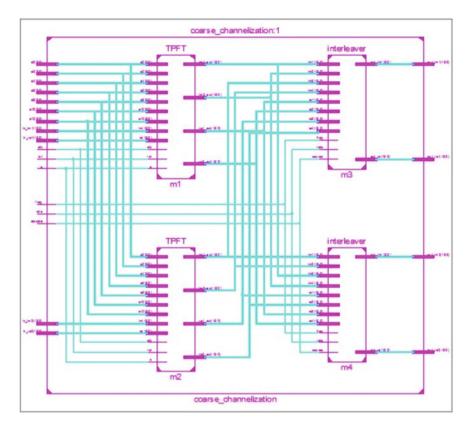

| Design and FPGA Implementation of TPFT-Based Channelization<br>for SDR Applications<br>P. Sri Lekha and K. Pushpa                                                                                           | 143 |

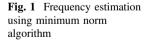

| Frequency Estimation Using Minimum Norm Algorithm<br>on Seismic Data<br>Ch. Namitha, V. Uma Mahesh, M. Anusha, S. Koteswara Rao<br>and T. Vaishnavi Chandra                                                 | 153 |

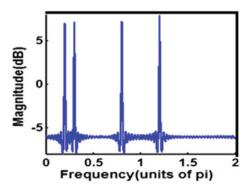

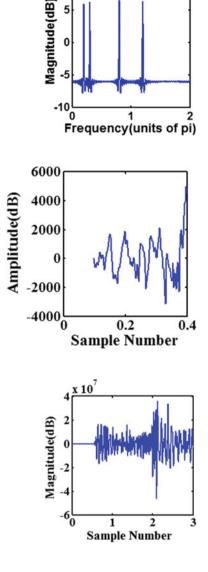

| <b>Processing of Seismic Signal Using Minimum Variance Algorithm</b><br>Md. Basha Saheb, U. Neeraj Kumar, S. Koteswara Rao<br>and V. Lakshmi Bharathi                                                       | 165 |

| IoT-Based Patient Health Monitoring System                                                                                                                                                                  | 177 |

| A Synoptic Review on Dielectric Resonator Antennas<br>G. Divya, K. Jagadeesh Babu and R. Madhu                                                                                                              | 185 |

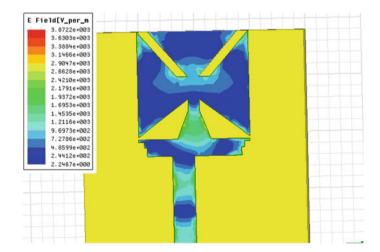

| DC Electric Field Analysis of Nomex, Kraft Paper, and PPLP<br>Insulation Arrangement in Liquid Nitrogen by Using<br>COMSOL Multiphysics<br>Vikram Singh and Shabana Urooj                                   | 197 |

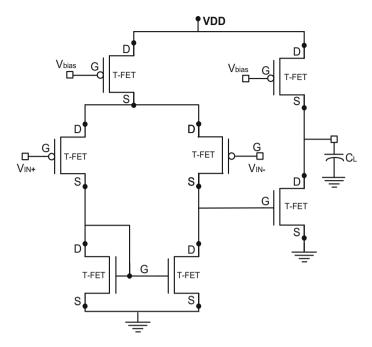

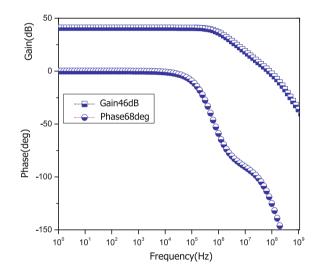

| Power and Area Efficient Opamp for Biomedical Applications Using 20 nm-TFET                                                                                                                                 | 207 |

| Bellamkonda Saidulu and Arun Manoharan                                                                                                                                                                      |     |

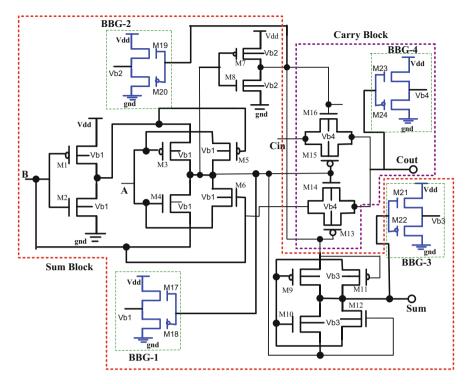

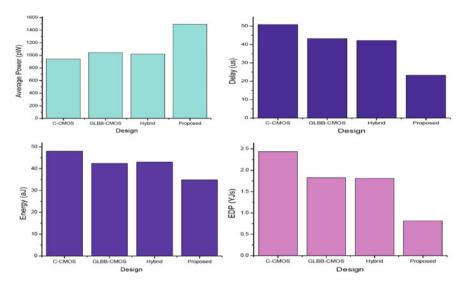

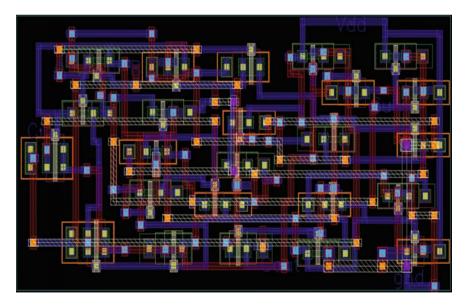

| <b>Design of Ultralow Voltage-Hybrid Full Adder Circuit Using</b><br><b>GLBB Scheme for Energy-Efficient Arithmetic Applications</b>                                                            | 217 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

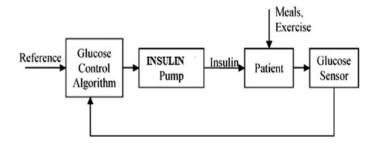

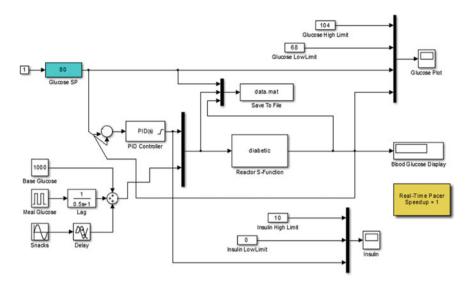

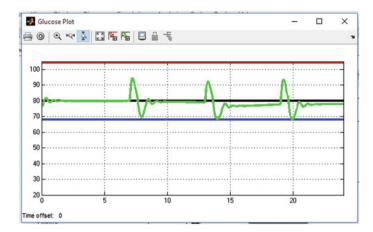

| Closed-Loop Blood Glucose Control for Type I Diabetes Patients<br>Using PID Controller<br>Bharat Singh, Shabana Urooj and Ravi Sharma                                                           | 225 |

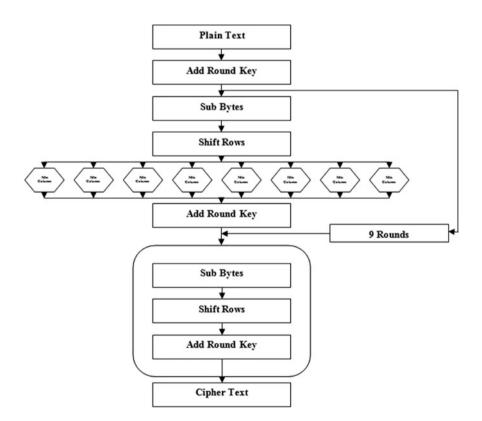

| FPGA-Based Implementation of AES Algorithm         Using MIX Column         S. Neelima and R. Brindha                                                                                           | 233 |

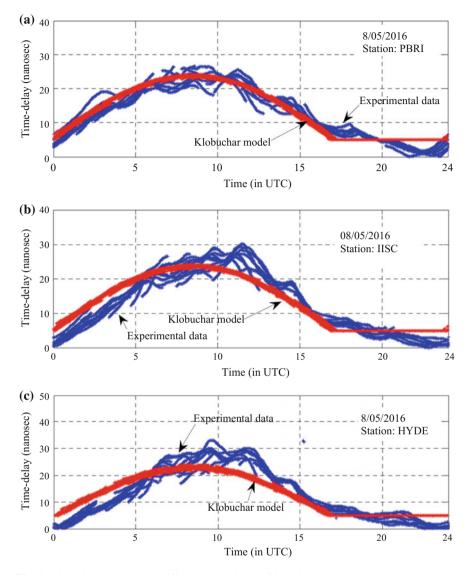

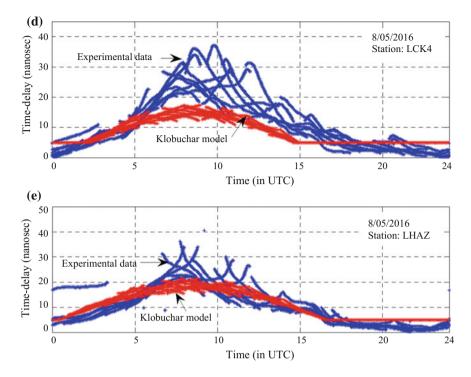

| Impact of High Geomagnetic Activity on Global Positioning SystemSatellite Signal (L-Band) Delay and Klobuchar AlgorithmPerformance Over Low Latitudinal RegionK. C. T. Swamy                    | 247 |

| Scalable Recursive Convolution Algorithm for the Development<br>of Parallel FIR Filter Architectures<br>Anitha Arumalla and Madhavi Latha Makkena                                               | 255 |

| <b>IoT-Based Green Environment for Smart Cities</b>                                                                                                                                             | 263 |

| Design of a Robust Estimator for Submarine Tracking<br>in Complex Environments<br>D. V. A. N. Ravi Kumar, S. Koteswara Rao and K. Padma Raju                                                    | 273 |

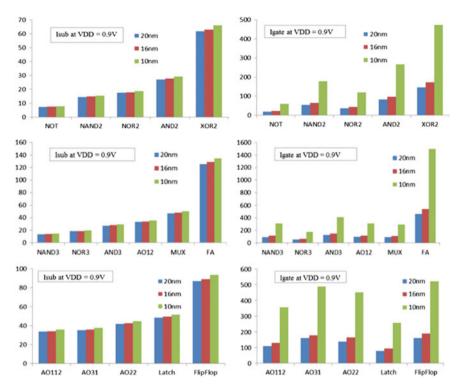

| Geometry Scaling Impact on Leakage Currents in FinFET Standard<br>Cells Based on a Logic-Level Leakage Estimation Technique<br>Zia Abbas, Andleeb Zahra, Mauro Olivieri and Antonio Mastrandrea | 283 |

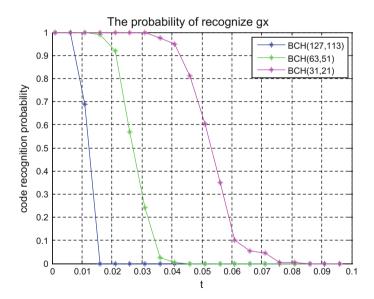

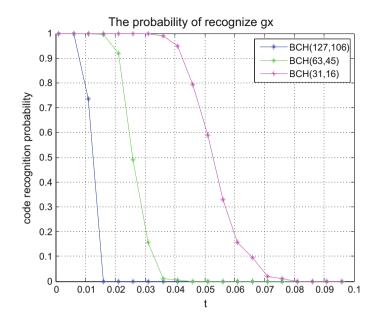

| Blind Recognition of Error-Correcting BCH Codes Using GFFT<br>A. Abhishek Nath and V. Navya                                                                                                     | 295 |

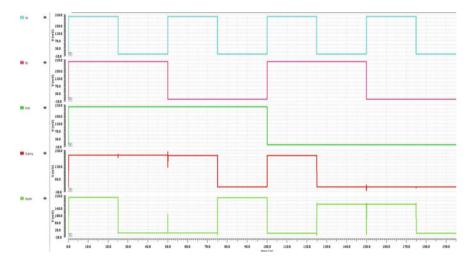

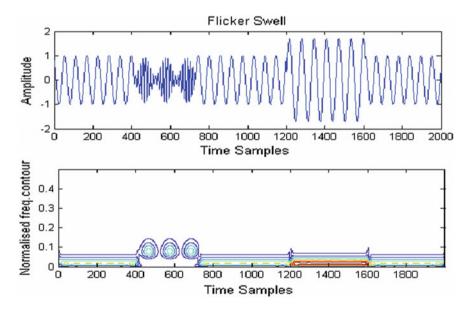

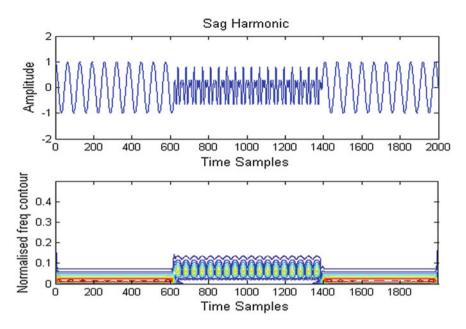

| Simultaneous Power Quality Disturbances Analysis Using Modified<br>S-Transform and Evolutionary Approach<br>G. Sahu and A. Choubey                                                              | 305 |

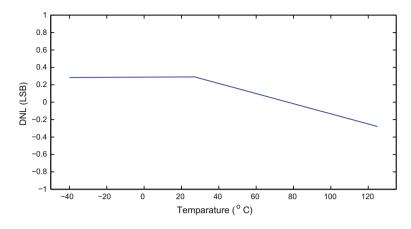

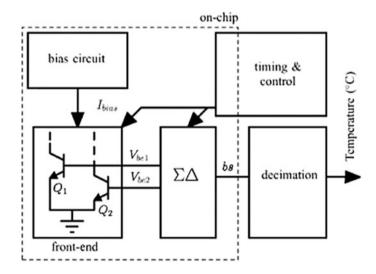

| Efficient Integration of Zoom ADC with Temperature Sensors for<br>System on Chip Applications—A Perspective                                                                                     | 315 |

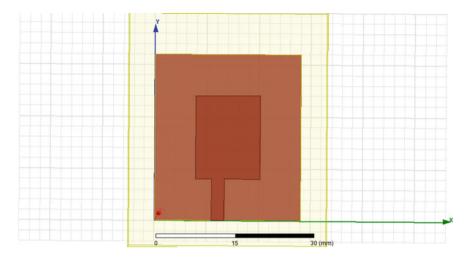

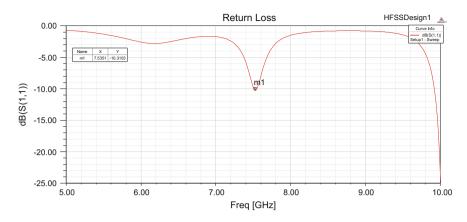

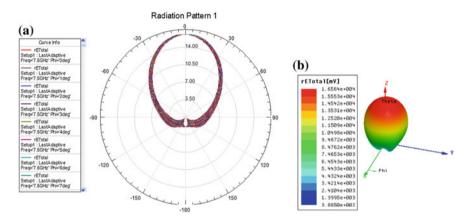

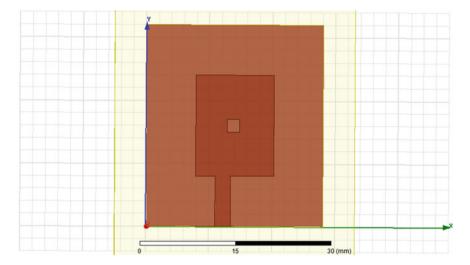

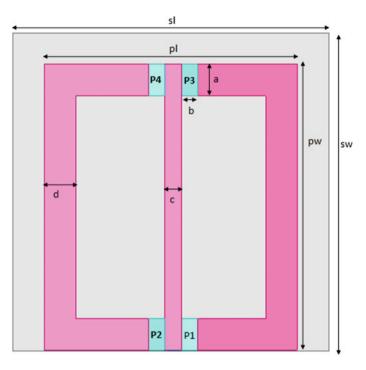

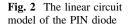

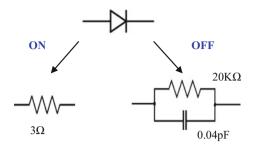

| A Compact Pattern Reconfigurable Antenna<br>for WiMAX Application<br>Devi Perla and Rajya Lakshmi Valluri                                                                                       | 325 |

| Low-Power Adiabatic Logic—Design and Implementation in<br>32-Nanometer Multigate Technology<br>Suresh Kumar Pittala and A. Jhansi Rani                                                                     | 335 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Design of Low-Power Binary Content Addressable Memoryfor Future NanotechnologiesG. Surekha, N. Balaji and Y. Padma Sai                                                                                     | 343 |

| Cross Talk Delay Reduction in System on Chip<br>R. Sridevi, P. Chandra Sekhar and B. K. Madhavi                                                                                                            | 349 |

| Design and Simulation of Boost Converter for Correction of PowerFactor and THD ReductionRenu Kadali and Srinivasa Rao Jalluri                                                                              | 361 |

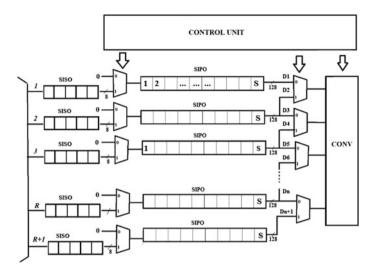

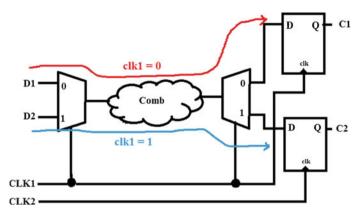

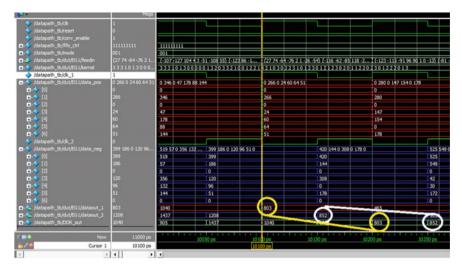

| Design and Simulation of High-Performance 2D         Convolution Architecture         V. S. Vishal and B. S. Kariyappa                                                                                     | 371 |

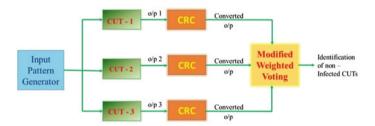

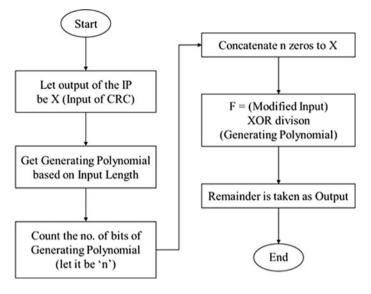

| CRC-Based Hardware Trojan Detection for Improved<br>Hardware Security<br>N. Mohankumar, M. Jayakumar and M. Nirmala Devi                                                                                   | 381 |

| A EHO-Based Clustering and Routing Technique for Lifetime<br>Enhancement of Wireless Sensor Networks<br>R. K. Krishna and B. Seetha Ramanjaneyulu                                                          | 391 |

| Joint Multiview Video Plus Depth Coding with Saliency Approach T. Manasa Veena, D. Satyanarayana and M. N. Giri Prasad                                                                                     | 401 |

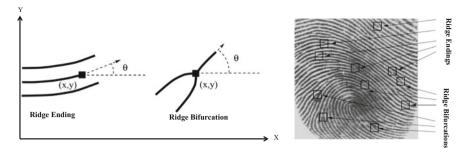

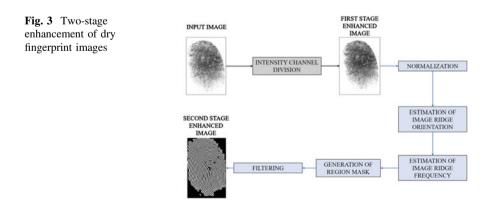

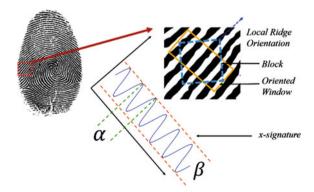

| Two-Stage Enhancement of Dry Fingerprint Images Using IntensityChannel Division and Estimation of Local Ridge Orientationand FrequencyRamagiri Priyakanth, Katta Mahesh Babu and Nyshadam Sai KrishnaKumar | 411 |

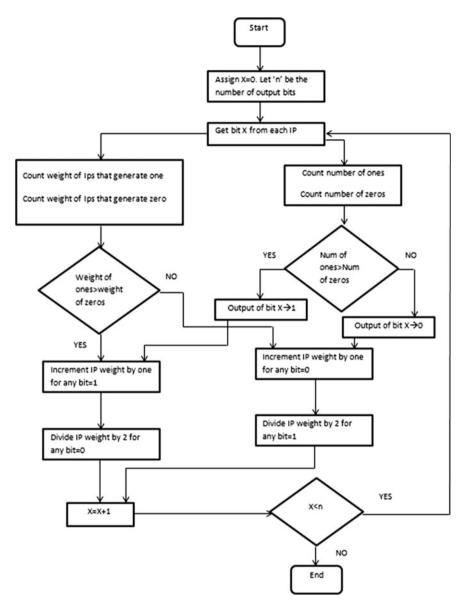

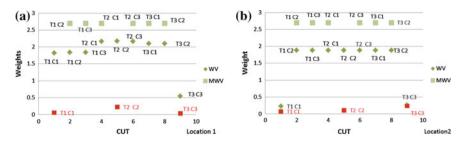

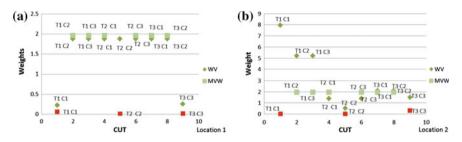

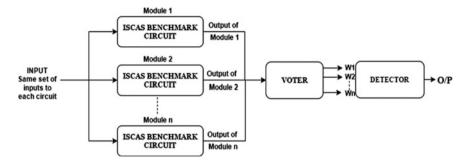

| Virtual Instrumentation-Based Malicious Circuit Detection Using<br>Weighted Average Voting<br>G. Aishwarya, Hitha Revalla, S. Shruthi, V. S. Pon Ananth<br>and N. Mohankumar                               | 423 |

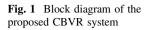

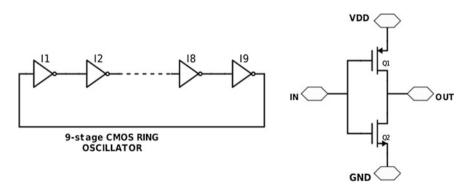

| High-Performance Video Retrieval Basedon Spatio-Temporal FeaturesG. S. N. Kumar, V. S. K. Reddy and S. Srinivas Kumar                                                                                      | 433 |

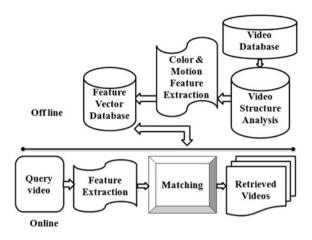

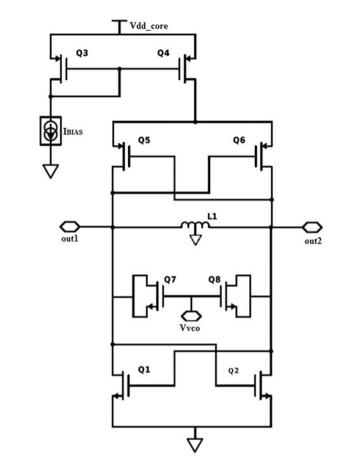

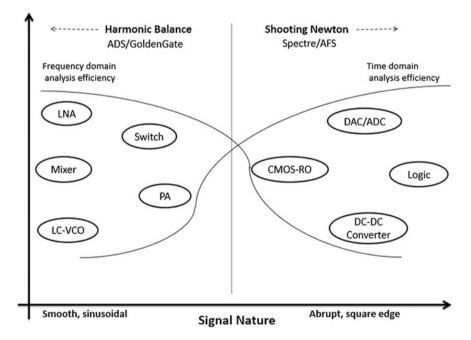

| Performance Comparison of Commercially Available RF Analog<br>and Mixed Signal Simulation Tools Using Benchmark Circuits<br>Vaibhav Ruparelia, Mayank Chakraverty, Sunita S. Desai<br>and P. S. Harisankar | 443 |

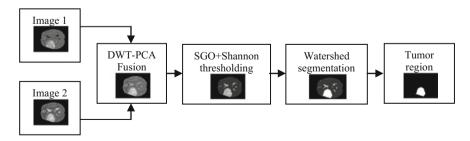

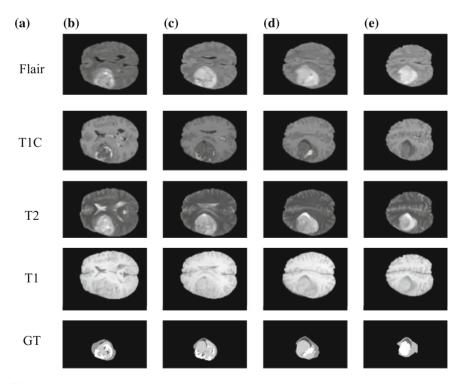

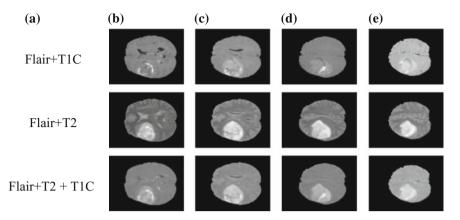

| <b>DWT-PCA Image Fusion Technique to Improve SegmentationAccuracy in Brain Tumor Analysis</b> V. Rajinikanth, Suresh Chandra Satapathy, Nilanjan Dey | 453      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| and R. Vijayarajan                                                                                                                                   |          |

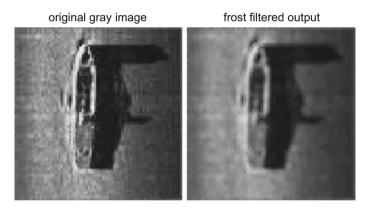

| Hybridization of PSO and Anisotropic Diffusion in Denoising                                                                                          | 160      |

| the Images                                                                                                                                           | 463      |

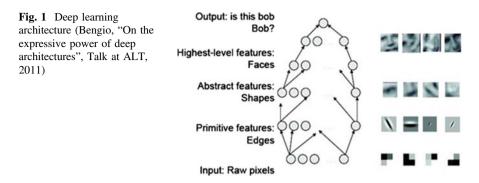

| Impact of Deep Learning in Image Processing                                                                                                          |          |

| and Computer Vision                                                                                                                                  | 475      |

| Study of Very Fast Front Surges in Gas Insulated Substation Due to                                                                                   | <b>.</b> |

| Switching Operation         Operation           V. HimaSaila, M. Nagajyothi and T. Nireekshana                                                       | 487      |

| <b>Fuzzy Logic Based Speech Recognition and Gender Classification</b><br>Sanjay Dubey, H. Ajay Kumar, R. Abhilash and M. C. Chinnaiah                | 495      |

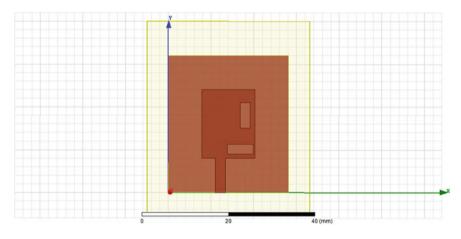

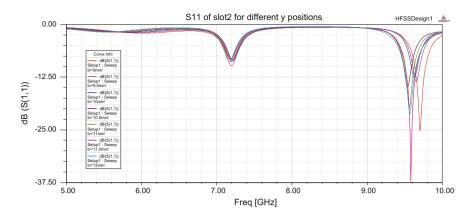

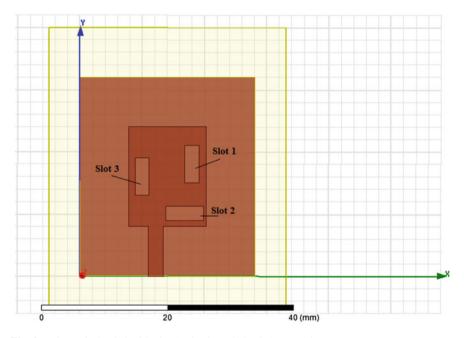

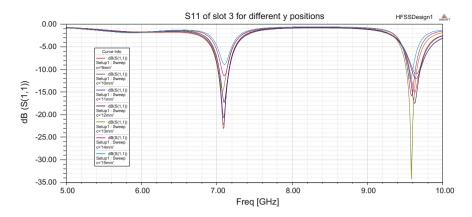

| Slot Positioning on Microstrip Antenna Using Parametric Analysis<br>Parsha Manivara Kumar, Dasari Kiran Kumar and Nalam Ramesh Babu                  | 505      |

| <b>Object Removal Using Median Filter in Wavelet Domain</b><br>Rajkumar L. Biradar                                                                   | 515      |

| An FPGA-Based Classical Implementation of Branch                                                                                                     |          |

| and Remove Algorithm                                                                                                                                 | 523      |

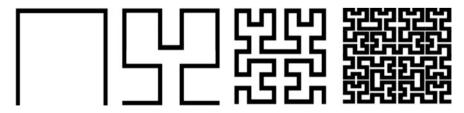

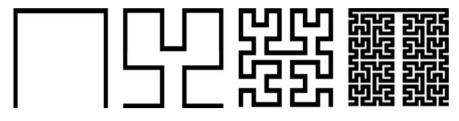

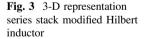

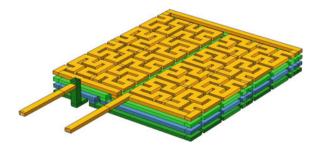

| A Novel Fractal Stacked Inductor Using Modified Hilbert Space<br>Filling Curve for RFICs<br>P. Akhendra Kumar and N. Bheema Rao                      | 535      |

| An Approach to Parallel Transformation Technique forHigh-Efficiency Video CodingP. Anitha, P. Sudhakara Reddy and M. N. GiriPrasad                   | 541      |

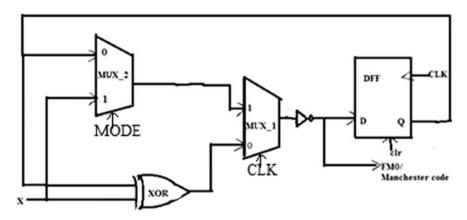

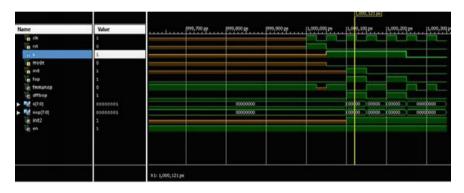

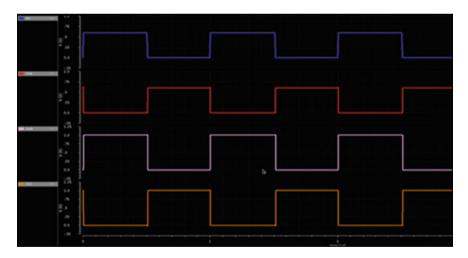

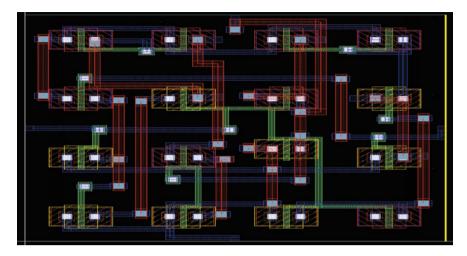

| On the Implementation of VLSI Architecture of FM0/Manchester<br>Encoding and Differential Manchester Coding<br>for Short-Range Communications        | 551      |

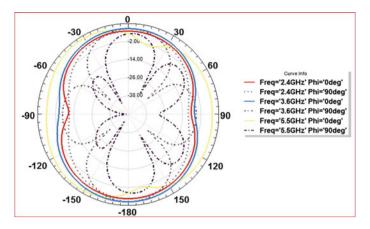

| Dual-Band-Notched CPW-Fed Antennas with WiMAX/WLAN                                                                                                   |          |

| <b>Rejection for UWB Communication</b>                                                                                                               | 559      |

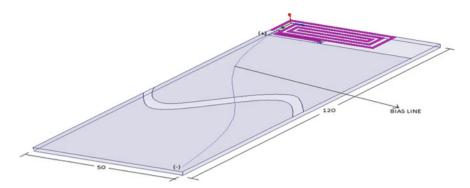

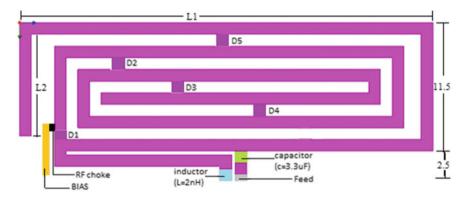

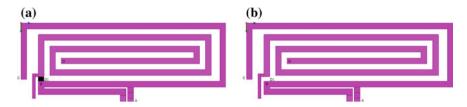

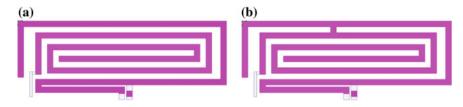

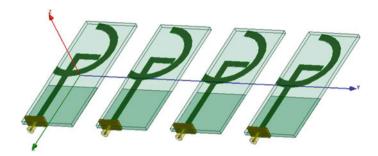

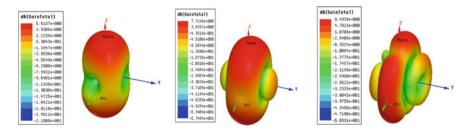

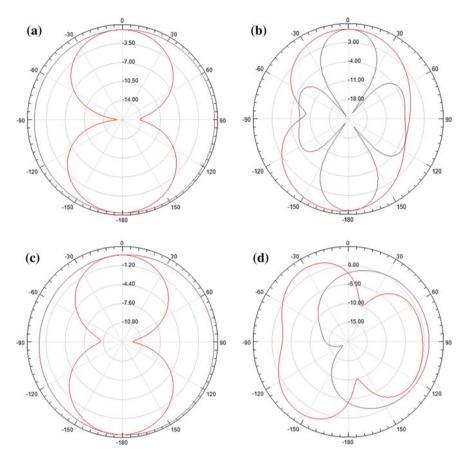

| A Frequency Reconfigurable Spiral F-Shaped Antenna for Multiple<br>Mobile Applications                                                                                                                          | 571 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Octagonal Shaped Frequency Reconfigurable Antenna for Wi-Fi<br>and Wi-MAX Applications<br>B. T. P. Madhav, M. Ajay Babu, P. Farhana Banu, G. Harsha Sai Teja,<br>P. Prashanth and K. L. Yamini                  | 581 |

| Cylindrical Structured Multiple-Input Multiple-Output Dielectric<br>Resonator Antenna<br>B. T. P. Madhav, M. Ajay Babu, P. V. S. Praneeth Kumar,<br>M. Venkateswara Rao and D. Padma Srikar                     | 589 |

| Multiband Semicircular Planar Monopole Antenna with SpiralArtificial Magnetic ConductorB. T. P. Madhav, T. V. Rama Krishna, K. Datta Sri Lekha, D. Bhavya,V. S. Dharma Teja, T. Mahender Reddy and T. Anilkumar | 599 |

| Implanted Antennas Inside the Human Body: Design, Simulations,and FabricationMedikonda Ashok Kumar, Sushanta K. Mandal and G. S. N. Raju                                                                        | 609 |

| Fusion of Wireless Sensor Images Using Improved Harmony SearchAlgorithm with Perturbation Strategy and Elite Opposition BasedLearningH. Rekha and P. Samundiswary                                               | 617 |

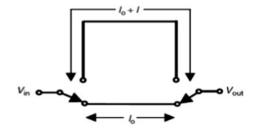

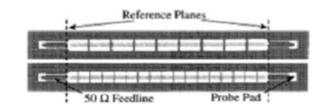

| A Review of Radio Frequency MEMS Phase Shifters                                                                                                                                                                 | 627 |

| Impact Analysis of Blackhole, Flooding, and Grayhole Attacksand Security Enhancements in Mobile Ad Hoc Networks Using SHA3AlgorithmP. Ramya and T. SairamVamsi                                                  | 639 |

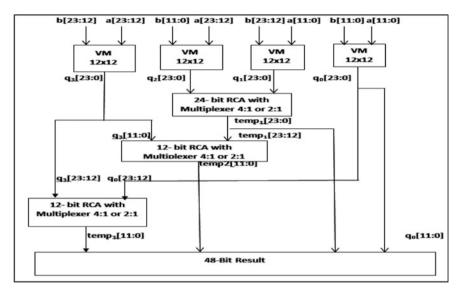

| Energy-Efficient and High-Speed Hybrid 1-Bit Full Adder                                                                                                                                                         | 649 |

| A Nonvolatile LUT Based on RRAM                                                                                                                                                                                 | 657 |

| Micro-strip Feed Reconfigurable Antenna for Wideband                                                                                                                                                            |     |

| Applications                                                                                                                                                                                                    | 665 |

| High Performance and Flexible Data Path Architecturefor DSP ApplicationsD. Naga Divya, M. V. Ganeswara Rao, Rajesh K. Panakalaand A. M. Prasad      | 673 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Ultralow Power 8T Subthreshold SRAM Cell<br>Devarapalli Mounika and Akondi Narayana Kiran                                                           | 683 |

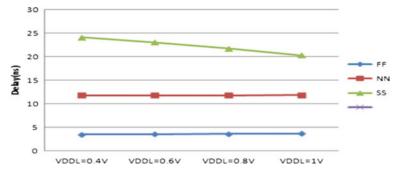

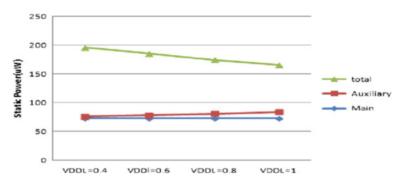

| <b>Double-Supply Voltage Level Shifter with an Auxiliary Circuit</b><br><b>for High-Speed Applications</b> Jalla Chinnari and Hanumantha Rao Sistla | 693 |

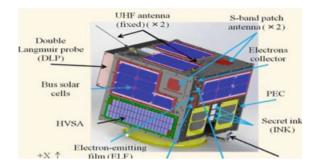

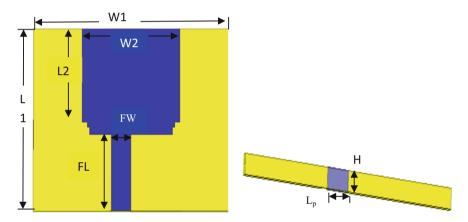

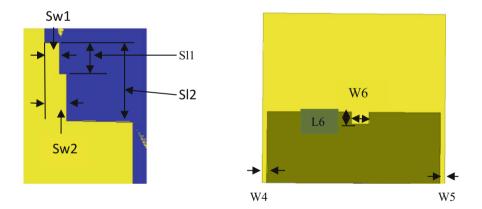

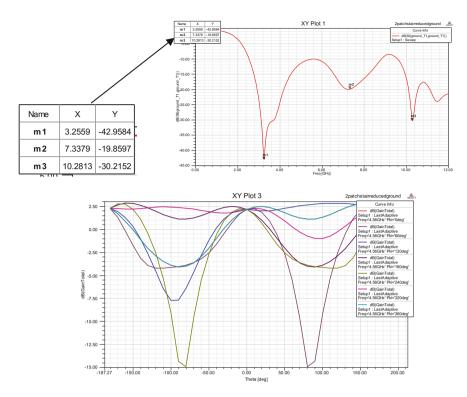

| Design and Analysis of Compatible Embedded Antenna         for Mini Satellites         M. Kishore Kumar and V. Pradyumna                            | 701 |

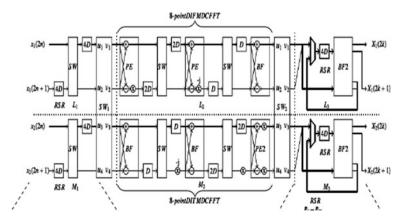

| Power Optimized FFT Architecture to Process Twin Data StreamsUsing Modified Booth EncodingM. Hemalatha and R. Ashok Chaitanya Varma                 | 711 |

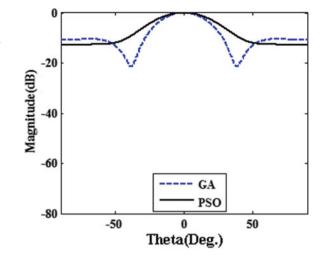

| Design of Thinned Rhombic Fractal Array Antenna Using GA<br>and PSO Optimization Techniques for Space and Advanced Wireless<br>Applications         | 719 |

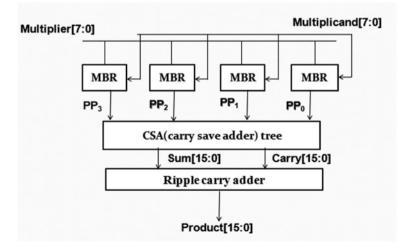

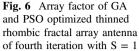

| <b>Design and Analysis of Single Precision Floating Point Multiplication</b><br><b>with Vedic Mathematics Using Different Techniques</b>            | 729 |

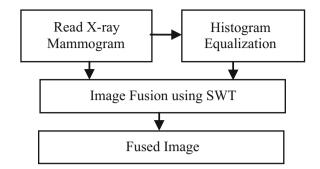

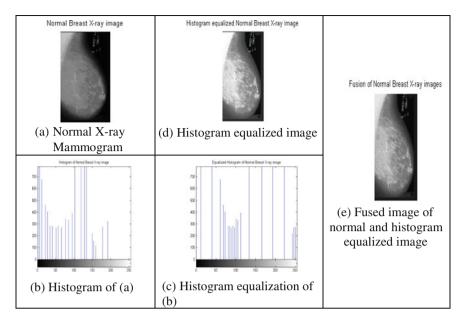

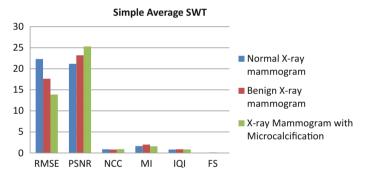

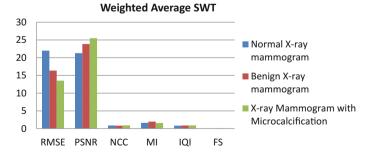

| Weighted Averaging SWT Technique for Enhanced Image Fusion         in X-ray Mammography         M. Prema Kumar, N. Sowjanya and P. Rajesh Kumar     | 739 |

| <b>The Reconfigurable Multi-ASIP Architecture for Turbo Decoding</b><br>A. L. Sruthi and P. Ravi Kumar                                              | 749 |

| Adaptive Beam Steering of Smart Linear Array Using LMSand RLS AlgorithmsBammidi Deepa and B. Roopa                                                  | 759 |

| A Level Cross-Based Nonuniform Sampling<br>for Mobile Applications<br>R. Viswanadham, T. Sudheer Kumar and M. Venkata Subbarao                      | 767 |

| SIW-Based Different Anchor-Shaped Slot Antennas<br>for 60 GHz Applications<br>M. Nanda Kumar and T. Shanmuganantham                                 | 779 |

| Microstrip Feed Dumbbell-Shaped Patch Antenna<br>for Multiband Applications<br>K. Yogaprasad and R. Anitha                                                                                                   | 789 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Arc-Shaped Monopole Liquid-Crystal Polymer Antenna<br>for Triple-Band Applications<br>S. S. Mohan Reddy, B. T. P. Madhav, B. Prudhvi nadh, K. Aruna Kumari,<br>M. V. S. Praveen, M. Hemachand and E. Mounika | 797 |

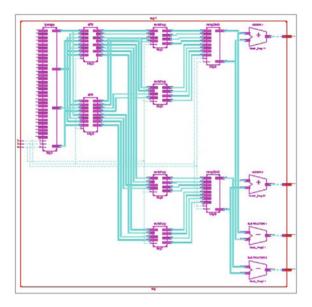

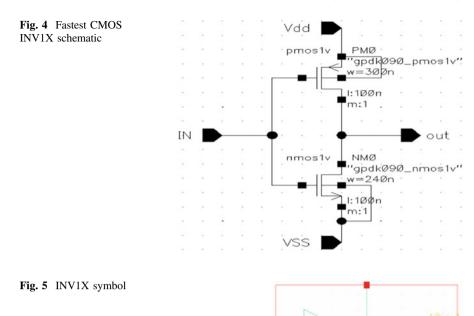

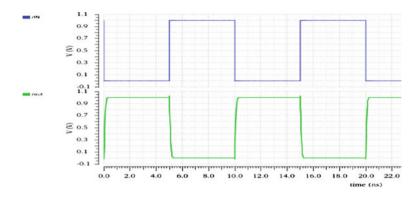

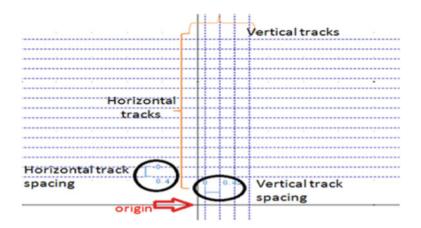

| Design and Characterization of an ASIC Standard Cell Library<br>Industry–Academia Chip Collaborative Project<br>M. Naga Lavanya and M. Pradeep                                                               | 807 |

| Design and Characterization of 6T SRAM Cell Industry-AcademiaCollaborative Chip Design ProjectHema Thota and G. R. L. V. N. Srinivasa Raju                                                                   | 817 |

| Spectrum Sensing in Cognitive Radio Networks Using<br>Time–Frequency Analysis and Modulation Recognition                                                                                                     | 827 |

| Synthesis of Linear Antenna Array Using Cuckoo Search and<br>Accelerated Particle Swarm Algorithms<br>M. Vamshi Krishna, G. S. N. Raju and S. Mishra                                                         | 839 |

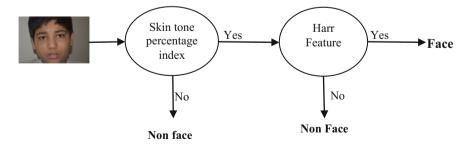

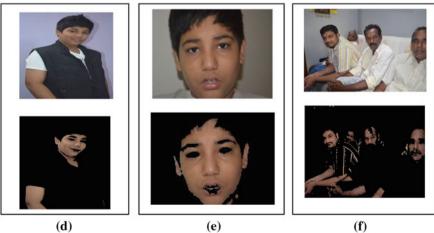

| A New VLSI Architecture for Skin Tone Detection<br>in an Uncontrolled Background<br>M. V. Ganeswara Rao, Rajesh K. Panakala and A. Mallikarjuna Prasad                                                       | 847 |

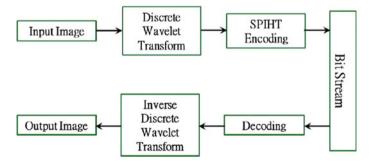

| Efficiently Secure Data Privacy on Hybrid Cloud Using Novel Image<br>Scrambling and Modified SPIHT<br>T. M. Praneeth Naidu and G. Spandana                                                                   | 855 |

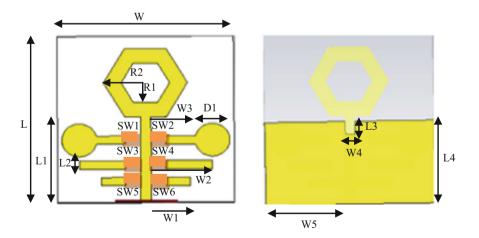

| Performance Analysis of Reconfigurable Antenna with Notch<br>Band Characteristics<br>Pavani Kollamudi                                                                                                        | 865 |

| Circular Array Synthesis Using Cuckoo Search Algorithm                                                                                                                                                       | 873 |

| Conformal Antennas—A Short Survey<br>N. V. K. Maha Lakshmi, P. V. Subbaiah and A. M. Prasad                                                                                                                  | 881 |

| Internet Security—A Brief Review                                                                                                                                                                             | 889 |

| Antenna Array Synthesis Using Social Group Optimization<br>V. V. S. S. Sameer Chakravarthy, P. S. R. Chowdary, Suresh<br>Chandra Satpathy, Sudheer Kumar Terlapu and Jaume Anguera                           | 895 |

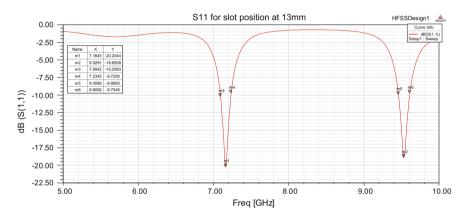

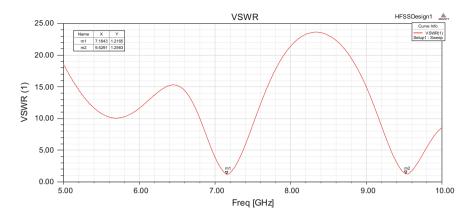

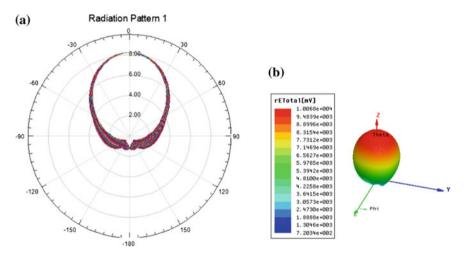

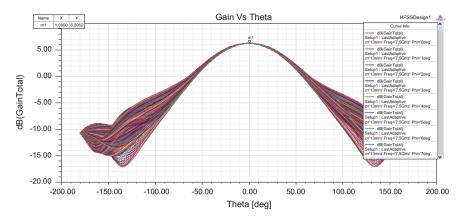

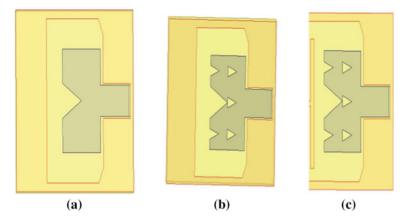

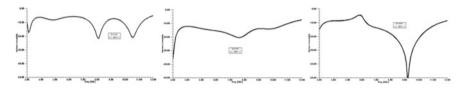

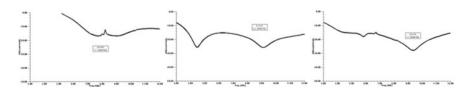

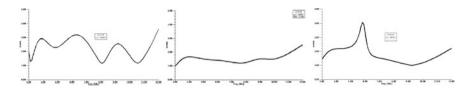

| On the Design of Fractal UWB Wide-Slot Antenna with Notch             |     |

|-----------------------------------------------------------------------|-----|

| Band Characteristics                                                  | 907 |

| Sudheer Kumar Terlapu, P. S. R. Chowdary, Ch Jaya, V. V. S. S. Sameer |     |

| Chakravarthy and Suresh Chandra Satpathy                              |     |

| Author Index                                                          | 913 |

# **About the Editors**

Dr. Jaume Anguera is a Professor in the Department of Electronics and Telecommunication, Universitat Ramon Llull. He is also an R&D Manager at Fractus, Barcelona, Spain. He is directing projects in the areas of multi-frequency and miniature monopoles; dual-frequency dual-polarized microcell antennas; monoband dual-polarized microstrip patch array; dual-band dual-polarized microstrip patch arrays; network feeding architectures for GSM-UMTS arrays; broadband matching networks: high cross-polarization techniques, array pattern synthesis with genetic algorithms, handset antennas, automotion antennas, and antennas for military applications among others. He obtained the degrees of Technical Engineer (Electronic Systems) and Electronic Engineer from Ramon Llull University, Barcelona, and degree of Telecommunication Engineer and Ph.D. (Doctor Ing.) from Polytechnic University of Catalunya (UPC), Barcelona. His research interests are miniature, wideband, multi-band, and high directivity printed antennas and arrays; fractal-shaped antennas genetic algorithms; handset antennas: internal and external multi-band antennas; base station antennas: multi-band cross-polarized antennas; low cross-polarization and high-isolation techniques for BTS antennas; automotive antennas: integration of antennas; short-range wireless and UWB antennas; and educational methods for electromagnetics. He has over 50 publications in journals and 100 papers in conference proceedings.

**Dr. Suresh Chandra Satapathy** is currently working as Professor and Head, Department of Computer Science and Engineering, PVP Siddhartha Institute of Technology, Andhra Pradesh, India. He obtained his Ph.D. in Computer Science and Engineering from JNTU Hyderabad and M.Tech. in CSE from NIT Rourkela, Odisha, India. He has 26 years of teaching experience. His research interests are data mining, machine intelligence, and swarm intelligence. He has acted as program chair of many international conferences and edited six volumes of proceedings from Springer LNCS and AISC series. He is currently guiding eight Ph.D. scholars. He is also a senior member of IEEE.

Prof. Vikrant Bhateja is Associate Professor, Department of Electronics and Communication Engineering, Shri Ramswaroop Memorial Group of Professional Colleges (SRMGPC), Lucknow, and also the Head (Academics & Quality Control) in the same college. His areas of research include digital image and video processing, computer vision, medical imaging, machine learning, pattern analysis and recognition, neural networks, soft computing, and bio-inspired computing techniques. He has over 90 quality publications in various international journals and conference proceedings. He has been on TPC and chaired various sessions from the above domain in international conferences of IEEE and Springer. He has been the track chair and served in the core-technical/editorial teams for international conferences: FICTA 2014, CSI 2014, and INDIA 2015 under Springer-ASIC Series and INDIACom-2015, ICACCI-2015 under IEEE. He is Associate Editor in International Journal of Convergence Computing (IJConvC) and also serving in the editorial board of International Journal of Image Mining (IJIM) under Inderscience Publishers. At present, he is a guest editor for two special issues floated in International Journal of Rough Sets and Data Analysis (IJRSDA) and International Journal of System Dynamics Applications (IJSDA) under IGI Global Publications.

Dr. K. V. N. Sunitha completed her B.Tech. ECE from Nagarjuna University, M.Tech. Computer Science from REC Warangal. She was awarded Ph.D. from JNTU, Hyderabad, in 2006. She has 24 years of teaching experience. She has been working as Founder Principal, BVRIT Hyderabad College of Engineering for Women, Nizampet, Hyderabad, since August 2012. She received "Academic Excellence Award" by G. Naravanamma Institute of Technology & Science on September 18, 2005, "Best Computer Science Engineering Teacher Award for the year 2007" by Indian Society for Technical Education (ISTE) on February 23, 2008, "Best Faculty" award in Academic Brilliance Awards-2013 by Indian Education Expo on April 2013 at New Delhi, "Distinguished Scientist Award in NLP" by Venus International on December 3, 2016, "Distinguished Principal Award" by CSI Mumbai on January 15, 2017 at IIT Bombay. She has been recognized and invited by AICTE as NBA Expert Evaluator. Her autobiography was included in "Marquis Who's Who in the World," 28th edition, 2011. She has authored four textbooks published by NOVA publishers, USA. Her areas of research include natural language processing, speech processing, network and Web security. She has guided six Ph.D. students and currently guiding eight research scholars. She received a research grant from CSI for her R&D project in March 2011 for 1 year and also received 38.5 lakhs of funding for DST-TIDE project. She has published over 125 papers in international and national journals and conferences. She is a reviewer for many national and international journals. She is a fellow of Institute of Engineers, senior member for IEEE & International Association CSIT, and life member of many technical associations like CSI and ACM.

# A DCT-CS Watermarking Method for Monochrome and Color Image

D. Susmitha and S. M. Renuka Devi

**Abstract** In order to overcome the threat of data transmission over Internet, watermarking techniques have been developed. Watermarking can be implemented in spatial or in frequency domain. In this paper, watermarking is implemented in frequency domain using DCT transform and compressive sensing technique. The paper deals with a proposed watermarking scheme that can be applied to binary, monochrome, and color image. Here, the features of compressive sampling are considered in order to overcome the drawback of insecure data transmission. A random Gaussian matrix is used as the secret key for encrypting the watermark in the process of compressive sensing. This encrypted watermark is then embedded into the mid-frequency DCT coefficients of the host image. Experimental results depict that the performance of our algorithm is better than basic DCT watermarking in terms of robustness. It is observed that the security level and embedding capacity are also improved by the usage of compressive sampling.

Keywords Discrete cosine transform • Watermarking • Compressive sampling

#### 1 Introduction

In the current years, the growth of technology has increased vastly in the concern of transfer of information over Internet. As Internet is an open source, the security of the digital media is put under risk. This threat can be faced by providing some authentication information along with the data. Embedding of authentication information into the digital media is referred as watermarking. Watermarking can be applied to video, audio, images, and other digital media also. Research in this

G. Narayanamma Institute of Technology and Science (for women), Hyderabad, India e-mail: susmitha.daparty18@gmail.com

S. M. Renuka Devi e-mail: renuka.devi.sm@gmail.com

D. Susmitha (🖂) · S. M. Renuka Devi

<sup>©</sup> Springer Nature Singapore Pte Ltd. 2018

J. Anguera et al. (eds.), Microelectronics, Electromagnetics

and Telecommunications, Lecture Notes in Electrical Engineering 471, https://doi.org/10.1007/978-981-10-7329-8\_1

area had been developed enormous from the past decade onward [1-3]. The resulting image after embedding the ownership or signature information is the watermarked image. Properties of HVS (human visual system) are used for embedding the data into the cover image imperceptibly.

Many authors [4–7] have discussed the watermarking performance evaluation by testing the algorithm's robustness against various attacks, embedding capacity and transparency, i.e., visual degradation of host and extracted watermark image. It is required to keep a trade-off between all these parameters.

Some of the authors [8–10] have already used watermarking based on compressive sampling and DCT. The main contribution of our work is in using compressive sampling and discrete cosine transform for providing better security by using a measurement matrix in compressive sampling and a full reference image watermarking scheme is used. Also, this paper explores the use of DCT-CS method for color images, which is the first of its kind.

This paper is organized as follows: Sect. 2 is about basics of compressive sampling and orthogonal matching pursuit algorithm; Sect. 3 discusses the proposed method of watermarking technique; and Sect. 4 concludes with the results by comparing the proposed method with basic DCT watermarking technique.

#### 2 Compressive Sampling

Bandwidth is of major concern when transmitting information over channel and so the data needs to be compressed as per the Shannon–Nyquist sampling theorem before transmitting [11, 12]. In order to satisfy this theorem, it requires acquiring large number of samples (i.e., double the maximum frequency of input signal), which is expensive in applications like radar and medical imaging [11]. Compressive sampling deals with this problem by acquiring the signal directly in the compressed domain. This is possible by representing the signal in an appropriate basis [11, 12]. For example, consider a 1-D signal X (of finite length N) that can be expressed in an appropriate basis  $\Psi$  using

$$X = \sum_{i=1}^{N} S_i \Psi_i \text{ or } X = \Psi S, \tag{1}$$

where S is the N  $\times$  1 column vector. X is similar to S except that their domain representation is different. If the number of samples in S that is nonzero, far less than the total number of samples, then S is said to be sparse representation of X, i.e., X is sparse in  $\Psi$  domain. Now, the signal X is in compressed form.

But recovering the signal X at the receiver, without having any knowledge about the location of nonzero coefficients is computationally complex problem [12]. This is overcome by computing M(M < N) inner products between X and  $\phi_j$  where j = 1 to M as  $y_j = \langle x, \phi_j \rangle$ .

A DCT-CS Watermarking Method for Monochrome and Color Image

$$\mathbf{Y} = \mathbf{\phi}\mathbf{X} = \mathbf{\phi}\Psi\mathbf{S} = \mathbf{\Theta}\mathbf{S} \tag{2}$$

$$\Theta = \phi \Psi \tag{3}$$

$\Theta$  is an M  $\times$  N matrix.  $\Theta$  can also be referred as dimensionally reduced space of signal X. The signal can be recovered from this dimensionally reduced matrix by using the recovery algorithms like OMP, l<sub>1</sub>-minimization [11, 13]. In our context, OMP is used since its performance is better as compared to l<sub>1</sub>-minimization and also OMP is a generalized algorithm and suits all kinds of applications [14].

#### 2.1 OMP (Orthogonal Matching Pursuit)

The OMP algorithm is an iterative process [14]. It makes use of the orthogonal projections of measurement matrix Y onto the random Gaussian matrix A. The algorithm for implementing the OMP is given below.

- 1. Initially, measurements  $Y_{M \times 1}$  and the measurement matrix  $A_{M \times N} = [a_1, a_2, ..., a_N] \in \mathbb{R}^M$  are given, where M is the number of measurements and N is the number of samples.

- 2. Calculate the angles  $\Theta_i$  for i = 1 to N, by orthogonally projecting Y onto the atoms,  $a_i$ ,  $\Theta_i$  = angle (Y,  $a_i$ ).

- 3. Find the inner product,  $\lambda_i$ , between Y and  $a_i$  and preserve the maximum value. This will be the first nonzero coefficient.

- 4. Calculate the index  $I_1$  = argmin ( $\Theta$ i), for i = 1 to N.

- 5. Calculate the residue  $Y1 = Y \lambda_{I_1} a_{I_1}$ .

- 6. Now calculate the inner product between residue Y1 and atoms of A (exclude the  $I_1$ th atom as it is already perpendicular) and preserve the maximum value to be the second nonzero coefficient.

- 7. Repeat the procedure until the residue value tends to be less than a predefined threshold (this is the stopping criteria).

#### **3** Proposed Method

#### 3.1 Watermark Embedding

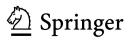

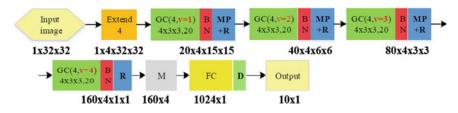

Figure 1 illustrates the watermarking scheme used. The cover image is taken to be a color image. Since modifying the three channels (R, G, B) is not recommendable,

Fig. 1 a Watermark embedding b Watermark extraction

usually blue channel [4] is used for embedding the watermark. So, select the blue channel and apply 2-D DCT. For a monochrome watermark, apply compressive sampling principles. This can be done by generating a measurement matrix and calculating the measurement vector. These measurements are embedded into the mid-frequencies of B channel. The mid-frequencies are used, since in DCT the low frequencies carry most of the visual information and especially the DC component should not be disturbed; otherwise, this results in degradation of the cover image. The high-frequency components are more susceptible to noise and compression attacks. The measurement matrix acts as key1 and the equation used for embedding given below acts as key2:

$$\mathbf{I} = \mathbf{I} + \mathbf{g}^* \mathbf{W},\tag{4}$$

where I' is the watermarked image, g is the watermarking strength (0 < g < 1) [7], and W is the watermark measurement vector. Watermarked image is produced by applying inverse DCT. In case of color cover image, combine the channels after applying inverse DCT to blue channel, for obtaining watermarked image.

#### 3.2 Watermark Extraction

Extraction of watermark can be achieved only when the key is shared with the authorized party. Watermark can be extracted by applying DCT to the watermarked image and using the following formula:

$$W = (I' - I)/g$$

(5)

Now, the measurement vector is obtained, from which watermark can be produced by using the compressive sampling reconstruction algorithm OMP. Recovery is successful only when the same random matrix (key1) is used. In case of using a color cover image, it is recommended to separate the three channels initially and then extract the watermark.

#### 4 Performance Measures and Results

Transform-domain watermarking provides less embedding capacity compared to the spatial-domain watermarking. For example, the DCT watermarking system offers less than half of the middle frequencies to be suitable for embedding without visual degradation [2]. This algorithm is carried out on  $256 \times 256$  host color image and watermark of sizes  $64 \times 64$  and  $32 \times 32$ . The extracted watermark quality is evaluated in terms of PSNR, SSIM, RMSE, and normalized correlation [2].

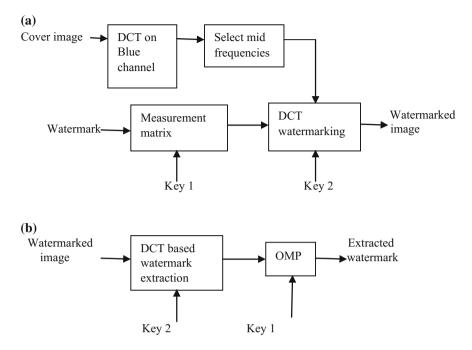

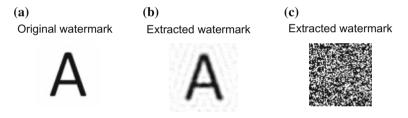

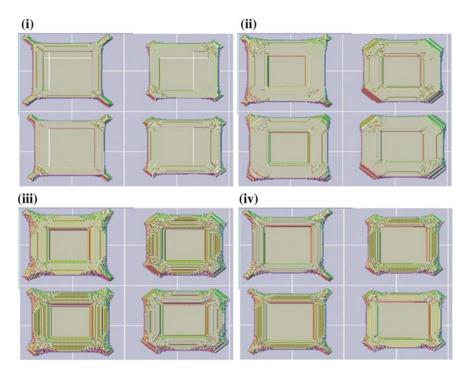

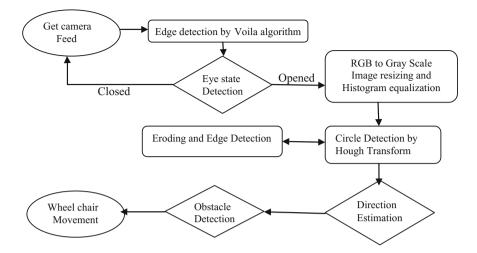

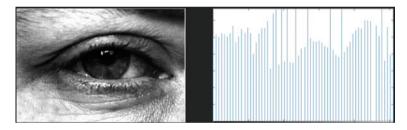

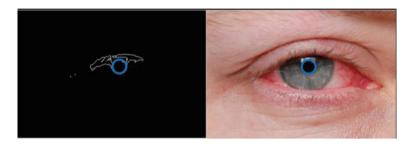

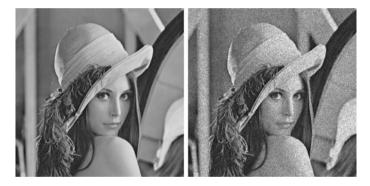

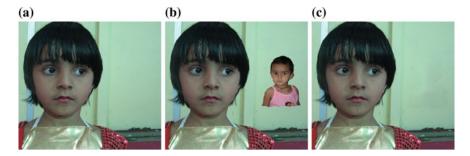

Figure 2 shows the results of the proposed system. Watermarks of size  $32 \times 32$  and  $64 \times 64$  are used for embedding the host image of size  $256 \times 256$ . Table 1 presents the performance evaluation of watermarked image for basic DCT method [5] and proposed DCT-CS method. Table 2 gives the quality measure of a  $64 \times 64$  watermark considering one-third of total samples and half number of measurements.

Fig. 2 a 64  $\times$  64 watermark; b Watermarked image of size 256  $\times$  256; c Extracted watermark using DCT-CS method, obtained NC = 0.9652

| Watermark                | PSNR (dB)          | SSIM         |                    |              | RMSE               |              | NC                 |              |

|--------------------------|--------------------|--------------|--------------------|--------------|--------------------|--------------|--------------------|--------------|

| size (Text<br>watermark) | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT |

| 32 × 32                  | 51.2432            | 38.4746      | 0.9955             | 0.9731       | 0.0333             | 0.0917       | 0.9999             | 0.9988       |

| 64 × 64                  | 39.6751            | 34.3594      | 0.9430             | 0.9619       | 0.1220             | 0.1208       | 0.9991             | 0.9969       |

Table 1

Quality measure of watermarked image in DCT-CS watermarking method in comparison with the basic DCT [5]

Table 2 Quality measure of extracted watermark for DCT-CS watermarking method in comparison with basic DCT [5]

| Watermark  | PSNR (dB) |         | SSIM     |        | RMSE     |        | NC       |        |

|------------|-----------|---------|----------|--------|----------|--------|----------|--------|

| size (Text | Proposed  | Basic   | Proposed | Basic  | Proposed | Basic  | Proposed | Basic  |

| watermark) | DCT-CS    | DCT     | DCT-CS   | DCT    | DCT-CS   | DCT    | DCT-CS   | DCT    |

| 64 × 64    | 19.2819   | 11.5241 | 0.7675   | 0.2949 | 0.1178   | 0.2862 | 0.9652   | 0.8543 |

| 32 × 32    | 23.2600   | 16.9982 | 0.5613   | 0.7805 | 0.0741   | 0.1533 | 0.9866   | 0.9403 |

It can be observed from Tables 1 and 2 that the performance of our system is far better than the traditional approach of watermarking in DCT domain in terms of PSNR, SSIM, RMSE, and NC for both watermarked image and extracted watermark.

Robustness of the watermark is evaluated by subjecting the watermarked image to attacks like salt and pepper noise, Gaussian filtering, additive white Gaussian noise (AWGN) and measuring the PSNR, SSIM, RMSE, and NC of the extracted watermark. Table 3 summarizes the robustness of extracted watermark ( $64 \times 64$ ) under the presence of various attacks. The results are compared against the basic DCT system.

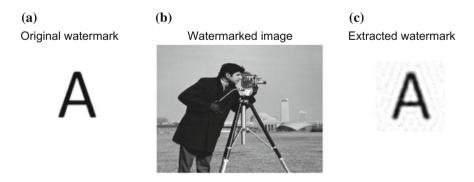

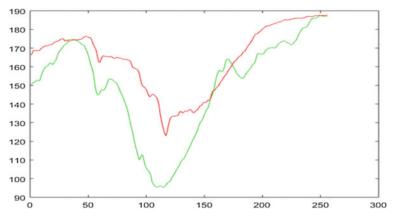

Figure 3 displays the effect of Gaussian noise on extracted watermark. It can be observed from the plot that the NC of the watermark extracted is at least 80% only when the SNR of the watermarked image (after the channel attacks) is greater than 35 dB.

| Type of attack                 | PSNR (dB)          |              | SSIM               |              | RMSE               |              | NC                 |              |

|--------------------------------|--------------------|--------------|--------------------|--------------|--------------------|--------------|--------------------|--------------|

|                                | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT | Proposed<br>DCT-CS | Basic<br>DCT |

| Salt and pepper (0.025)        | 8.6410             | 3.156        | 0.2002             | 0.022        | 0.3989             | 0.750        | 0.6698             | 0.36         |

| Gaussian filter $(5 \times 5)$ | 23.0097            | 2.603        | 0.5532             | 0.040        | 0.0763             | 0.799        | 0.9862             | 0.47         |

| AWGN<br>(SNR = 35 dB)          | 11.0732            | 2.588        | 0.2430             | 0.041        | 0.3015             | 0.800        | 0.8070             | 0.47         |

Table 3

Robustness evaluation of extracted watermark in proposed DCT-CS system compared with basic DCT system [5]

Fig. 3 Performance of extracted watermark with Gaussian noise attack on channel

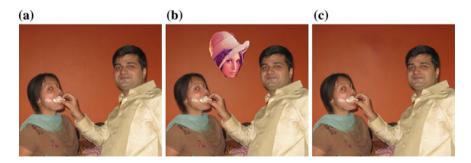

Fig. 4 a Embedded watermark of size  $64 \times 64$ ; b Extracted watermark by using right key, obtained NC = 0.9652; c Extracted watermark by using wrong key, obtained NC = 0.0003

The degree of resistance of this system to intruders depends on watermarking key (key2) used for selecting the embedding location and the measurement matrix (key1) used for implementing compressing sensing. Figure 4 illustrates the importance of the keys in extracting the watermark.

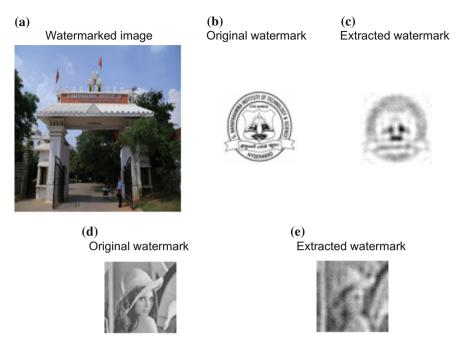

Our method of DCT-CS is also suitable for color images, by embedding the watermark in one of the channels (R, G, B). The performance analysis by using a cover color image is similar to that of grayscale image since the same watermarking method is used except that the watermark is embedded in the blue channel. Figure 5 shows the performance of our algorithm for color image.

**Fig. 5 a** Watermarked image of size  $256 \times 256$ ; **b** Embedded logo watermark of size  $64 \times 64$ ; **c** Extracted logo watermark, obtained NC = 0.7166; **d** Embedded Lena watermark of size  $64 \times 64$ ; **e** Extracted Lena watermark, obtained NC = 0.7874

#### 5 Conclusion

DCT-CS watermarking scheme proposed in this paper can be applied to binary, monochrome, and color images. This paper deals with the full reference watermarking where the original cover image is required for extracting the watermark. In this DCT-CS system with full reference watermarking, initially the watermark is compressively sensed and is embedded into the mid-band coefficients of DCT of the cover image. For improving the security and robustness, compressive sampling is considered. Since the compressive sampling reduces the total number of samples required for reconstruction of a signal, it therefore enhances the embedding capacity. In future, our algorithm can be stretched to other digital media like video and audio signals.

#### References

1. Smita Pandey, Rohit Gupta, "A Comparative Analysis on Digital Watermarking with Techniques and Attacks", International Journal of Advanced Research in Computer Science and Software Engineering, Volume 6, Issue 6, June 2016.

- Neetha K.K and Aneesh M. Koya, "A Compressive sensing approach to DCT watermarking system", International Conference on Control, Communication and Computing India (ICCC), IEEE conference publications, November 2015, pp. 495–500.

- 3. Potdar, V., S. Han and E. Chang, "A Survey of Digital Image Watermarking Techniques", in Proceedings of the IEEE International Conference on Industrial Informatics, Perth, Australia, 2005, pp. 709–716.

- 4. Verma, Bhupendra, et al., "A New color image watermarking scheme", INFOCOMP, Journal of computer science, Volume 5, Issue 3, 2006, pp. 37–42.

- 5. Barni, Mauro, et al. "A DCT-domain system for robust image watermarking", Signal processing, Volume 66, Issue 3, 1998, pp. 357–372.

- J.J.K. O'Ruanaidh, F.M. Boland, W.J. Dowling, "Phase watermarking of digital images", Proceedings IEEE International. Conference on Image Processing (ICIP'96), Vol. III, Lausanne, Switzerland, 16–19 September 1996, pp. 239–242.

- M.D. Swanson, B. Zhu, A.H. Tewfik, "Transparent robust image watermarking", Proceedings IEEE International Conference on Image Processing (ICIP'96), Vol. III, Lausanne, Switzerland, 16–19 September 1996, pp. 211–214.

- P. K. Korrai and K. Deergha Rao, "Compressive Sensing and Wavelets Based Image Watermarking and Compression", TENCON 2014 - 2014 IEEE Region 10 Conference, IEEE Conference Publications, 2014, pp. 1–5.

- 9. Zhang, Xinpeng, et al. "Watermarking with flexible self-recovery quality based on compressive sensing and compositive reconstruction", IEEE Transactions on Information Forensics and Security, Volume 6, Issue 4, 2011, pp. 1223–1232.

- Hsiang-Cheh Huang and Feng-Cheng Chang, "Robust Image Watermarking Based on Compressed Sensing Techniques," Journal of Information Hiding and Multimedia Signal Processing, Volume 5, Issue 2, April 2014, pp. 275–285.

- 11. Justin Romberg, "Imaging via compressive sampling," IEEE signal processing magazine, March 2008, pp. 14–20.

- 12. Richard G. Baraniuk, "Compressive sensing", IEEE signal processing magazine, July 2007, pp. 118–121.

- V. Pavithra and S. M. Renuka Devi, "An image representation scheme by hybrid compressive sensing", 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (Prime Asia), Visakhapatnam, 2013, pp. 114–119.

- 14. Tropp, Joel A., and Anna C. Gilbert, "Signal recovery from random measurements via orthogonal matching pursuit", IEEE Transactions on information theory, Volume 53, Issue 12, 2007, pp. 4655–4666.

# **Intelligent Counter System for Generating Attendance**

N. Edna Elizabeth, T. K. Gowthaman, J. Joannes Sam Mertens and P. Likhitta Dugar

**Abstract** In the present time, in most educational institutes, proxy is witnessed as one of the most inexcusable violences of the rules and regulations. It is also often observed that the attendance in all the educational institutes is taken manually by the faculty in charge to avoid proxy, but ends up in reducing the productive time available in the classroom. The solution to the above-faced difficulties is to bring about an automated system to mark the student's presence in each hour. Thus, the aim of this project is to bring a two-factor authentication system for generating the attendance by integrating the radio frequency identity cards along with biometrics. The result shows the prototype of the system designed with security. Also, wireless communication through radio waves between the transmitter and the receiver is carried out in this work.

**Keywords** Two-factor authentication • Biometrics • Proxy avoidance Automated system

- Electronics and Communication Department, Sri Sivasubramaniya Nadar College of Engineering, Old Mahabalipuram Road, Kalavakkam 603110, Tamil Nadu, India e-mail: ednaelizabethn@ssn.edu.in

- J. Joannes Sam Mertens e-mail: sam.mertens0007@gmail.com

- T. K. Gowthaman · P. Likhitta Dugar (☉)

Sri Sivasubramaniya Nadar College of Engineering,

Old Mahabalipuram Road, Kalavakkam 603110, Tamil Nadu, India e-mail: likhitta@dugar.in

T. K. Gowthaman e-mail: gowthaman13029@ece.ssn.edu.in

© Springer Nature Singapore Pte Ltd. 2018 J. Anguera et al. (eds.), *Microelectronics, Electromagnetics and Telecommunications*, Lecture Notes in Electrical Engineering 471, https://doi.org/10.1007/978-981-10-7329-8\_2

N. Edna Elizabeth · J. Joannes Sam Mertens

#### 1 Introduction

The current scheme used for marking the attendance in the classroom is very time consuming and not entirely secure in terms of avoiding proxy. Hence, the idea to develop a handy terminal was implemented. The incapability of manipulating the biometric human characteristics was a major concern while implementing the project. It is used by assigning the fingerprint to their individual details, like name and unique register number in their passive Radio Frequency Identification (RFID) tags. The successful matching of both the authenticated factors helps in enlisting and creating a database for each time the attendance is generated.

This system is carried out by the integration of a fingerprint scanner along with an RFID reader and a Liquid Crystal Diode (LCD) screen. The LCD screen is used to display the acknowledgment and to avoid any mismatch of data. With the help of an Arduino UNO 3 using the transceiver, Serial Peripheral Interface (SPI) communication is the methodology used to communicate with the student terminal to the faculty terminal and vice versa. The faculty terminal is a complete integration of the transceiver with the database storage device as an individual module. As a device for local storage, a computer/laptop present in each classroom is used. The present local storage device is only accessible by the faculty in charge, of that particular hour. On the confirmation of the database observed on the Graphical User Interface (GUI), it is transferred to the faculty's Simple Storage Device (SSD) for anytime access. Our major concern is to access any particular hour's attendance by the faculty, within the premises, in case of any discrepancies. The faculty is the sole controller.

There are already available attendances marking systems but lack in some way or the other when taken into account the proxy or possible violations. The readily available systems are either wall mount or designed on only one-factor authentication.

When taken in the case of the wall mount biometric systems, there is a possibility of intentional time waste in doing the same. On the other hand, while analyzing the case of the available one-factor authentication system, i.e., RFID or biometric factor, there is no evidence of proxy or other malpractices.

In present time, at the end of each attendance slot allotted by the universities, it becomes a tedious job for faculties to create the database and get it reviewed by each and every student to avoid discrepancies, which lead us in creating this automated counter system.

#### 2 Related Works

The article [1] has proposed a design using the emerging technology for identification (not proper format). Biometric refers to automatic identification of a person based on biological characters such as fingerprint, iris, facial recognition, etc. In this article, the main heart of the circuit is fingerprint module. This sends commands to the controller whenever fingerprint is matched.

Anif Jamaluddin et al. [2] have proposed a design for the improvement of assessment model using RFID technology which is implemented on Computer Based Test (CBT). But this system still needs human as a proctor for monitoring server.

G. V. Ambadkar and A. R. Karwankar [3] described the implementation techniques of RFID, integrated with biometric sensor to improve the security system. In this system, it uses both the techniques for registering proper attendance of student. No one can give proxy. It operates when the students swipe their RFID tag and also access the biometric, so that the attendance gets marked and the class door gets opened for the day. The limitation in the above paper is that the attendance was marked only at one instance in the whole day. This leads to high percentage of the students' attendance, for every subject even if the particular student was absent on particular class hours on several days.

Kong Shengli et al. [4] have explained the basic concept of the connection of RC522 reader to the Arduino platform for the acquisition of RFID card information. They have also given the optimum frequency of working as 13.5 MHz. They state that the usage of RC522 reader is for low power consumption, low cost, and low voltage requirements.

#### **3** Proposed System Overview

#### 3.1 Introduction

The system consists of a transmitter module and a receiver module. The microcontroller is common to all modules and it performs logical operations. The transmitter is placed on the students' desk, while the receiver is connected to the faculty accessible laptops. For communication between the transmitter and receiver, Serial Peripheral Communication (SPI) is used. This can be adapted easily by the windows operating software which is analyzed to be a common platform of operation in the present times. SPI communication was chosen as there are a common clock and other general signals. This type of communication is preferred as they communicate from one to many devices by just proving single and separate "chip enable" pin layouts for each device that is being connected and used.

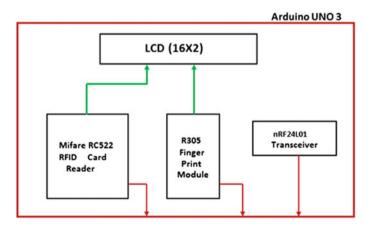

#### 3.2 Transmitter

The transmitter module consists of the Arduino UNO 3, fingerprint sensor module, the RFID reader, a  $16 \times 2$  LCD screen, and the nRF24L01 transceiver. A communication link is established between the transmitter and the receiver, when the transmitter module receives the initializing signal transmitted from the module present in the faculty side.

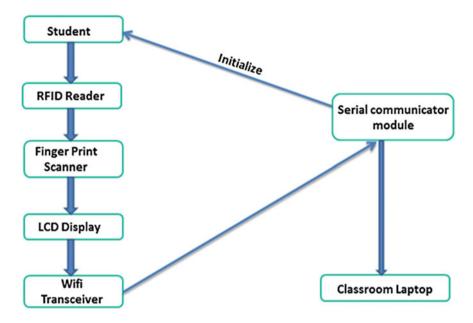

Figure 1 describes the transmission module which contains the fingerprint sensor, Arduino, RFID reader, LCD, and transceiver. Once the initial signal is received, the Arduino supplies power to the LCD screen and the RFID reader. The LCD screen first displays, stating that the module is ready to accept and receive data. The students are asked to swipe the passive tags that are distributed individually consisting of unique RFID numbers.

Initially, a database is created in the faculty accessible laptop, when the students are simultaneously made to enroll one of their fingers as password along with the tag swipe, for the two factors of authentication. In the case of mismatching of the fingerprint and the RFID retrieved details, the error messages are displayed on the LCD screen. This ensures a high-level security in the attendance system.

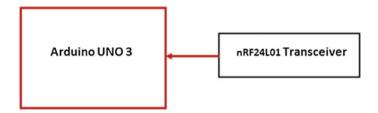

#### 3.3 Receiver

The message signals from the various transmitters present are received by the module that is present at the receiver end. This module is an integrated system of the Arduino UNO 3 with the transceiver.

Figure 2 describes the receiver module which contains an Arduino and a transceiver. This module is also used as the initialization system. When this receiver

Fig. 1 Transmission module

Fig. 2 Receiver module

module is powered on by the faculty, through the method of SPI communication, it is observed that the receiver module sends the initial enabling signals to all the connected modules (transmitter) present in that classroom.

The signal is sent to each module and there is a particular time slot given to the students by the faculty within which they are asked to post in their attendance by passing through the two-factor authentication procedure. At the end of that time slot, the receiver module resends a signal which collects the generated list of attendance. On the successful reception of the data, the receiver sends the acknowledgement signal back to the students' module, stating the confirmation of the attendance received. On the contrary if there is any loss of data or errors observed, that particular unique ID number would not get an acknowledgement, by which they are required to repost their attendance.

#### **4 Proposed System Execution**

Implementing the process flow of the system is the major part that should be done carefully. Interfacing each component individually with Arduino UNO 3, and then integrating them completely, gives the final counter system. The student's terminal is the first step, which consists of an RFID reader and the fingerprint sensor with an LCD display connected to the Arduino UNO along with a transceiver. Next is the faculty terminal, which has an Arduino UNO 3 connected with a transceiver which receives the data sent from the students terminal and displays it on the laptop screen which the faculty accesses. The transceiver present at both the terminals is used for sending and receiving data. Further, there is a discussion about the interfacing steps for each component in the system.

In Fig. 3, the overall system process flow is shown. As seen in the process flow diagram, the proceedings of this counter system begin when the students' side terminal get powered on by the initializing signal received from the teacher's terminal. Once the student terminal is powered, the students are accessible to scan their tags along with matching their respective enrolled finger for marking their attendance.

On the event of both the factors of authentication, a temporary database is created and stored in the Arduino present in the student terminal. Once the faculty

Fig. 3 Attendance process flow

in charge clicks on the "STOP" button, there is a link created between the transceivers of the faculty and student terminals. Through SPI communication by the link, the temporary stored database is communicated and enlisted on the GUI screen on the faculty side terminal. The enlisted database created is then saved and used for further processing by the faculty.

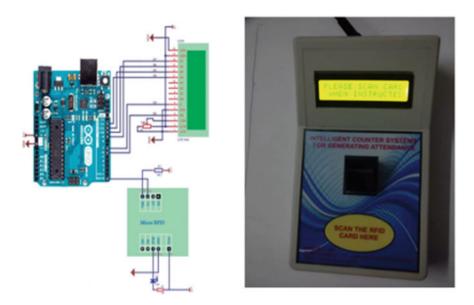

#### 4.1 Interfacing RFID with Arduino

This stage is the first factor for authentication, which is done using the RFID tag and reader. The passive RFID tag is made to swipe over the reader which uses its signals to capture the data from the tag swiped. The reader sends energy to an antenna which converts it into an RF wave and sends it into the read zone. Once the tag is read within the read zone, the RFID tag's internal antenna draws in energy from the RF waves. Mifare RFID reader is connected to the Arduino UNO R3 with its respective pin configurations. The LCD-connected pins, i.e., the secret slave pin and the reset pin of the RFID, are defined. Each card is read by the reader and the unique ID associated with each card is defined with its owner. The details of this owner (i.e., the name of the owner) of that particular card are made to display on the LCD screen as well as the serial monitor screen. When the faculty in the class is ready to take attendance, the faulty gives in the power signal from the terminal present there and once each unit receives the initial start signal, the LCD monitor

Fig. 4 Interfacing RFID with Arduino

present in the students terminal displays the message that reads "SCAN CARD WHEN INSTRUCTED" as shown in Fig. 4. Once the student swipes his RFID tag on the reader, the LCD displays the student's name (owner's name).

In case of any unauthenticated card tapped on the reader, it will display an error message stating the detection of an invalid card.

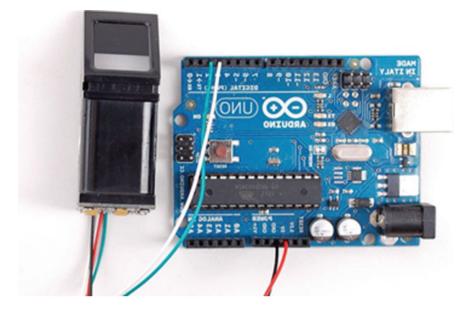

# 4.2 Interfacing Biometric with Arduino

The second factor of authentication is carried out by using the biometric factor, i.e., the fingerprint sensor as shown in Fig. 5. Fingerprint authentication refers to the automated method of verifying a match between the saved fingerprint image and the fingerprint scanned at that moment. Fingerprint is one of many forms of biometrics which is said to be unique and is used to rightly identify individuals or verify their identity, addressed by the enrolment and matching of the fingerprint. The module is connected to Arduino UNO 3 and LCD with its respective pin configurations.

ENROLING—Here, the student's finger is placed twice for confirmation while creating the image and is then made to recognize by the Arduino. By the captured images, a database is created by the allocation of unique ID numbers (starting from 0).

Fig. 5 Interfacing biometric with Arduino

MATCHING—The initial setup is kept the same as that in the enrolling step. The fingerprint sensor is programmed to blink until it identifies and captures a valid finger. Upon capturing, it is compared with the already existing images in the database. If a matched fingerprint is found, the associated ID is displayed on the LCD display.

Depending on the instructions displayed on the LCD, the student imprints and acquires the confirmation with the associated unique number. On the contrary, if it does not match, it displays the error message "NOT MATCHED".

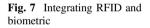

#### 4.3 Integrating RFID and Biometric

This step deals with the integration of the above two explained stages. Each RFID unique number is tagged not only with the owner's name but also with their respective biometric information. At first, the RFID is made to tap on the reader and once the first factor is authenticated successfully, it is then lead to the second level of authentication. At this stage, it captures the fingerprint and checks if it matches with the details pertaining to that of the unique ID of the matched RFID tag.

In Fig. 6, once the student "X" swipes the RFID tag and gets successfully recognized by the reader, the LCD displays as follows:

Fig. 6 Integrating RFID and biometric

X PLACE YOUR FINGER

The student X then will place the enrolled finger on the fingerprint sensor, assuming it was enrolled with the number "1" and gets it verified as the second factor of authentication. If both, the RFID and fingerprint, match successfully, the LCD displays and the next continues the same process to mark his attendance. This is shown in Fig. 7.

1 OK MATCHED

## 4.4 Transmission of Data

The nRF24L01 transceiver is connected on both ends to send and receive the student's data in each hour. The transmission/reception of data through the transceivers takes place only when the numbers of both the transceivers trying to connect and communicate are verified to be the same. In the case of identification of different numbers, there is no communication that takes place between those two transceivers.

## 4.5 Display of the Database

The final step of this counter system is the display of the database on the faculty accessible laptop screen. The data received through the transceiver is displayed on the GUI created for each laptop. The application (or) GUI created on the laptop is programmed such that the faculty has the control from the beginning to the end of attendance process. Once all the databases from each unit in the class are collected,

| 🗱 Form3                                                          | - 0 X                       |

|------------------------------------------------------------------|-----------------------------|

| COM Port<br>R COM5 V Dis-connect Timer: ON                       | E 04-08-2017<br>12:37:58 PM |

| STUDENT PRESENT LIST                                             | VI VII VIII                 |

| IPERIOD<br>12:35:50 PM<br>04:08:2017<br>NAME_4<br>NAME_2<br>Home | HAND TERMINAL               |

| Send display<br>Clear                                            | TERMINAL1 O TERMINAL I      |

| START STOP SAVE SEND TO SERVER                                   | ADD DEL                     |

Fig. 8 Form of the students present

the GUI gives the list of all the students who have marked their attendance in the classroom during that particular hour.

Figure 8 shows the created GUI which has a presentation screen on which the dates with the respective period numbers are mentioned. On the event of clicking upon a particular period, a list of the created database appears on a side tab.

The form is used for creating and storing the initial database of all the students in the educational institution. The form is filled when the students are enrolled in the educational institution at the time of admission. Alongside is also given a provision of viewing the personal information, such as their name, photo, register number, etc., upon selecting the student's database created.

#### 5 Conclusion and Future Work

Thus, the attendance database generated by the intelligent counter system, through the two-factor authentication, is a secured system and does not involve any manipulation of data. Despite the existence of various methods which propose the generation of attendance using RFID solely or the generation of attendance by using only the biometrics factor, our proposed work stands high with the combination of both RFID system and the biometric for a secured way of authenticated attendance marking, thus avoiding proxy. The most common and efficient way of communication is purely wireless. So wireless communication through radio waves is what is carried out in this work. Interference or loss during the transmission is very less compared to the usual communication as SPI communication is the methodology used in this project. For reducing the burden of the faculty and by eliminating the large amount of time taken during marking the attendance, this intelligent counter system does justice.

Another aspect of work that can be done using the RFID tag is by replacing it with a smart card [5]. Each student having their own smart card can access it for multiple purposes in the college premises, for example, paying their fee, using it for paying bills in cafeteria, Xerox purposes, and also for transit application [5].

#### References

- "Biometric Attendance System Circuit" http://www.electronicshub.org/biometric-attendancesystem-circuit/ (22 October 2015)

- Anif Jamaluddin; Dewanto Harjunowibowo; M Akbar Rochim; Fajar Mahadmadi; HBulan Kakanita; Pringgo W. Laksono "Implementation of RFID on Computer Based Test (RF-CBT) system", Proceedings of the Joint International Conference on Electric Vehicular Technology and Industrial, Mechanical, Electrical and chemical Engineering (ICEVT & IMECE), pp. 153– 156, https://doi.org/10.1109/ICEVTIMECE.2015.7496645, IEEE Conference Publications (2015)

- G.V. Ambadkar, A.R. Karwankar, "RFID and Fingerprint Based Student Attendance System", International Journal of Industrial Electronics and Electrical Engineering, ISSN: 2347-6982, vol 3, (4 April 2015)

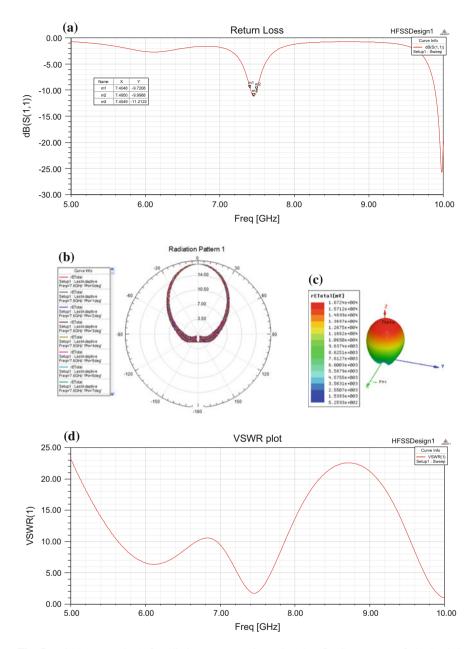

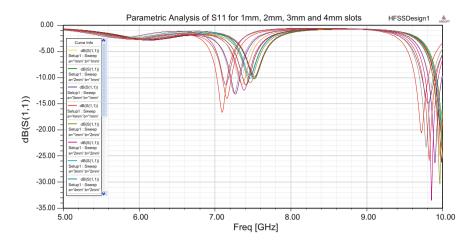

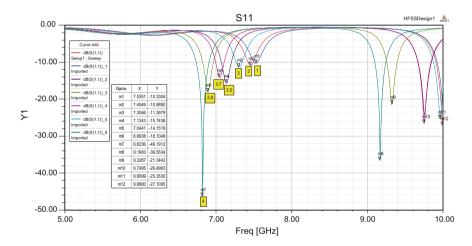

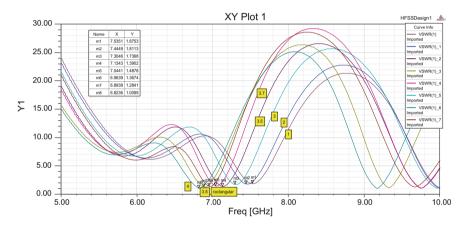

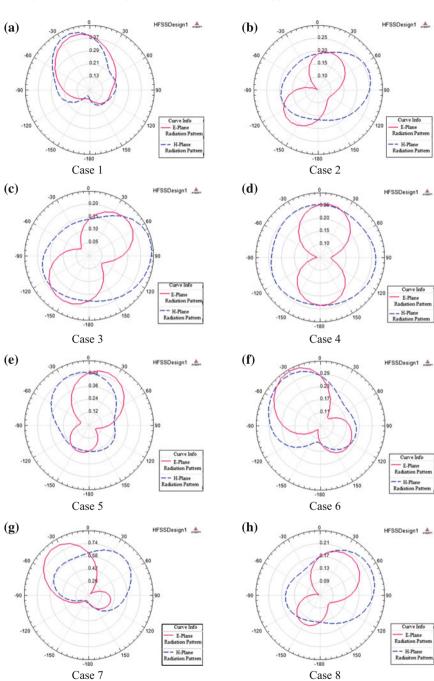

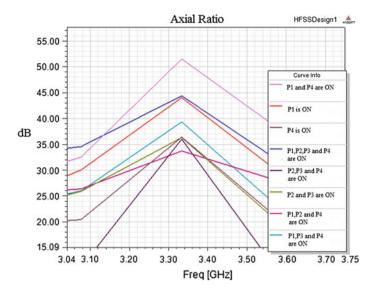

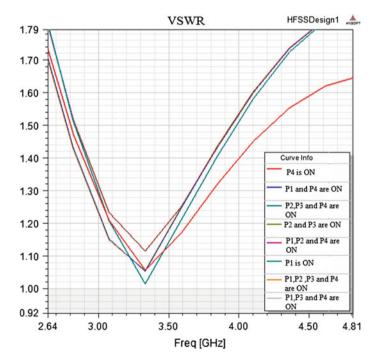

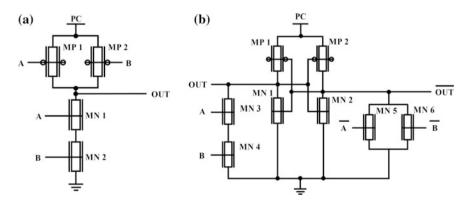

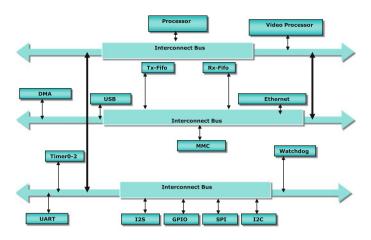

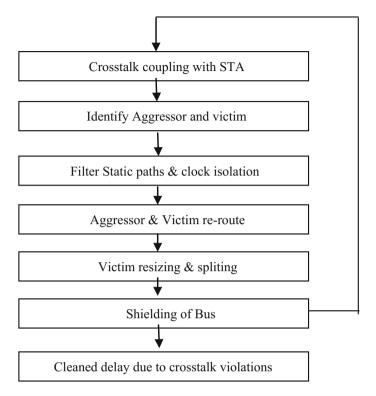

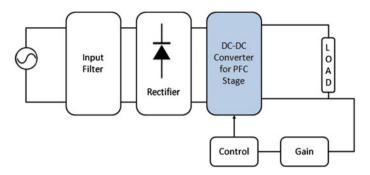

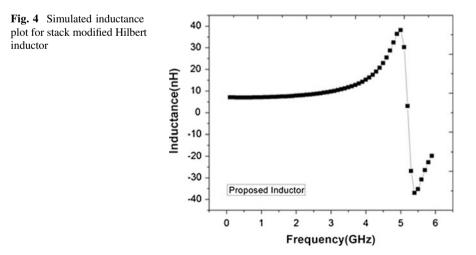

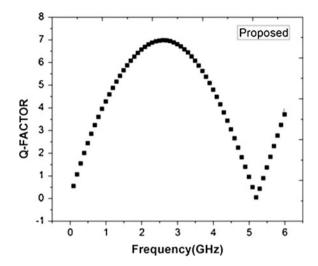

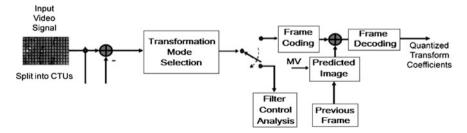

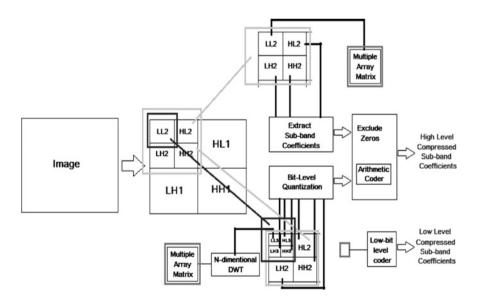

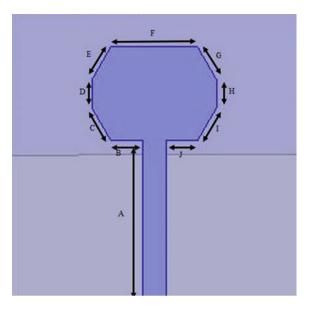

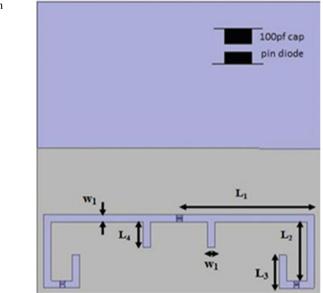

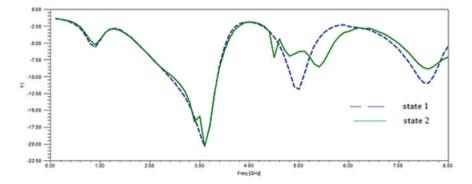

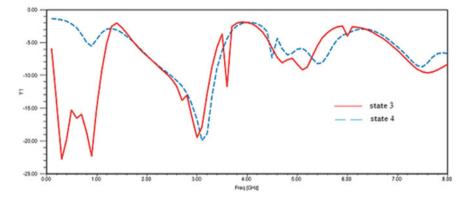

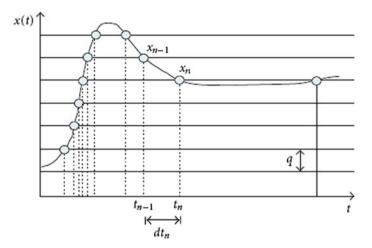

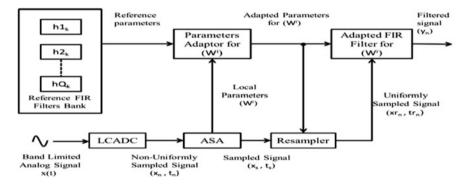

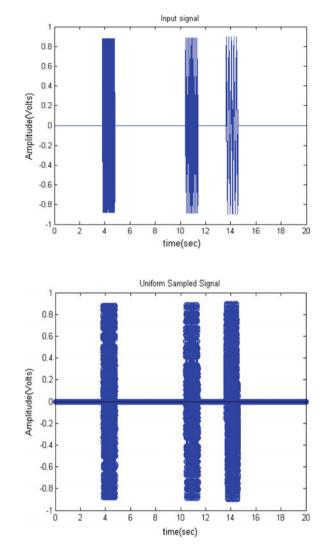

- Kong Shengli, Zhao Jun, Shi Guang, Wu Chunhong, Zhao Wenpei, "The Design and Implementation of the Attendance Management System based on Radio Frequency Identification Technology", International Conference on Electronic Science and Automation Control, (ESAC 2015)