Lecture Notes in Electrical Engineering 403

# Vijay Nath Editor

Proceedings of the International Conference on Nanoelectronics, Circuits & Communication Systems

## Lecture Notes in Electrical Engineering

#### Volume 403

#### **Board of Series editors**

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Haibin Duan, Beijing, China Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Bijaya Ketan Panigrahi, New Delhi, India Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Haitao Wu, Beijing, China Junjie James Zhang, Charlotte, USA

#### About this Series

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

More information about this series at http://www.springer.com/series/7818

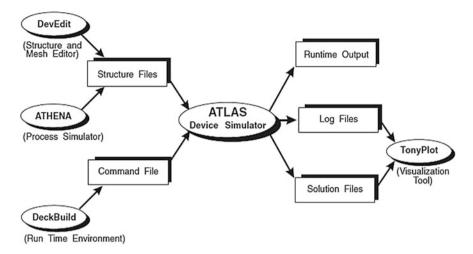

Vijay Nath Editor

# Proceedings of the International Conference on Nano-electronics, Circuits & Communication Systems

*Editor* Vijay Nath Department of Electronics and Communication Engineering Birla Institute of Technology, Mesra Ranchi, Jharkhand India

ISSN 1876-1100

ISSN 1876-1119 (electronic)

Lecture Notes in Electrical Engineering

ISBN 978-981-10-2998-1

ISBN 978-981-10-2998-1

ISBN 978-981-10-2999-8 (eBook)

DOI 10.1007/978-981-10-2999-8

Library of Congress Control Number: 2016956192

#### © Springer Nature Singapore Pte Ltd. 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer Nature Singapore Pte Ltd. The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

## Preface

Manufacturing plays a major role in the development of the country. However, the manufacturing industry is facing several challenges such as rapid product development, flexibility, and low to medium volume, transportation, and low cost etc. Many advanced and unconventional technologies, tools, and software are being developed worldwide to enable solutions to these challenges. Manufacturing and design of integrated circuits (ICs) comprises a large portion of research advances in manufacturing because of the need for precise work. To enable exchange of ideas on current trends in this area, the 1st International Conference on Nano-electronics, Circuits & Communication Systems (NCCS-2015) was organized by the Indian Society of VLSI Education (ISVE), Ranchi and the Institution of Electronics and Telecommunication Engineers (IETE) Ranchi at Advanced Regional Telecom Training Centre (ARTTC) near Jumar River Hazaribag Road Ranchi from 9 to 10th May, 2015. Around 300 papers were received in total, the best of which are presented in this volume. For this selection, all papers were blind reviewed by three expert reviewers and the presentation sessions were reviewed by a six-member expert committee.

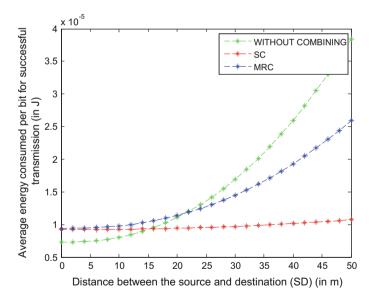

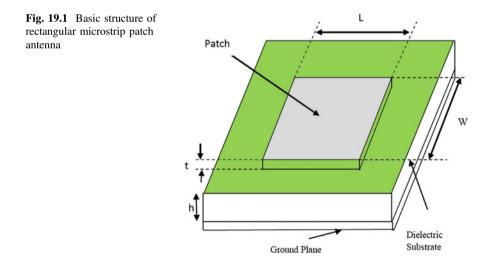

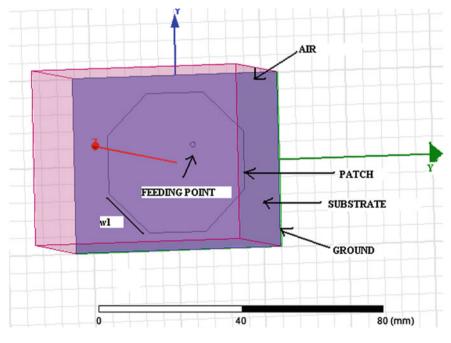

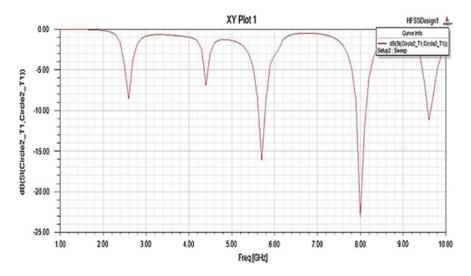

There are a total of 35 papers in this volume that cover the core themes of the conference, i.e., design, simulation, verification, implementation and applications of nano-electronics, circuits and communication systems. The paper by L. Rajesh et al. describe user demand wireless network selection using game theory, with this concept unwanted power radiation will be reduced. Ankur Saxena et al. demonstrate his work on review on band notching techniques for ultra-wideband antenna. Biswajit Ghosh et al. demonstrate his research work on comparing energy efficiency of DF relay assisted cooperative and non-cooperative short-range wireless systems. Abhishek Rawat et al. describe dual band octagonal shape microstrip patch antenna at 5.70 and 8.0 GHz. Nabajyoti Mazumdar et al. explain distributed faulttolerant multi-objective clustering algorithm for wireless sensor network. Abhishek Nag et al. describe an autonomous power in clock getting technology in SRAM-based

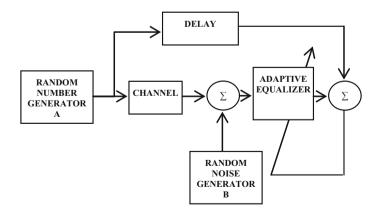

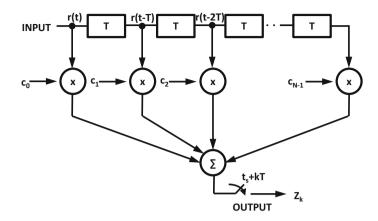

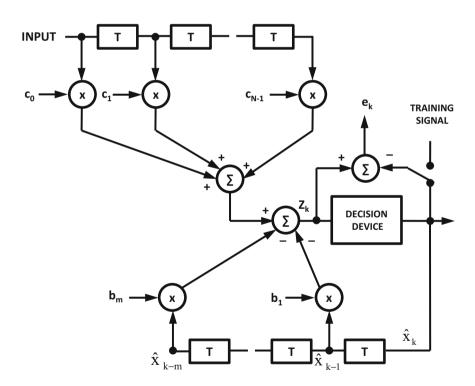

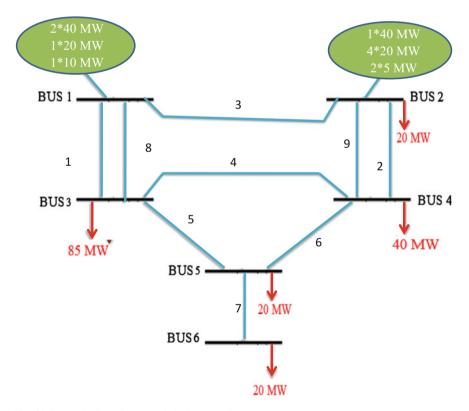

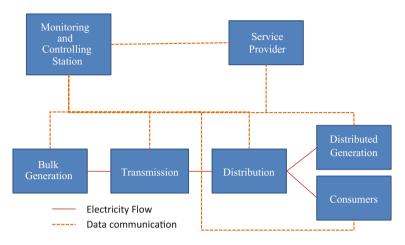

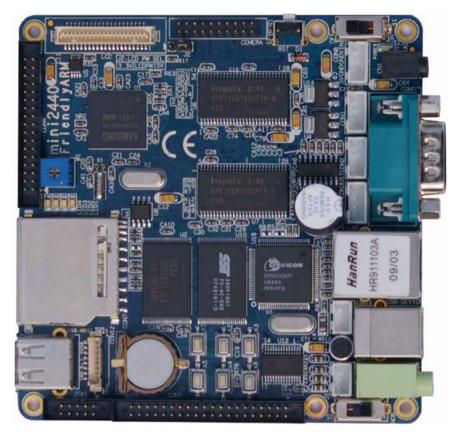

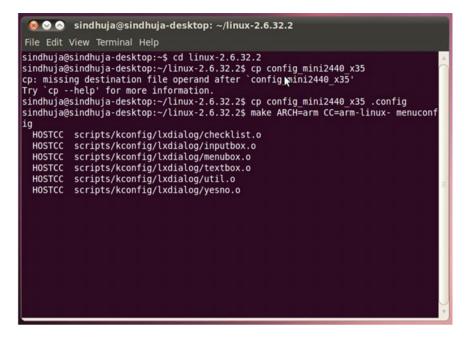

FPGA. C. Ranjith et al. explain a hardware implementation of evolvable embedded system for combinational logic circuits using Vertex 6 FPGA. J. Dhurga Devi et al. describe design of a third order self-bias adaptive band width PLL. Srinivasulu Avireni et al. describe operational transconductance amplifier based sinusoidal oscillator with grounded capacitors. Manas Ray et al. describe the evaluation of wavelet based speech codec for VOIP applications. Trupa Sarkar et al. describe leakage reduction by test pattern reordering. R.K. Mugelan et al. demonstrate the performance enhancement of LTE HetNet using EVM based constellation combiner ECC in warp. D.C. Diana et al. describe modified PSO based equalizer for channel equalization. Abahan Sarkar et al. describe online counting of cigarette in packages as an image processing approach. Jha Vijay Kumar et al. demonstrate fuzzy minmax neural-based intrusion detection system. Amiya Sagar Das et al. describe implementation of breadth first search for storage optimization in random storage assignment of automated storage and retrieval system. Neeti Singh et al. describe efficient algorithms for removal of high-density random value impulse noises in images. Bhabani Shankar Das et al. explain prediction depth average velocity and boundary shear distribution in a single-stage channel by lateral distribution method. Kamalini Devi et al. describe the flow computation in symmetric compound channels using conveyance estimation system. Sarika Tyagi et al. describe a 21 nW CMOS operational amplifier for biomedical application. Pallavi Dutta et al. describe performance analysis of three-phase induction motor using Simulink and TMS320C6713. Abhishek Gandhar et al. describe effect of static synchronous series compensator on power balancing in wind farms. Mohini Yadav et al. describe reliability and energy benefit analysis of distribution system incorporating wind turbine generator. A.K.P. Kovendan et al. describe present context of smart girds in India: a survey. S. Sridevi et al. describe real-time simulation design for continuous process industries. M. Rajendra Prasad et al. describe system level performance analysis of embedded system for GSM application. S.M. Annapurna et al. describe robotics research visibility in BRICS country as a scientometrics study. A. Ravishankar Holla et al. describe characterization of TFT sensors for chemical sensing applications. Anurag Kumar Paliwal et al. describe design of a high-performance CMOS charge pump for phase-locked loop synthesizers. Adesh Kumar et al. describe IC packaging with 3D IC tech. method. Akshat Chitransh et al. describe analysis of a self-compensating, low-noise, low-power PLL circuit @45 nm technology node. Krishan Kumar Singh et al. describe design of comparator in sigma delta using 45 nm CMOS technology. Sudhanshu Kumar et al. describe investigation of electrostatic actuation scheme for low-voltage MEMS switch. Kumar Amit et al. describe evaluating the performance of dye-sensitized solar cell with the various key components like electrodes, dyes and electrolytes. Jitendra Yadav et al. describe modeling and simulation of the dynamic response of a generic mechanical linkage for control application under the consideration of the nonlinearities imposed by friction.

Preface

Authors and editors have taken utmost care in preparing this volume for publication, but there some errors that might have crept in despite our best efforts. Readers are requested to provide their valuable feedbacks on the quality of presentation and alert us of any inadvertent errors or omissions. We expect that the book will be welcomed by students as well as practicing engineers, researchers, and professors.

Ranchi, India

Vijay Nath

### **Editorial Acknowledgements**

We extend our thanks to all the authors for contributing to this book by sharing their valuable research findings. We specially thank a number of reviewers for promptly reviewing the papers submitted to the conference. We are grateful to the volunteers, invited speakers, session chairs, sponsors, sub-committee members, members of international advisory committee, and members of national advisory committee, members of technical program committee, members of joint secretary, and members of scientific advisory committee for successful conclusion of the conference. The editors express their heartfelt gratitude towards Smriti Dagur, President IETE New Delhi, Sanjay Kumar Jha, Executive Engineer Government of Jharkhand & Chairman of IETE Ranchi, Prasad Vijay Bhushan Pandey, DGM ETR Jharkhand Circle Ranchi & Chairman ISVE Ranchi, A.A. Khan, Former VC Ranchi University, M.K. Mishra, VC BIT Mesra, Labh Singh, CGM BSNL Ranchi, K. Pandey, VC Ranchi University, P.K. Barhai, Former VC BIT Mesra, R. Mishra, Former CMD HEC Ranchi, Ajay Kumar, AGM(admin) ARTTC BSNL Ranchi & Secretary IETE Ranchi, P.R. Thakura, Executive member of ISVE & Professor of BIT Mesra Ranchi, Anand Kumar Thakur Treasurer, IETE Ranchi for their support, encouragement, and motivation to organize such a prestigious event that paved the way for this book on nano-electronics, circuits and communication systems (NCCS). Finally, we express our sincere gratitude towards the editorial team at Springer who helped in publishing this book.

# Contents

| 1 | An Autonomous Power and Clock Gating Technique<br>in SRAM-Based FPGA<br>Abhishek Nag and Sambhu Nath Pradhan                                                         | 1   |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | A Hardware Implementation of Evolvable Embedded System<br>for Combinational Logic Circuits Using Virtex 6 FPGA<br>C. Ranjith and S.P. Joy Vasantha Rani              | 15  |

| 3 | Evaluation of Wavelet-Based Speech Codecs for VoIP<br>Applications<br>Manas Ray and Mahesh Chandra                                                                   | 29  |

| 4 | User Demand Wireless Network Selection Using<br>Game Theory<br>L. Rajesh, K. Boopathy Bagan and B. Ramesh                                                            | 39  |

| 5 | Leakage Reduction by Test Pattern Reordering<br>Shrabanti Chakraborty, Trupa Sarkar and Sambhu Nath Pradhan                                                          | 55  |

| 6 | Review on Band-Notching Techniques for Ultrawideband         Antenna                                                                                                 | 69  |

| 7 | Real-Time Simulation Design for Continuous Process         Industries          S. Sridevi and P. Sakthivel                                                           | 83  |

| 8 | Performance Enhancement of LTE HetNet Using EVM-Based<br>Constellation Combiner (ECC) in WARP<br>R.K. Mugelan, M. Anusiya and M.A. Bhagyaveni                        | 99  |

| 9 | Performance Analysis of 3-Phase Induction Motor: Through<br>Simulation in SIMULINK and TMS320C6713<br>Nutan Lata Nath, Pallavi Dutta, Shilpi Kumari and Urjaswit Lal | 113 |

| С | on | te | n  | ts |

|---|----|----|----|----|

| C | on | u  | 11 | u  |

| 10 | A Distributed Fault-Tolerant Multi-objective Clustering<br>Algorithm for Wireless Sensor Networks<br>Nabajyoti Mazumdar and Hari Om                                                                           | 125 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11 | Comparing Energy Efficiency of DF Relay-Assisted Cooperative<br>and Noncooperative Short-Range Wireless Systems<br>Biswajit Ghosh, Aniruddha Chandra and Ashis Kumar Mal                                      | 139 |

| 12 | <b>Modified PSO-Based Equalizers for Channel Equalization</b><br>D.C. Diana and S.P. Joy Vasantha Rani                                                                                                        | 153 |

| 13 | Investigation of Electrostatic Actuation Scheme for Low<br>Voltage MEMS Switch<br>Sudhanshu Kumar, Neela Chattoraj, Manish K. Sinha<br>and Niharika Danu                                                      | 167 |

| 14 | On Online Counting of Cigarette in Packets—An Image<br>Processing Approach                                                                                                                                    | 177 |

| 15 | Fuzzy Min-Max Neural Network-Based Intrusion DetectionSystemAzad Chandrashekhar and Jha Vijay Kumar                                                                                                           | 191 |

| 16 | Effect of Static Synchronous Series Compensator on Power<br>Balancing in Wind Farms<br>Abhishek Gandhar, Balwinder Singh and Rintu Khanna                                                                     | 203 |

| 17 | Characterisation of TFT Sensors for Chemical Sensing         Applications         A. Ravishankar Holla, Ananth Noorithaya and M. Uttarakumari                                                                 | 215 |

| 18 | Storage Optimization of Automated Storage and RetrievalSystems Using Breadth-First Search AlgorithmAmiya Sagar Das, Prashant Kumar Dwivedi, Amit Kumar Mondal,Roushan Kumar, R. Manohar Reddy and Adesh Kumar | 229 |

| 19 | Design Analysis of Octagonal-Shaped Microstrip Patch Antenna<br>at 5.70 and 8.00 GHz<br>Dinesh Kumar Cholkar and Abhishek Rawat                                                                               | 239 |

| 20 | Blueprint of a CMOS Charge Pump for Phase-Locked Loop<br>Synthesizers with High Efficiency<br>Adesh Kumar, Anurag Kumar Paliwal and Saurabh Sharma                                                            | 249 |

| 21 | An Efficient Algorithm for Removing RVIN<br>in Grayscale Images<br>Neeti Singh, G. Vasugi and O. UmaMaheswari                                                                                                 | 259 |

| 22 | Reliability Analysis and Energy Benefit Analysis of Distribution<br>System Incorporating Wind Turbine Generator<br>Mohini Yadav, Prem Prakash and R.C. Jha                                                    | 265 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 23 | <b>Development of Smart Grid System in India: A Survey</b> A.K.P. Kovendan and D. Sridharan                                                                                                                   | 275 |

| 24 | System-Level Performance Analysis of Embedded Systemsfor GSM ApplicationsM. Rajendra Prasad and D. Krishna Reddy                                                                                              | 287 |

| 25 | IC Packaging: 3D IC Technology and Methods<br>Adesh Kumar, Gaurav Verma, Vijay Nath and Sushabhan Choudhury                                                                                                   | 303 |

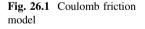

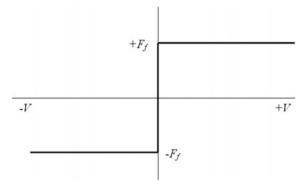

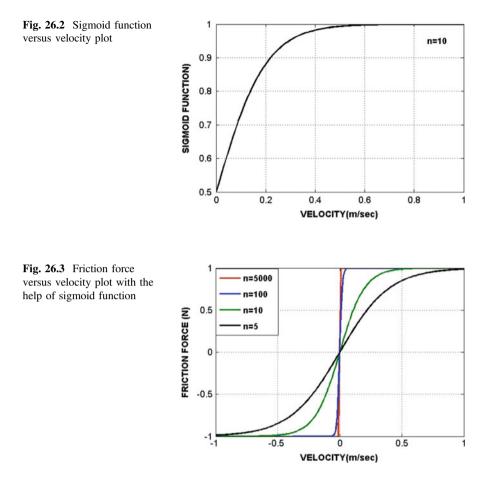

| 26 | Modeling and Simulation of the Dynamic Response<br>of a Generic Mechanical Linkage for Control Application<br>Under the Consideration of Nonlinearities Imposed<br>by Friction                                | 319 |

| 27 | Design of a Third Order Self Biased Adaptive Bandwidth<br>Phase Lock Loop<br>J. Dhurga Devi                                                                                                                   | 331 |

| 28 | <b>Operational Transconductance Amplifier-based Sinusoidal</b><br><b>Oscillator with Grounded Capacitors</b><br>Srinivasulu Avireni, G. Sowjanya, S.H. Gautham,<br>Pitchaiah Telagathoti and V.S.V. Krishna V | 343 |

| 29 | Robotics Research Visibility in BRICS Countries:A Scientometrics StudyM. Vijayakumar and S.M. Annapurna                                                                                                       | 353 |

| 30 | Analysis of a Self-compensating, Low-Noise, Low-Power<br>PLL Circuit @ 45-nm Technology Node<br>Agnish Mal, Akshat Chitransh, Harsh Srivastava, Suraj Kumar Saw<br>and Vijay Nath                             | 361 |

| 31 | Evaluating the Performance of Dye-Sensitized Solar Cell<br>with Various Key Components such as Electrodes, Dyes,<br>and Electrolytes<br>Rishi Sharma, Kumar Amit, P.K. Barhai and R.L. Boxmann                | 371 |

| 32 | Design of Comparator in Sigma-Delta ADC Using 45 nm<br>CMOS Technology<br>Varun Kumar, Krishan Kumar Singh, Abhishek Pandey<br>and Vijay Nath                                                                 | 381 |

| 33 | A 21nW CMOS Operational Amplifier for Biomedical<br>Application                                                                             | 389 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | Sarika Tyagi, Swapnil Saurav, Abhishek Pandey,<br>Padma Priyadarshini, Madhu Ray, B.B. Pal and Vijay Nath                                   | 007 |

| 34 | Prediction of Depth-Averaged Velocity and Boundary Shear<br>Stress Distribution in a Single-Stage Channel by Lateral<br>Distribution Method | 397 |

|    | Bhabani Shankar Das, Kishanjit K. Khatua and Kamalini Devi                                                                                  |     |

| 35 | Flow Computation in Symmetric and Asymmetric Compound                                                                                       |     |

|    | Channels Using Conveyance Estimation System                                                                                                 | 409 |

### About the Editor

**Dr. Vijay Nath** received his Bachelor's degree in Physics and Master's degree in Electronics from DDU Gorakhpur University, India in 1998 and 2001. He received a PGDCN from MMM Engineering College Gorakhpur (Gold Medalist) in 1999. He received his Ph.D. in VLSI Design & Technology from Dr. RML Avadh University, Faizabad in association with CEERI- Pilani in 2008. He was a member of the faculty of the Department of Electronics, DDU Gorakhpur University, Gorakhpur (2002–2006). In 2006, he joined as a faculty member in the Department of Electronics and Communication Engineering, Birla Institute of Technology Mesra, Ranchi, India. Currently he is Professor In-charge of VLSI Design Lab & Embedded System Design Lab, Department of ECE, BIT Mesra, Ranchi. His research interests include analog, digital, mixed CMOS VLSI circuits, low-power VLSI circuits, ADC, DAC, PTAT, CMOS bandgap voltage reference, piezoresistive pressure sensors, double ring capacitive pressure sensors, MEMS sensors, signal-processing circuits, ASICs, embedded systems designs, smart cardiac pacemaker, and early stage cancer detection. He has to his credit around 100 publications in international journals and conferences. He is a member of several reputed professional and academic bodies including IETE, ISVE, and IEEE.

## Chapter 1 An Autonomous Power and Clock Gating Technique in SRAM-Based FPGA

Abhishek Nag and Sambhu Nath Pradhan

#### 1.1 Introduction

Dynamic power was given the utmost importance initially for power reduction schemes in a FPGA; however, recent studies indicate the major impact of leakage power in the total power dissipation [1]. Power gating has turned out to be a popular method of leakage reduction in FPGA. All prior works in this field have used spice-based modeling of the FPGA to carry out any transistor-level operation, as in [2, 3]. Most of these prior works have been associated with the theoretical aspect of FPGA operations.

In [3], the authors have considered power-reducing techniques in a FPGA by obtaining spice net list of the architectures and varying the various parameters associated. Power gating has proven to be one of the most popular methods of reducing the leakage power of a programmable device [4]. Configuration bits were mostly used in earlier works involving power gating, to control the power. This is termed as statically controlled power gating, as in [5, 6]. The concept of dynamically controlled power gating was very recently introduced in programmable device such as in [7].

On the other hand, clock gating is an efficient technique of dynamic power reduction, by stopping the activity of clock during inactive periods of the circuit, as in [8–10]. Similar works in this field include the work done in [11, 12], considering spice precharacterization level modeling of the FPGA. However, implementing the power reduction operations in a circuit level will provide more insight into the working of the programmable device and an elaborate analysis can be carried out.

A. Nag (🖂) · S.N. Pradhan

Department of Electronics and Communication Engineering, National Institute of Technology Agartala, Agartala, India e-mail: abhi14379@gmail.com

S.N. Pradhan e-mail: sambhu.pradhan@gmail.com

© Springer Nature Singapore Pte Ltd. 2017

V. Nath (ed.), Proceedings of the International Conference on Nano-electronics, Circuits & Communication Systems, Lecture Notes in Electrical Engineering 403, DOI 10.1007/978-981-10-2999-8\_1

In this work, an efficient and dynamic technique of power and clock gating is introduced in a SRAM-based TILE prototype, designed and developed in CADENCE tool, using a technology of 45 nm. Our TILE architecture is inspired from the work done by authors in [13]. Correct simulation results have been obtained for all the sub-blocks of the architecture. We have implemented a basic FSM circuit in the TILE and introduced a fine level gating technique in the proposed architecture. The simulation results indicate significant reduction of the total power of the TILE prototype. An in-depth delay analysis is also obtained and reported.

The following paper is presented as follows: Sect. 1.2 presents the basics of power and clock gating techniques. The transistor-level design of the TILE prototype is presented in Sect. 1.3. Section 1.4 deals with the proposed power and clock gating logic implemented in the TILE prototype. The experimental results of the power-gated FPGA are presented in Sect. 1.5 followed by conclusion in Sect. 1.6.

#### **1.2 Power and Clock Gating**

In this section, we elaborate about the basics of the gating techniques being used in our approach for power reduction of the TILE.

#### 1.2.1 Power Gating

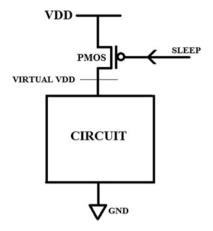

Power gating has proven to be one of the most effective methods of reducing leakage power of a circuit [4]. Power gating techniques were initially introduced for ASICs, which can now be implemented on programmable devices also. With the growing need for programmable devices like FPGA, power dissipation stands as a major concern. Consequently, power reduction techniques are gaining popularity. The basic of power gating is to disable/enable the functionality of a circuit by a sleep transistor or power switch. The voltage supply of a device is provided through a PMOS transistor, called the sleep transistor on or off. The gate input to sleep transistor is called the sleep signal or activation signal, which decides the criteria of when to turn the sleep transistor "on" or "off." The function generating the activation signal is termed as activation function. The power gating basics is explained in Fig. 1.1.

Power gating significantly reduces the overall leakage power of the circuit. However, the extra PMOS transistor results in some resistance, which may affect the performance of the circuit. By appropriately sizing the transistor, an acceptable trade-off between power and performance can be obtained. Again, the excess area

Fig. 1.1 Basic of power gating

overhead will be minimal when the same transistor is used to power gate a large portion of the circuit.

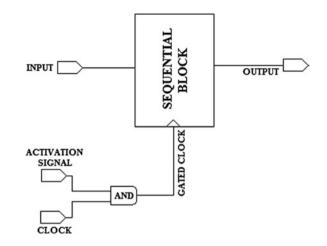

#### 1.2.2 Clock Gating

Clock gating has turned out to be a popular technique of dynamic power reduction in a sequential circuit [8]. The clock gating logic is to stop the activity of the clock, when no useful computation is being performed by the circuit. In other words, when a sequential circuit does result in any state transition, the clock is being disabled to reduce the unnecessary power dissipated by the clock during idle states. The activation signal for clock gating is kept low when the necessary clock gating condition occurs, which is then AND gated with the global clock signal to obtain the gated clock. By knowing the inputs and states of a circuit, activation signal can be generated. The gated clock signal is then finally provided to a sequential block, which needs to be gated. The basic idea of clock gating in a sequential circuit is depicted in the following Fig. 1.2.

#### **1.3 Transistor-Level Design**

The FPGA prototype developed in this work is a SRAM-based TILE-oriented FPGA. Static memory cells are the basic building blocks of the FPGA. The SRAM cells are arranged throughout the entire FPGA architecture for providing configuration. SRAM-based programming technology is the most popular approach for FPGA due to its reprogrammable nature and use of standard CMOS process

technology. This leads to increased integration, higher speed, and lower dynamic power consumption.

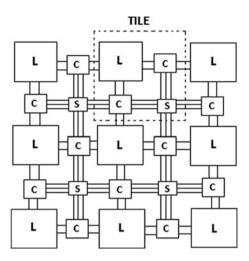

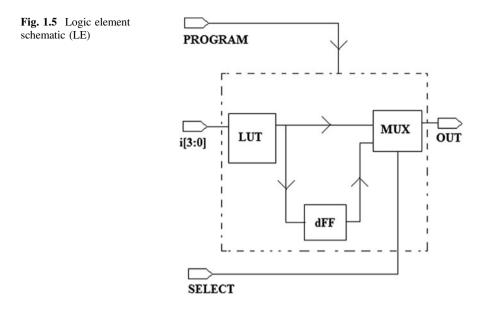

FPGA, being a regular architecture, is divided into TILEs, where each TILE compromises of logic element and routing resources. The basic building blocks of a TILE-based FPGA in its highest level are logic element (LE), which consists of a lookup table (LUT), flip-flop, and a multiplexer that chooses whether to forward the output of the LUT or the flip-flop outside the LE. A k-LUT consists of a set of multiplexers that can implement any function of k inputs by forwarding one of the 2 k configuration bits to the output of the LUT. LEs are interconnected with routing resources, which are also configurable. Configuration of routing resources is achieved using pass gates controlled by a routing configuration bits. The desired configuration is stored in SRAM cells. One SRAM cell is required per pass gate, while a k-LUT requires 2 k SRAM cells.

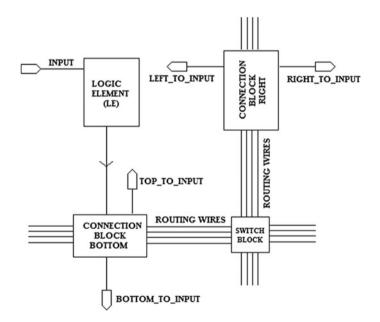

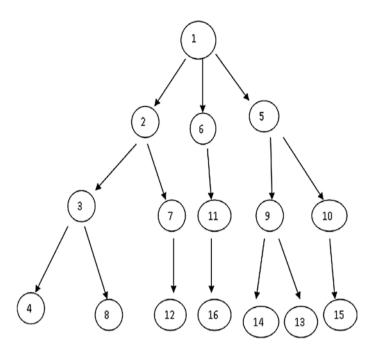

The routing resources include connection blocks (C) and switch blocks (S), where the purpose of connection block is to interconnect the logic elements, whereas the routing wires (running horizontally and vertically) are connected inside the switch block. The FPGA developed in this work is based on the architecture developed in [13]. The top view of a TILE-based FPGA architecture is shown in Fig. 1.3 [13].

The structure of a TILE with the corresponding programming and routing resources used in this work is shown in Fig. 1.4. The entire architectural description of the internal structures is explained in [13].

#### 1.3.1 Logic Element

The logic element is the computational block of an FPGA. This is where an arbitrary function can be applied to the input signals to produce a specific result.

gating

Fig. 1.2 Basic of clock

Fig. 1.3 Top view of FPGA architecture

Fig. 1.4 Outline of a basic TILE structure

Figure 1.5 shows the top level view of the logic element. The logic element used in this work consists of three sub-blocks: a 4 input LUT, a register, and a 2:1 MUX.

The LUT is used to create the result of the desired arbitrary function. LUTs are chosen because at the time of fabrication of the FPGA, it is unknown what functions

the end user of the FPGA wants. LUT is the simplest way to provide the functionality for allowing arbitrary function to be programmed. In this work, we use 4 input LUTs, and hence, each LUT needs 16 (24) SRAM cells (it is 24 because each input can have two values [0 or 1], and there are 4 inputs). The SRAM cells are to be programmed with the 16 possible results of the arbitrary functions. The inputs to the LUT are provided through the select lines.

#### 1.3.2 TILE

The design and simulation of the TILE architecture in Fig. 1.4 has been carried out in CADENCE Virtuoso spectrum at 45 nm technology. Figure 1.6 shows the input and output terminals of a single TILE.

The description and configuration of the various input and the output pins of the TILE are presented in Table 1.1.

As mentioned earlier, using an array of rows and columns of the above TILE, an entire FPGA architecture can now be established [13]. In our architecture, we have not considered the impact of I/O blocks associated with FPGAs. Also, since our aim is just to analyze the effectiveness of our proposed gating technique in the TILE, we have not considered the resistive and capacitive effect after layout generation of the TILE prototype. All these points are kept in considerations for future scope.

|              |        | -  | _          | -  | -  |      | -   | •        | ٠  | t          | Ŧ | - | -   | -  | -   |      |      | _  |

|--------------|--------|----|------------|----|----|------|-----|----------|----|------------|---|---|-----|----|-----|------|------|----|

|              | -      | -  | _          | _  | _  | _    | -   | Ŀ        | Ť  | 느          | 느 | - | -   | _  | _   |      | -    |    |

| VDD          |        | 1  | 1          | 1  | 2  | ġ    |     | 5        | C  | v_track(2) | g |   | 1   | 1  | 1   |      | 1    | 13 |

| VDD          |        |    |            |    |    | . H  | • • | <u> </u> | ₫. | 5          | 2 |   |     |    |     |      |      |    |

| CLOCK        | • • •  | +  | • •        |    |    |      | 1.  | 2        | 3  | E.         | Ε |   |     |    |     |      |      | Ŀ  |

|              |        | 1  |            |    | *  | 2    |     | 5        | -  | 1          | - | 1 | 1   | 1  |     |      |      | Ľ  |

| BL           | •      |    |            |    |    |      |     |          |    |            |   | 1 | -   | 1  |     |      |      |    |

| BLB          | • • •  |    |            |    |    | . 5  | •   |          |    |            |   | F | lig | ht | to  | in   | put  | ⊢  |

| WL           |        | •  | • •        |    |    | - H  |     |          |    | • •        | • |   |     |    |     |      | · ·  | Ŀ  |

|              |        | *  | • •        |    | *  | • •  | *   |          | *  | •          |   | 1 | *   |    |     |      |      |    |

| Left_to_in   | put .  | ÷. |            |    | 1  |      | 1   | ÷.       |    |            |   |   | 1   |    |     |      |      | L  |

|              | • • •  |    |            |    |    |      |     |          |    |            |   |   |     |    |     |      |      | L  |

| RESET        |        |    |            |    |    |      | *   |          |    | • •        |   |   |     |    |     |      |      |    |

| SET          |        |    | • •        |    | •  | * *  | *   | *        |    | • •        | • |   | *   |    | *   |      |      |    |

| - SEL        | - : :  | 1  | : :        | 1  | 1  | •    |     | ÷.       | 2  | 2.2        |   |   | 1   | 1  |     |      |      | L  |

| I_track(0)   | •      |    |            |    |    |      |     |          |    |            |   |   |     |    |     |      | k(0) |    |

|              |        |    |            |    |    |      |     | -        | -  |            |   |   | -   | -1 | r_t | raci | k(1) | ⊢  |

| l_track(1)   |        | *  | • •        |    | *  |      | *   | *        | *  | • •        |   |   | *   |    |     |      | k(2) |    |

| h_track(2)   |        | ÷. | 1.1        | 1  | 2  |      | 1   | ÷.       | 1  | 1          |   | 1 | 1   |    |     |      |      |    |

| h_track(3)   | •      |    |            |    |    |      |     | ÷.       |    |            |   |   |     |    | ÷   | rac  | k(3) | г  |

| 1            |        |    |            |    |    | • •  |     |          |    |            |   |   |     |    |     |      |      | L  |

|              |        |    |            |    |    | • •  | *   |          | *  | • •        |   |   | ٠   |    |     |      |      |    |

| -11          | input  | •  |            |    | +  |      | 1   | ÷.       | 1  | 1          |   | 1 | 1   |    | 1   |      |      |    |

| - i2 · · · · | · . #, |    |            |    |    |      | 1   |          |    |            |   |   |     |    |     |      |      | L  |

| -i3 .        | 3      | 0  | -          | 0  | -  |      |     |          |    |            |   |   |     |    |     |      |      | L  |

| -i4          | · ·    | ŝ  | Ç,         | G, | S. |      |     |          |    |            |   |   | +   | -  |     |      |      |    |

| 14           | - · 8  | 5  | 2          | 5  | 2  |      |     |          | •  | • •        |   |   | *   | •  | *   |      |      | L  |

|              |        | E. | E.         | Ξ. | E  | 3    |     | ÷.       | 2  | 1          |   |   | 1   | 1  |     |      |      | 1  |

|              | Bottom | ام | b_track(1) | 1  | 1  | -    |     |          |    |            |   |   |     |    |     |      |      | L  |

|              | 1      | Ť  | Ť          | T  | T  | ŀ    | +   | +        | +  |            |   |   | +   |    | +   | • •  |      |    |

|              |        | ⊥  | ÷.,        | +  | 1  | - L- |     |          |    |            |   |   |     |    |     |      |      |    |

Fig. 1.6 I/O terminals of a TILE

| Sl. no. | PIN name                                    | Description                             | Direction |

|---------|---------------------------------------------|-----------------------------------------|-----------|

| 1       | VDD                                         | Supply voltage                          | Input     |

| 2       | Clock                                       | DFF clock signal                        | Input     |

| 3       | BL, BLB                                     | Bit lines (program data)                | Input     |

| 4       | WL                                          | Word line                               | Input     |

| 5       | Set, reset                                  | Set/reset signal of DFF                 | Input     |

| 6       | l_track(0,1), r_track(0,1),<br>b_track(0,1) | Routing tracks                          | I/O       |

| 7       | t_track(0,1), v_track(2,3),<br>h_track(2,3) | Routing tracks                          | I/O       |

| 8       | i1, i2, i3, i4                              | LE inputs                               | Input     |

| 9       | Bottom_to_Input, Top_to_Input               | Outputs from connection<br>block bottom | Output    |

| 10      | Right_to_Input, Left_to_input               | Output from connection block right      | Output    |

| 11      | VSS                                         | Ground terminal                         | Input     |

#### 1.4 Proposed Power and Clock Gating Technique

In order to carry out gating in the TILE, we have first implemented an arbitrary 4 input FSM circuit "EXCKT" in the TILE. A finite state machine (FSM) is an abstract model of a system (physical, biological, mechanical, electronic, or software). FSM is modeled as a useful abstraction for sequential circuits containing

Fig. 1.7 Block diagram of a FSM

| I(2) | I(1) | I(0) | PS | 0 | NS |

|------|------|------|----|---|----|

| 0    | 0    | 0    | 0  | 0 | 0  |

| 0    | 0    | 0    | 1  | 1 | 0  |

| 0    | 0    | 1    | 0  | 1 | 0  |

| 0    | 0    | 1    | 1  | 1 | 0  |

| 0    | 1    | 0    | 0  | 0 | 1  |

| 0    | 1    | 0    | 1  | 1 | 1  |

| 0    | 1    | 1    | 0  | 1 | 1  |

| 0    | 1    | 1    | 1  | 0 | 0  |

| 1    | 0    | 0    | 0  | 1 | 0  |

| 1    | 0    | 0    | 1  | 0 | 0  |

| 1    | 0    | 1    | 0  | 0 | 1  |

| 1    | 0    | 1    | 1  | 0 | 0  |

| 1    | 1    | 0    | 0  | 0 | 1  |

| 1    | 1    | 0    | 1  | 1 | 1  |

| 1    | 1    | 1    | 0  | 1 | 1  |

| 1    | 1    | 1    | 1  | 0 | 1  |

Table 1.2 State table of a 4 input FSM circuit

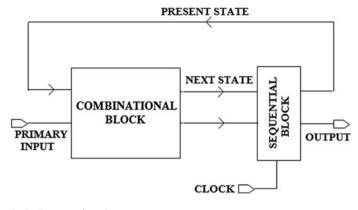

centralized "states" of operation. At each clock edge, combinational logic generates outputs and next state as a function of inputs and present state. The block diagram of a mealy FSM is shown in Fig. 1.7.

The description of an arbitrary FSM circuit "EXCKT" is presented in the following Table 1.2. Here, "PS" stands for present state and "NS" stands for next state. The implementation of the FSM circuit in the FPGA is done by simple binary coding technique, where all the output and next state bits are generated in an individual TILE. Based on the description of the FSM circuit EXCKT in Table 1.2, we require two TILEs to generate the output (O) and next state (NS). The

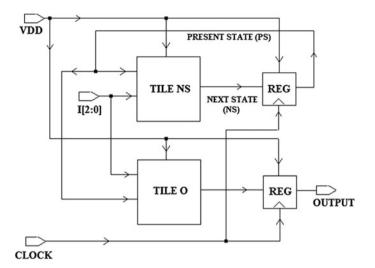

Fig. 1.8 Implementation of EXCKT in FPGA

architecture of the TILEs implementing the FSM EXCKT is shown in the Fig. 1.8. A register (REG) is being utilized in the architecture to generate the present state of the FSM as FPGA has scope for inbuilt memory devices in their architecture. We have developed the register using D-F/Fs, in the same 45 nm technology.

#### 1.4.1 Method of Gating

The idea of gating the TILE is obtained from the logic used in [14]. The logic of gating the circuit in [14] was used for reducing the dynamic power, by implementing clock gating in ASICs. However, we have extended that approach in our architecture for implementing concurrent clock and power gating, to achieve total power reduction of a programmable TILE.

The basic logic behind gating the architecture is to stop the functionality of a circuit when the present state and next state of the FSM become equal, referred to as "self-loops." During that instant, the TILE implementing the next state function is no longer required to operate and compute. To avoid the functioning of the TILEs during self-loops, the architecture is power gated, depending on the sleep signal generated. The sleep signal, also referred to as the activation signal, is generated from the knowledge of the present state and primary inputs of the circuit, and the function generating the sleep signal is termed as activation function. The activation signal becomes high when a self-loop occurs and restricts the power supply to the TILE, through a PMOS (sleep transistor). The activation function is implemented as

a combinational block which extracts information from the primary inputs and state inputs of the circuit.

Activation signal =

$$\begin{array}{l} 1, & \text{if } PS = NS \\ 0, & \text{else} \end{array}$$

(1.1)

Based on the state table presented in Table 1.2, the activation function (F) generated for the FSM EXCKT is,

$$F = [\sim I(0). \sim I(1). \sim PS] + [\sim I(1). \sim I(2). \sim PS] + [I(1). \sim I(2).PS]$$

(1.2)

Here "~" stands for NOT operation. Concurrently, with the power gating of the TILE, the register (REG) clock signal in Fig. 1.8 is disabled during self-loops. Disabling the activity of clocks during periods of inactivity (self-loops in this case) results in significant dynamic power savings of the FPGA. The clock gating of the registers is achieved by AND gating the global clock signal with the activation signal. The clock gating condition called activation signal is so generated such that it becomes low whenever a self-loop occurs. Thus, the gated clock signal will be low during self-loops irrespective of the state of the global clock.

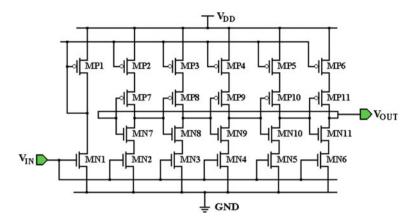

#### 1.4.2 Power and Clock-Gated TILE

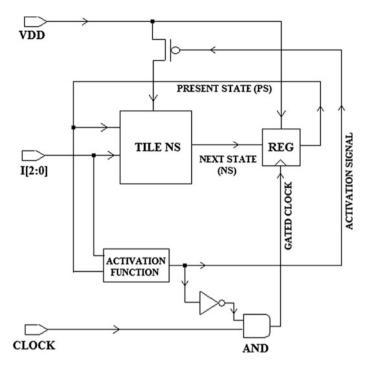

The TILE architecture displaying the concurrent power and clock gating is shown in Fig. 1.9. The activation function is same for both clock gating and power gating. The power gating is carried out through a PMOS transistor, where the activation signal is fed as the gate input and the power supply to its drain input. Based on the activation signal, the PMOS gets switched on and off, thus controlling the supply voltage from entering the TILE. The activation signal becomes high, whenever a self-loop appears and hence shuts down the pMOS transistor. On the other hand, during clock gating, the activation signal should be low whenever a self-loop appears. For this reason, we have used a NOT gate to generate the activation signal for clock gating. The inverted activation signal is now passed through a AND gate, whose other input is the clock signal. This generates the gated clock signal, which is fed to the external register.

One important thing to note here is that the gating is being implemented only for the TILE implementing the next state. The output TILE is not being gated. This is because, in several FSMs, there may arrive a situation where even during self-loops the output changes. The TILE architecture displaying the proposed gating logic in the next state function of the FSM EXCKT is shown in the Fig. 1.9.

The proposed architecture has successfully resulted in the total power reduction of the TILE with a minimal increase in delay. One of the limitations of our approach is the excess area overhead due to the introduction of new circuit elements

Fig. 1.9 Proposed power and clock gating in a TILE

for gating. However, by appropriately sizing the transistors in the activation function circuit, a proper trade-off between area and power can be maintained.

#### 1.5 Results

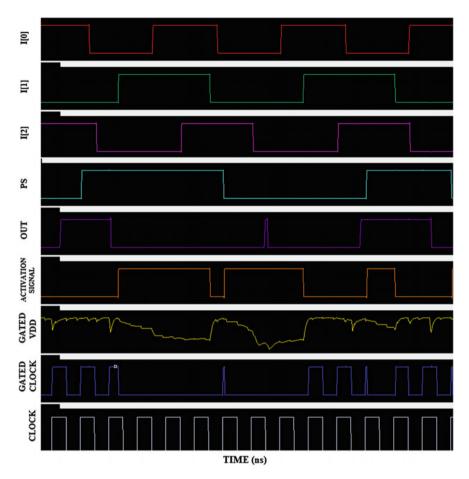

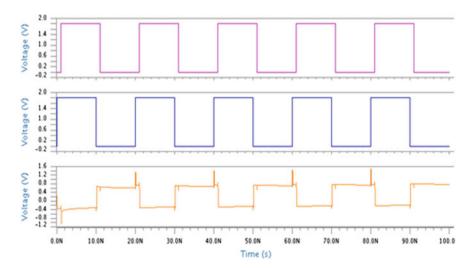

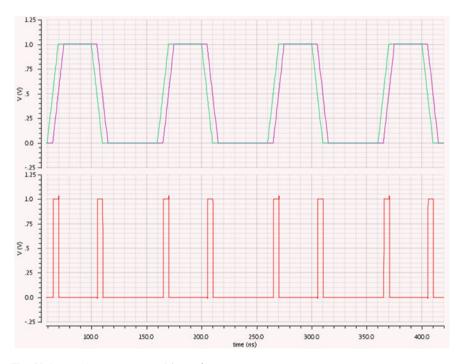

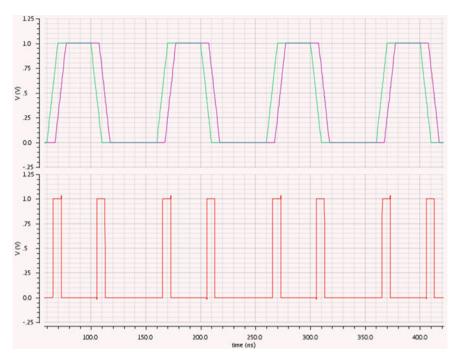

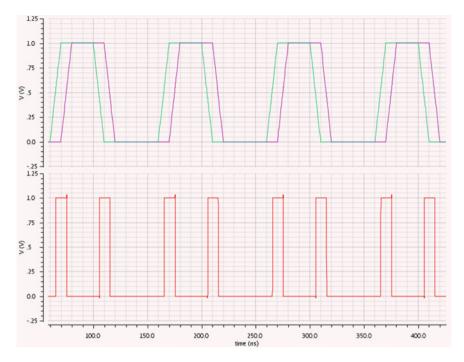

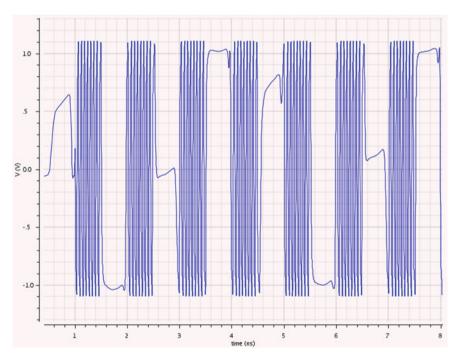

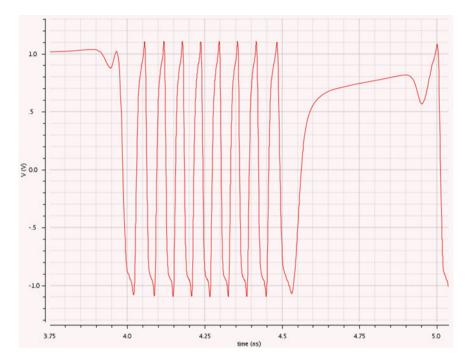

The power analysis and delay analysis of the TILE are presented in this section. The simulation of the TILEs has been carried out in CADENCE tool, using a technology of 45 nm and power supply (VDD) of 1 V. The simulation waveform of the TILEs implementing the gated FSM circuit EXCKT is shown in the following Fig. 1.10.

The power, delay, and area analyses for both with power and clock gating (PCG) and without power and clock gating (WPCG) for the circuit EXCKT are shown in the Table 1.3.

Here, "k" is the width of a minimum width transistor and " $\lambda$ " stands for the feature size of the concerned technology. The power results in Table 1.3 show a reduction of approximately 19% of the total power dissipation of the TILEs after gating. This number is, however, likely to increase as the number of self-loops in a FSM increases. However, power and clock gating results in an increase in delay due to the wake up time associated with the logic block for power supply adjustments as

Fig. 1.10 Simulation waveform of gated EXCKT

Table 1.3

WPCG (without power and clock gating) and PCG (power and clock gating) results for "EXCKT"

|      | Power (uW) | Delay (ps) | Area $(\lambda^2)$ |

|------|------------|------------|--------------------|

| WPCG | 17.81      | 187.9      | 1284 k             |

| PCG  | 14.49      | 189.9      | 1332 k             |

well as for the introduction of new circuit elements. The increase in area after gating is only 3.7%.

The proposed gating technique in our work works at a fine level of granularity, considering power reduction of an individual TILE. Majority of the previous works in this field considered coarse-level power reduction, shutting down the activity of some portion of the FPGA at a time. Power reduction in individual TILE level can

also result in significant power savings of a practical FPGA, which consists of several thousands of TILEs.

#### 1.6 Conclusion

In this work, an efficient and autonomous power and clock gating technique is being proposed and analyzed in a transistor-level TILE architecture, designed and developed in CADENCE tool, using a technology of 45 nm. FPGA, being a regular architecture, is divided into TILEs, where each TILE compromises of a logic element and routing resources. Using an array of rows and columns of the TILEs, an entire FPGA architecture can be established. The prototype designed in this work results in correct functionality and resembles the working principle of an actual TILE. The gating logic implemented in this work is based on the knowledge of self-loops in a finite state machine and works at a fine level of granularity. The results show a reduction of approximately 19% of the total power dissipation of the TILE after implementing power and clock gating with a minimal increase in delay and area. Our proposed gating method has proven to be effective and can be generally implemented to any FSMs with sufficient self-loops. In an extension to this work, we are focusing on introducing the proposed gating logic in a larger module consisting of multiple TILEs.

Acknowledgments This work was supported by Fast Track Project (Ref. No. SB/FTP/ETA-341/2012) sponsored by Science and Engineering Research Board (SERB), Department of Science and Technology (DST), Govt. of India, New Delhi—110016.

#### Reference

- "40-nm FPGA Power Management and Advantages", Link: http://www.altera.com/literature/ wp/wp-01059-stratix-iv-40nm-power-management.pdf

- Smith AM, Constantinides GA, Cheung PYK (2010) FPGA architecture optimization using geometric programming. Comput-Aided Des Integr Circ Syst IEEE Trans 29(8):1163–1176

- Kapre N, DeHon A (2009) Accelerating SPICE model-evaluation using FPGAs. In 17th IEEE Symposium on Field Programmable Custom Computing Machines, pp 37–44

- Henzler S (2007) Power management of digital circuits in deep sub-micron CMOS technologies. Springer, Berlin Springer Series in Advanced Microelectronics, Secaucus, NJ, USA

- Lin Y, Li F, He L (2005) Routing track duplication with fine-grained power-gating for FPGA interconnect power reduction. In Proceedings of the 2005 Asia and South Pacific design automation conference, 2005, pp 645–650

- Gayasen A, Tsai Y, Vijaykrishnan N, Kandemir M, Irwin MJ, Tuan T (2004) Reducing leakage energy in FPGAs using region-constrained placement. In Proceedings of the 12th ACM/SIGDA international symposium on field-programmable gate arrays, 2004, pp 51–58

- Bsoul AAM, Wilton SJE (2010) An FPGA architecture supporting dynamically controlled power gating. In International conference on field-programmable technology (FPT), pp 1–8

- Dev MP, Baghel D, Pandey B, Pattanaik M (2013) Clock gated low power sequential circuit design. In IEEE Conference on Information & Communication Technologies (ICT), 2013, pp 440–444

- Kuo YM, Weng SH, Chang SC (2008) A novel sequential circuit optimization with clock gating logic. In International conference on Computer-Aided Design, ICCAD 2008, IEEE/ACM, pp 230–233

- 10. Man X, Kimura S (2011) Comparison of optimized multi-stage clock gating with structural gating approach. In IEEE Region 10 conference on TENCON 2011, pp 651–656

- Li F, Chen D, He L, Cong J (2003) Architecture evaluation for power-efficient FPGAs. In Proceedings of the 2003 ACM/SIGDA eleventh international symposium on field programmable gate arrays, pp 175–184

- 12. Poon KKW, Yan A, Wilton SJE (2002) Flexible power model for FPGAs. 12th Int Conf Field-Program Logic Appl 2438:312–321

- 13. Fort B, Paladino D, Plavec F (2004) Full custom layout of an SRAM-based FPGA. University of Toronto, Toronto

- 14. Nag A, Pradhan S (2014) An efficient clock gating approach based on registers splitting. In International conference on VLSI and signal processing (ICVSP). IIT Kharagpur

## Chapter 2 A Hardware Implementation of Evolvable Embedded System for Combinational Logic Circuits Using Virtex 6 FPGA

C. Ranjith and S.P. Joy Vasantha Rani

#### 2.1 Introduction

The traditional method of designing digital systems was in the form of schematic or programming by hardware description languages (HDL). The above two methods require an in-depth analysis of the system under design. The manual design through schematic or programming can be sometimes complex and may lead to monotonous solutions. Another, novel method of circuit design is by evolvable hardware, wherein the circuits is evolved automatically based on some optimisation algorithm. The mode of digital design is now getting due importance from the research community and the industry. Research in this field received a boom with major chip industries innovating novel tools and chips for the application and testing of "evolvable" circuits.

Evolvable hardware (EHW) was a term coined by Hugo De Garis in the year 1992 for circuits which could configure its own hardware structure dynamically depending on the changes in the environment or on design parameters [1]. This capability of configuring the hardware was achieved by employing efficient search algorithms, like genetic algorithms (GA) [2, 3]. Evolvable systems for digital domain are mainly designed using field programmable gate array (FPGA) chips. FPGA-based EHW can be classified based on the evaluation of the solutions. The first method is recognized as *extrinsic evolution*, where the development of circuits uses a simulation approach of determining the best evaluation; such solutions are then implemented in the device. The second approach is *intrinsic evolution*, where

C. Ranjith (🖂) · S.P. Joy Vasantha Rani

Electronics Engineering Department, M.I.T. Campus, Anna University, Chennai, Tamil Nadu, India e-mail: ranjith.kmct@gmail.com

S.P. Joy Vasantha Rani e-mail: joy\_mit@annauniv.edu

© Springer Nature Singapore Pte Ltd. 2017

V. Nath (ed.), Proceedings of the International Conference on Nano-electronics, Circuits & Communication Systems, Lecture Notes in Electrical Engineering 403, DOI 10.1007/978-981-10-2999-8\_2

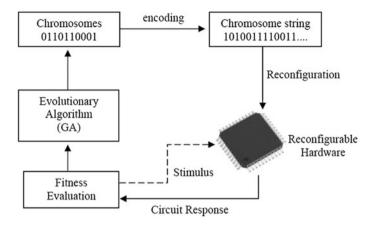

Fig. 2.1 Basic structure of EHW

each candidate solution is physically tested on the hardware device. The latter offers better accuracy and operation of self-evolved circuits [4]. The basic concept of the combination of GAs with FPGA in EHW is with regard that the configuration bit strings to the FPGA is chromosomes of the GA. The fitness function is designed, such that the GA can autonomously find the best hardware for the design to be implemented in the FPGA. Figure 2.1 depicts a simple example of the EHW concept [5]. In conventional works on EHW, the GA operations were conducted in computer or workstations, which would make the system robust and slow. In recent works, the GA operation is performed on the same FPGA chip either by hardware or by software in a dedicated core.

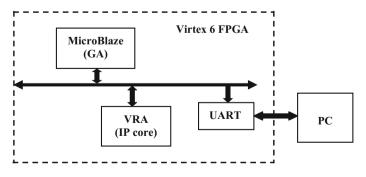

This paper describes the implementation of the evolvable embedded system which uses the evolutionary algorithm to dynamically modify some of the system components or parameters in order to adapt to the changing environment [2]. The use of a soft processor (MicroBlaze) for computing the optimal search algorithm (GA) and hardware architecture for evolution are integrated in a single FPGA, therefore termed *evolvable embedded system*. An evolvable embedded system architecture of combinational circuits using the intrinsic mode of evolution is discussed. The hardware was changed based on the fitness evaluation of the GA. The evolvable embedded hardware architecture was implemented on Virtex 6 (XC6VLX240T-1FFG1156) ML605 Evaluation Kit. Combinational circuits with 8 inputs and outputs could be evolved in this architecture with GA results displayed onto a PC. A 2-bit adder and multiplier circuits were evolved as an example using this architecture.

The paper is organized as follows: Section 2.2 describes the structure of EHW system, with Sect. 2.3 giving a complete view of the modeled system and its design. Section 2.4 describes the specifications and implementation process. Section 2.5 analyses the results, and final conclusion of the paper is discussed in brief.

#### 2.2 Structure of Evolvable Embedded System

The architecture of the EHW uses the concept of the virtual reconfigurable architecture (VRA) [6]. A hardware description of the architecture was layered over the reconfigurable chip, to implement the evolutionary structure. The GA program was fused in the MicroBlaze soft processor where the computed fitness measure was displayed on the PC through a configured UART peripheral. The complete structure is as shown in Fig. 2.2.

#### 2.2.1 Study of VRA

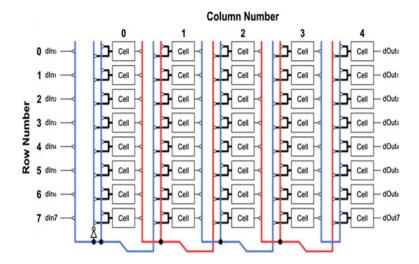

VRA is modeled in HDL and is taken as a second reconfigurable layer on the FPGA. The primary advantage of this concept is to provide a simple and efficient mode of intrinsic evolution [6]. Figure 2.3 shows the VRA structure implemented for the design of evolvable combinational circuits. An array of HDL-defined, configurable cells are arranged in rows and columns, where each cell's input is connected to the outputs of the two previous columns with the exception of the first-array column which is connected to the inputs and its invert as shown in Fig. 2.3. The number of rows and columns selected depends on the complexity of the problem. Configuration bits from the GA provide the connectivity and logic based on the 16-bit input combinations to the cell. The outputs are checked for problem logic (truth table conditions) to determine the fitness criteria. The VRA approach is widely employed in the implementation of EHW systems as the configuration bit formats of the FPGA are company proprietary. The VRA concept is similar to the Cartesian genetic programming (CGP) and provides other benefits, including (1) array of configuration cells directly connected to the hardware of the GA in the same FPGA, making the communication faster; (2) the VRA is modeled as an HDL source code which makes it easier to modify and synthesize in other

Fig. 2.2 Structure of evolvable embedded system

Fig. 2.3 An  $8 \times 5$  VRA structure

target platforms; and (3) The VRA architecture modeled can be utilized for similar set of problem definitions.

#### 2.2.2 Genetic Algorithm Flow

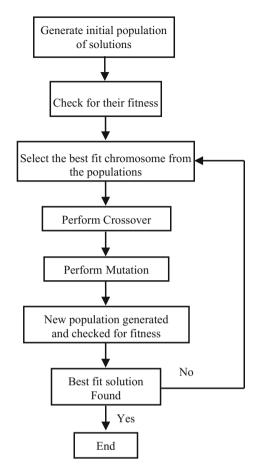

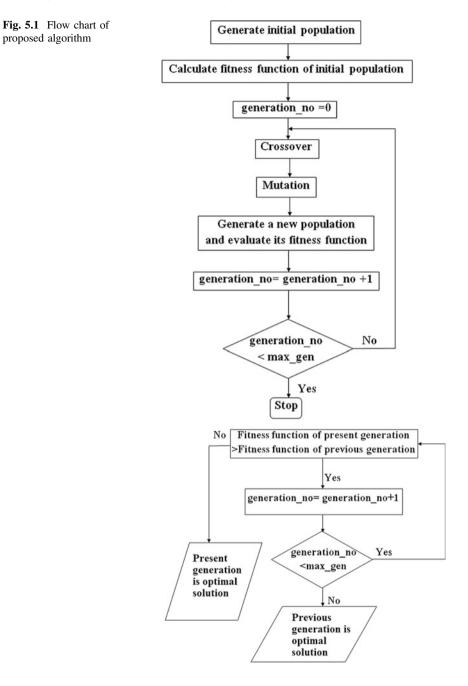

In this paper, we make use of a simple GA to search for the best solution [7]. The algorithm runs on the principle of population size of individuals (candidate) solutions to the optimization problem. These individuals consist of a string (chromosomes) of genes (genotype). The genotype is encoded to produce the configuration set (phenotype). The operations of GA include selection, reproduction, crossover, and mutation on the individuals to get a better solution [3]. The initial step is to prepare a chromosome format for the given problem, the length of which corresponds to the total number of decision variables in the search. Each of these chromosomes is passed on their fitness probability and the best fit chromosomes are selected. The best chromosome strings from the pool of populations undergoes genetic operations like crossover, mutation, and selection. New populations are generated at each iteration and checked for their fitness to produce new solutions. The cycle repeats till an optimized and best solution is found. The complete flow diagram of GA process is shown in Fig. 2.4.

Fig. 2.4 Flow graph of simple GA structure

#### 2.2.3 Reconfigurable FPGA Chip

The evolvable embedded architecture is implemented on a ML605 Evaluation board with Virtex 6 FPGA. The Virtex-6 family is built on a 40-nm process for high computational electronic systems. This series of FPGAs have integrated features that include DSP blocks, PCI-Express controllers, Ethernet MAC blocks, and high-speed transceivers [8]. The use of Virtex 6 FPGA was mandatory due to simple and flexible implementation of a 32-bit soft core MicroBlaze processor [9]. This processor computes the GA, therefore faster evaluation time can be achieved. The main advantage is that the complete EHW process can be implemented on a single chip, thereby making area efficient and flexible.

#### 2.3 Evolvable Embedded System Design

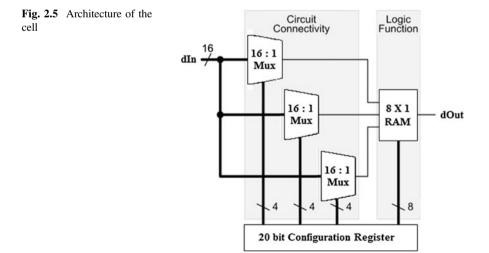

This section gives an overall view of the complete evolvable embedded system design. The VRA architecture of combinational circuits is modeled and coded by a hardware description language. The architecture of the VRA is modeled as shown in Fig. 2.5. The heart of the architecture unit is named as configuration cell, consisting of three 16:1 multiplexers and an  $8 \times 1$  bit RAM. This unit offers logical function and interconnectivity for the system under design. Three multiplexers are used to select the inputs to the lookup table (LUT), which are driven from one of the set of sixteen inputs. The configuration cell is driven by 20 configuration bits (3 \* 4 select lines of MUX + 8 selectable lines to RAM). The configuration cells are interconnected in 'm' rows and 'n' columns to form a Cell Array. A simple interconnection principle is followed where each cell input is connected to the output of the two columns, except for the first cell array column, which are connected by the inputs and its invert. This interconnection principle simplifies the cell-to-cell routing. For the design, an  $8 \times 5$  cell array was selected, with a prospect of evolving simple combinational circuits with a maximum of 8 inputs and outputs. Here, a 400 configuration bits (40 cells \* 20 configuration bits) were required to perform the complete logical functions and interconnection between cells. The configuration bits are provided by the GA taking the fitness function criteria. A reconfigurable hardware is tested using a hardware setup of simple logical gates to check the functionality of the design.

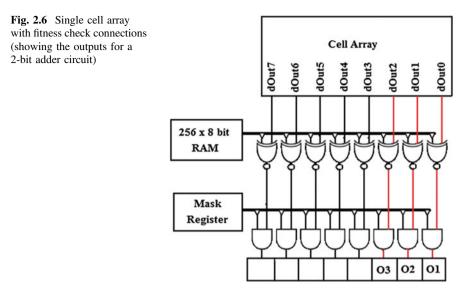

The major advantage of performing fitness evaluations in hardware was that multiple evaluations in parallel could be achieved easily. In this design, we have combined 8 cell arrays into a single block. The block contains extra circuitry to help determine the fitness of an individual. Figure 2.6 shows one such cell array with the additional circuits to perform a fitness evaluation. The RAM is used to store the

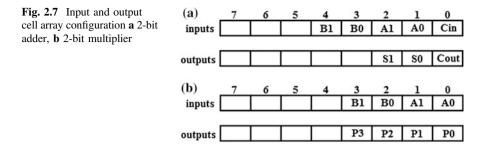

truth table of the target circuit (in this case, a 2-bit adder/multiplier). The output bits of the cell array after configuration bit selection are compared with the correct values of the 8-bit RAM outputs, using XNOR gate (last 3 bits are the truth table entries of Cout, S0, S1 for a 2-bit adder), and final values are masked by keeping one input of AND gate to high depending on the number of outputs of the evolved circuit. Match outputs are obtained (O1, O2, O3) as shown for a 2-bit adder circuit. Here, O1, O2, O3 symbolizes Cout, S0, S1 of a two-input adder. The same could be employed for a 2-bit multiplier where 4 outputs are valid, so the last 4 AND gates input are held high.

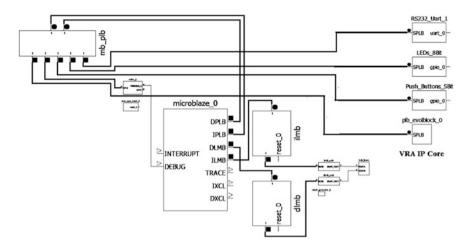

The evolutionary system was developed using Xilinx Platform Studio (XPS) tool. An embedded system with both hardware and software elements was created in the EDK (Embedded Development Kit) and SDK (Software Development Kit), respectively; a 32-bit MicroBlaze soft core processor (for performing the GA) with a clock frequency of 50 MHz and an 8-cell array VRA core structure (for evaluating candidate solutions). The system also includes a configured serial UART (universal asynchronous receiver/transmitter) to send GA computations to the PC. The cell array VRA block was imported as an IP core (intellectual property) and integrated as a peripheral to the Microblaze processor. The IP core was plugged into the processor bus using the generated macros in situ with an interface program [9]. The system netlist (ngc files) and bitstream (bit files) are generated from the EDK. The C program for the GA optimization was hand-coded, encoding the inputs and outputs of the cell array. The input and output cell array configuration for a 2-bit adder and 2-bit multiplier is as shown Fig. 2.7a, b. The GA parameters such as crossover rate, mutation rate, and number of selections are assigned by trial and error. The evaluation is based upon minimum iterations to converge to a better fit for the optimization of the circuit. The program calls for

additional header files, to hold parameters required to communicate the application program with the devices to the embedded system. This application program creates an executable and linkable format file (elf file) for the program to be realized by the FPGA. This file along with the bit file is integrated to be programmed into the FPGA (ML605) through a JTAG cable.

#### 2.4 Implementation

The VRA architecture was coded in VHDL and synthesized in Xilinx ISE Design Suite 14.6. An inbuilt MicroBlaze soft processor having 32 bit, Reduced Instruction Set Computer (RISC) architecture is utilized for modeling the system [9]. The MicroBlaze processor with its peripherals for the design include UART (for communication with PC), 4 seven-segment LEDs, push buttons for inputs and reset options, realized from XPS 14.6 EDK platform tool. The peripherals are linked to the processor via the processor local bus (PLB). The synthesized VRA module files are exported to realize as a user IP core. This IP core is connected to the processor via the PLB. The generated macros are modified to interconnect the user IP core to the PLB bus. The complete embedded processor structure with its peripherals realized as block schematic is presented in Fig. 2.8. The microprocessor hardware specification file (mhs file) and peripheral analysis order file (pao file) has to be updated to include the changes accommodated by the addition of new IP core, along with the creation of black box definition file (bbd file). Once the following peripherals are connected, new netlist files (system.ngc) and bit files (system.bit) are generated.

The hardware system created in EDK is exported to SDK tool to develop the GA program to operate in association with the hardware. A simple GA program with

Fig. 2.8 MicroBlaze processor with peripheral interconnections (viewed through XPS tool)

optimization for the evolution of circuits is coded in C language. The GA program is developed with the following subroutines:

- (i) The truth table of the target circuit to be stored in the  $256 \times 8$  bit RAM. Here, 2-bit adder/multiplier truth tables are initially stored occupying the first 16 locations of the RAM, whereas the rest is default taken to be nil.

- (ii) Configure the input and output registers of the cell array with the bit placing as shown in Fig. 2.7a, b. For a 2-bit adder, the first 5 bits of the input register represent the 2-bit input, and a carry (Cin, A0, A1, B0, B1), whereas the first 3 bits of output register represent the outputs (C0, S0, S1) of the 2-bit adder circuit. Similar logic holds for a 2-bit multiplier, having of 4 inputs (A0, A1, B0, and B1) and generating 4 outputs (P0, P1, P2, and P3).

- (iii) A simple GA program to find a best fit configuration is to be applied to the cell. The fitness function is the truth table of the 2-bit adder/multiplier circuit. The fitness function can be calculated as:

fitness =

$$2^i$$

, where  $i$  = inputs of the system (2.1)

From the criteria, the fitness of the 2-bit adder circuit is summed to 96 (sum of the fitness of C0, S0, S1), and that of 2-bit multiplier to be 64. The GA program is developed and tested for the following parameters:

No. of iterations: 500 Population size: 128 with 16 sets of population for each cell array (8 cell arrays in parallel) Crossover rate: 55% Mutation rate: 0.1% Selection method: Tournament selection.

The GA program communicates with the devices of the embedded system through the header files provided by the vendor. Two header files, namely *xpa*-*rameters.h* and *xgpio.h*, holding parameters for the communication are added to the application program. The *.elf* file (software) from the SDK and the *system.bit* file (hardware) from the EDK are combined to the Virtex 6 FPGA (XC6VLX240T-1FFG1156). The combinations of these two files integrate to form *download.bit*. This bit files are used to program the FPGA through the JTAG cable.

# 2.5 Results

The results are monitored on a PC connected through the UART peripheral. The results display the GA program evaluating the fitness calculations for a 2-bit adder/multiplier circuits. The program is terminated once the fitness is evaluated and displays the number of generations and configurations for each cell array as shown in Fig. 2.9a, b for 2-bit adder and multiplier, respectively. From the results, it can be analyzed that a 2-bit adder was evolved over 88 generations, and 135 generations were required to evolve a 2-bit multiplier. The number of generations differs with the number of inputs and outputs of the system. The experiments were repeated for different values of crossover rate, mutation rate, and selection criteria.

Optimized results were obtained for crossover rate = 55%, mutation rate = 0.1%, and tournament selection of 5 individuals at a time. The hardware interconnections could be analyzed from the configurations of the individual cells. The complete floor plan of the evolvable embedded system for the combinational circuit using the VRA concept is shown in Fig. 2.10 using the PlanAhead tool. From the figure, it can be seen that around 40% of the implemented chip area were occupied by the MicroBlaze processor and its peripherals and the rest, by the VRA IP core. From the total chip area, around 6% of LUTs, 4% IOBs and 3% of registers were used from the available resources as tabulated in Table 2.1. The timing criteria were met with an implementation time of 17.063 ns (maximum frequency of 58.606 MHz).

| Image: C/C++ - Xilinx SDK         File Edit Source Refactor Navigate Search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help         Image: Comparison of the search Run Project Xilinx Tools Window Help <tr< th=""><th></th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Image: Second |       |

| Problems 🕢 Tasks 🖾 Console 🖾 Properties 🖾 Console 🖨 Problem Details 🔊 Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| Serial: (COM3, 9600, 8, 1, Even, None - CONNECTED) - Encoding: (UTF-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 🖾   |

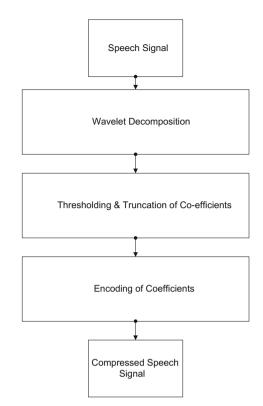

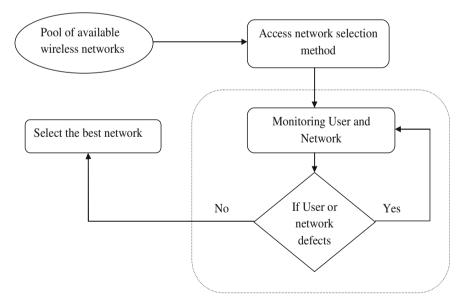

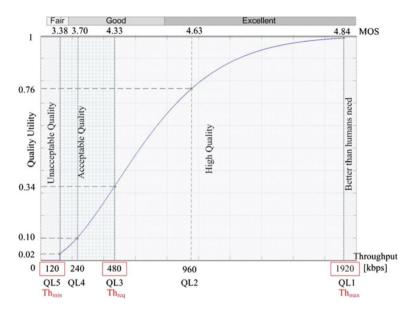

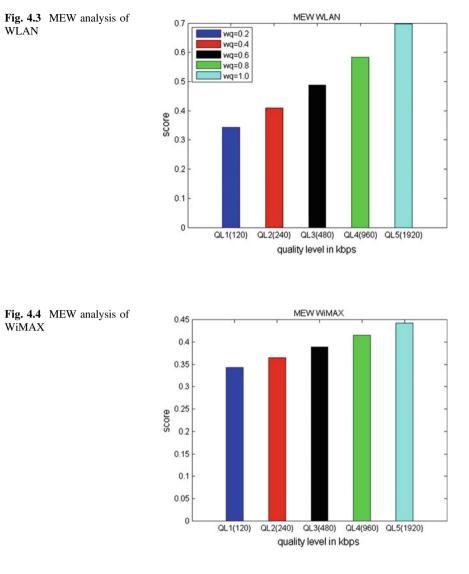

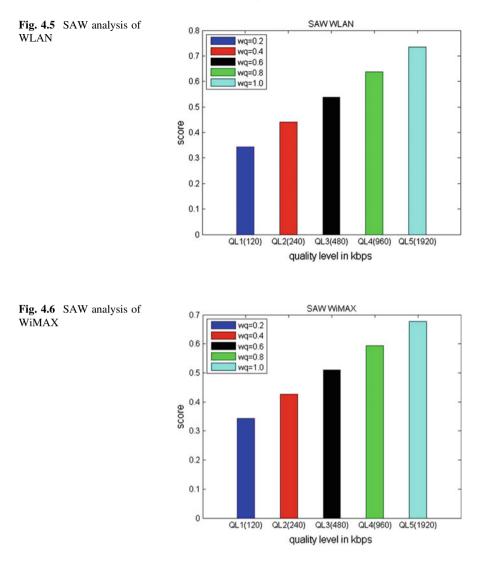

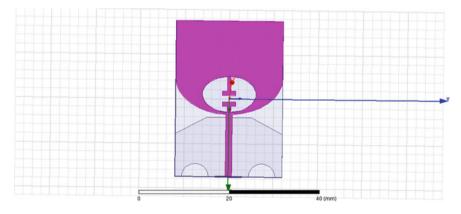

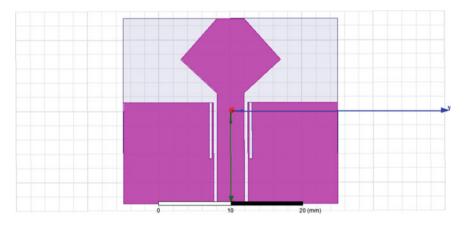

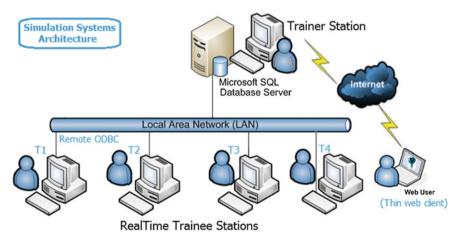

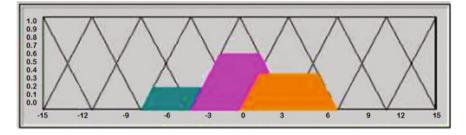

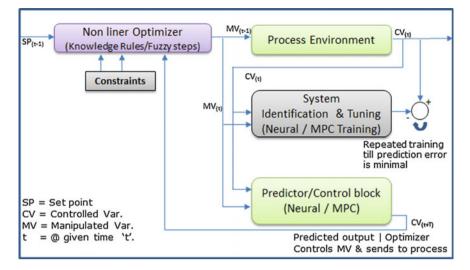

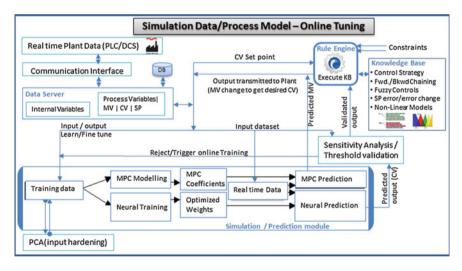

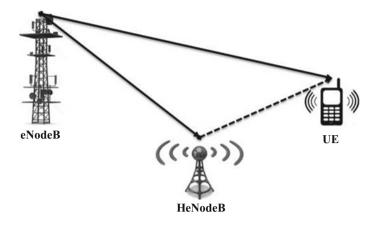

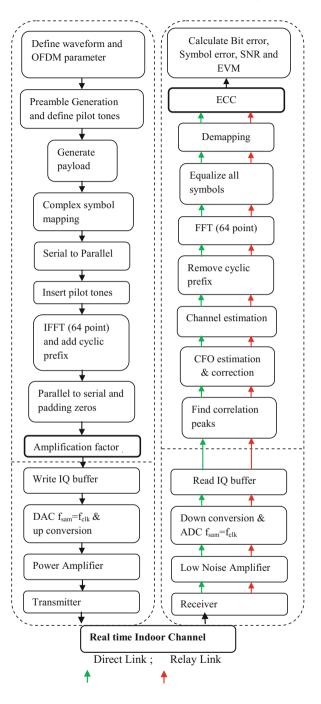

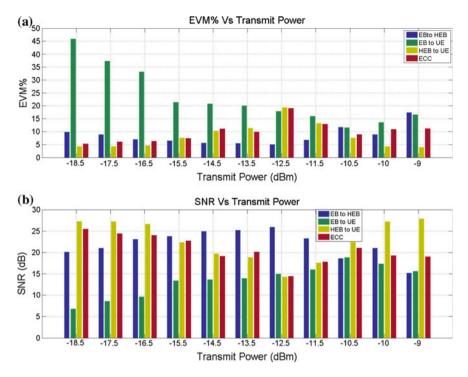

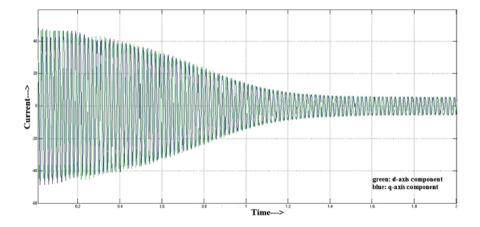

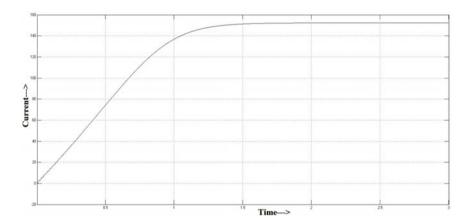

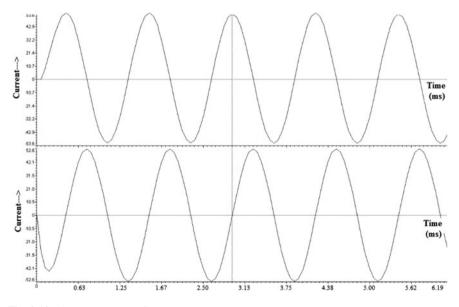

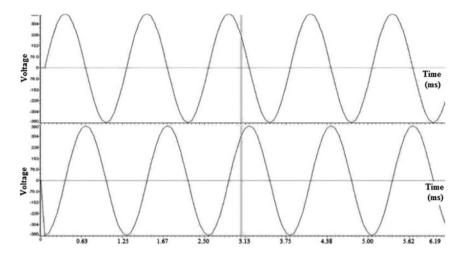

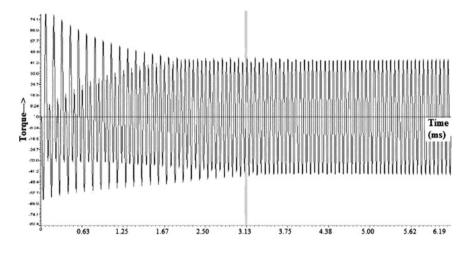

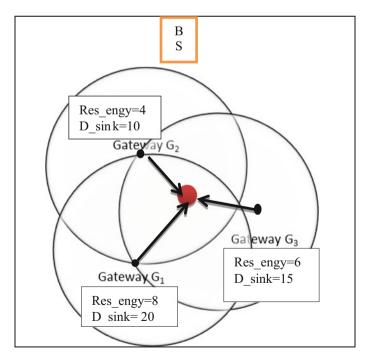

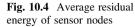

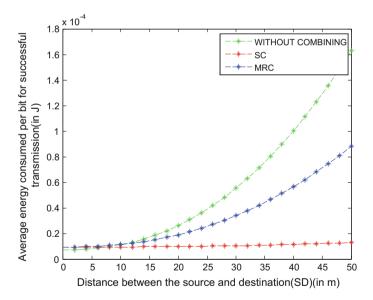

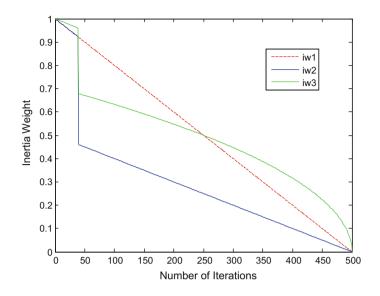

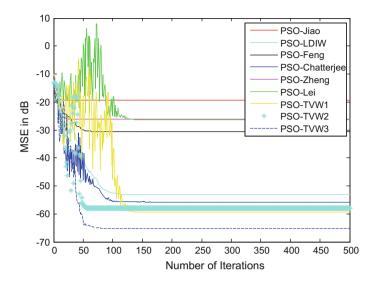

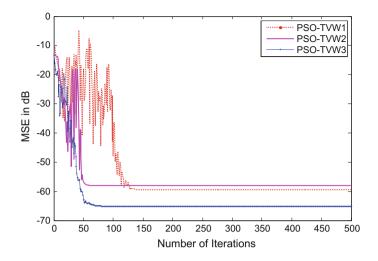

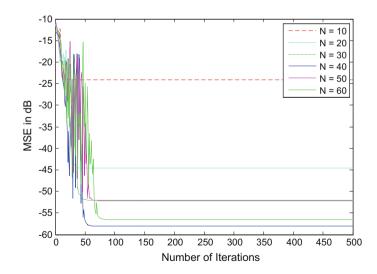

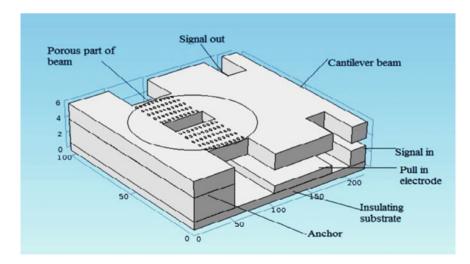

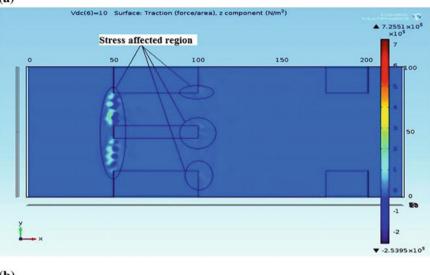

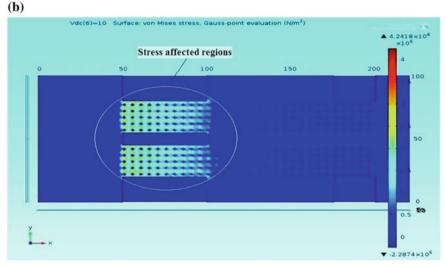

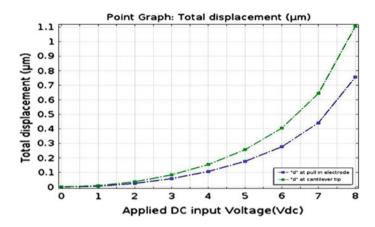

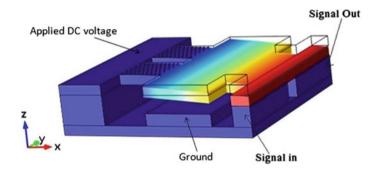

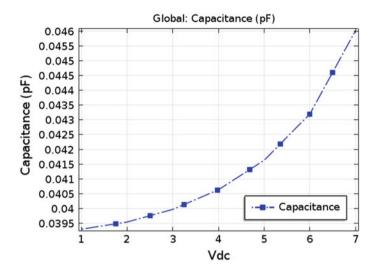

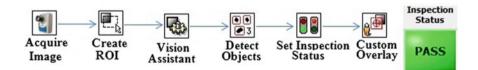

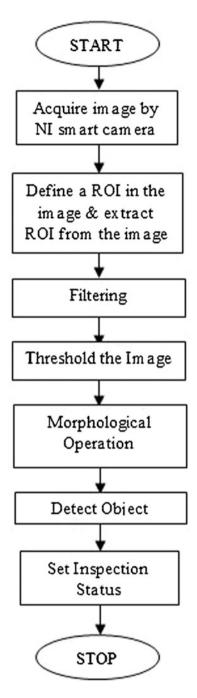

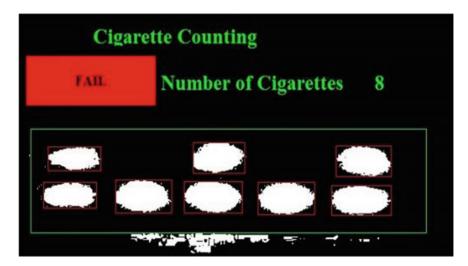

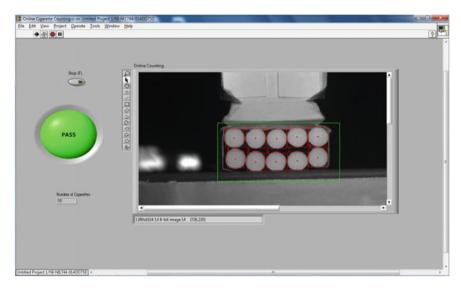

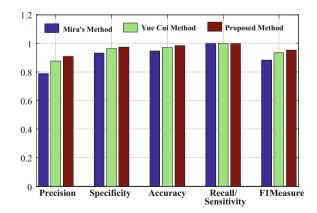

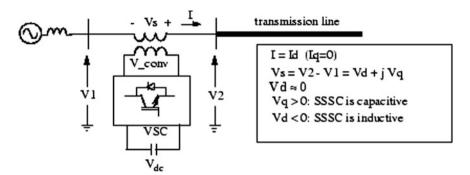

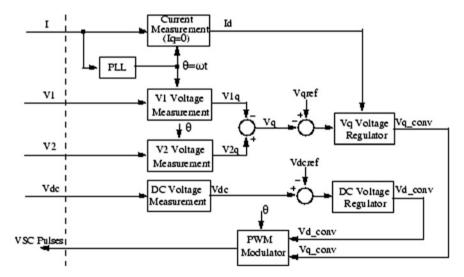

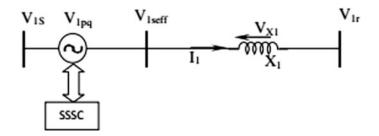

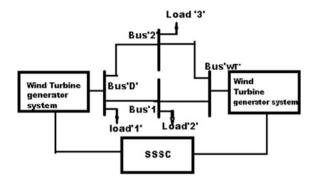

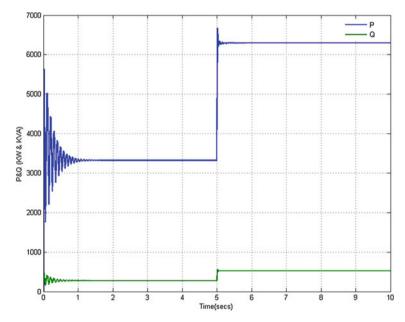

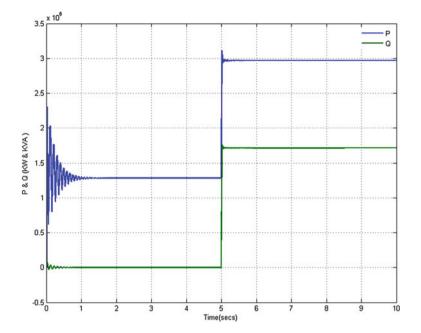

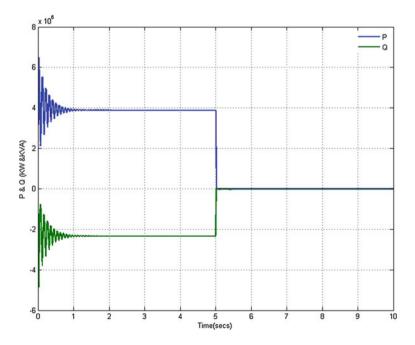

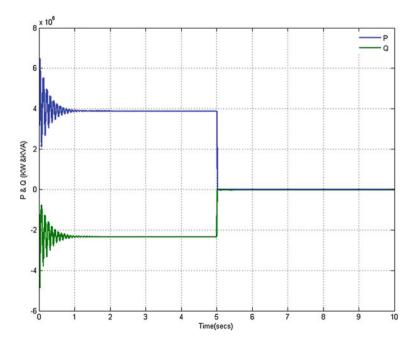

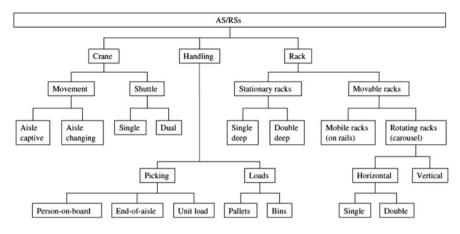

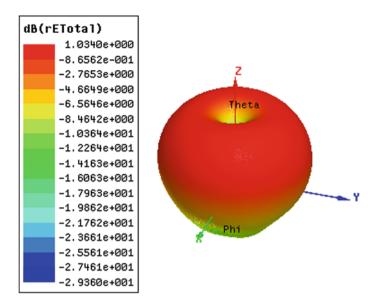

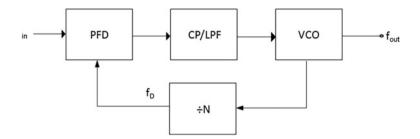

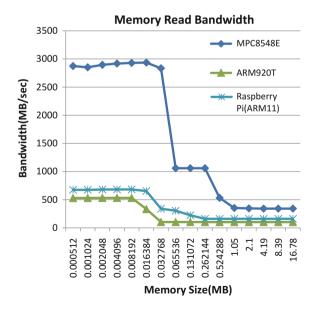

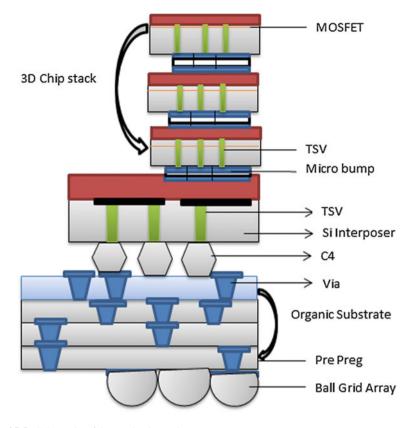

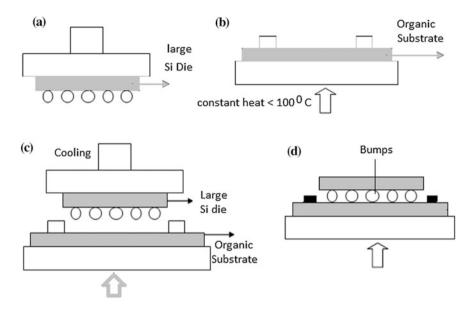

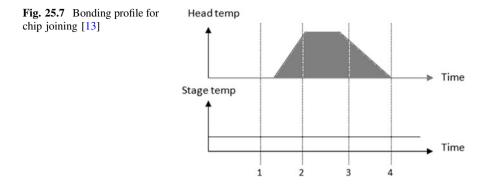

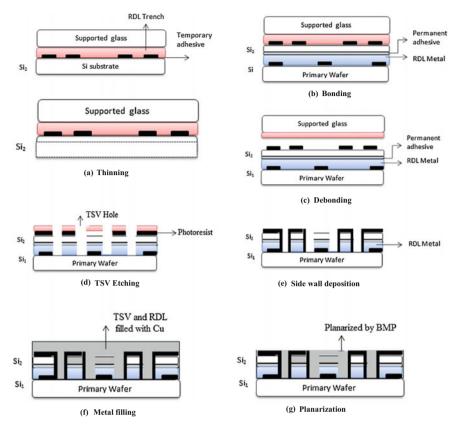

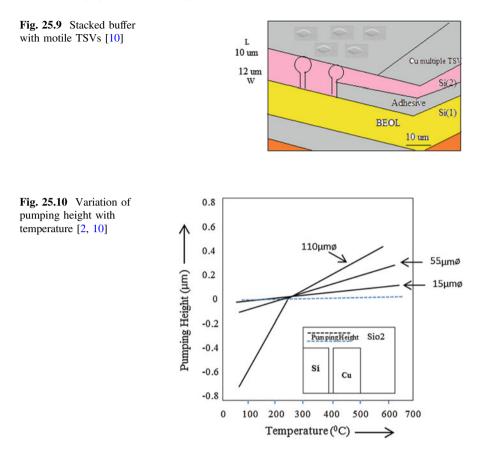

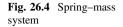

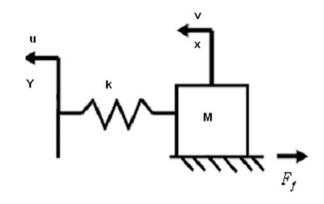

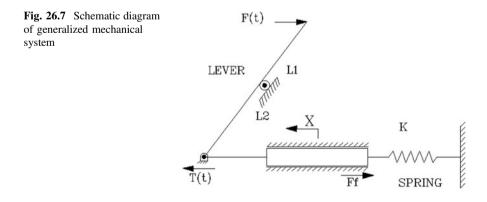

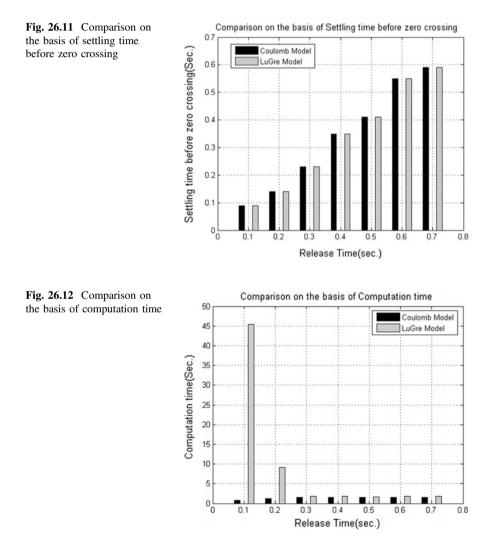

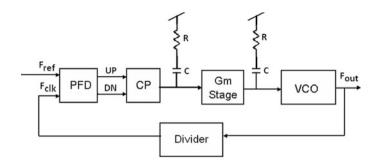

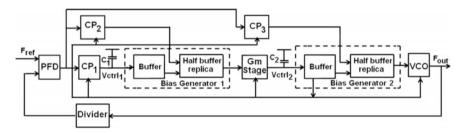

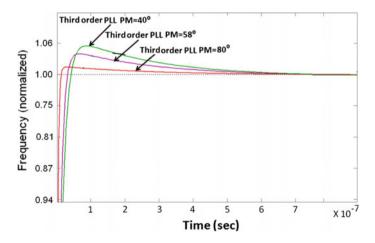

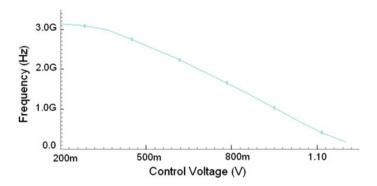

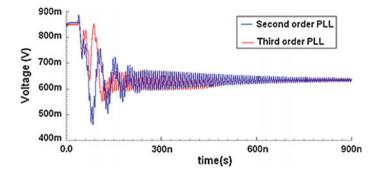

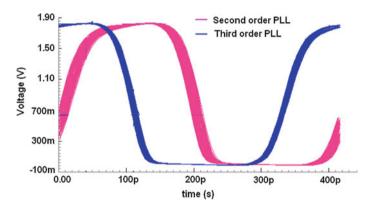

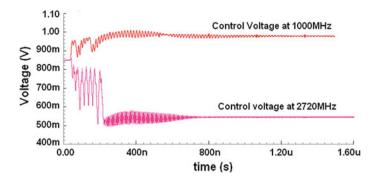

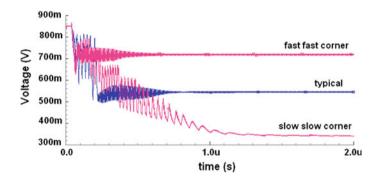

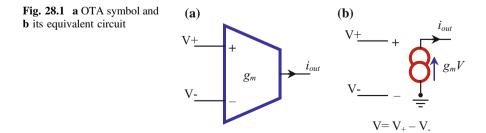

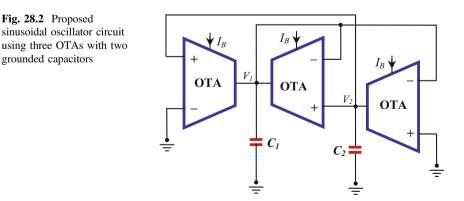

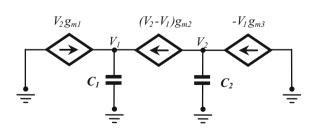

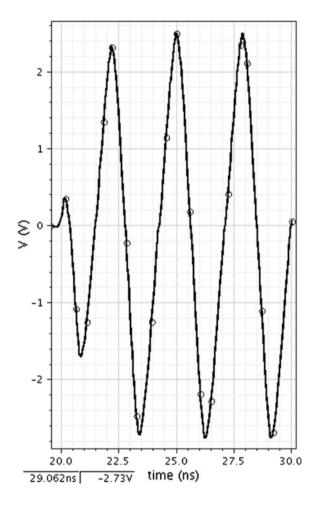

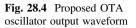

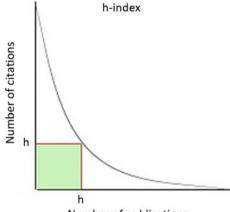

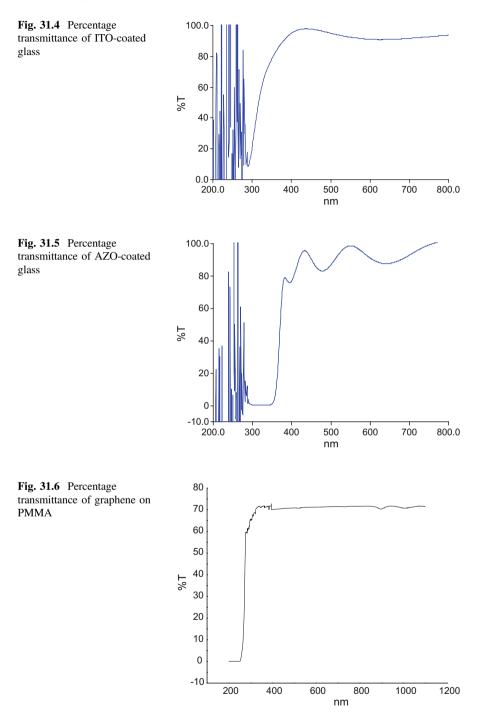

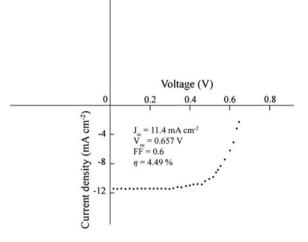

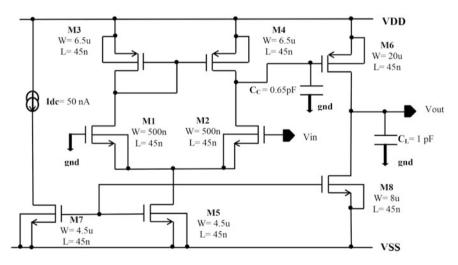

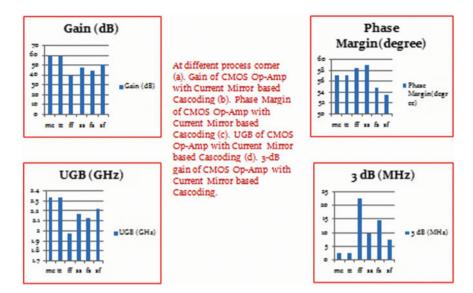

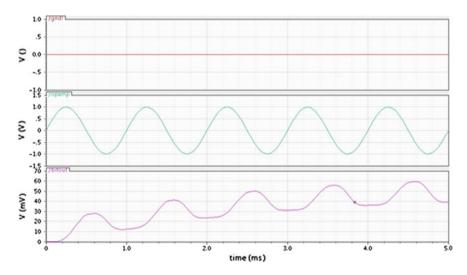

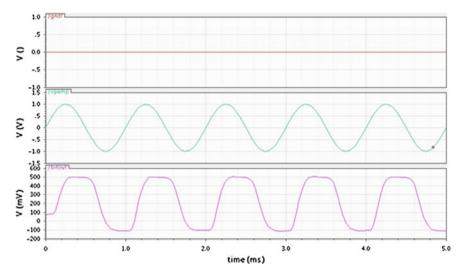

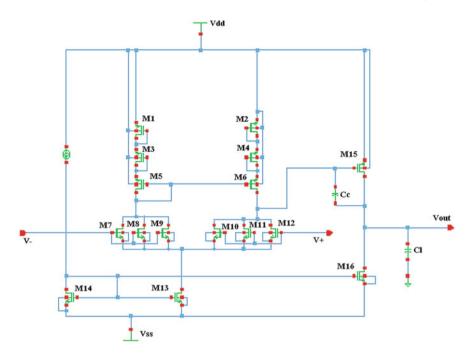

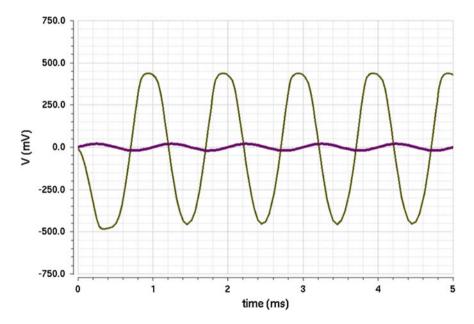

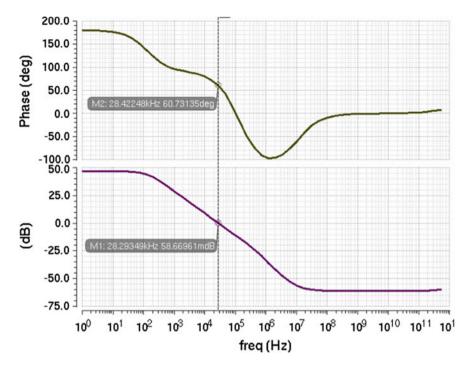

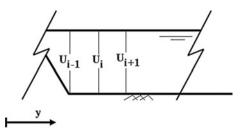

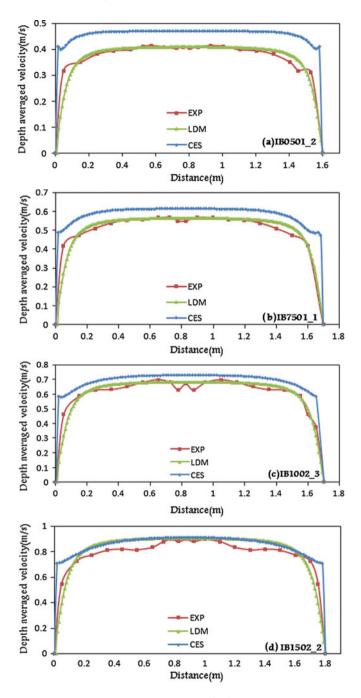

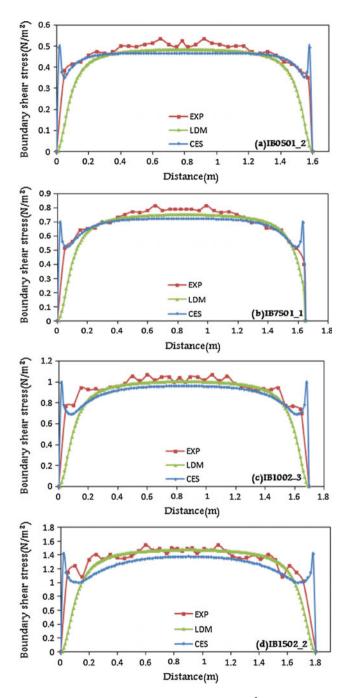

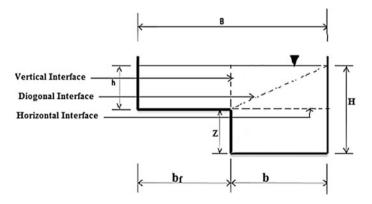

| Serial: (COM3, 9600, 8, 1, Even, None - CONNECTED) - Encoding: (UTF-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.00  |