# Modeling Hardware/Software Embedded Systems with UML/MARTE: A Single-Source Design Approach

## Fernando Herrera, Julio Medina, and Eugenio Villar

## Abstract

Model-based design has shown to be a powerful approach for embedded software systems. The Unified Modeling Language (UML) provides a standard, graphically based formalism for capturing system models. The standard Modeling and Analysis of Real-Time Embedded Systems (MARTE) profile provides syntactical and semantical extensions required for the modeling and HW/SW codesign of real-time and embedded systems. However, the UML/MARTE standard is not sufficient. In addition, a modeling methodology stating how to build a model capable to support the analysis and HW/SW codesign activities of complex embedded systems is required. This chapter presents a UML/MARTE modeling methodology capable to address such analysis and design activities. A distinguishing aspect of the modeling methodology is that it supports a *single-source* design approach.

| Acronyms |                          |  |

|----------|--------------------------|--|

| BCET     | Best-Case Execution Time |  |

| BSP      | Board Support Package    |  |

| CPS      | Cyber-Physical System    |  |

| DSE      | Design Space Exploration |  |

| DSL      | Domain-Specific Language |  |

| EDF      | Earliest Deadline First  |  |

| EML      | Execution Modeling Level |  |

| ESL      | Electronic System Level  |  |

|          |                          |  |

F. Herrera • E. Villar

GESE Group, TEISA Department, ETSIIT, Universidad de Cantabria, Santander, Cantabria, Spain

e-mail: fherrera@teisa.unican.es; evillar@teisa.unican.es

J. Medina (🖂)

Software Engineering and Real-Time Group, University of Cantabria, Santander, Cantabria, Spain e-mail: medinajl@unican.es

© Springer Science+Business Media Dordrecht 2017

S. Ha, J. Teich (eds.), *Handbook of Hardware/Software Codesign*, DOI 10.1007/978-94-017-7267-9\_6

| FPGA  | Field-Programmable Gate Array                       |  |  |

|-------|-----------------------------------------------------|--|--|

| GME   | Generic Modeling Environment                        |  |  |

| HLS   | High-Level Synthesis                                |  |  |

| HRM   | Hardware Resource Modeling                          |  |  |

| HSCD  | Hardware/Software Codesign                          |  |  |

| ISA   | Instruction-Set Architecture                        |  |  |

| M2M   | Model-to-Model                                      |  |  |

| MARTE | Modeling and Analysis of Real-Time Embedded Systems |  |  |

| MCS   | Mixed-Criticality System                            |  |  |

| MDA   | Model-Driven Architecture                           |  |  |

| MPSoC | Multi-Processor System-on-Chip                      |  |  |

| NFP   | Non-Functional Property                             |  |  |

| OMG   | Object Management Group                             |  |  |

| OS    | Operating System                                    |  |  |

| PIM   | Platform Independent Model                          |  |  |

| PVT   | Programmers View Time                               |  |  |

| RR    | Round Robin                                         |  |  |

| RTOS  | Real-Time Operating System                          |  |  |

| SLS   | System-Level Synthesis                              |  |  |

| TLM   | Transaction-Level Model                             |  |  |

| UML   | Unified Modeling Language                           |  |  |

| UTP   | Universal Testing Profile                           |  |  |

| VHDL  | VHSIC Hardware Description Language                 |  |  |

| VHSIC | Very High Speed Integrated Circuit                  |  |  |

| VSL   | Value Specification Language                        |  |  |

| WCET  | Worst-Case Execution Time                           |  |  |

## Contents

| 5.1 | Introdu               | uction                                                  | 143 |

|-----|-----------------------|---------------------------------------------------------|-----|

| 5.2 | Modeling Requirements |                                                         | 144 |

|     | 5.2.1                 | Single-Source Approach                                  | 144 |

|     | 5.2.2                 | Separation of Concerns                                  | 146 |

|     | 5.2.3                 | Incremental Modeling                                    | 146 |

|     | 5.2.4                 | Component-Based Functional Modeling                     | 147 |

|     | 5.2.5                 | Support of System-Level Design Activities               | 147 |

|     | 5.2.6                 | Support of Mixed-Criticality                            | 148 |

| 5.3 | State of              | f the Art                                               | 149 |

| 5.4 | Single-               | Source Modeling Methodology                             | 151 |

|     | 5.4.1                 | Introductory Example: Quadcopter System                 | 151 |

|     | 5.4.2                 | Introduction                                            | 152 |

|     | 5.4.3                 | Platform-Independent Model                              | 154 |

|     | 5.4.4                 | Platform Resources                                      | 159 |

|     | 5.4.5                 | Platform-Specific Model                                 | 162 |

|     | 5.4.6                 | Extra-Functional Properties and Performance Constraints | 162 |

|     | 5.4.7                 | Design Space                                            | 167 |

|     | 5.4.8                 | Modeling for Software Synthesis                         | 170 |

|     |                       |                                                         |     |

|      | 5.4.9                              | Verification Environment             | 171 |  |

|------|------------------------------------|--------------------------------------|-----|--|

|      | 5.4.10                             | Mixed-Criticality                    | 172 |  |

|      | 5.4.11                             | Modeling for Schedulability Analysis | 178 |  |

| 5.5  | 5 Single-Source Design Framework 1 |                                      |     |  |

| 5.6  | 6 Conclusions                      |                                      |     |  |

| Refe | rences                             |                                      | 183 |  |

## 5.1 Introduction

Model-based design is a powerful approach for the design of complex embedded systems [27]. It can be adapted to different design contexts and domains, being compatible with methodologies like *Agile* [2]. The Unified Modeling Language (UML) supports Model-Driven Architecture (MDA) [40] and provides the following remarkable advantages:

- It is a widely spread language, known and used in different domains.

- It is an Object Management Group (OMG) standard [30].

- It provides a set of **generic modeling elements**, supported by a **graphical syntax** and a closed set of **diagrams**, which enables the capture of architectural and behavioral details.

A key of the success of UML is related to the generality of the provided modeling elements. These elements have a simple semantics that can be easily understood and interpreted by engineers of different domains. For instance, stating that a UML *port* is a mechanism to access to/from a UML *component* which hides component internals. This simple element semantics is encompassed by a simple graphical syntax, which facilitates the comprehension and adoption of UML diagrams.

UML has been also proposed for the modeling of embedded systems. Embedded systems have become complex. The increasing amount of silicon available in a single-chip enables the integration of more hardware and software functions. In close relationship, the specification and modeling tasks have become increasingly complex. Models need to reflect systems integrating multiple applications and diverse software platform components, e.g., embedded RTOS, middleware, drivers, etc. Similarly, current hardware architectures rely on multi-core processors, surrounded by many HW devices for communication, storage, sensing, and actuation. In addition, several types of analysis are applied (e.g., schedulability, timed-simulations, etc.) which require to add additional information to the model, e.g., annotations of extra-functional properties related to timing, memory sizes, energy, etc.

A solution is to build models integrating parts under different Domain-Specific Languages (DSLs). However, fragmentation into DSLs limits the understanding of the overall model (all the engineers handling the model should know all the DSLs involved) and requires an additional effort to integrate the DSLs.

In this scenario, relying on UML has the advantage of providing a common and comprehensive host language. UML lacks the semantics and specific elements required for tackling the Hardware/Software Codesign (HSCD) of complex embedded systems. However, UML enables to cover this *semantic lack* by means of a UML extension mechanism called profile. A UML profile provides *stereotypes*. Stereotypes are applied to UML modeling elements and add them additional attributes and domain-specific semantics. In fact, the OMG currently provides a rich portfolio of UML profiles oriented to different domains like telecommunication, middleware, and real time.

Among these OMG standard profiles, the Modeling and Analysis of Real-Time Embedded Systems (MARTE) profile [29] provides a rich set of modeling elements, sufficiently broad to cover HSCD of real-time and embedded systems. For instance, it supports the modeling of the hardware and software platform, of the application, of extra-functional properties, and the definition of performance and real-time analyses.

As well as the UML and the MARTE profile, a modeling methodology is required. The modeling methodology states how to use the language in order to build the model of a system. It states which information have to be captured and how it is structured and captured through the available modeling techniques, such that the model can be processed and provides all the information required by the analysis tools and processes related to the HW/SW codesign. All these aspects defining a modeling methodology have to serve to its main purposes. The main purpose of the methodology presented in this chapter is to enable the development of abstract models which can be used as a single-source for the different activities involved in electronic system-level design. The modeling methodology shall not fix a specific Electronic System Level (ESL) design flow, but it has to allow that applicable design flows can progressively enrich the model from early stages, when limited information is available, toward an enriched model which allows the implementation of an efficient, potentially optimal, solution.

Following, Sect. 5.2 presents the goals of the methodology. The section motivates how these goals turn into requirements because of the need of higher design productivity. Moreover, it precises the meaning of some of this requirements (e.g., single-source, incremental modeling) in the modeling context. Section 5.3 provides an overview of related modeling approaches, showing how they partially cover the aforementioned requirements. Then, Sect. 5.4 presents the generic UML-based modeling techniques adopted by the methodology to cover Sect. 5.2 requirements. Section 5.5 introduces, before the conclusions, a single-source design framework exploiting the presented modeling methodology.

#### 5.2 Modeling Requirements

## 5.2.1 Single-Source Approach

A model-driven design approach helps in analyzing and predicting the behavior of a system from different perspectives and for different purposes. In a *multi-source* approach, several models of the same system have to be developed, each one associated to a perspective, type of analysis, or design activity. However, relying on several models easily leads to extra modeling efforts, redundancies, inconsistencies, and traceability problems. In contrast, an advanced software development methodology like *Agile* adopts a *single-source* approach, which reduces the maintenance burden and the traceability burden and increases consistency [2].

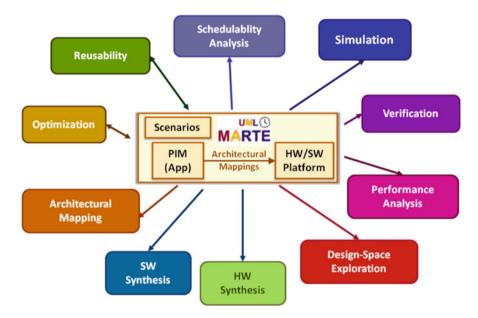

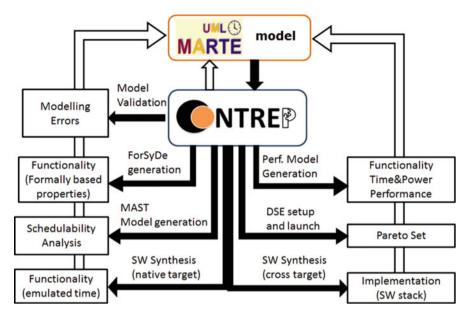

The same advantages motivate the proposal of a single-source approach for modeling and design of embedded systems [7], which is sketched in Fig. 5.1.

A single model, a UML/MARTE model in this case, captures all the information required by the many tasks involved in a modern embedded system design flow, e.g., reusability, verification, schedulability analysis, architectural mapping, simulation and performance analysis, design space exploration, etc.

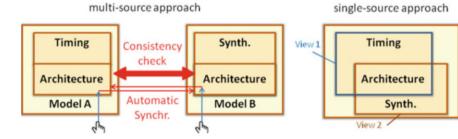

The left-hand side of Fig. 5.2 illustrates the multi-source approach, where two independent models, A and B, of an embedded system are developed.

Fig. 5.1 The MARTE model as a single-source model

Fig. 5.2 Multi-source vs. single-source approach

Model A serves for analyzing timing performance. Model B is the input for a SW synthesis process. Model A adds some timing annotations, which are not present in model B. Model B adds target information, which is not present in model A. However, both models should reflect the same architecture of the application. Therefore, a double unnecessary modeling effort has been done. A consistency check to ensure that both models A and B reflect the same architecture is required, at least after the first development of the models and specially in a context where model architectures can be edited. These problems exponentially grow with the number of independent models required (in the worst case, one per design activity shown in Fig. 5.1).

In contrast, in the single-source approach (right-hand side of Fig. 5.2), the architectural information is captured once in the model. Then, in order to capture models A and B, the model is extended twice: once for capturing the time annotations required by the A model and once more for capturing the synthesis information required by the B model. The adoption of a single-source approach is a distinctive and remarkable aspect of the shown approach. Moreover, there are other important characteristics which need to be preserved and adopted, as addressed in the following sub-sections.

#### 5.2.2 Separation of Concerns

The single-source approach centralizes the information required for the design tasks in a single model, with the advantages discussed in the previous section. The complex system model will have a big amount of information. In this context, *Separation-of-concerns* helps to provide a structure to such information. Model *Viewpoints* [22] and *Perspectives* [46] become essential for the modeling activity. Viewpoints are about defining the most relevant categories of information and about the structure the model concerning them. Perspectives are related to the model concerns, e.g., model properties or actions performed on the model, that shall be presented and can be accessed in the modeling framework. Combining perspectives and viewpoints facilitates model edition. It enables the cooperation of different modelers, which can focus on specific information of the model. It also simplifies tools and activities around it, e.g., the model navigation performed by code generators.

#### 5.2.3 Incremental Modeling

In software engineering, *incremental modeling* refers to the delivery of a series of releases called *increments* [39]. This approach enables to progressively provide more functionality on each increment. In software modeling, increments can refer to customizations, as well as to extensions [1].

In our single-source modeling context, incremental modeling refers to the possibility to start by building a first model that enables a first set of analysis and design activities, and enhance it later on. Then, further modeling increments may enable additional design activities and/or improve the results of the previously applicable activities, e.g., enabling more accuracy in the performance assessments. A model increment shall not prevent performing the design activities already enabled by previous versions of the model.

#### 5.2.4 Component-Based Functional Modeling

A software component-based approach [38] has important advantages. First, it enables to build system functionality as a composition of existing and reusable components. These components interact with each other only through well-defined interfaces [32], which declare the functional services they provide and require. Adopting a software-centric approach, i.e., assuming a default software implementation of the functionality, is also an efficient approach according to the increasing and dominant amount of software in current embedded systems.

#### 5.2.5 Support of System-Level Design Activities

Adoption of ESL design [4] is key in order to shorten the *productivity gap* [19]. ESL design tackles the productivity gap by raising the abstraction of the starting model and by introducing automated design activities around that system-level model. Two main design activities are:

- **Design Space Exploration (DSE):** consists in the activity of exploring design alternatives and selecting the optimal ones.

- System-Level Synthesis (SLS): consists in the generation of the implementation from the initial model, used as a specification. It requires the decision of the HW/SW partition and the automated generation of software, hardware, and HW/SW interfaces.

DSE can rely on SLS. For instance, [4] highlights that one of the most important benefits for High-Level Synthesis (HLS) is that it enables (hardware) design exploration. The methodology in [37] enables the automated SW synthesis from a UML/MARTE model of the binaries targeted to a multi-core heterogeneous platform. This automation is exploited for the exploration of different software implementation alternatives. The aforementioned approaches are applied after HW/SW partition.

An *explore-then-synthesise* approach relying on performance assessment techniques is also possible. Kang et al. [20] refers to DSE as the activity of exploring design alternatives *prior to implementation*. Therefore, in this approach, the exploration activity is done first on the model. Performance estimations on different model configurations, which can reflect different HW/SW partitions, serve to decide the most convenient one. Thus the system-level synthesis is only applied on that choice. In a UML/MARTE context, [13] showed how the model can reflect different mappings, comprising different HW/SW partitions. It enables the generation of a performance assessment model which, linked to a DSE tool, enabled an automated search of the Pareto solutions set.

The automation of the DSE and SLS activities is key in order to cope with the exploration of huge design spaces and in order to eliminate human errors both in the exploration and implementation steps. This has motivated the development of automated DSE, SW synthesis, and hardware HLS frameworks. The possibility to exploit these frameworks relies on the fact of enabling an input model which conjugates the abstraction required by ESL, with the information required for performing these activities. This chapter shows how it is done from a UML/MARTE model under a single-source approach.

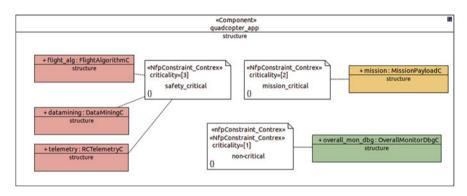

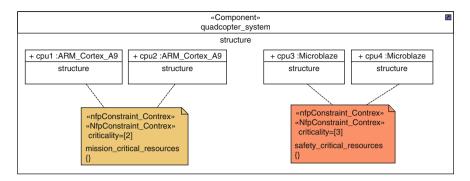

#### 5.2.6 Support of Mixed-Criticality

Mixed-Criticality System (MCS) have got an increasing interest [23]. MCS integrate applications with constraints whose fulfillment has different levels of criticality and which can share computational, memory, and communication resources. Although there is not an unanimous convey in the meaning of criticality, it has been associated to the impact of the occurrence of a failure [6]: e.g., safety critical when the failure can cause injures to humans, *mission critical* when the failure prevents the system to perform its expected behavior, but it does not compromise safety, and low critical when the impact is affordable. Safety standards associate criticalities to a set of more or less strict requirements on the development process. There are several reasons for the highest interest in mixed-criticality systems. Reusing existing functionalities and integrating them in the same chip or in the same platform is an efficient way to exploit growing integration capabilities and cost-effective platforms. However, dependability problems arise, as not all the functionalities and performance requirements are equally important. A mixed-criticality aware design methodology considers this differences. For instance, methodologies need to combine real-time analysis for the safety parts with hard real-time constraints, with other techniques employed in the optimization of soft real-time embedded systems, e.g., based on simulation and on average-case optimization. Accordingly, MCS models need to provide support for the emerging mixed-criticality design methodologies. Mixed-criticality has to be reflected in system models.

The modeling scenarios which can be identified in recent MC research and in current industrial practices related to safety standards lead to the need to associate criticalities to different type of elements, i.e., application components, platform resources, constrains, annotations of extra-functional properties. These criticality annotations are used to apply mixed-criticality-specific modeling rules to feed mixed-criticality-specific schedulability analyses, DSE flows, and development and implementation constraints.

## 5.3 State of the Art

There are several examples of model-based methodologies for modeling, exploration, and implementation of complex embedded systems. For instance, *MILAN* [5] enables a model-based approach to capture the application and the platform (called resource model). MILAN also introduced the idea of constraint model, which distinguishes between semantic constraints, which give composability rules, from design constraints, which capture performance requirements. The framework shows how a model-based approach facilitates the integration of several simulation tools at different levels of abstraction for the estimation of the performance of the design point by relying on a Generic Modeling Environment (GME) [35]. *Koski* [21] is a design flow for Multi-Processor System-on-Chip (MPSoC) covering the design phases from system-level modeling to Field-Programmable Gate Array (FPGA) prototyping. System-level modeling relies on UML and separates the capture of the application from the platform. However, this approach relies on a proprietary profile for capturing the required semantics.

Despite the relative recent release of the standard MARTE profile, there have been already several proposals relying on it. *Gaspard2* [8, 35] is a design environment for data-intensive applications which enables a MARTE description of both the application and the hardware platform, including MPSoC, and regular structures. Gaspard2 uses composite diagrams and the MARTE profile for capturing both application and platform architectures. Gaspard2 tooling supports the chaining of different Model-to-Model (M2M) transformation tools. This facilitates the generation of synthesis flows and also of performance models. Specifically, Gaspard2 supports the generation of SystemC TLM models at the Programmers View Time (PVT) level. It enables fast simulations, which speeds up exploration.

*MoPCoM* [45] is another design methodology for the design of real-time embedded systems which supports UML and the MARTE profile for system modeling. Specifically, MoPCoM uses the Non-Functional Property (NFP) MARTE profile for the description of real-time properties; the Hardware Resource Modeling (HRM) MARTE profile for platform description; and the Alloc MARTE profile for architectural mapping. Moreover, MoPCoM defines three levels of generation. The second level, called Execution Modeling Level (EML), targets the generation of models for performance analysis, and it is suitable for obtaining performance figures used in DSE iterations. However, work reported in [24] mostly focuses on the Detailed Modeling Level (DML), intended for implementation, by enabling VHDL code generation.

The *PHARAON* methodology [33] provided a solution for automatically synthesizing models combining new communication semantics with standard UML/MARTE real-time management features. This approach provides a flexible and easy-to-use way to specify and explore the system's concurrent architecture.

*CoFluent* methodology [18] captures application and hardware architecture by means of composite diagrams and SysML blocks. UML activity diagrams are used to specify application execution flows. The MARTE HRM profile is used for capturing the HW platform. CoFluent models can be translated into executable SystemC transaction-level models, which serves to obtain utilization, time, and power performance metrics.

A main limitation of the previous methodologies is that the exploration of architectural alternatives requires the edition of the UML/MARTE model and a regeneration of the executable performance model.

In [24], a UML-MARTE-based methodology relying on activity threads is proposed in order to reduce the effort required to capture the set of architectural mappings. An activity thread is a UML activity diagram where each path reflects a design alternative, that is, an architectural mapping.

In [26], a methodology for supporting designers on the evaluation of the HW/SW partitioning solutions, specifically, to identify design points fulfilling the timing constraints is shown. It proposes a way to depict in one set of diagrams all possible combinations of system configurations. By means of annotation of MARTE non-functional properties and of the application of schedulability analysis, the design space is restricted to the design points fulfilling timing requirements. However, this methodology does not rely on automated technologies for the estimation of performance metrics.

These MARTE-based specification methodologies are still limited for DSE purposes. The exploration of different platform architectures, of different architectural mappings, and even a small change in a design parameter (e.g., a cache size) still requires a manual change of the model. The *COMPLEX* [13] flow proposes a single-source approach to overcome the aforementioned limitations. Moreover, the COMPLEX framework produces a configurable performance model which avoids the re-generation and re-compilation of a performance model for each exploration alternative and thus a significant impact in the exploration time. This framework also supported the capture of the output performance metrics to be used by the objective function(s) of the DSE process within the model and of performance constraints. Enabling the capture of the performance metrics in the model, and so in a tool independent manner, enabled the direct relation of such metrics with the performance constraints also captured in the model.

Modeling complexity has increased with the need to consider the modeling of Cyber-Physical System (CPS) and Mixed-Criticality Systems (MCS). A *UML-Modelica-SysML* integrated modeling environment as a ModelicaML profile integrated in Eclipse is presented in [36]. *Modelica* is an object-oriented mathematical language for component-oriented modeling of complex physical systems containing components of diverse nature, e.g., mechanical, electrical, electronic, hydraulic, thermal, control, electric power, etc. The modeling of mixed-criticality systems in UML/MARTE has been proposed in [15, 16]. This work provides modeling techniques which cover a number of scenarios where mixed-criticality has to be captured.

## 5.4 Single-Source Modeling Methodology

## 5.4.1 Introductory Example: Quadcopter System

Along the following sections, the main modeling techniques of the proposed singlesource methodology are presented. These modeling techniques will be presented by taking excerpts of a model of a digital electronics system embedded in a quadcopter. This quadcopter system, shown in Fig. 5.3, has been developed by the OFFIS Institute for Information Technology in the context of the CONTREX project [28]. The quadcopter digital system includes:

- The data mining, radio control & telemetry, and flight control functionalities. They are safety critical as a failure on them compromises person's safety.

- A mission functionality, which consists in the detection and tracking through a camera a moving ball, e.g., in a sport action, in order to track, record, and stream that action video to a base station.

- A functionality to log monitoring and debug data.

All this functionality is implemented in a *Xilinx Zynq* platform, which contains a processing system with two *ARM Cortex-A9* processors. In addition, the Zynq platform has an FPGA which allows the integration of custom logic and additional *Microblaze* processors, configured without caches, for enabling more predictable computational resources for safety critical functions. The Zynq board is integrated

Fig. 5.3 The digital electronic system of a quadcopter is used for introducing the single-source methodology

in a board together with sensor components, motor actuators, and IO devices IO. These components are abstracted as part of the environment in the UML/MARTE model.

#### 5.4.2 Introduction

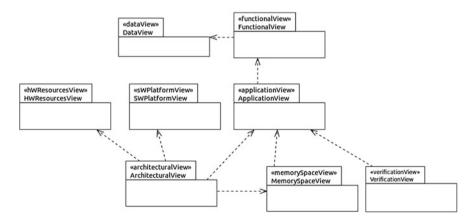

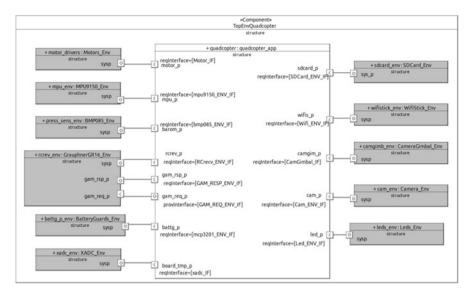

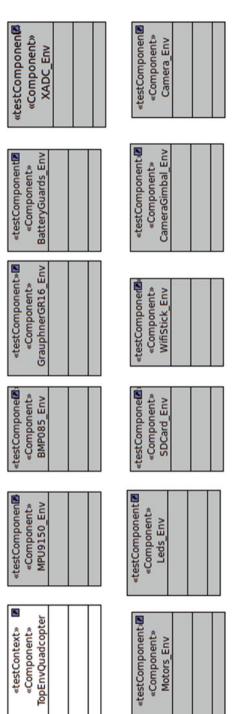

The modeling methodology supports separation of concerns. At the root of the UML/MARTE model, model information is distributed into *views*. Model views are captured as UML packages decorated with a methodology-specific stereotype which adds the view semantics. Figure 5.4 shows a diagram with the views enclosing all the quadcopter model information.

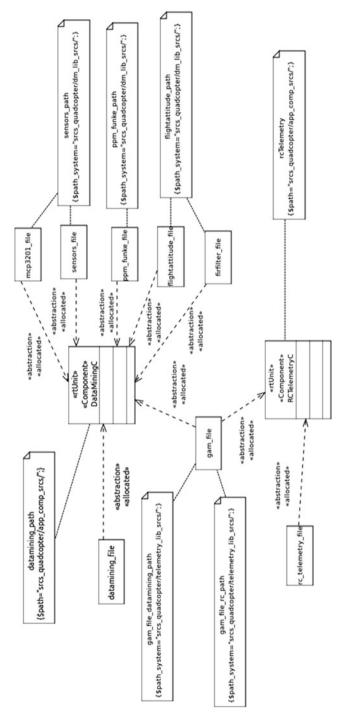

In this methodology, model views support the separation under different concerns. The model of the verification environment (verification view) is separated from the system model (remaining views). As stated in MDA, the Platform Independent Model (PIM) is separated from the platform model. The PIM is captured through the data, functional and application views. Platform-dependent information is added later. The *HW resources view* declares the HW components. which can be later instanced in the *architectural view*. The declaration of software platform resources (in the SW platform view) is also separated from the declaration of hardware platform resources. Architectural information is captured through UML composite diagrams, and separated from component declaration, which have associated the behavioral information. The methodology follows a pragmatical and generic approach with respect to the association of behavior to the model. Figure 5.5 shows an excerpt of the quadcopter model where source files are associated to application components (UML artifacts allocated to the PIM component via UML relations decorated with the MARTE «allocated» stereotype). In addition, the methodology allows the association of paths for the sources through UML

Fig. 5.4 Model views

constraints associated to the artifacts. This mechanism is language independent and has been exploited in the automated generation of executable performance models and of synthesized binaries.

As Fig. 5.4 shows, building a platform-specific model depends on the PIM model, but not the opposite. Then, incremental model development is possible. Thus, for instance, the methodology makes possible the generation of an executable functional model. After capturing the platform-dependent model, the generation of a performance model or the synthesis phase is enabled. Similarly, time or energy annotations can be added, e.g., to a hardware component, to add accuracy to the automatically generated performance model. However, if these annotations are not present, the generation of the performance model is still possible (default values are used).

#### 5.4.3 Platform-Independent Model

The methodology enables the description of a platform-independent model (PIM) under a component-based approach.

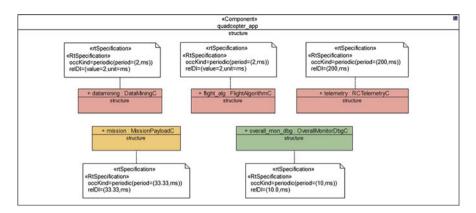

The methodology enables a clean separation of the PIM information. Figure 5.6 shows the components of the quadcopter PIM as they are seen in the Eclipse model explorer view.

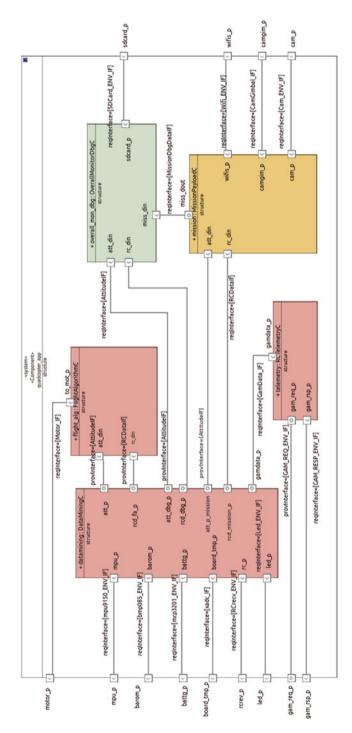

Among the six components, the *quadcopter\_app* component is decorated as *«system»* component (it can be seen in Fig. 5.7). The PIM system component is the top component of the PIM model hierarchy, which contains the PIM architecture, shown in Fig. 5.7. The remaining components are PIM components, to be eventually instanced in the PIM system component and which shall be stereotyped to be either an active component, a passive component, or a shared variable. The MARTE *«RtUnit», «PpUnit», and «SharedComResource»* stereotypes are respectively used for that purpose. Figure 5.8 shows the application of the *«RtUnit»* stereotype to the datamining (DataMiningC) and radio-control and telemetry (RCTelemetryC) components of the quadcopter. As can be observed in Fig. 5.6, non-system components have been enclosed in an additional UML package called *AppComponents*. This

Fig. 5.6 Components of the quadcopter PIM model

- ApplicationView

- Innamed

- quadcopter\_app

- AppComponents

- MissionPayloadC

- FlightAlgorithmC

- DataMiningC

- RCTelemetryC

- OverallMonitorDbgC

Fig. 5.7 Quadcopter PIM architecture

| «clientServerSpecification»<br>«Interface»<br>Motor_IF   | + set_motor_control_value( + ln: motor_ld_e, + out: motor_info_s, + ln: u16)<br>+ motor_dev_init(): err_motor_e<br>+ get_motor_status(+ in: motor_id_e(unique)): motor_info_s<br>+ set_motor_rotation( + in: motor_id_e, + in: motor_direction_e) |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| «clientServerSpecification»<br>«Interface»<br>RCDatalf   | <pre>+ get_thrust(): ppm_channel_s + get_gier(): ppm_channel_s + get_nick(): ppm_channel_s + get_roll(): ppm_channel_s + get_hold_altitude(): bool + get_camera_on(): bool + get_camera_on(): bool + get_sw_motor_on(): bool</pre>                |

| «clientServerSpecification»<br>«Interface»<br>AttitudelF | + getAttitude(): attitude_type<br>+ isAttitudeValid(): bool                                                                                                                                                                                       |

is not required, but supported by the methodology, to structure more PIM model information.

The architecture of the platform-independent model is captured within the PIM system component by means of a UML composite diagram, as shown in Fig. 5.7.

The PIM system component makes instances of the PIM components as UML properties, either active components or passive components, that is either of *«RtUnit»* or *«PpUnit»* components. The quadcopter model only instances active components, since all the components have internal periodic tasks. For instance, *datamining* is an instance of the *DataMiningC* component. PIM component instances are connected via channels. Channels are captured as UML port-to-port connectors. While these connectors reflect to *internal connections*, the PIM architecture also contains UML connectors. In this case, they connect a port of the top component and a port of an internal component, reflecting the delegation of the function services or requirements across one hierarchy level.

Each port is stereotyped as a client-server port via the MARTE «*ClientServer*-*Port*» stereotype. This stereotype has the attribute *kind*, of the MARTE *ClientServerKind* type, which allows the methodology to state that the port has either a *provided* or a *required* interface. In addition, the attributes *provInterface* and *reqInterface*, both of the UML interface type, enable the specification of the specific interface associated to the port. Such an interface has to be previously captured as a client-server interface in the functional view. Figure 5.8 shows an excerpt of the functional view of the quadcopter, with three interfaces.

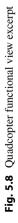

All of them have been applied to the MARTE *«ClientServerSpecification»* stereotype to identify the interfaces that can be exported by PIM components. Each interface declares the methods that are exported at that interface. For instance, the AttitudeIF interface declares two methods: the *getAttitude* method for obtaining the attitude information from the provider component and the *isAttituteValid* method for obtaining a flag stating if the attitude value that can be currently retrieved from the component is valid. In turn, each of those methods are specified by their input and output parameters. Both of them have to have a precisely specified type. The data view enables the user to precise all the types to be employed in the interfaces. Figure 5.9 shows an excerpt of the data view of the quadcopter model. This excerpt shows the capability of the methodology to capture complex structured types, e.g., the *attitude\_type* returned by the *getAttitude* method.

Concerning the capture of communication semantics, Fig. 5.7 reflects the simplest case, where a default semantics is associated to channels. For instance, the default semantics states that the call to the service is blocking at the initiation and end of the service. That is, the component requiring the service, i.e., making the call, waits for the provider component, i.e., the one implementing the called function, to be ready for executing it, and also waits for its completion.

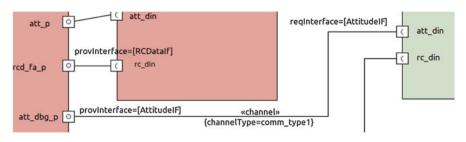

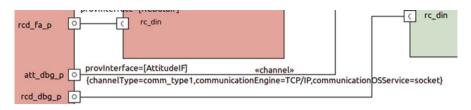

In addition, the methodology enables a more detailed specification of the channel semantics. Figure 5.10 illustrates a case where the semantics of the channel used by the *overall\_mon\_dbg* component to retrieve attitude data from the *datamining* component has a user-defined semantics. For it, the UML port-to-port connector representing the channel is stereotyped with the *«channel»* methodology-specific

Fig. 5.10 Channel instance with custom semantics

Fig. 5.11 Specification of channel with custom semantics

stereotype. The *«channel»* stereotype provides the attribute *channelType*. This attribute can be assigned a UML component decorated with the MARTE *«CommunicationMedia»* stereotype. This component has to be included in an additional view, the communication view (see Fig. 5.11), and represents a channel whose semantics can be customized by the user. In order to customize the communication semantics, the MARTE *«StorageResource»* stereotype and the *«ChannelTypeSpecification»* stereotype are used. The former stereotype makes possible to specify the channel buffering capability, i.e., how many function calls can be buffered by the channel. The methodology-specific *«ChannelTypeSpecification»* stereotype contributes additional attributes for configuring the channel semantics, for instance, if the communicating components shall synchronize at function call and at function return.

## 5.4.4 Platform Resources

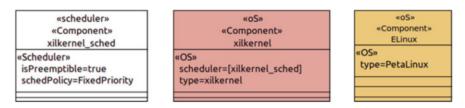

As was mentioned, the methodology enables the specification of platform resources in two separated views. The *SW platform view* is used to declare the software resources of the platform, i.e., operative systems and drivers. Figure 5.12 shows the software platform resources in the software platform view of the quapcopter model. The basic SW platform resource is the Operating System (OS), which is captured as a UML component decorated by the methodology-specific *«OS»* stereotype. The only OS semantics injected by this means is used for producing performance models based on generic RTOS models. However, more specific information is required in other contexts. The *«OS»* stereotype provides the *type* property, which serves as a string descriptor which uniquely identifies the target OS or RTOS in SW synthesis. The methodology also supports a more detailed specification of the OS behavior. This is necessary for safety critical cases, where an accurate performance analysis also relies on an accurate modeling of the OS scheduler behavior. For it, the *«OS»*

Fig. 5.12 SW resources of the quadcopter platform

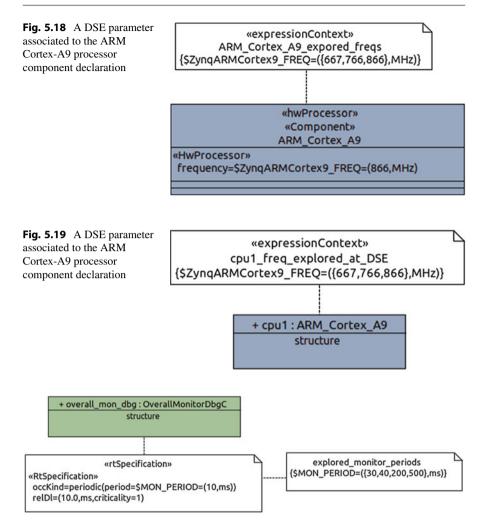

stereotype provides the *scheduler* attribute. The scheduler attribute specifies one scheduler component, i.e., a component stereotyped with the MARTE «Scheduler» stereotype. In turn, the «Scheduler» stereotype enables the attributes isPreemptible, schedPolicy, schedule, and otherSchedPolicy, which enable quick and versatile specification of scheduling policy. The *schedPolicy* attribute enables a synthetic capture of the most usual scheduling policies (static scheduler, fixed priorities, Earliest Deadline First (EDF), Round Robin (RR), etc.). The attribute isPreemptible states that the RTOS re-schedules on release events of other application tasks. The *schedule* attribute is used to configure and complete the description of the scheduling policy when *schedPolicy=TimeTableDriven*. The*TimeTableDriven* value can be used in MARTE to specify both order-based schedules and time-triggered schedules. In the former case, the *schedule* attribute serves to capture the execution order, i.e., the schedule of the tasks allocated to the OS. The otherSchedPolicy attribute is used to support other scheduling policies not covered by MARTE. In the methodology, it is also exploited for enabling a more synthetic description capable to preserve the single-source approach in a DSE context (an example is given in [16]). In the quadcopter case, the SW resource view shown in Fig. 5.12 states that the xilkernel OS has been configured with a priority-based scheduling policy.

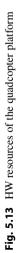

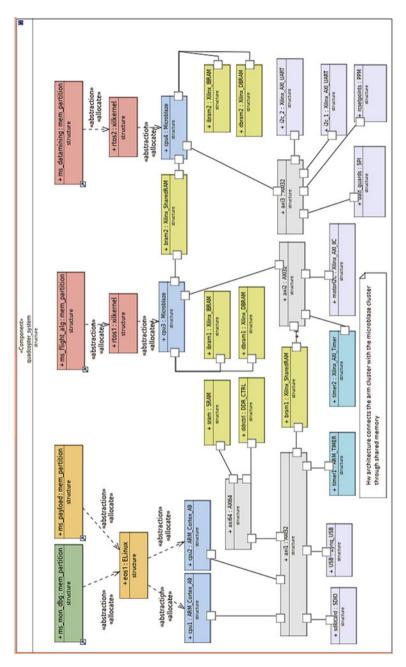

Figure 5.13 shows the resources declared in the hardware platform view of the quapcopter model. In this view, all the hardware platform resources to be instanced in the hardware platform architecture shall be declared. Each platform resource is declared through a component with a specific MARTE stereotype adding the hardware resource semantics. For this, the HRM MARTE profile is intensively used. As shown in Fig. 5.13, the methodology supports the modeling of computational resources (e.g., HW processors), communication resources (e.g., buses), memory resources (e.g. cache memories), main memories, and I/O devices. Depending on the type of hardware component, and thus of the stereotype, different attributes are available. None of the platform views contain any architectural information. There is one exception in the HW resources view, which allows to directly link a set of cache components to a processor component. The set is passed as the value of the caches attribute of the MARTE «HwProcessor» stereotype. Each element of the set passed to the caches attribute is a component decorated with the «HwCache» MARTE stereotype and also declared in the HW resources view. This mechanism has been used in the quadcopter model to simplify the capture of level 1 caches associated to the ARM\_Cortex\_A9 processor components. For the same example,

| Components<br>«Components<br>L2 UCache<br>etMcaches<br>tevel=2<br>type=unifed<br>memorySize=(512,KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Components<br>ahvid_O, hwhediaw<br>acomponents<br>2yng_USB<br>eHwhediaw<br>bendwidth=(35, Mbps)                                 | (Ambridge and Construction of the second |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

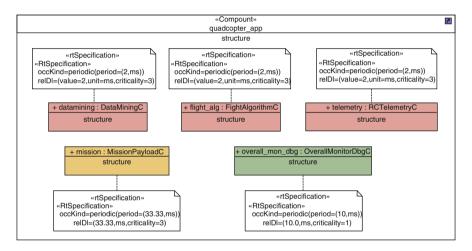

| «hwCache»<br>«Component»<br>«Component»<br>«Component»<br>Sets=256<br>Byte)<br>Byte)<br>(32,KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Components<br>etworters<br>DBR_CTRL<br>DBR_CTRL<br>ARM_TIMER                                                                    | And O, hwdedia»<br>that O, hwdedia»<br>time AXI UART<br>thwdedia»<br>bandwidth=(19200,bps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ethwCaches<br>ethwCaches<br>etwel=1<br>blockSizee(64<br>blockSizee(64<br>blockSizee(64<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blockSize(64)<br>blo                                                                                                                                                                         | <ul> <li></li></ul>                                                                                                             | CD<br>ehwitmen<br>e.components<br>Xilins_AM_Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ethwCaches<br>ethwCaches<br>«Components<br>accomponents<br>accomponents<br>accomponents<br>ARMContex49_L1_Lcache<br>evel=1<br>ARMContex49_L1_Lcache<br>evel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel=1<br>Revel= | etwBuss<br>ecomponents<br>AMBA,AHB<br>AMI,AHB<br>AXI,AHB<br>AXI,AHB<br>as<br>as<br>as<br>as<br>as<br>as<br>as<br>as<br>as<br>as | Ma<br>entra<br>RAM<br>512,KB)<br>encrySize=(32,KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Cortexa9_L1_DCache]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | +heurs<br>+components<br>AT132<br>AT132<br>MIdth=(32,bits)<br>wordb                                                             | etwRAMs<br>etwRAMs<br>components<br>Xilinx JBRAM<br>etwRAMs<br>memorySize=(512,KB)<br>memorySize=(512,KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ethwProcessons<br>«Components<br>ARM_Cortex, AB<br>ethwProcessons<br>caches=[ARMCortex49_L1_]Cache, ARM<br>frequency=(866,MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li></li></ul>                                                                                                             | ahwProcessorn<br>accomponents<br>Microblaze<br>artwProcessors<br>frequency=(100,MHz)<br>frequency=(100,MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

the *microblaze* processor components declared in the HW resources view have an empty *cache* attribute. The microblaze processors in the quadcopter system have no cache since they are used to run the datamining and control functionalities, which require more predictability due to their criticality.

#### 5.4.5 Platform-Specific Model

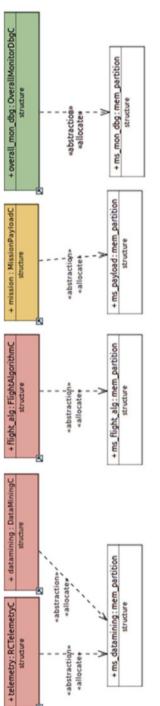

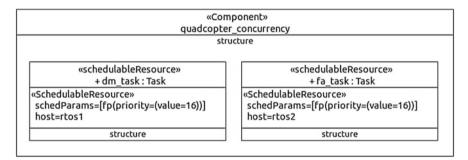

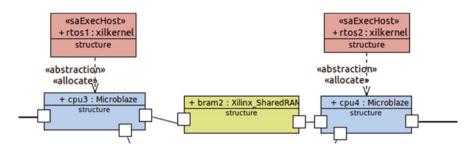

As was shown in Sect. 5.4.4, the SW platform and the HW resources views declare platform resources. They do not contain architectural information, apart from cache resources associated to processors. The methodology supports the specification of the SW/HW platform architecture and of the mapping of the PIM model to the SW/HW platform through the memory space and architectural views.

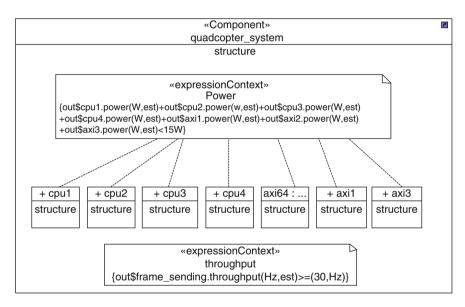

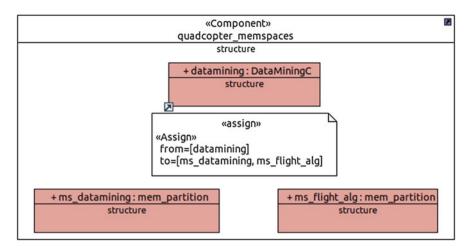

The memory space view is a non-mandatory view which can be used to specify memory spaces and the mapping of the component instances to the declared memory spaces. This is a first mapping level, which is relevant in SW implementation. A software process is inferred for each memory space. By default, if the user does not specify a memory space view, an implicit one with a single memory space is inferred, and it will be assumed that all the component instances are mapped to the implicit memory space. Figure 5.14 reflects a case where four memory spaces have been specified. The specification is done again within a composite diagram associated to a system top component, called *quadcopter\_memspaces*, captured within the memory space view. This component is captured as a specialization of the PIM top component. Therefore, the references to the component instances, i.e., *telemetry, datamining, flight\_alg, mission,* and *overall\_mon\_dbg*, are visible and can be used as source of the allocations.

Figure 5.15 shows the architectural view of the quadcopter system. The architectural view captures the mapping of memory spaces to OS instances, which effectively closes the mapping of the PIM to the SW/HW platform.

The SW/HW architecture captures the mapping of the OS instances onto the computing elements, i.e., HW processors, and the interconnection of the different HW elements.

As can be noticed, the mapping of memory spaces to OS instances and the mapping of OS instances to computing elements are captured again by means of UML abstractions with the *«allocate»* stereotype. Regardless of the type of source or destination, a static mapping is captured with the same modeling technique. For the connection of PIM component instances, hardware platform components are linked also through UML port-to-port connectors. Summing up, the methodology employs the same modeling techniques, to solve the same type of modeling needs, for yielding more understandable models and an easier to learn methodology.

#### 5.4.6 Extra-Functional Properties and Performance Constraints

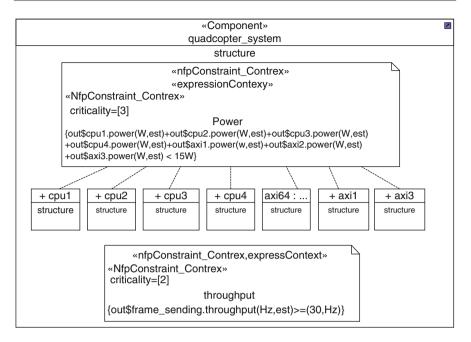

The methodology supports the annotation of several types of extra-functional properties (EFPs). These annotations are used by performance and schedulability

analyses. Most of them are performed in the HW resources view. Figure 5.12 illustrates several types of EFPs. For instance, the sizes of the different types of memories and structural information of caches, i.e., number of sets, cache policies, bus widths, frequencies for processors (and other types of hardware resources), and I/O device bandwidths, can be stated by only relying on the different MARTE stereotypes from the HRM profile.

Moreover, the methodology also supports the annotation of power and energy consumption associated to HW resources. For annotating static power consumption, the HW component is decorated with the MARTE «HW Component» stereotype, which provides the *staticConsumption* property. Moreover, the methodology supports the modeling of power state machines. The HW component can have different functional modes defined by the operating frequency, source voltage, dynamic power, and average leakage. A UML state diagram associated to the HW component and the MARTE «mode» and «ModeTransition» stereotypes are employed for that purpose. The *«HwPowerState»* stereotype introduced in [3] and the MARTE «ResourceUsage» stereotypes are used for characterizing the static and dynamic power consumptions of each mode. The modeling methodology also supports the annotation of energy consumption. The annotations depend on the modeling element. For instance, in order to annotate the energy consumed per cycle in a processor, a cycle attribute of MARTE NFP Energy type, and decorated with the MARTE «NFP» stereotype, is added to the processor component. An analog technique is used for associating energy consumptions to other components. For buses and memories, the energy associated to an access is annotated. For caches, two energy consumption figures are annotated, for distinguishing the hit consumption from the *miss* consumption.

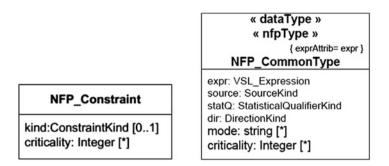

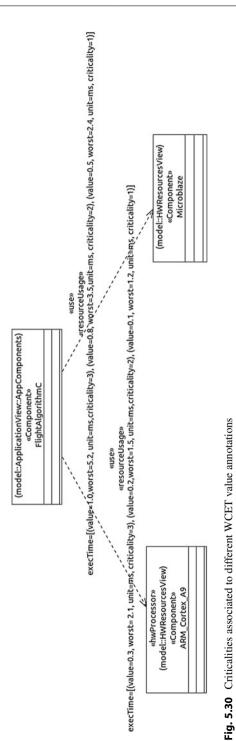

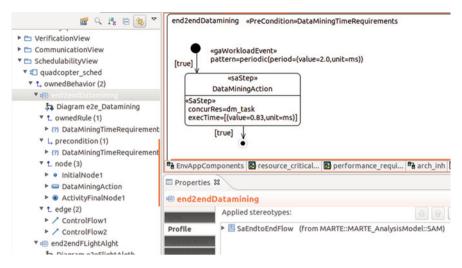

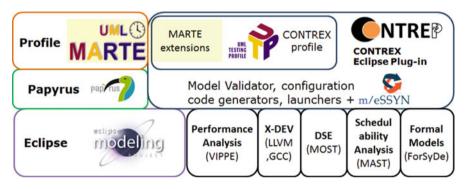

The methodology also allows the annotation of workloads, e.g., Worst-Case Execution Time (WCET), average times, and Best-Case Execution Time (BCET), to application components. Figure 5.30 in Sect. 5.4.10 illustrates such annotations in the mixed-criticality context and how they depend on the allocation to platform resources.