# General Principles of Spin Transistors and **30** Spin Logic Devices

# Supriyo Bandyopadhyay and Marc Cahay

# Contents

| Introduction                                                     | 1176 |

|------------------------------------------------------------------|------|

| Spin Field-Effect Transistors                                    | 1178 |

| Datta-Das Transistor                                             | 1178 |

| Another Spin Field-Effect Transistor                             | 1182 |

| Nonidealities                                                    | 1183 |

| Other Types of SPINFET                                           | 1184 |

| Two-Dimensional Datta-Das SPINFET                                | 1191 |

| Experimental Status                                              | 1192 |

| Obstacles to Experimental Demonstration                          | 1193 |

| Are SPINFETs Energy Efficient?                                   | 1194 |

| Unusual Features of SPINFETs                                     | 1196 |

| Transit Time Spin Field-Effect Transistor (TTSFET)               | 1197 |

| Is the TTSFET an Energy-Efficient Device?                        | 1201 |

| "Base Transport Factor" of the TTSFET                            | 1202 |

| Experimental Status of the TTSFET                                | 1202 |

| Comparison Between the SPINFET, TTSFET, and MOSFET for Device    |      |

| Density, Speed, and Cost                                         | 1202 |

| Spin Bipolar Junction Transistors                                | 1203 |

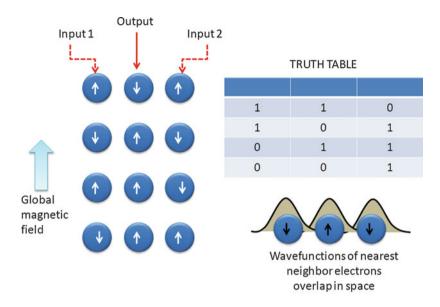

| Single-Spin Logic                                                | 1205 |

| Single-Spin Logic (SSL) Family                                   | 1208 |

| SSL NAND Gate for Universal Boolean Logic                        | 1209 |

| Theory of the SSL NAND Gate                                      | 1210 |

| Spin Wire: Unidirectional Information Transfer Along a Spin Wire | 1212 |

| Energy Dissipation in SSL                                        | 1215 |

S. Bandyopadhyay (🖂)

Department of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, VA, USA e-mail: sbandy@vcu.edu

M. Cahay

Department of Electrical and Computer Engineering, School of Electronics and Computing Systems, University of Cincinnati, Cincinnati, OH, USA e-mail: cahaymm@ucmail.uc.edu; mcahay@ececs.uc.edu

© Springer Science+Business Media Dordrecht 2016 Y. Xu et al. (eds.), *Handbook of Spintronics*, DOI 10.1007/978-94-007-6892-5\_43 1175

| Speed of SSL                                                            | 1216 |

|-------------------------------------------------------------------------|------|

| Gate Error Probability in SSL                                           | 1219 |

| Temperature of Operation of SSL                                         | 1219 |

| Current Experimental Status of SSL                                      | 1220 |

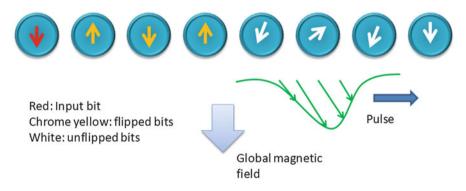

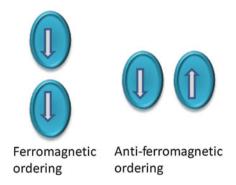

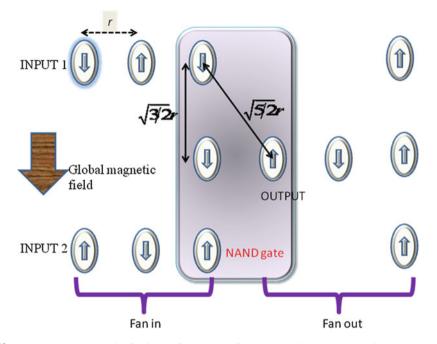

| Nanomagnetic Logic                                                      | 1220 |

| Magnetic Quantum Cellular Automata                                      | 1222 |

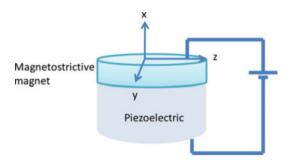

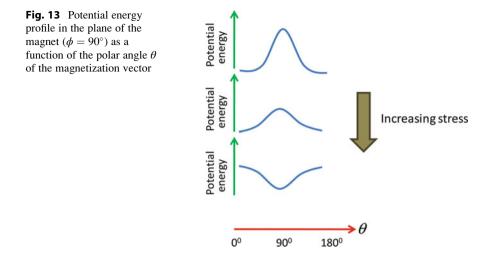

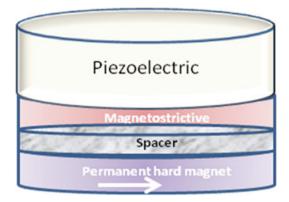

| Hybrid Spintronics and Straintronics                                    | 1224 |

| Logic                                                                   | 1226 |

| Error Rates in Magnetic Quantum Cellular Automata                       | 1230 |

| Memory                                                                  | 1230 |

| Energy Dissipation in Straintronics                                     | 1232 |

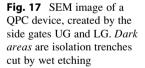

| All-Electrical Spintronics                                              | 1233 |

| All-Electrical Spintronics Using Quantum Point Contacts (QPCs)          | 1233 |

| Spin Polarization Using Quantum Point Contacts (QPCs)                   | 1233 |

| 0.5 Conductance Plateau in QPCs with Lateral Spin-Orbit Coupling (LSOC) | 1234 |

| Outlook                                                                 | 1236 |

| Conclusion                                                              | 1236 |

| References                                                              | 1236 |

|                                                                         |      |

#### Abstract

This chapter provides an overview of the field of spin-based devices, circuits, and architectures for digital information processing. Electron spin – as opposed to electron charge – is used as a classical degree of freedom to encode binary bits, and this approach improves the energy efficiency of information processing. However, there are also disadvantages associated with unreliability, difficulty of reading and writing information, and sometimes the need for cryogenic operation. These issues are discussed exhaustively, pointing the readers to niche applications where spin-based devices may offer some advantage. Both the basic and the applied aspects of spintronic information processing are discussed.

## Introduction

The fundamental device at the heart of all digital computing hardware is the binary switch that has two well-separated stable states. They store and encode the binary bits 0 and 1. When the switch is implemented with metal-oxide-semiconductor field-effect transistors (MOSFET), the two states are the high-conductance ("on") and low-conductance ("off") states of the device. The MOSFET is turned on by moving charge into the "channel" and turned off by moving charge out. Switching is therefore associated with motion of charges.

In all charge-based switches, the switching action invariably requires charge motion. This is because charge is a *scalar* quantity. Therefore, the two states must be demarcated by a difference in the magnitudes of the charge in the device. Switching will require changing the magnitude by an amount  $\Delta Q$ , in a time  $\Delta t$ ,

leading to a current flow of magnitude  $I = \Delta Q/\Delta t$ . This current causes an unavoidable energy dissipation of  $I^2 R \Delta t = (\Delta Q)^2 R/\Delta t$ , where *R* is the resistance in the path of the current. One can reduce this dissipation by increasing  $\Delta t$  (switching slowly) or by decreasing  $\Delta Q$ , but neither is desirable since the former makes the switch slow and error prone, while the latter reduces noise immunity since it decreases the logic-level separation by bringing the two states closer together.

The above shortcoming of charge-based devices has motivated the search for alternate state variables, such as electron spin, to encode binary bits. For example, a single electron's spin polarization in a magnetic field has two stable states that are parallel and antiparallel to the field since these are the allowed eigenstates. These two mutually antiparallel polarizations can encode the bits 0 and 1. Switching between them merely requires flipping the spin, without moving the electron in space and causing current flow. This eliminates the  $l^2R\Delta t$  dissipation, but does not eliminate dissipation altogether since the two spin states are nondegenerate and separated in energy by the Zeeman splitting  $g\mu_B B$  ( $g = \text{Landé g-factor}, \mu_B = \text{Bohr} magneton, B = flux density of the magnetic field). Therefore, even if a single spin is used as a binary switch [1], the minimum energy dissipation would have been <math>g\mu_B B$  per bit flip event.

In fact, the minimum energy dissipation for any "single" entity (single spin, single charge, single "anything") will be always  $k_BT \ln(1/p)(k_B = \text{Boltzmann} \text{ constant}, T = \text{absolute temperature}, and p = \text{probability of random switching}$  between the two bits at temperature T) as long as the switch is in thermodynamic equilibrium with its surrounding (and therefore characterized by a unique temperature T) [2, 3]. From that perspective, it should make no difference whether single charge or single spin is used as the vehicle to encode logic bits. However, what does make a difference is that no single entity is ever stable enough in a noisy environment to encode logic bits reliably. Therefore, an *ensemble* of entities (many spins, many single electron charges) is required to encode a logic bit in a robust fashion. In that case, *spin has a very important advantage over charge*.

The minimum energy dissipated to switch an ensemble of information carriers (spins, charges, etc.) is  $Nk_BT \ln(1/p)$ , where N is the number of degrees of freedom that the ensemble possesses. In the case of charges, N = M, where M is the number of charges in the ensemble. This happens because the different charges act independently. However, in the case of spin,  $N \sim 1$ , since exchange interaction between spins makes all of them act in unison. In fact, in a single-domain magnet, the entire ensemble behaves like one giant classical spin [4, 5], and all spins rotate together under an applied torque, so that effectively N = 1. Therefore, the minimum ratio of the dissipations incurred in switching a spin ensemble and a charge ensemble is

$$\frac{\text{Dissipation}|_{\text{spin ensemble}}}{\text{Dissipation}|_{\text{charge ensemble}}} = \frac{1}{M}$$

which gives spin a significant advantage over charge when M > 1.

## Spin Field-Effect Transistors

The field of "spintronics," which deals with the science and technology of storing, processing, and communicating information (including digital information in the form of binary bits 0 and 1) via the spins of charge carriers, came into maturity with the early proposals for spin field-effect transistors (SPINFETs) [6]. In a SPINFET, the current flowing between two terminals (the "source" and the "drain") is modulated by applying an electrostatic potential to the third terminal (the "gate"), as in a MOSFET. The difference is that the gate potential does not modulate the charge, or number of charge carriers, in the channel, but instead modulates the spin polarization of the carriers. If the source and drain contacts are efficient spin filters, then modulation of the spin polarization can modulate the current flowing between the source and drain, thus realizing transistor action. The gate potential can therefore turn the transistor on or off, but without changing the amount of charge in the channel. In other words,  $\Delta Q = 0$ , which should make the energy dissipation  $(\Delta Q)^2 R/\Delta t$  vanish. That it does, but there is additional energy cost associated with modulating spin polarization, and that cost may or may not exceed  $(\Delta O)^2 R/$  $\Delta t$ . If it does exceed, then the SPINFET is actually less energy efficient than the MOSFET. This issue will be visited later following the description of the earliest SPINFET due to Datta and Das [6], but it is curious that numerous papers on spintronics start out with the preamble "spin devices/transistors promise low dissipation and faster speed...." Unfortunately, there is almost never any substantiation of such claims in the same papers. The reality is that spin transistors are generally no more energy efficient than MOSFETs, and they are not faster either. In fact, they may have major shortcomings that make them less desirable than MOSFETs as binary switches. These issues are discussed later in this chapter.

# **Datta-Das Transistor**

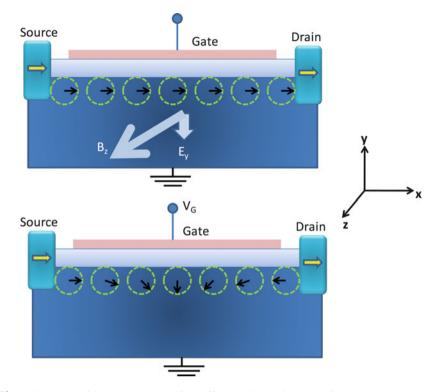

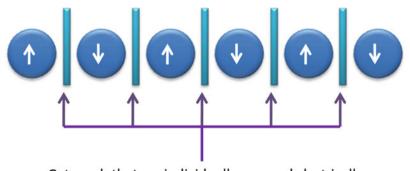

The spin field-effect transistor (SPINFET) concept was first proposed more than two decades ago by Datta and Das [6]. They examined a structure identical to that of a traditional depletion-mode MOSFET that is normally on, i.e., the transistor's conductance is high when the gate voltage is zero. Application of a gate voltage turns the transistor off by making the conductance go low. The only difference between the SPINFET's and the depletion-mode MOSFET's structure is that the source and drain contacts in the SPINFET are ferromagnetic and magnetized along the direction of current flow. Figure 1 shows this structure. Although the channel can be either one-, two-, or three-dimensional, the operation of the transistor will be explained by assuming it to be one-dimensional (a quantum wire), with only the lowest transverse subband occupied by carriers. Extension of the theory to polydimensional channels, or even the one-dimensional channel with multiple subbands occupied, is unfortunately not trivial and will be addressed later.

The two ferromagnetic contacts in the SPINFET are magnetized along the direction of current flow in the channel, and their magnetizations are mutually

**Fig. 1** Structure of the Datta-Das spin field-effect transistor with a one-dimensional channel. The spin orientations of electrons at different regions of the channel are shown within *broken circles* when the gate voltage  $V_G = 0$  (*top panel*) and  $V_G = V_{th}$  (*bottom panel*). The gate voltage causes an electric field  $E_y$  in the y-direction, while the source-to-drain current flows in the x-direction. The electric field induces Rashba spin-orbit interaction in the channel that causes an effective magnetic field in the z-direction whose magnitude depends on the electron's velocity in the x-direction. Precession of electron spin around this magnetic field gives rise to current modulation and transistor action

parallel. One of them (the "source" contact) injects electrons into the channel with spins aligned along the direction of the source's magnetization, which, in this case, is the +*x*-direction. The spin injection efficiency is assumed to be 100 %, so that every injected carrier has its spin aligned in the +*x*-direction. If there is no spin-orbit interaction in the channel and one can neglect the magnetic field caused by the magnetized contacts, then the electron spins do not precess as the electrons travel from the source to the drain under a source-to-drain bias V<sub>DS</sub>. Now, if there is no spin relaxation in the channel due to magnetic impurities, spin flip events, hyperfine interaction with nuclear spins, etc., then the injected carriers arrive at the "drain" contact with their spins still aligned in the original (+*x*) direction. This is shown in the top panel of Fig. 1. The drain is a spin-selective transmitter since it is also ferromagnetic. Assume that it is a 100 % efficient spin filter which allows only carriers whose spins are aligned parallel to its magnetization (i.e., the +*x*-direction)

to go through and completely blocks carriers whose spins are antiparallel (i.e., pointing in the -x-direction). Since the arriving carriers have their spins aligned parallel to the drain's magnetization, the drain transmits all of them and the maximum possible current flows between the source and drain contacts.

When an electrostatic potential  $V_G$  is applied between the "gate" terminal and ground, it induces an electric field transverse to the channel (in the y-direction). This electric field induces Rashba spin-orbit interaction in the channel [7] which produces an effective magnetic field that is oriented in a direction mutually perpendicular to the direction of current flow and the gate-induced electric field. Since the channel is strictly one-dimensional, current flows only in the x-direction. Therefore, the effective magnetic field of flux density  $B_{\text{Rashba}}$  is directed along the z-direction. Because of the one-dimensionality of the channel, the axis of this magnetic field is *fixed* and always points along the z-axis.

The strength of this magnetic field depends on the carrier's velocity, although starting with the Ehrenfest theorem of quantum mechanics one can show that this field is actually proportional to the electron's wavevector instead of the velocity. But in that case, it will be *spin dependent* since an electron of a given energy will have two different wavevectors in the two spin-split bands. If one wishes to define a spin-independent field, it will be necessary to postulate that the field is proportional to the velocity of the electron since that quantity is the same in two spin-split bands for any given energy. One should note that in the presence of spin-orbit interaction, an electron's velocity is not proportional to the wavevector even if the band is parabolic. With this consideration, the field is given by

$$B_{\text{Rashba}}(v) = \frac{2m^* a_{46}}{g\mu_B \hbar} E_y v, \qquad (1)$$

where v is the carrier velocity,  $E_y$  is the gate-induced electric field causing the Rashba interaction,  $m^*$  is the carrier effective mass,  $a_{46}$  is a material constant, and e is the electronic charge.

The spins of the injected carriers execute Larmor precession about  $B_{\text{Rashba}}(v)$  with a frequency  $\Omega$  given by the Larmor relation:

$$\Omega(v) = \frac{g\mu_B B_{\text{Rashba}}(v)}{\hbar} = \frac{2m^*}{\hbar^2} a_{46} E_y v.$$

<sup>(2)</sup>

This precession takes place on the *x*-*y* plane since the axis of the magnetic field is along the z-direction.

At this point, it is necessary to assume that there is no "damping" in the system, meaning that there is no energy dissipation. In other words, inelastic processes are absent. If strong damping is present, then the electron spins must ultimately align along the magnetic field  $\vec{B}_{Rashba}(v)$ , so that all spins will be pointing in the z-direction. To prevent this from happening, all energy relaxation processes must be eliminated. That requires the channel length to be much shorter than the inelastic

mean free path of electrons, which may be a few tens of nanometers at best if the device is operated at room temperature. At low temperatures (~4.2 K), the inelastic mean free path can be a few tens of  $\mu$ m.

If no damping is present, then the electron spins will precess continuously about  $\vec{B}_{\text{Rashba}}(v)$  since that field is in the z-direction, while the spins are polarized in the x-direction. Therefore, the *spatial* rate at which spin rotates when the electron travels through the SPINFET's channel can be obtained from the Larmor frequency as

$$\Omega(v) = \frac{d\phi}{dt} = \frac{d\phi}{dx}\frac{dx}{dt} = \frac{d\phi}{dx}v = \frac{2m^*}{\hbar^2}a_{46}E_yv$$

$$\Rightarrow \underbrace{\frac{d\phi}{dx}}_{\text{snatial rate}} = \frac{2m^*}{\hbar^2}a_{46}E_y,$$

(3)

where  $\phi$  is the angle through which spin rotates.

Note that the spatial rate  $d\phi/dx$  is *independent* of the carrier velocity. Therefore, every electron, regardless of its injection velocity and regardless of any elastic momentum randomizing collision that it suffers in the channel, rotates by exactly the *same* angle as it traverses the distance between the source and drain. This angle is given by

$$\Phi_{\text{Rashba}} = \frac{2m^*}{\hbar^2} a_{46} E_y L,\tag{4}$$

where L is the source-to-drain separation (or the channel length). Thus, if every electron was injected by the source with the same spin polarization, every electron arrives at the drain with identical spin polarization. There is no randomization of spin polarization in the channel, no matter how much momentum randomizing elastic scattering there is, because the spin precession angle is a constant independent of carrier velocity. This is a remarkable result for the strictly one-dimensional SPINFET.

Now, if the electric field  $E_y$  is such that  $\Phi_{\text{Rashba}} = (2n + 1)\pi$ , where *n* is an integer, then the carriers arriving at the drain have had their spins rotated by an odd multiple of 180°, which means their spin polarization is antiparallel to the original polarization and the drain's magnetization. Therefore, these carriers are blocked by the drain from transmitting and ideally no current flows. On the other hand, if  $\Phi_{\text{Rashba}} = 2n\pi$ , then the arriving carriers have their spins aligned parallel to the drain's polarization and are fully transmitted. Thus, by changing  $E_y$  with a gate potential, one can change  $\Phi_{\text{Rashba}}$  and modulate the source-to-drain current. *This realizes field-effect transistor action*.

Note that this one-dimensional transistor can operate at elevated temperatures, as long as the temperature is not so high as to make the channel length approach the inelastic mean free path. The only effect of higher temperature will be to induce a thermal spread in the electron velocity and perhaps increase the rate of elastic collisions that change an electron's velocity randomly, but none of this matter. Since  $\Phi_{Rashba}$  is independent of electron velocity, thermal averaging and increased momentum randomizing elastic collisions have no effect on  $\Phi_{Rashba}$ . Therefore, raising the temperature does not degrade the performance of the one-dimensional SPINFET, as long as the temperature is not so high as to introduce inelastic collision processes.

#### **Another Spin Field-Effect Transistor**

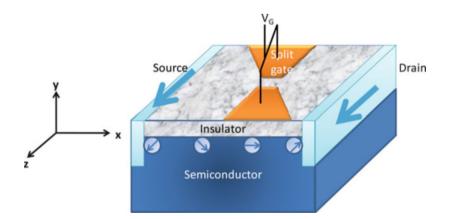

In addition to the Rashba interaction, there can be other types of spin-orbit interaction in a semiconductor channel which can be modulated by an external gate potential. An example is the Dresselhaus spin-orbit interaction [8] which generally exists in any material that lacks crystallographic inversion symmetry. This interaction also results in an effective magnetic field in the channel, just like the Rashba interaction. Assume that the channel of the transistor is in the [9] crystallographic direction and that it is made of a non-zinc-blende semiconductor. It has been claimed that the Dresselhaus interaction vanishes in the [9] crystallographic direction in one-dimensional structures made of zinc-blende semiconductors [10], which is why a non-zinc-blende semiconductor is chosen. In the lowest order approximation, one can neglect weak Dresselhaus contributions. In that case, the effective magnetic field due to the Dresselhaus interaction in the channel of the one-dimensional transistor shown in Fig. 2 will be directed along the x-axis and its strength will be given by

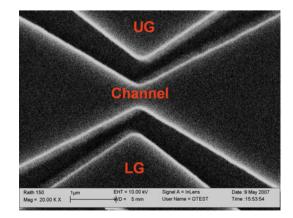

**Fig. 2** Structure of the spin field-effect transistor based on the Dresselhaus interaction. The one-dimensional channel is realized with split gates, and its width can be varied with a split gate potential  $V_G$  that increasingly constricts the channel as the potential is made more negative. The contacts are magnetized in the +z-direction. The Dresselhaus spin-orbit interaction in the channel gives rise to an effective magnetic field in the x-direction whose magnitude depends on the electron's velocity in the x-direction

$$B_{\text{Dresselhaus}}(v) = \frac{2m^* a_{42}}{g\mu_B \hbar} \left[ \left( \frac{\pi}{W_z} \right)^2 - \left( \frac{\pi}{W_y} \right)^2 \right] v, \tag{5}$$

where  $W_z$ ,  $W_y$  are the transverse dimensions of the quantum wire channel (assumed to be of rectangular cross section) and  $a_{42}$  is another material constant. Fortunately, this effective magnetic field is also proportional to the carrier velocity v.

It is easy to understand that if one injects spins from the source contact that are initially polarized along either the y- or z-axis (this will require magnetizing the source and drain contacts along the y- or z-axis), then these spins will precess about the x-directed effective magnetic field due to the Dresselhaus interaction. The precession takes place in the y-z plane. The angle by which the spin precesses in traveling between the source and drain will be given by (compare with Eq. 4)

$$\Phi_{\text{Dresselhaus}} = \frac{2m^* a_{42}}{\hbar^2} \left[ \left( \frac{\pi}{W_z} \right)^2 - \left( \frac{\pi}{W_y} \right)^2 \right] L.$$

(6)

This angle too is independent of the carrier velocity. One can change  $\Phi_{\text{Dresselhaus}}$  by varying the width of the one-dimensional channel  $W_z$  with a split gate potential  $V_G$ . That will also realize transistor action since changing  $\Phi_{\text{Dresselhaus}}$  will modulate the source-to-drain current [11]. This device has all the advantages of the original Datta-Das SPINFET, namely, that since  $\Phi_{\text{Dresselhaus}}$  is independent of carrier velocity, thermal averaging and elastic momentum-relaxing scattering have no deleterious effect. Accordingly, this transistor is also able to operate at elevated temperatures, without any serious degradation in performance, as long as the temperature is not so high as to induce inelastic collisions in the channel.

#### Nonidealities

If both Rashba and Dresselhaus interactions are present in the channel of a Datta-Das SPINFET or the SPINFET based on the Dresselhaus interaction, then the total effective magnetic field experienced by an electron in the channel due to spin-orbit interaction is the vector sum of the individual fields:

$$\mathbf{B}_{SO} = B_{\text{Dresselhaus}} \hat{\mathbf{x}} + B_{\text{Rashba}} \hat{\mathbf{z}},\tag{7}$$

where  $\hat{\mathbf{x}}$  and  $\hat{\mathbf{z}}$  are the unit vectors along the *x*- and *z*-axes. This resultant field lies in the *x*-*z* plane and subtends an angle  $\theta$  with the *x*-axis (channel axis or direction of current flow in the channel) given by

$$\tan \theta = \frac{B_{\text{Rashba}}}{B_{\text{Dresselhaus}}} = \frac{a_{46}}{a_{42}} \frac{E_y}{\left[\left(\frac{\pi}{W_z}\right)^2 - \left(\frac{\pi}{W_y}\right)^2\right]}.$$

(8)

Note that this angle is also independent of carrier velocity. Hence the axis of the effective magnetic field  $\mathbf{B}_{SO}$  is again the *same* for every electron, at any fixed values of  $E_y$ ,  $W_z$ , and  $W_y$ . If one injects spins with polarization normal to this axis, they will all precess about this axis (on a plane normal to this axis) as they travel from the source to the drain. The precession angle will be given by (compare with Eqs. 4 and 6)

$$\Phi_{\text{total}} = \frac{2m^*L}{\hbar^2} \sqrt{\left(a_{46}E_y\right)^2 + a_{42}^2 \left(\left[\frac{\pi}{W_z}\right]^2 - \left[\frac{\pi}{W_y}\right]^2\right)^2}.$$

(9)

One can change  $\Phi_{\text{total}}$  by changing  $E_y$  with a gate potential, but doing that also changes the angle  $\theta$  (see Eq. 8) and therefore the axis of the effective magnetic field will change. Thus, the precession plane will change if one changes the gate voltage, unlike in the previous two cases. This is a complicated effect. The reader will understand that if the source and drain contacts are magnetized in the same direction, which is *fixed*, then the current is never completely blocked at any gate voltage and a large leakage current will flow through the transistor during the off state. Therefore, the simultaneous presence of both Rashba and Dresselhaus interactions is not desirable.

There is an additional problem. The ferromagnetic contacts will induce a real magnetic field  $\mathbf{B}_{real}$  in the channel, whether or not it is a fringing field or a direct field. This field is *not* proportional to the carrier velocity (it is a constant) and therefore the angle by which a spin precesses about it, as the carrier travels a fixed distance *L* from the source to the drain, will depend on the carrier velocity *v*. This angle will be  $g\mu_B |\mathbf{B}|_{real} vL/\hbar$ . In that case, different electrons with different velocities due to scattering and the finite spread in electron energy will precess by different angles in traversing the transistor's channel. Consequently, ensemble averaging over all the electrons will reduce the current modulation significantly. In other words, both the on-to-off-conductance ratio and the transconductance of the transistor will decrease. The magnetic field can also increase spin flip scattering rate in the presence of spin-orbit interaction, which is an additional problem since it randomizes spin polarization. All these damaging effects have been discussed in Ref. [12].

#### Other Types of SPINFET

A number of other SPINFETs, inspired by the Datta-Das construct, have been proposed over time. One of them – the so-called non-ballistic SPINFET – works on the following principle:

Consider a two-dimensional semiconductor channel in the x-z plane as in Fig. 1 or 2. The quantum mechanical Hamiltonian describing an electron in this system is

$$H = \frac{p_x^2 + p_y^2 + p_z^2}{2m^*} + V(y) - \frac{\eta}{\hbar} [p_x \sigma_z - p_z \sigma_x] - \frac{\nu}{\hbar} [p_x \sigma_x - p_z \sigma_z],$$

(10)

where  $\eta$  and  $\nu$  are the strengths of the Rashba and Dresselhaus interactions, respectively. In terms of material constants,  $\eta = a_{46} |\mathbf{E}|; \nu = -\frac{a_{42}}{\hbar^2} \langle p_y^2 \rangle = a_{42} \langle \frac{\partial^2}{\partial y^2} \rangle$ , where **E** is the electric field inducing the Rashba interaction and  $\langle p_y^2 \rangle / 2m^*$  is the expectation value of the kinetic energy associated with motion in the direction of confinement. This quantity will be different in different subbands and will depend on the shape of the confining potential (e.g., in a rectangular well with infinite barriers,  $\langle p_y^2 \rangle = (n\pi\hbar/W)^2$  in the *n*-th subband where *W* is the width of the well and  $m^*$  is the electron's effective mass). The  $\sigma$ -s are the Pauli spin matrices and V(y) is the confining potential in the y-direction.

Since the Hamiltonian is invariant in the coordinates x and y, the wavevectors  $k_x$  and  $k_y$  are good quantum numbers, and one can write the spatial (or orbital) part of the wavefunction as

$$\psi(x, y, z) = e^{ik_x x} e^{ik_z z} \lambda_n(y).$$

(11)

Using this wavefunction, the spatial average of the Hamiltonian is calculated as

$$\langle H \rangle = \varepsilon_n + \frac{\hbar^2}{2m^*} \left( k_x^2 + k_z^2 \right) - \eta [k_x \sigma_z - k_z \sigma_x] - \nu [k_x \sigma_x - k_z \sigma_z], \qquad (12)$$

where  $\varepsilon_n$  are the subband energy levels in the quasi two-dimensional electron gas formed in the *x*-*z* plane.

Writing this Hamiltonian explicitly by replacing the Pauli spin matrices, one gets

$$\langle H \rangle = \varepsilon_n + \frac{\hbar^2}{2m^*} \begin{pmatrix} k_x^2 + k_z^2 \end{pmatrix} - \eta \begin{bmatrix} k_x & 0 \\ 0 & -k_x \end{bmatrix} + \eta \begin{bmatrix} 0 & k_z \\ k_z & 0 \end{bmatrix} - \nu \begin{bmatrix} 0 & k_x \\ k_x & 0 \end{bmatrix} + \nu \begin{bmatrix} k_z & 0 \\ 0 & -k_z \end{bmatrix}$$

$$= \begin{bmatrix} E_n - \eta k_x + \nu k_z & \eta k_z - \nu k_x \\ \eta k_z - \nu k_x & E_n + \eta k_x - \nu k_z \end{bmatrix},$$

$$(13)$$

where  $E_n = \varepsilon_n + \frac{\hbar^2}{2m^*} (k_x^2 + k_z^2)$ .

Diagonalization of this Hamiltonian yields the dispersion relations of the two spin-split branches of any subband and the corresponding eigenspinors. The former are

$$E_{\pm}(n,k_x,k_y) = E_n \pm \sqrt{(\eta k_x - \nu k_z)^2 + (\nu k_x - \eta k_z)^2},$$

(14)

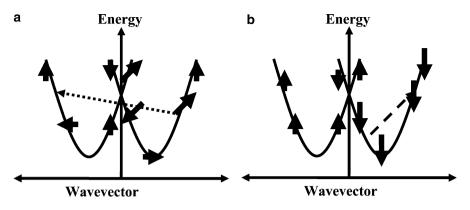

**Fig. 3** Energy dispersion relations of any spin-split subband showing the spin orientations at various wavevector states: (a) when  $\eta \neq \nu$  and (b) when  $\eta = \nu$ . The *broken arrows* show momentum-relaxing scattering events

while the latter are

$$\begin{aligned}

\varphi_{+}(k_{x},k_{y}) &= \begin{bmatrix} -\sin(\phi_{k}) \\ \cos(\phi_{k}) \end{bmatrix} \\

\varphi_{-}(k_{x},k_{y}) &= \begin{bmatrix} \cos(\phi_{k}) \\ \sin(\phi_{k}) \end{bmatrix},

\end{aligned}$$

(15)

where

$$\phi_k = \frac{1}{2} \arctan\left[\frac{-\eta k_z + \nu k_x}{\eta k_x - \nu k_z}\right].$$

(16)

Note that if  $\eta \neq \nu$ , then the angle  $\phi_k$  is wavevector dependent which makes the eigenspinors in Eq. 15 wavevector or velocity dependent. Therefore, neither spin-split branch has a fixed spin quantization axis. The spin orientation of an electron in either branch depends on its wavevector or velocity. This situation is depicted in Fig. 3a. Note that since the electron's spin will orient in the direction of the effective magnetic field **B**<sub>SO</sub> (for a positive g-factor), clearly the direction of **B**<sub>SO</sub> is velocity or wavevector dependent in either branch.

But now consider the special case when  $\eta = \nu$ . In this case,  $\phi_k = \pi/8$ , so that the eigenspinors become wavevector independent. In that case, each branch has a fixed (wavevector independent) spin quantization axis. However, these axes will be mutually antiparallel in the two branches since the eigenspinors are orthogonal. This situation is shown in Fig. 3b. Once again, since the spins will have oriented along **B**<sub>SO</sub>, it can be concluded that the direction of **B**<sub>SO</sub> is fixed in either branch, albeit mutually antiparallel in the two branches.

When  $\eta \neq \nu$ , and the eigenspinor in either spin-split branch changes with wavevector, it is always possible to find two states in the two branches at different

wavevectors whose eigenspinors are not orthogonal, meaning that the spin orientations in these two states are not exactly antiparallel. A nonmagnetic impurity or phonon can then induce a scattering between these two states because the matrix element for such scattering will be nonzero. However, such a scattering event will change the electron's spin polarization since the spin orientations of the initial and final states are. Therefore, any interbranch scattering caused by a nonmagnetic impurity or phonon will relax spin. In fact, even an intra-branch scattering event will relax spin since the spin orientation changes with wavevector within the same branch as well. Note that since the wavevector also changes in such scatterings, spin relaxation is accompanied by momentum relaxation and vice versa. This is essentially the Elliott-Yafet mechanism of spin relaxation [13, 14]. However, when  $\eta = \nu$ , the eigenspinors in the two branches are perfectly orthogonal at every wavevector. Consequently, it is impossible to have any interbranch scattering via phonons or nonmagnetic impurities since the matrix element for such a transition is exactly zero. It is of course possible to have intrabranch transition since the initial and final states have parallel spins (which makes the matrix element nonzero), but such a transition does not relax spin at all because the spin orientations of the initial and final state are parallel. Therefore, phonons and nonmagnetic impurities cannot relax spin in the special situation when  $\eta = \nu$ . In other words, the Elliott-Yafet mechanism becomes inoperative when  $\eta = \nu$ .

Next, recall that the effective magnetic field due to spin-orbit interaction  $\mathbf{B}_{SO}$  has a constant direction, independent of wavevector or velocity, in either branch when  $\eta = \nu$ . Therefore, there can be no D'yakonov-Perel' relaxation in this case since the latter is caused by change in the direction of  $\mathbf{B}_{SO}$  when an electron's velocity changes due to momentum-relaxing scattering [15, 16]. If the direction of  $\mathbf{B}_{SO}$  is independent of velocity, then no amount of change in the velocity due to scattering will change the direction of  $\mathbf{B}_{SO}$  and cause D'yakonov-Perel' spin relaxation. In the end, if  $\eta = \nu$ , then the two major spin-relaxation mechanisms in the channel of a SPINFET, namely, Elliott-Yafet and D'yakonov-Perel', are eliminated. The only remaining spin-relaxation mechanisms are those due to magnetic impurities, the Bir-Aronov-Pikus mechanism [17] and hyperfine interaction with nuclear spins. These mechanisms are usually very weak.

It is now possible to describe the operation of the "non-ballistic SPINFET," but before doing that, it should be pointed out that when  $\eta = \nu$ , the eigenspinors [from Eqs. 15 and 16] are

$$\varphi_{+} = \begin{bmatrix} -\sin(\pi/8) \\ \cos(\pi/8) \end{bmatrix}$$

$$\varphi_{-} = \begin{bmatrix} \cos(\pi/8) \\ \sin(\pi/8) \end{bmatrix}.$$

Therefore, the components of an electron's spin along the x-, y-, and z-axis in either spin-split branch is given by

$$S_{x} = [\varphi_{\pm}][\sigma_{x}][\varphi_{\pm}] = \pm \sin(\pi/4) = \pm \frac{1}{\sqrt{2}}$$

$$S_{y} = [\varphi_{\pm}][\sigma_{y}][\varphi_{\pm}] = 0$$

$$S_{z} = [\varphi_{\pm}][\sigma_{x}][\varphi_{\pm}] = \pm \cos(\pi/4) = \pm \frac{1}{\sqrt{2}}$$

which means that when the electron is in an eigenstate, its spin polarization vector lies in the *x*-*z* plane and subtends an angle of  $45^{\circ}$  with the *x*- or *z*-axis.

The so-called non-ballistic SPINFET proposed by two groups independently [18, 19] works as follows. The device has exactly the same structure as the one in Fig. 1, except that the source and drain contacts are magnetized (parallel to each other) in the *x*-*z* plane in a direction that subtends an angle of 45° with the *x*- or *z*-axis. The gate voltage is tuned to make  $\eta = \nu$  and the source injects spins into the channel in an eigenstate. The Dresselhaus interaction strength  $\nu$  is independent of the gate voltage, but the Rashba interaction strength  $\eta$  depends on it since  $\eta = a_{46}E_y$ . Next, it is assumed that the spin injection efficiency is 100 %, so that *every* spin, without exception, is injected in the same eigenstate. The injected electrons do not relax spin via the Elliott-Yafet and D'yakonov-Perel' mechanisms as explained before and therefore arrive at the drain with their spins aligned along the drain's magnetization. These electrons are all transmitted by the drain and the current is a maximum. This is the "on" state of the transistor.

To turn the device off, the gate voltage is detuned to make  $\eta \neq \nu$ . Then, Elliott-Yafet and D'yakonov-Perel' mechanisms become operative and relax spin. As a result, many of the electrons reaching the drain will have their spins flipped. They will be blocked by the drain (assuming that the drain is a 100 % efficient spin filter) and the current will drop. This is interpreted as the "off" state.

A little bit of reflection will convince the reader that the maximum ratio of the on-to-off-conductance is only 2:1. That is because, when spins are flipped randomly in the channel, what can happen at best is that 50 % of the spins arriving at the drain will have their spins antiparallel to the drain's magnetization (blocked), while the remaining 50 % will have their spins parallel (transmitted). After all, the spin polarization of the current cannot be less than zero. Thus, the off-current is no less than 50 % of the on-current, so that the maximum conductance ratio is 2. An actual simulation carried out by Shafir et al. [20] found that the conductance ratio in realistic scenarios is not even 2:1, but only ~1.2:1. Transistors require a conductance modulation of about  $10^5$ :1 for mainstream applications. Therefore, this "transistor" is not suitable for any such application.

One can obviously improve the conductance ratio by making a minor simple change to the design. Let us consider the situation when the magnetizations of the source and drain are *antiparallel*. One possible way to make them effectively antiparallel is to magnetize them in the same direction but ensure that the signs of spin polarizations of carriers at the Fermi energy are opposite in the two contacts. One can implement this by choosing two different materials such as iron and nickel for the two contacts [21]. In that case, when  $\eta = \nu$ , the drain blocks every electron and the current is ideally zero. When the gate voltage is changed to make  $\eta \neq \nu$ ,

spins flip and the drain now transmits the flipped spins. Then, the transmitted current will be nonzero. With the antiparallel arrangement, the conductance ratio  $I_{on}/I_{off}$  is *ideally* infinite, which would have been excellent, but in reality it is far from that. The real ratio is quite small since it is impossible to inject or filter spins with 100 % efficiency. This is shown below.

If the source injects both majority spins and minority spins, then the former will be blocked by the drain when  $\eta = \nu$  (if the drain is an ideal spin filter), but the latter will still transmit. Thus, the off-current will be *nonzero* due to the minority spins. Furthermore, if the drain is nonideal as well and transmits both its own majority and minority spins, then that too will make the off-current nonzero. If the spin injection efficiency at the source is  $\xi_s$  and the spin-filtering efficiency of the drain is  $\xi_D$ , then the ratio of on-current to off-current will be

$$\frac{I_{\rm on}}{I_{\rm off}} = \frac{1}{1 - \xi_S \xi_D}.$$

(17)

The spin injection efficiency is defined as  $\xi_s = \frac{I_{maj} - I_{min}}{I_{maj} + I_{min}}$ , where  $I_{maj}$  is the current due to majority spins in the injecting contact and  $I_{min}$  is the current due to minority spins in the injecting contact. Similarly, the spin detection efficiency is  $\xi_D = \frac{i_{maj} - i_{min}}{i_{maj} + i_{min}}$  where  $i_{maj}$  is the current due to majority spins in the detecting contact and  $i_{min}$  is the current due to majority spins in the detecting contact and  $i_{min}$  is the current due to majority spins in the detecting contact and  $i_{min}$  is the current due to majority spins in the detecting contact and  $i_{min}$  is the current due to minority spins in the detecting contact.

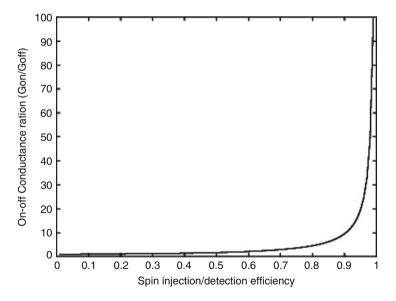

In order to make this ratio  $10^5$ , which is typical of modern transistors, the spin injection and filtering efficiencies have to be 99.9995 %!

It is unlikely that one can achieve spin injection efficiency this high at room temperature. Not only is this impossible in the near term, it may be *forever* impossible, since there are fundamental barriers to  $\sim 100 \%$  spin injection efficiency, particularly at room temperature.

There are two known routes to achieving high spin injection efficiency: (1) using highly spin-polarized half metals as the ferromagnetic spin injector and detector and (2) using spin-selective barriers that inject and detect spins of a particular polarization only [22, 23]. Unfortunately, there can be *no* half metals with 100 % spin polarization at any temperature above absolute zero. Dowben and Skomski [24] has shown that all half metals lose their high degree of spin polarization at temperature T > 0 K because of magnons and phonons. Even at T = 0 K, there are no ideal half metals with 100 % spin polarization because of surfaces and inhomogeneities [24]. Therefore, half metals will not achieve ~100 % spin injection efficiency, even at 0 K, let alone room temperature. Consequently, half metals are not a viable route.

Spin-selective barriers can at best transmit one kind of spin at one specific injection energy. The best spin-selective barriers use resonant tunneling [22]. At 0 K, the transmission energy bandwidth can approach zero, so that nearly 100 % spin injection efficiency is possible in principle, but at any nonzero temperature, thermal broadening of the carrier energy will ensure that the spin injection efficiency is far less than 100 %. Therefore, this route will not work either at room temperature.

The highest spin injection efficiency for spin injection from a metallic ferromagnet into a semiconductor through a tunneling barrier, demonstrated at or near room temperature, is only about 70 % [25]. and at very low temperatures, a spin injection efficiency of ~90 % has been shown to be possible [26]. If these two values for  $\xi$  are used in Eq. 17, then the maximum on-to-off ratio of the conductance are only 2 and 5, which are still a far cry from the 10<sup>5</sup> required. Therefore, these spin transistors may be theoretical curiosities, but are not viable as "transistors."

The reader will understand that the same problem afflicts the device of Ref. [1]. In fact, this is a generic problem that afflicts *all* spin field-effect transistors that require spin injection and detection.

Neither Ref. [1] nor Refs. [18, 19] ever made the claim that their device is competitive with the silicon MOSFET which is the workhorse of electronics. The authors of Ref. [1], in particular, carefully avoided calling their device a "transistor." However, claims were made by a group [27] that their SPINFET will be superior to a MOSFET. This group has proposed a device whose structure is very similar (almost identical) to that of the device of Refs. [18, 19] with the sole difference being that the source and drain contacts are magnetized in the antiparallel configuration, rather than the parallel configuration. The way this device works is as follows. The source injects electrons with spins polarized parallel to the source's magnetization. When the gate voltage is zero, the spin-orbit interaction in the channel is small or nonexistent so that both Elliott-Yafet and D'yakonov-Perel' relaxations are suppressed and the injected spins do not flip much. The drain therefore blocks most or all injected electrons from transmitting and the current is zero or at least low. This is the "off" state. When the gate voltage is turned up, the spin-orbit interaction in the channel increases dramatically, and the spins flip much more frequently. When electrons with flipped spins arrive at the drain, they are transmitted and the current rises. This is the mode of switching the transistor from the "off" to the "on" state with the gate voltage.

It should be obvious to the reader that the maximum conductance ratio of this device is given by Eq. 17 since this device suffers from the same malady as all SPINFETs, namely, that spin injection and filtering efficiencies have to be very high for the device to work with adequate conductance on-off ratio. If one generously assumes a spin injection efficiency of even 90 % at room temperature, then the maximum conductance ratio of this device is only 5:1, which immediately makes it noncompetitive with the silicon MOSFET by a long shot because the latter has on/off ratios exceeding 10<sup>6</sup>:1 [28, 29]. Additionally, it is not clear at all that a reasonable gate voltage can increase spin-orbit interaction in the channel by a lot, which is the basic operating principle of this device. Nitta et al. [30] studied the dependence of Rashba spin-orbit interaction on gate voltage in a transistor channel and found a weak dependence. Kwon et al. [31] experimentally measured the dependence of spin-relaxation length on gate voltage and found that an increase of gate voltage by 3 V decreases the spin-relaxation length by a mere 2.5 %. In view of that, the claim in Ref. [27] that only ~100 mV of gate voltage can turn the transistor fully on and provide a large on/off ratio of the conductance seems to be overly optimistic, if not far-fetched. It is believed that even if the spin injection and spin detection efficiencies could miraculously reach 100 %, the on/off ratio will still be very small, possibly much less than 10:1, despite the claim in Ref. [27] that it will be  $\sim 10^5$ :1.

#### **Two-Dimensional Datta-Das SPINFET**

The analysis of the Datta-Das SPINFET that was presented in section titled Datta-Das Transistor assumed a one-dimensional channel. For such a device, the source-to-drain current at any given gate voltage  $V_G$  will be given by [32]

$$I_{SD}^{1-D} = \frac{I_0}{2} [1 + \xi_s \xi_D \cos \Phi_{\text{Rashba}}(V_G)],$$

(18)

where  $I_0$  is the maximum current that flows through the transistor when it is on and  $\Phi_{\text{Rashba}}(V_{GS})$  is the gate-voltage-dependent spin precession angle. Since the transistor is on when  $\Phi_{\text{Rashba}}(V_{GS}) = 0$  and it is off when  $\Phi_{\text{Rashba}}(V_{GS}) = \pi$ , the maximum ratio of on- to off-current for the one-dimensional Datta-Das SPINFET is

$$\frac{I_{\text{on}}}{I_{\text{off}}}\Big|_{1-\text{D Datta-Das}} = \frac{1+\xi_S\xi_D}{1-\xi_S\xi_D}.$$

(19)

The source-to-drain current in a two-dimensional Datta-Das SPINFET however does not obey Eq. 18. The expression for a two-dimensional channel has been derived in a number of publications [33–35] and (for 100 % spin injection and detection efficiencies) is given by

$$I_{SD}^{2-D} = \frac{e^2 W_z}{\pi h} \int_{0}^{k_F} dk_z \left[ \cos^2 \Theta(k_z, k_F, V_{GS}) + \frac{k_z^2}{k_F^2} \sin^2 \Theta(k_z, k_F, V_{GS}) \right] V_{SD}$$

$$= \frac{e^2 W_z}{\pi h} \int_{0}^{k_F} dk_z \left[ \frac{k_z^2}{k_F^2} + \left( 1 - \frac{k_z^2}{k_F^2} \right) \cos^2 \Theta(k_z, k_F, V_{GS}) \right] V_{SD},$$

(20)

where  $k_z$  is the wavevector in the direction transverse to current flow in the two-dimensional channel,  $W_z$  is the width of the channel,  $k_F$  is the Fermi wavevector, and

$$\Theta(k_z, k_F, V_{GS}) = \frac{\left(2m^* E_y[V_{GS}]/\hbar^2\right)k_F - (m^*)^2 E_y^2[V_{GS}]/\hbar^4}{\sqrt{k_F^2 - k_z^2}}L.$$

(21)

Equation 20 is valid only at low temperatures and under small applied source-todrain bias. Clearly in this case the ratio of on- to off-current is much less than infinity even if the spin injection and detection efficiencies at the source and drain contact were 100 %. This is because the minimum current or off-current is

$$I_{\rm off}^{2-D} = \frac{e^2 W_z}{\pi h} \int_{0}^{k_F} dk_z \frac{k_z^2}{k_F^2} V_{SD} = \frac{e^2 W_z k_F}{3\pi h} V_{SD} \neq 0,$$

(22)

while the maximum current or on-current is

$$I_{\rm on}^{2-D} = \frac{e^2 W_z}{\pi h} \int_{0}^{k_F} dk_z V_{SD} = \frac{e^2 W_z k_F}{\pi h} V_{SD}.$$

(23)

Therefore, the best possible conductance on-off ratio is 3:1. Scattering and other nonidealities will make it worse than 3:1. This is the reason why the Datta-Das SPINFET has been so elusive to experimentalists who typically employ two-dimensional structures.

#### **Experimental Status**

The ability to modulate Rashba spin-orbit interaction strength in the channel of an FET-like structure was demonstrated long ago [30], but an experimental demonstration of current modulation in a SPINFET due to gate-induced modulation of the spin-orbit interaction strength has remained elusive even two decades after the first proposal of the Datta-Das SPINFET. There has been a recent claim in the literature that a two-dimensional SPINFET structure has exhibited the conductance modulation expected from a Datta-Das SPINFET due to gate voltage change [36], but unfortunately the authors of this claim used the wrong one-dimensional formula (Eq. 18) to match their experimental data with theory, even though their device structure was two-dimensional. This makes their claim dubious, although it is possible that in the regime where this device operated, the actual difference between the predictions of the correct two-dimensional formula (Eq. 20) and the incorrect one-dimensional formula (Eq. 18) may not be perceptible [35]. Calculations have shown that the predictions of the correct two-dimensional formula disagree with the experimental data by about  $\sim 15$  %, but more importantly the experimental data had only one and one-half periods of conductance modulation which is not enough to draw any definitive conclusion either way. In a two-dimensional channel, scattering plays a major role since it can randomize the spin precession angle  $\Theta(k_z, k_F, V_{GS})$  [because the transverse wavevector  $k_z$  is randomized by momentum relaxation events]. This is a major difference between a one- and a two-dimensional channel. Therefore, inclusion of scattering can further complicate matters, and a claim has been made [37] that scattering can make the correct two-dimensional formula agree with the experimental data of Ref. [36]. This is however never a convincing argument since the details of scattering in a particular structure cannot be known with certainty.

The more important issue to understand is that the two-dimensional channel has inherently poor on/off ratio because of ensemble averaging over the transverse wavevector represented by the integral over  $k_z$  in Eq. 20. Only one-dimensional SPINFETs are immune to the deleterious effect of ensemble averaging, but they are unfortunately unable to carry much current since the maximum conductance of a one-dimensional channel will be  $e^2/h$ . Thus, it is impossible to attain both high current levels (for large fan-out) and large on/off ratios with SPINFETs. This is a major shortcoming and seems to be insurmountable.

#### **Obstacles to Experimental Demonstration**

There are serious obstacles to demonstrating the Datta-Das SPINFET and its various clones, primary among which is the inability to inject and detect spins with high enough efficiencies at the source/channel and drain/channel interfaces. In Fig. 4, the on/off ratio of the current (or conductance) of the one-dimensional Datta-Das SPINFET is plotted as a function of the spin injection or detection efficiency [32].

Clearly, even when the spin injection and detection efficiency is as large as 90%, the conductance on/off ratio is a mere 10:1. This makes the conductance modulation of the transistor very weak and probably undetectable in a noisy environment. The second obstacle to experimental realization is the weak spin-orbit interaction in the conduction band of semiconductors which makes it difficult to precess the spin

**Fig. 4** The conductance on/off ratio of the one-dimensional Datta-Das SPINFET as a function of spin injection or detection efficiency (assuming the two are equal). Everything else is assumed to be ideal (Reproduced from [32] ("Switching voltage, dynamic power dissipation and on-to-off conductance ration of a spin field effect transistor") with permission from Institute of Engineering and Technology)

by  $180^{\circ}$  with a reasonable gate voltage. Spin-orbit interaction can be stronger in the valence band of some semiconductors [38, 39], but spin precession of holes is a more complicated business because of the presence of two different types of holes (heavy and light) and possible mixing between them. Therefore, it is not clear whether a p-channel SPINFET is any easier to demonstrate than an n-channel SPINFET. The third obstacle is the inevitable magnetic field in the channel caused by the ferromagnetic source and drain contacts. Since these are two ferromagnets facing each other, they will invariably generate a magnetic field in the channel. This field, like the Rashba field, also causes Larmor spin precession and the spatial rate of precession due to it is not velocity independent unlike that due to the Rashba field (see Eq. 3). As a result, electrons with different velocities in the channel undergo different additional spin precessions, and ensemble averaging over these electrons will dilute the conductance modulation. Finally, there is also the possibility of Ramsauer resonances occurring in the channel of the SPINFET which may cause current oscillation [11]. Under some circumstances, these oscillations may be mistaken for current modulation due to the Rashba effect [11] and therefore complicate matters. The channel magnetic field also causes a leakage current [37]. As a result, the experimental demonstration of the Datta-Das SPINFET (or any other related device) is very challenging and eluded the most committed efforts.

The other types of SPINFET that have been discussed are even harder to demonstrate. The device in Ref. [10] avoids a channel magnetic field, but employs the Dresselhaus interaction which is typically weaker than the Rashba interaction in technologically important semiconductors. It also requires a more complicated structure that is more vulnerable to fabrication defects. Therefore, it is harder to implement. The devices of Refs. [18, 19], on the other hand, require a very delicate balance between the Rashba and the Dresselhaus interactions, which is difficult to achieve given the numerous imperfections in fabrication. Therefore, these devices have remained theoretical curiosities and eluded experimental realization.

### Are SPINFETs Energy Efficient?

Research in SPINFETs, or for that matter any nontraditional transistor, is motivated by a desire to overcome the fundamental speed and power limitations of MOSFETs. The MOSFET is switched from the "on" state to the "off" state (or vice versa) by moving charge carriers into and out of the channel with a gate voltage. This physical motion of charges causes excessive energy dissipation. There is no way to eliminate this dissipation, as was explained in the Introduction section. The high levels of dissipated to switch an isolated nanoscale MOSFET is about 50,000 kT at room temperature and in a circuit, that dissipation goes up to roughly  $10^6 kT$ because of additional capacitances and drive overheads. With current 22-nm node technology, the device density on a chip is approaching  $10^{10} \text{ cm}^{-2}$  and if the energy dissipation per switching event remains the same, then at a clock rate of 2 GHz, the power dissipation per unit area will be 8.4 kW/cm<sup>2</sup> if roughly 10 % of the transistors are switching every clock cycle. This is just about enough to overwhelm current heat sinking technology. Further downscaling of transistors and increasing their density on a chip seems to be impossible in this scenario unless the energy dissipation per switching event can be reduced. Without that, Moore's law [41] that envisions doubling of the device density on a chip every 18 months is seriously threatened. A consensus seems to be emerging that charge-based devices are fundamentally energy inefficient and will not be able to extend Moore's law beyond the year 2020, which is why alternate state variables, such as electron spin, are being increasingly examined.

At first look, it appears that the SPINFET is a promising candidate since it is switched without changing the carrier concentration in the channel. Therefore, it might appear that no current needs to flow to switch the transistor, thus eliminating the  $I^2 R \Delta t$  loss. Unfortunately, this is *not* true since switching is still accomplished with a gate voltage and some current flow is needed to charge up the gate (a capacitor) to the required voltage. The energy dissipated to charge up the gate to a voltage  $V_G$  is still  $(1/2)CV_G^2$  if the gate is charged abruptly or non-adiabatically (it can be shown that if the voltage  $V_G$  on the gate is turned on abruptly or non-adiabatically, then the energy dissipated  $I^2 R \Delta t$  is exactly equal to  $(1/2) C V_G^2$ where C is the gate capacitance [37]). Thus, in terms of gate dissipation, the SPINFET is no different from the MOSFET where the gate dissipation is again the same  $(1/2)CV_G^2$ . It does not matter what the gate voltage does – whether it changes the carrier concentration or the spin polarization of the carriers. The energy dissipated to charge the gate non-adiabatically is always  $(1/2)CV_G^2$  regardless of the role of the gate voltage. Therefore, the SPINFET provides no special advantage. If any advantage were to accrue, it would be solely due to the fact that the gate voltage required to switch a SPINFET is smaller than that required to switch a MOSFET.

Bandyopadhyay et al. [10] examined whether the gate voltage needed to switch a SPINFET is indeed less than that required to switch a MOSFET. For nanoscale transistors, the answer turned out to be *negative*. In fact, the SPINFET normally will require a much larger gate voltage than a comparable MOSFET and hence is *less* energy efficient, as long as the channel length is shorter than ~1  $\mu$ m. The problem is that the gate voltage in a spin transistor changes the spin polarization of carriers by affecting *spin-orbit interaction* – be it the Rashba or the Dresselhaus spin-orbit interaction band of most semiconductors is very weak, so that a very large gate voltage will be required to induce sufficient change in the spin polarization to turn a SPINFET from "on" to "off," or vice versa. The ratio of the gate voltages required to switch the SPINFET of Ref. [1] and to switch a comparable MOSFET was shown to be [10]

$$\frac{V_G^{\text{SPINFET}}}{V_G^{\text{MOSFET}}} \approx \frac{\hbar^2 \pi e}{2m^* \gamma E_F L},\tag{24}$$

where  $E_F$  is the Fermi energy in the channel,  $m^*$  is the electron effective mass in the channel, L is the channel length and  $\gamma$  is the rate of change of spin-orbit interaction strength with gate voltage ( $\gamma = \partial \eta / \partial V_G$ , where  $V_G$  is the gate voltage).

For realistic values of  $E_F$  and  $\gamma$ , the above ratio was shown to be smaller than unity only if the channel length of the transistor is several micrometers long [10]. Thus, no sub-micron SPINFET, of the type in Ref. [1], has any advantage over a comparable MOSFET in terms of power dissipation or energy efficiency, since the power dissipated to turn the transistor on or off is proportional to the square of the gate voltage required to switch the transistor.

The same conclusion holds for the SPINFET of Ref. [27]. The gate voltage required to modulate the conductance of this structure between the maximum and minimum values is likely to exceed that of MOSFETs by a large margin since a large amount of voltage is required to change the spin-relaxation length in a channel. This will make such a transistor much less energy efficient than a MOSFET.

In the end, traditional SPINFETs do *not* produce any advantage over traditional MOSFETs in terms of energy efficiency, which begs the question why should there be so much interest in SPINFETs. Part of it is certainly due to the novelty of the concept and the allure of anything nontraditional. However SPINFETs may have some unique features that do set them apart and make them desirable for certain niche applications.

# **Unusual Features of SPINFETs**

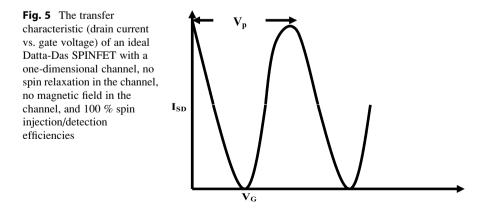

The transfer characteristic of a Datta-Das SPINFET is non-monotonic and *oscilla-tory* as shown in Fig. 5. Now, if the ac gate voltage happens to be a sinusoid with amplitude  $V_a$  and the period of the oscillation in the transfer characteristic is  $V_p$ , then for every period of the gate voltage swing, the source-to-drain current oscillates by  $V_a/V_p$  periods. Hence if the frequency of the sinusoidal gate voltage is f, then the frequency of the source-to-drain current will be  $(V_a/V_p)f$ . In other words,

the device can act like a frequency multiplier with a multiplication ratio of  $V_a/V_p$ . This is made possible by the oscillatory nature of the transfer characteristic. Thus, one can implement a *single-transistor-frequency-multiplier* with a SPINFET, which is not possible with traditional MOSFETs. However, this is not unique to SPINFETS; any device whose transfer characteristic is oscillatory (quantum interference transistors of 1980s vintage is one such example [42]) can implement a single-transistor-frequency-multiplier.

Another interesting feature is that the transconductance of the transistor, which is the slope of the transfer characteristic in Fig. 5, can be either positive or negative depending on the value of  $V_G$ , or the gate bias. By connecting two SPINFETs in series – one with positive and the other with negative transconductance – one can realize a complementary device (analogous to CMOS), where the static energy dissipation is zero and current flows only during switching, resulting in dynamic dissipation only. This, of course, assumes that the off-current in a SPINFET is exactly zero, which can happen only in a true one-dimensional device where a single subband is occupied in the quantum wire channel, there is no spin relaxation in the channel, there is no extraneous magnetic field in the channel, and the spin injection/detection efficiencies of the ferromagnetic source and drain contacts are both exactly 100 %. All of these requirements – especially the last – are very difficult to fulfill. In general, the leakage current (current flowing in the off state) is quite high in a SPINFET, which makes the standby (static) energy dissipation substantial and possibly much more than that in a modern CMOS device.

### Transit Time Spin Field-Effect Transistor (TTSFET)

A different of genre of transistors that exploit spin properties for operation was proposed by Appelbaum and Monsma, which they termed "transit time spin field-effect transistor" (TTSFET) [43]. This device employs silicon – the most technologically developed semiconductor – which unfortunately also has very weak spin-orbit interaction. Therefore, this device could not possibly have relied on gate controlled spin-orbit interaction to precess spins and modulate current as in the Datta-Das SPINFET. Instead it uses a fixed magnetic field in the channel (directed along the length of the channel) and a bias voltage to modulate the electron's velocity in the channel. The velocity modulation modulates spin precession. This, together with spin-selective injection and extraction of carriers in the channel, realizes transistor action very much like in the Datta-Das SPINFET.

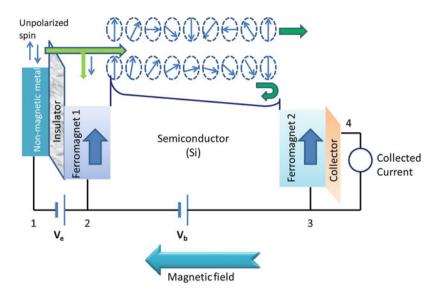

The TTSFET is a four-terminal device and consists of six material layers with current flowing perpendicular to the heterointerfaces. The structure of this device is shown in Fig. 6.

The principle of operation of this transistor can be explained in five steps: First, a tunnel junction, composed of the first three layers on the left, injects unpolarized spins from a nonmagnetic metal emitter into the ferromagnetic base (Ferromagnet 1) under the emitter bias  $V_e$  applied between terminals 1 and 2. Second, the ferromagnetic base preferentially scatters the hot minority spins which then lose

Fig. 6 Structure and operational principle of the TTSFET

energy and fall down into the base. The majority spins (i.e., spins whose polarizations are parallel to the magnetization of Ferromagnet 1) are much less scattered and hence do not lose much of their energy. As a result, they are able to emit over the Schottky barrier into the semiconductor (Si) [44, 45] – a phenomenon known as "hot-electron ballistic spin filtering." Third, the electrons that enter the semiconductor layer are at least partially spin polarized as a result of the filtering action. There is a static magnetic field in the semiconductor layer pointing in the direction of current flow. As the entering spins drift through this layer under the applied bias  $V_b$  applied between terminals 2 and 3, they precess about this magnetic field with an angular frequency given by the Larmor formula:

$$\Omega = \frac{d\phi}{dt} = \frac{g\mu_B B}{\hbar}.$$

(25)

The angle by which a given spin precesses in traveling from the ferromagnetic source to the ferromagnetic drain is

$$\Phi = \frac{g\mu_B B}{\hbar} \tau_t = \frac{g\mu_B B}{\hbar} \frac{L}{v},$$

(26)

where  $\tau_t$  is the transit time through the semiconductor layer, *L* is the width of the layer, and *v* is the electron's velocity in this layer.

Upon reaching the second ferromagnetic layer (Ferromagnet 2), spins which are parallel to this ferromagnet's magnetization are transmitted while the antiparallel spins are blocked. This step, namely, spin detection, is the fourth step in device operation. In the final (fifth) step, the transmitted electrons are collected by the collecting layer which results in a current between terminals 3 and 4.

One can calculate the total transmission probability through the entire structure taking into account the imperfect spin-filtering action of Ferromagnet 1 and imperfect spin detection action of Ferromagnet 2.

Let the ferromagnets be magnetized in the +z-direction so that the spinors describing majority and minority spins in either ferromagnet are

$$\begin{split} \left[\Psi\right]_{\text{maj}} &= \begin{bmatrix} 1\\0 \end{bmatrix} \\ \left[\Psi\right]_{\text{min}} &= \begin{bmatrix} 0\\1 \end{bmatrix}. \end{split} \tag{27}$$

The spin-filtering action by Ferromagnet 1 will allow majority spins to enter the semiconductor layer with a probability of  $(1 + \xi_1)/2$  and minority spins to enter with a probability of  $(1 - \xi_1)/2$ , where  $\xi$  is the spin-filtering efficiency for Ferromagnet 1. Using the Bloch sphere notation, the spinor describing the precessed majority spin at the interface with Ferromagnet 2 is

$$[\Upsilon]_{\rm maj} = \begin{bmatrix} \cos\left(\frac{\Phi}{2}\right) \\ e^{i\nu}\sin\left(\frac{\Phi}{2}\right) \end{bmatrix}$$

(28)

while the spinor describing the precessed minority spin at the interface with Ferromagnet 2 is

$$[\Upsilon]_{\min} = \begin{bmatrix} \sin\left(\frac{\Phi}{2}\right) \\ -e^{i\nu}\cos\left(\frac{\Phi}{2}\right) \end{bmatrix}$$

(29)

The overall probability of the precessed majority spin transmitting into the majority and minority spin bands of Ferromagnet 2 are respectively

$$\begin{aligned} |T_{\text{maj-maj}}| &= \frac{(1+\xi_1)(1+\xi_2)}{4} \left| \left[ \cos\left(\frac{\Phi}{2}\right) & e^{-i\nu} \sin\left(\frac{\Phi}{2}\right) \right] \left[ \begin{matrix} 1\\0 \end{matrix} \right] \right|^2 \\ &= \frac{(1+\xi_1)(1+\xi_2)}{4} \cos^2\left(\frac{\Phi}{2}\right) \\ |T_{\text{maj-min}}| &= \frac{(1+\xi_1)(1-\xi_2)}{4} \left| \left[ \cos\left(\frac{\Phi}{2}\right) & e^{-i\nu} \sin\left(\frac{\Phi}{2}\right) \right] \left[ \begin{matrix} 0\\1 \end{matrix} \right] \right|^2 \\ &= \frac{(1+\xi_1)(1-\xi_2)}{4} \sin^2\left(\frac{\Phi}{2}\right) \end{aligned}$$

(30)

where  $\xi_2$  is the spin detection efficiency at Ferromagnet 2.

Similarly, the overall probability of the precessed minority spin transmitting into the majority and minority spin bands of Ferromagnet 2 are respectively

$$\begin{aligned} |T_{\min-maj}| &= \frac{(1-\xi_1)(1+\xi_2)}{4} \left| \left[ \sin\left(\frac{\Phi}{2}\right) - e^{-i\nu} \cos\left(\frac{\Phi}{2}\right) \right] \left[ \begin{matrix} 1\\0 \end{matrix} \right] \right|^2 \\ &= \frac{(1-\xi_1)(1+\xi_2)}{4} \sin^2\left(\frac{\Phi}{2}\right) \\ |T_{\min-min}| &= \frac{(1-\xi_1)(1-\xi_2)}{4} \left| \left[ \cos\left(\frac{\Phi}{2}\right) - e^{-i\nu} \cos\left(\frac{\Phi}{2}\right) \right] \left[ \begin{matrix} 0\\1 \end{matrix} \right] \right|^2 \\ &= \frac{(1-\xi_1)(1-\xi_2)}{4} \cos^2\left(\frac{\Phi}{2}\right). \end{aligned}$$

(31)

The total transmission probability is therefore

$$|T_{\text{total}}| = |T_{\text{maj-maj}}| + |T_{\text{maj-min}}| + |T_{\text{min-maj}}| + |T_{\text{min-min}}|$$

=  $\frac{1}{2}(1 + \xi_1 \xi_2 \cos \Phi).$  (32)

Note that the total transmission probability is not the same for every electron since  $\Phi$  depends on electron velocity *v*.

The angle  $\Phi$  in Eq. 26 can be varied by varying the average electron velocity  $\langle v \rangle = v_d$  by changing the bias voltage V<sub>b</sub> across the semiconducting layer. Note that because of the Schottky barriers at the Ferromagnet 1/Semiconductor and Ferromagnet 2/Collector interfaces, the bias V<sub>b</sub>, by itself, does not cause a current to flow. Instead, it modulates the current caused by V<sub>e</sub>, i.e., the current flowing between terminals 3 and 4, by controlling the spin precession in the semiconducting layer by varying the drift velocity  $v_d$ . Since V<sub>b</sub> controls the current flowing between terminals 3 and 4, transistor action has been realized.

This device shares one feature with the Datta-Das SPINFET and all its clones, namely, that current modulation is achieved via spin precession and not via charge modulation. In all other respects, it is very different from the Datta-Das SPINFET since it (1) does not rely on modulating spin-orbit interaction with a voltage (which is an advantage since it takes a lot of voltage to change spin-orbit interaction strength even slightly), and (2) it is a four-terminal device instead of a three-terminal device. The major disadvantage however is that the spin precession angle  $\Phi$  is *not* velocity or energy independent, unlike in the case of the Datta-Das SPINFET. As a result, ensemble averaging over the electron energy (or velocity) will reduce the current modulation and adversely affect the transconductance of the transistor as well as causing some leakage current in the OFF state. The saving grace is that because of hot-electron transport across the semiconducting layer, the spread in the electron velocity is likely to be relatively small and hence the deleterious effect of ensemble averaging over the electron velocity may not be drastic.

One way to account for the deleterious effect of ensemble averaging phenomenologically is to replace Eq. 32 with the equation

$$|T_{\text{total}}| = \frac{1}{2} \left[ 1 + \xi_1 \xi_2 v_0 \int_0^{\tau_t} \frac{1}{\sqrt{4\pi Dt}} \cos\left(\frac{g\mu_B B}{\hbar}t\right) e^{-t/\tau_s} e^{-(L - v_d t)^2/4Dt} dt \right]$$

where  $v_0$  is a normalizing velocity,  $\tau_t$  is the transit time, L is the separation between the two ferromagnetic contacts,  $\tau_s$  is the spin-relaxation time,  $v_d$  is the drift velocity, and D is the diffusion coefficient of electrons. The integral in the above equation represents the effect of ensemble averaging. One would like to keep  $\tau_t$  and L small in order to suppress the deleterious effect of ensemble averaging as much as possible, but then the spin may not be able to rotate by a sufficiently large angle between the two ferromagnetic contacts. Since the rotation rate is the Larmor precession rate that is fixed by the magnetic field, the angle of rotation increases with increasing transit time. One can try to increase the Larmor precession rate by increasing the magnetic field to compensate for a shorter transit time, but there is a limit on the magnetic field. If the magnetic field is too large, it will demagnetize the magnetic contacts and flip their magnetizations in the direction of the field. In other words, the magnetic field cannot exceed the coercive field of the contacts and hence cannot be increased indefinitely. The consequence of all this is that the effect of ensemble averaging remains a problem, unlike in the case of the Datta-Das transistor, and this limits the performance of the TTSFET.

#### Is the TTSFET an Energy-Efficient Device?

Since the TTSFET does not require charge modulation to achieve conductance modulation, and furthermore since the conductance modulation does not require modulating spin-orbit interaction which is weak in technologically important semiconductors, it may appear that the TTSFET will be more energy efficient than the Datta-Das SPINFET. However, this may not be true. It is a hot-electron device and therefore necessarily a high-power device. Hot-electron transport is needed for both the spin-filtering effect and to ensure that the energy spread in the transiting electrons is small so that energy averaging over the spin precession angle does not reduce the conductance modulation (on/off ratio) too much. The energy of the hot electrons that transit the device is dissipated in the collecting contact. Thus, it is not clear that the TTSFET is any more energy efficient than the Datta-Das SPINFET; in fact, it is likely to be less energy efficient since it takes a lot of energy to generate hot electrons.

In terms of conductance on/off ratio, that quantity is once again determined by the efficiencies of ballistic spin filtering and spin detection at ferromagnet/paramagnet interfaces. In fact, from Eq. 32, it can be predicted that the on-off ratio cannot exceed  $(1 + \xi_1\xi_2)/(1 - \xi_1\xi_2)$  which makes it very similar to the Datta-Das SPINFET.

# "Base Transport Factor" of the TTSFET

The expression for the transmission probability derived above did not account for the "base transport factor"  $\alpha_T$  which is the fraction of the hot carriers injected into the semiconductor layer from the emitter that successfully makes it to the collector without being lost in the semiconductor layer (which is called "base") due to recombination with carriers of the opposite polarity or other effects. Since the carriers injected in the base of the TTSFET are hot carriers with high kinetic energy, they have a significant probability of being backscattered into the emitter and never reaching the collector. This will reduce  $\alpha_T$  and hence  $|T_{total}|$ , which, in turn, reduces the on-current and the transconductance of the transistor. In order to retain a high enough  $\alpha_T$ , it is imperative to keep the semiconductor layer width as small as possible in order to reduce the probability of backscattering. The problem with that approach is (see Eq. 26) if the layer width *L* is reduced, then the magnetic field strength *B* has to be increased in order to obtain the same degree of spin precession [same  $\Phi$ ] with all other variables being the same. This is not always desirable.

#### **Experimental Status of the TTSFET**

There has been significant progress towards the experimental demonstration of the TTSFET. Huang et al. and Appelbaum et al. have shown spin injection and detection in this transistor as well as transistor operation [46, 47]. In particular, Ref. [46] showed a 37 % spin injection efficiency and clear modulation of the transistor current by varying the bias voltage across the semiconductor layer which causes a variation in the spin precession angle  $\Phi$ . The modulation however is small – the collector current changes by a factor of 7 or so, indicating that the conductance on/off ratio of this device is currently of the order of 7:1. This small ratio is most likely due to inefficient ballistic spin-filtering effect and spin detection, as well as perhaps some deleterious effect of ensemble averaging over electron velocity. Thus, it seems that all SPINFET type devices that require spin injection and detection at ferromagnet/paramagnet interfaces, including the TTSFET, suffer from the curse of having a very small conductance on/off ratio. The only solution to this problem is to enhance spin injection and detection efficiencies, but that seems to be a tall order.

# Comparison Between the SPINFET, TTSFET, and MOSFET for Device Density, Speed, and Cost

The device density and cost for the SPINFET and the MOSFET are about the same since both are identical structures, except that the source and drain are

ferromagnetic for the SPINFET. The TTSFET will have a slightly lower device density and a slightly higher cost because it is a 4-terminal device as opposed to a 3-terminal device.

The speeds of these devices are determined by the transit time of carriers through the active region (channel in the cases of MOSFET and SPINFET, and the semiconducting layer in the case of the TTSFET). Since the thickness of the semiconducting layer in TTSFET is determined by film growth techniques while the channel lengths in SPINFET and MISFET are determined by lithography, and furthermore since the velocity of carriers in TTSFET is higher because they are hot carriers, the TTSFET is likely to have a slightly higher switching speed because carriers will travel through it faster.

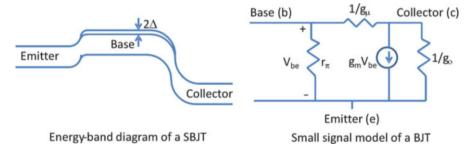

#### Spin Bipolar Junction Transistors