David J.R. Cristaldi Salvatore Pennisi Francesco Pulvirenti

# Liquid Crystal Display Drivers

Techniques and Circuits

Liquid Crystal Display Drivers

# Liquid Crystal Display Drivers

# Techniques and Circuits

by

David J.R. Cristaldi DIEES - University of Catania, Italy

Salvatore Pennisi DIEES - University of Catania, Italy

and

Francesco Pulvirenti STMicroelectronics, Catania, Italy

Dr. David J.R. Cristaldi Università Catania Dipto. Ingegneria Elettrica Elettronica e dei Sistemi (DIEES) Viale Andrea Doria, 6 95125 Catania Italy dcristaldi@diees.unict.it Dr. Francesco Pulvirenti STMicroelectronics Stradale Primosole, 50 95121 Catania Italy francesco.pulvirenti@st.com

Prof. Salvatore Pennisi Università Catania Dipto. Ingegneria Elettrica Elettronica e dei Sistemi (DIEES) Viale Andrea Doria, 6 95125 Catania Italy spennisi@diees.unict.it

ISBN 978-90-481-2254-7

e-ISBN 978-90-481-2255-4

DOI 10.1007/978-90-481-2255-4

Library of Congress Control Number: 2009920981

© Springer Science+Business Media B.V. 2009

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

9 8 7 6 5 4 3 2 1

springer.com

The amateur photo in the cover was taken by S. Pennisi during a summer thunderstorm in front of Taormina, Sicily, where he lives. The idea of the cover was suggested by his friend Eng. Giuseppe Cavallaro.

# Contents

| Forewords |      | xi                                           |          |

|-----------|------|----------------------------------------------|----------|

| Preface   |      | XV                                           |          |

|           |      |                                              |          |

| 1.        |      | id Crystals                                  | 1        |

|           |      | Early History                                | 1        |

|           | 1.2  | Classification                               | 7        |

|           |      | 1.2.1 Cause of formation                     | 7        |

|           |      | 1.2.2 Shape and molecular structure          | 8        |

|           |      | 1.2.3 Liquid crystal phases                  | 10       |

|           | 1.3  | Physical Characteristics                     | 14       |

|           |      | 1.3.1 Molecular order                        | 15       |

|           |      | 1.3.2 Elastic properties                     | 15       |

|           |      | 1.3.3 Surface Aligning Properties            | 16       |

|           |      | 1.3.4 Viscosity                              | 19       |

|           |      | 1.3.5 Electromagnetic Properties             | 20       |

|           |      | 1.3.6 Ion Transport                          | 23       |

|           |      | 1.3.7 Optical Properties and Birefringence   | 24       |

|           |      | 1.3.8 Temperature Effects                    | 28       |

|           | 1.4  | Concluding Remarks                           | 28       |

|           | Refe | erences                                      | 30       |

| h         | Time | id Createl Displace                          | 22       |

| 2.        |      | id Crystal Displays<br>Towards the First LCD | 33<br>33 |

|           | 2.1  |                                              |          |

|           |      | 2.1.1 The first LC Application               | 34       |

|           |      | 2.1.2 The Pioneering Role of RCA             | 34       |

|           |      | 2.1.3 The First LCD                          | 37       |

|           | 2.2  | 2.1.4 The Pocket Calculator                  | 40       |

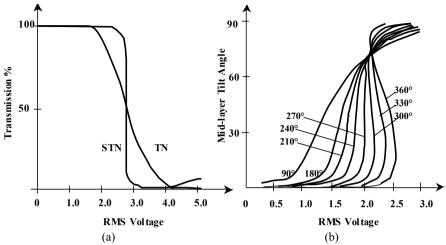

|           | 2.2  | The Twisted Nematic Mode                     | 42       |

|           |      | 2.2.1 TN Principle of Operation              | 43       |

|           |      | 2.2.2 Electro-Optic Transfer Function (EOTF) | 45       |

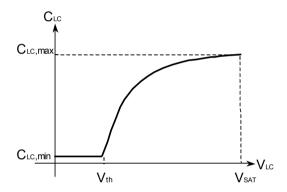

|           |      | 2.2.3 LC Capacitance                         | 48       |

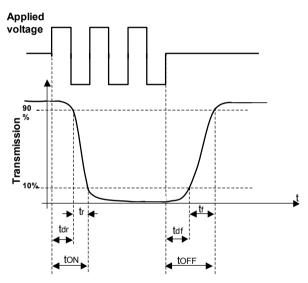

|           |      | 2.2.4 Response Time                          | 48       |

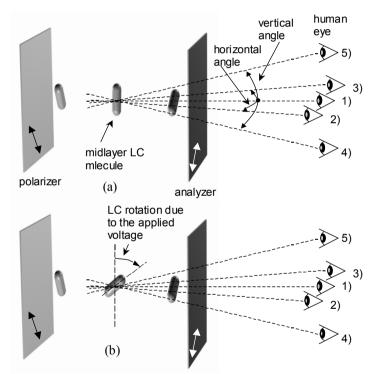

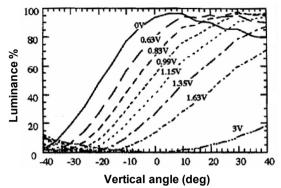

|           |      | 2.2.5 Viewing Angle                          | 49       |

|           |      | 2.2.6 Application of the TN Mode             | 51       |

|           | • •  | 2.2.7 The LC Digital Watch                   | 53       |

|           | 2.3  | New High-Performance LC Materials            | 54       |

|    | 2.4   | Further Developments                                    | 56  |

|----|-------|---------------------------------------------------------|-----|

|    |       | 2.4.1 Passive Addressing and Super Twisted Nematic Mode | 56  |

|    |       | 2.4.2 Active Matrix Addressing Schemes                  | 58  |

|    |       | 2.4.3 The First LCD for Television Set                  | 61  |

|    |       | 2.4.4 Improving the Viewing Angle                       | 62  |

|    | 2.5   | Concluding Remarks                                      | 65  |

|    |       | rences                                                  | 68  |

| 3. | Passi | ve LCDs and Their Addressing Techniques                 | 75  |

|    | 3.1   | Seven-Segment Displays and Direct Addressing            | 75  |

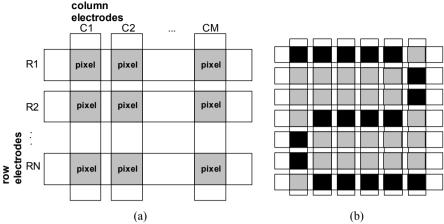

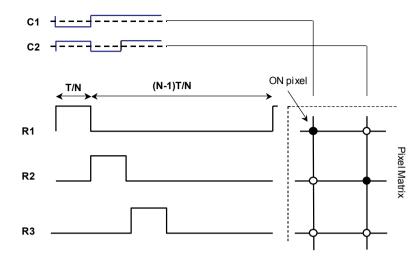

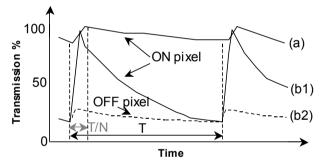

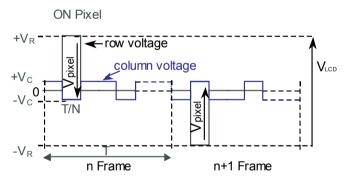

|    | 3.2   | Addressing of Passive-Matrix LCDs                       | 78  |

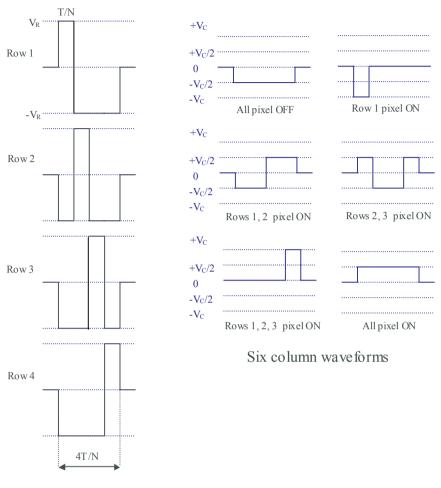

|    |       | 3.2.1 Single Line Addressing                            | 81  |

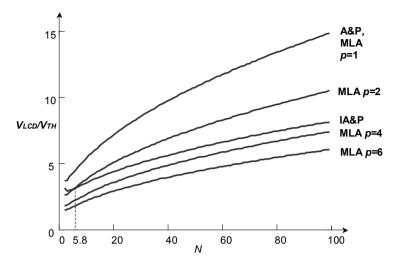

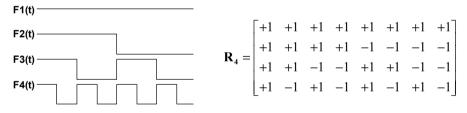

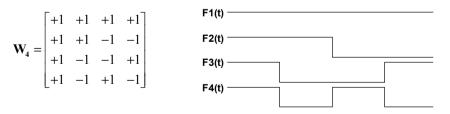

|    |       | 3.2.2 Multiple Line Addressing                          | 83  |

|    |       | 3.2.3 Further considerations on MLA                     | 88  |

|    |       | 3.2.4 Active Addressing                                 | 89  |

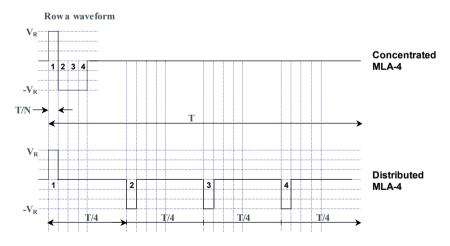

|    |       | 3.2.5 Distributed MLA                                   | 90  |

|    | 3.3   | Limitations of Passive-Matrix Addressing                | 91  |

|    |       | 3.3.1 Maximum Drive Margin                              | 92  |

|    |       | 3.3.2 Minimum Driving Voltage                           | 95  |

|    |       | 3.3.3 Crosstalk                                         | 96  |

|    | 3.4   | Displaying Gray Levels                                  | 99  |

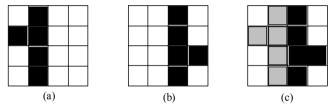

|    |       | 3.4.1 Spatial Dithering                                 | 100 |

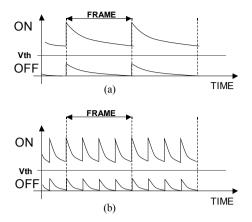

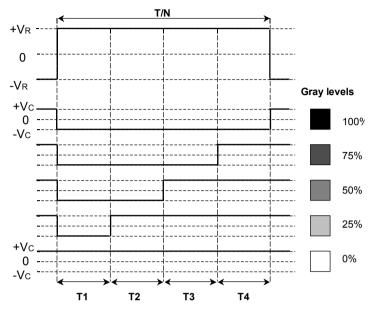

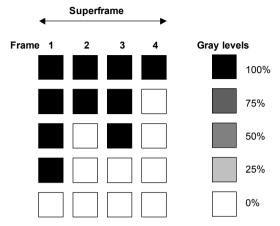

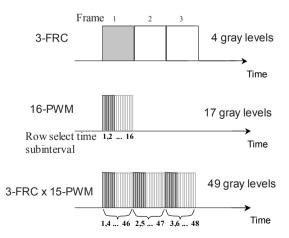

|    |       | 3.4.2 Pulse Width Modulation                            | 100 |

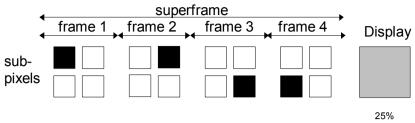

|    |       | 3.4.3 Frame Rate Control                                | 101 |

|    |       | 3.4.4 Mixed Techniques                                  | 102 |

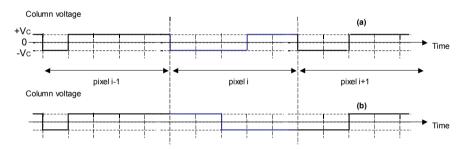

|    |       | 3.4.5 Column Pulse Height Modulation                    | 103 |

|    |       | 3.4.6 Row Pulse Height Modulation                       | 104 |

|    | 3.5   | Concluding Remarks                                      | 104 |

|    | Refe  | rences                                                  | 106 |

| 4. | Drive | ers for Passive-Matrix LCDs                             | 109 |

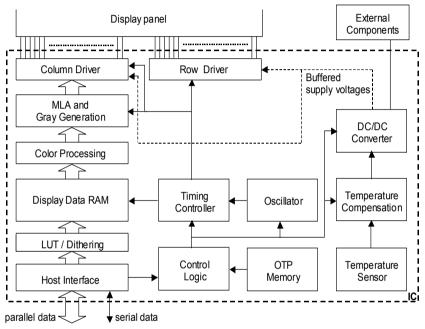

|    | 4.1   | Driver Architecture                                     | 109 |

|    | 4.2   | Host Interface                                          | 111 |

|    |       | 4.2.1 Interfaces                                        | 111 |

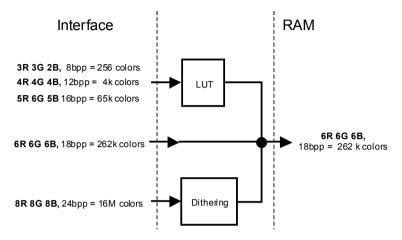

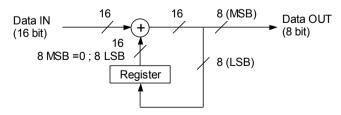

|    |       | 4.2.2 LUT/Dithering                                     | 112 |

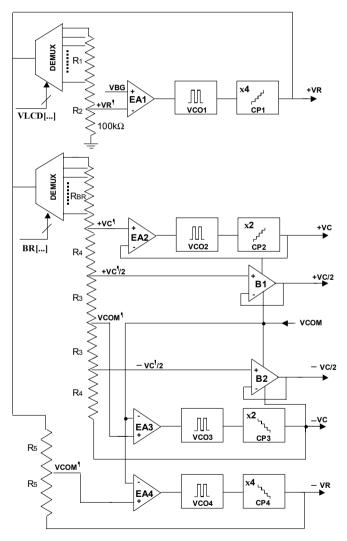

|    | 4.3   | Power Manager                                           | 114 |

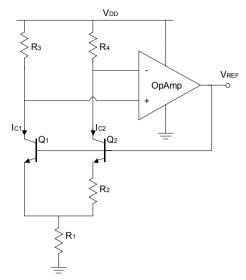

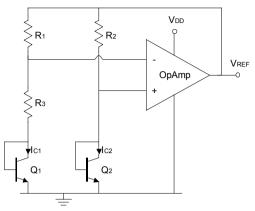

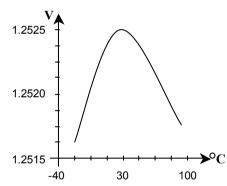

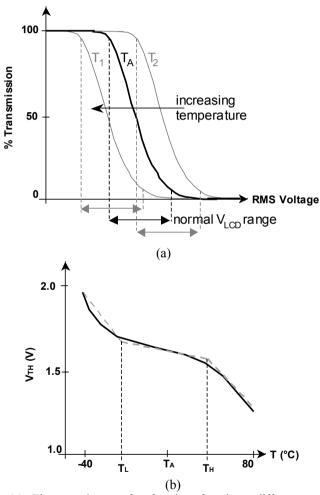

|    |       | 4.3.1 Temperature-Compensated Voltage Generator         | 114 |

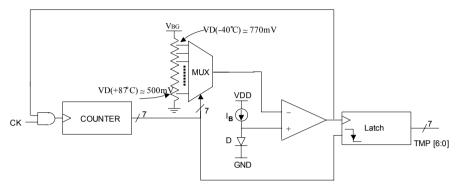

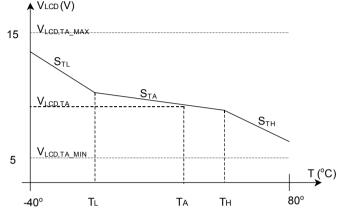

|    |       | 4.3.2 Temperature Sensor                                | 116 |

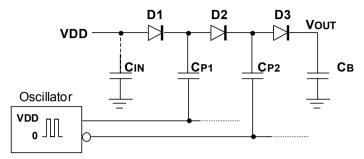

|    |       | 4.3.3 DC/DC Converter                                   | 119 |

|    | 4.4   | Driver Manager                                          | 122 |

|    |       | 4.4.1 One Time Programmable Memory                      | 122 |

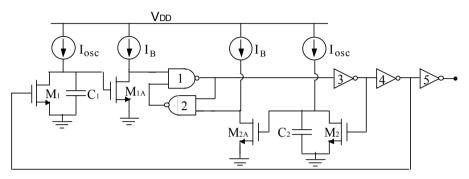

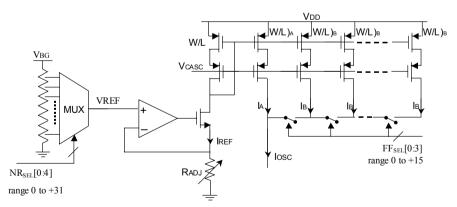

|    |       | 4.4.2 Oscillator (Internal Clock Generator)             | 122 |

|    |       | 4.4.3 Control Logic                                     | 124 |

|    | 4.5   | Image Processing                                        | 125 |

|    |       | 4.5.1 Display Data RAM                                  | 125 |

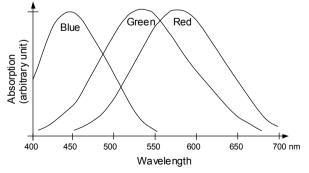

|    |       | 4.5.2 Color Processing                                  | 125 |

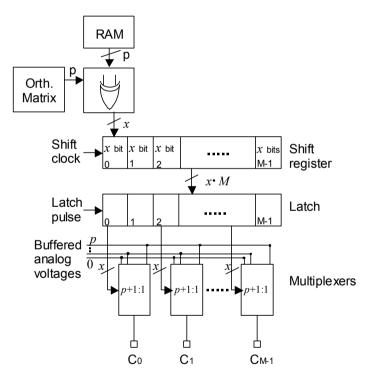

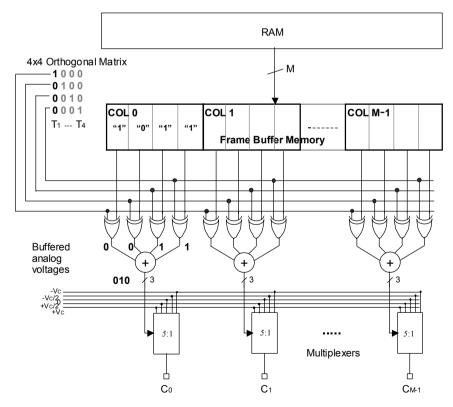

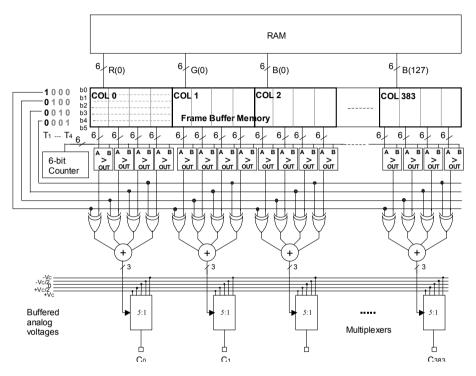

|    |                   | 4.5.3 MLA and Gray Generation                                | 129 |

|----|-------------------|--------------------------------------------------------------|-----|

|    |                   | 4.5.4 Timing Controller (TCON)                               | 129 |

|    | 4.6               | Output Driver                                                | 129 |

|    |                   | 4.6.1 Row Drivers                                            | 129 |

|    |                   | 4.6.2 Column Drivers                                         | 130 |

|    | 4.7               | Silicon Processes for Display Drivers                        | 133 |

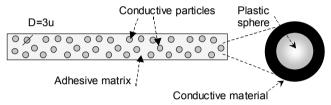

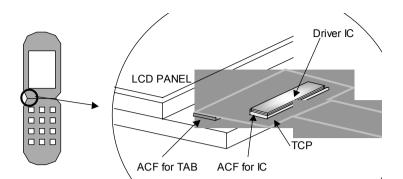

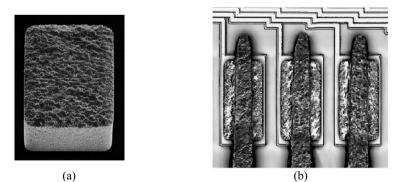

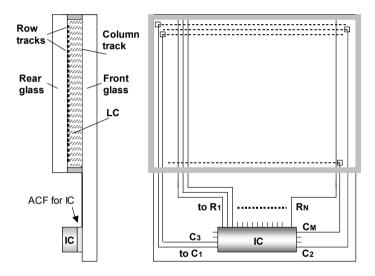

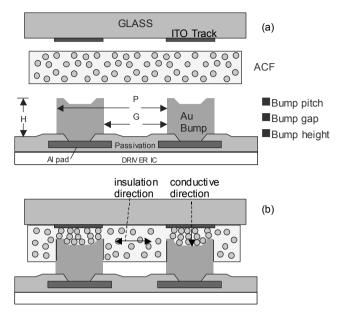

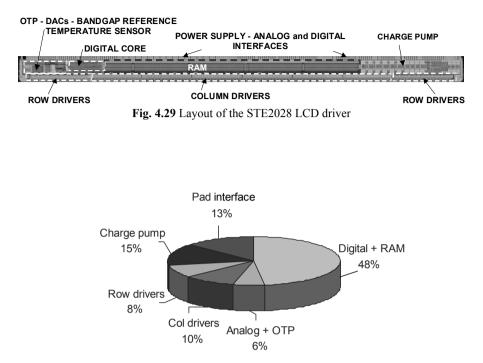

|    |                   | Packaging and Assembling Techniques                          | 135 |

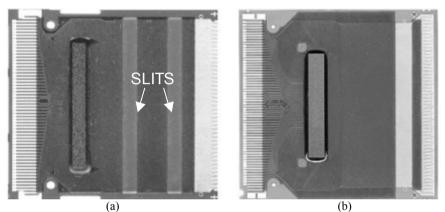

|    |                   | 4.8.1 Chip on Flex                                           | 136 |

|    |                   | 4.8.2 Chip on Glass                                          | 138 |

|    | 4.9               | Concluding Remarks                                           | 139 |

|    |                   | erences                                                      | 141 |

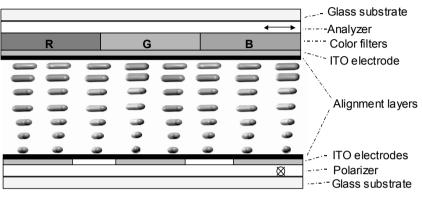

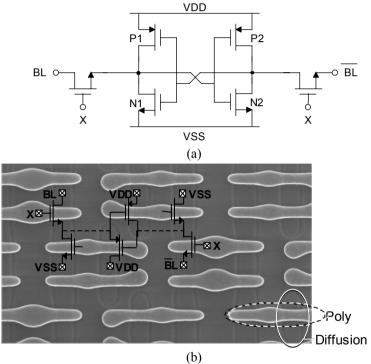

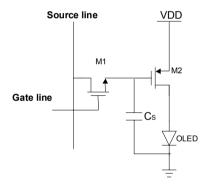

| 5. | Acti              | ve Matrix LCDS and Their Addressing Techniques               | 145 |

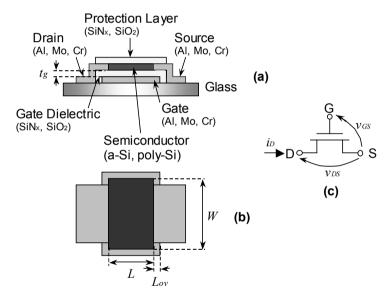

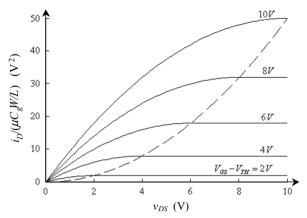

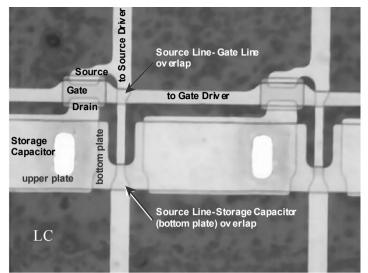

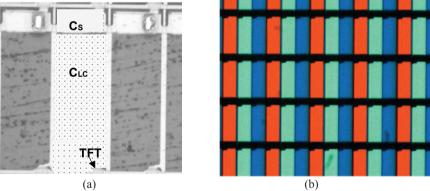

|    | 5.1               | Thin Film Transistors                                        | 146 |

|    |                   | 5.1.1 a-Si TFT                                               | 149 |

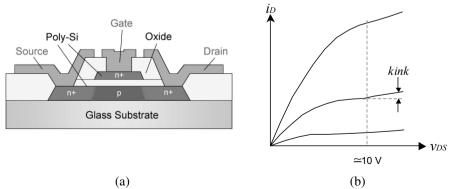

|    |                   | 5.1.2 Poly-Si TFT                                            | 149 |

|    |                   | 5.1.3 Further comparison of a-Si and poly-Si TFT performance | 151 |

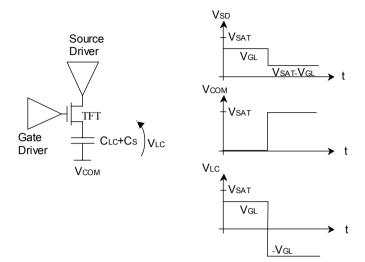

|    |                   | Structure of an Amlcd Panel                                  | 152 |

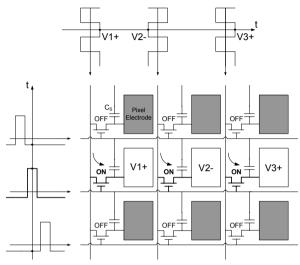

|    | 5.3               | General Considerations                                       | 154 |

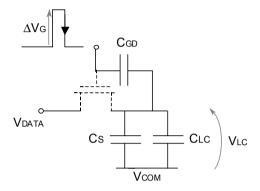

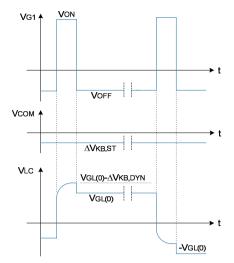

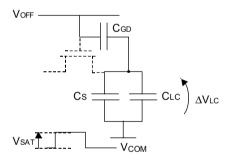

|    |                   | 5.3.1 Kickback                                               | 157 |

|    |                   | 5.3.2 RC Delay and Pre-emphasis Driving Method               | 159 |

|    | 5.4               | Crosstalk Reduction and Polarity Inversion Techniques        | 162 |

|    |                   | 5.4.1 Crosstalk in AMLCDs                                    | 162 |

|    |                   | 5.4.2 Power Analysis of Polarity-Inversion Techniques        | 168 |

|    | 5.5               | Kickback Compensation Methods                                | 169 |

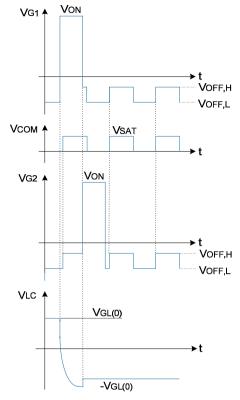

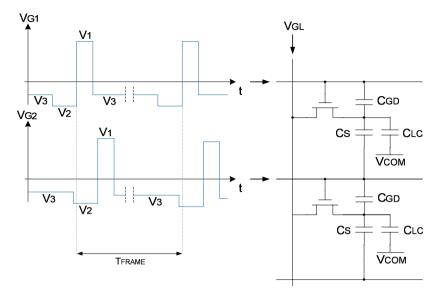

|    |                   | 5.5.1 2-Level Driving                                        | 170 |

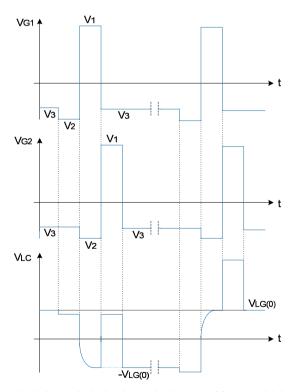

|    |                   | 5.5.2 V <sub>COM</sub> Switching                             | 172 |

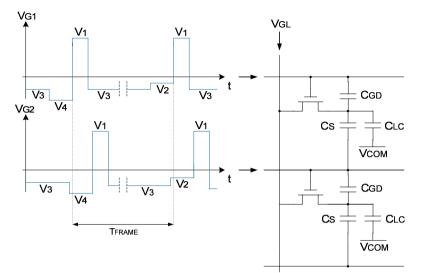

|    |                   | 5.5.3 3-Level Driving                                        | 176 |

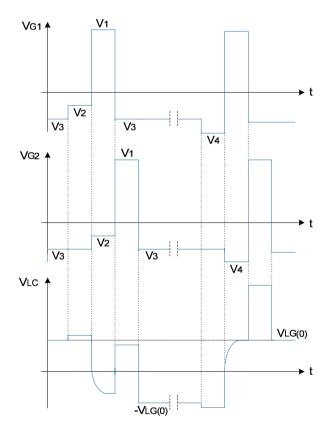

|    | - /               | 5.5.4 4-Level Driving                                        | 179 |

|    |                   | Concluding Remarks                                           | 182 |

|    | Ref               | erences                                                      | 184 |

| 6. |                   | ers for Active-Matrix LCDs                                   | 189 |

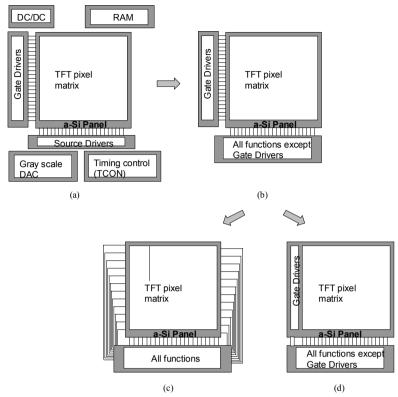

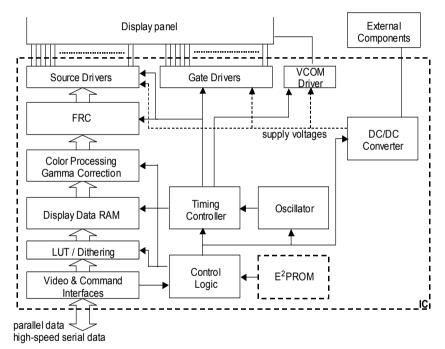

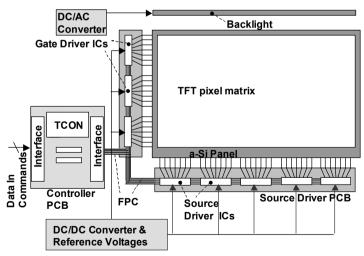

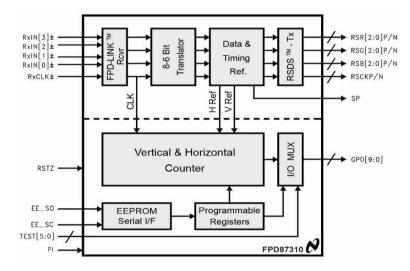

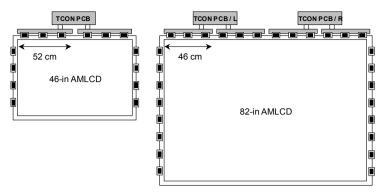

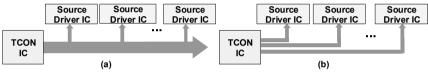

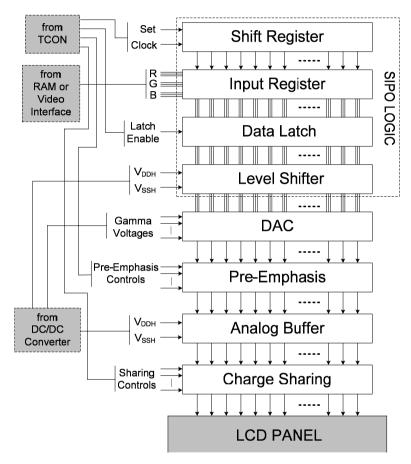

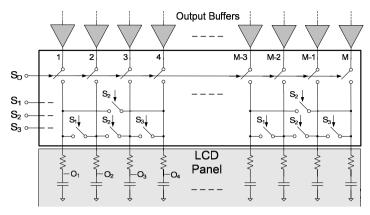

|    | 6.1               | Amled Driver Architectures                                   | 190 |

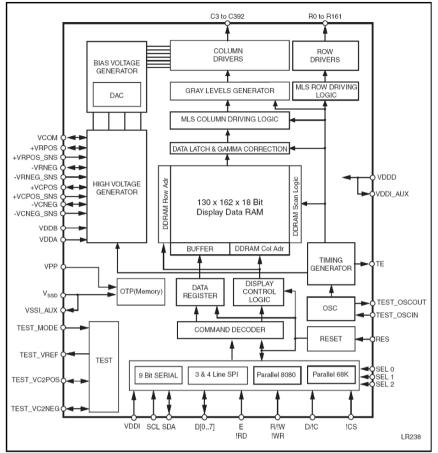

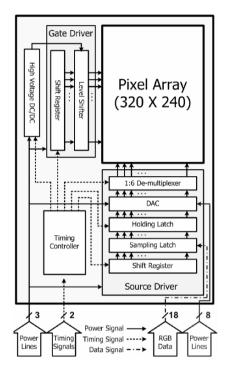

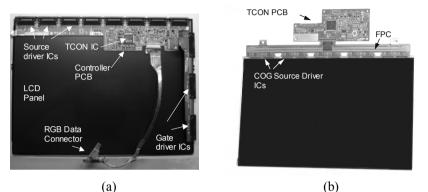

|    |                   | 6.1.1 Driver Architecture for Small-area a-Si Panels         | 190 |

|    |                   | 6.1.2 Driver Architecture for LTPS Panels                    | 192 |

|    | <i>(</i> <b>)</b> | 6.1.3 Driver Architecture for Large-area Panels              | 195 |

|    | 6.2               | Video Interfaces                                             | 198 |

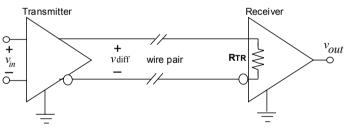

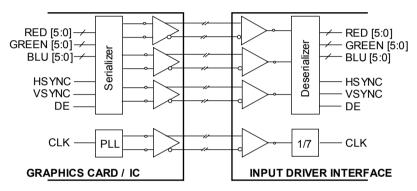

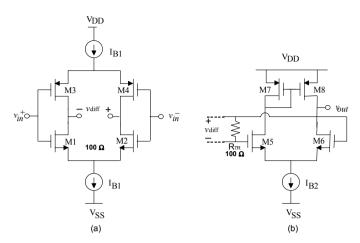

|    | <i>(</i> <b>)</b> | 6.2.1 Low Voltage Differential Signalling                    | 199 |

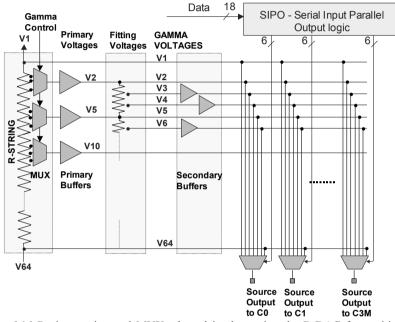

|    | 6.3               |                                                              | 203 |

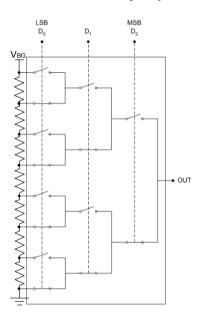

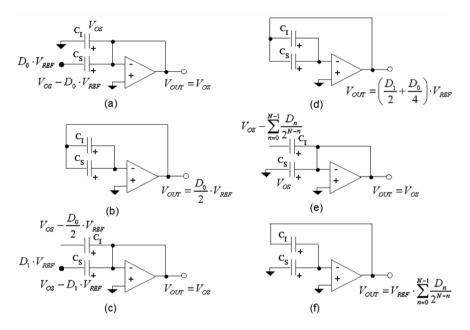

|    |                   | 6.3.1 DACs                                                   | 204 |

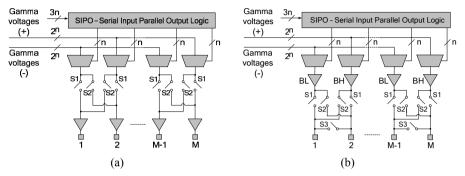

|    |                   | 6.3.2 Polarity Inversion                                     | 211 |

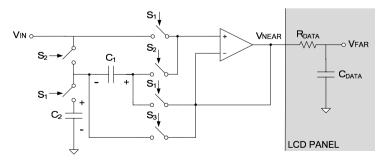

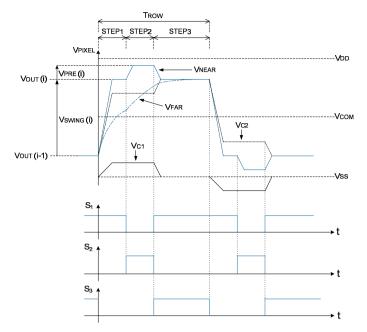

|    |                   | 6.3.3 Pre-emphasis                                           | 212 |

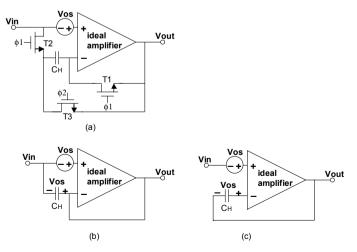

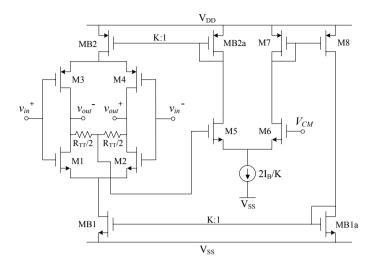

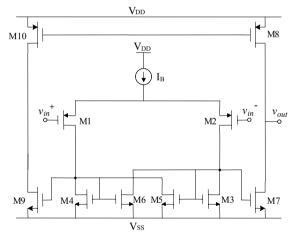

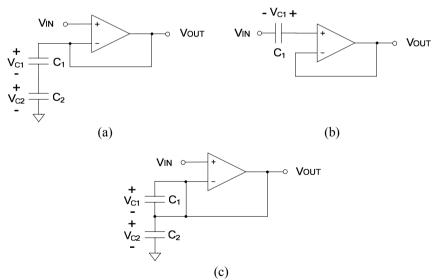

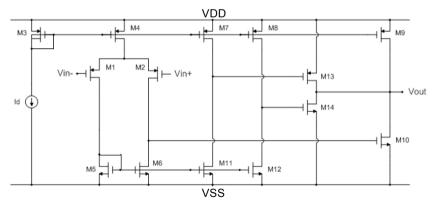

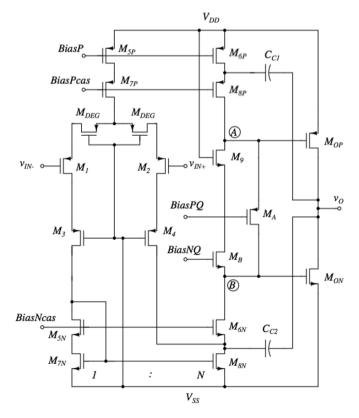

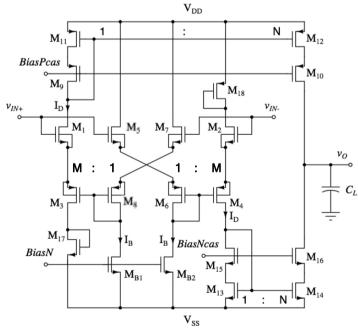

|    |                   | 6.3.4 Analog Buffers                                         | 215 |

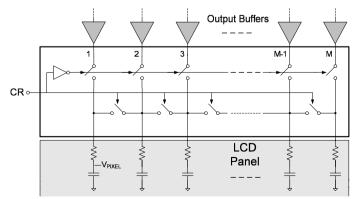

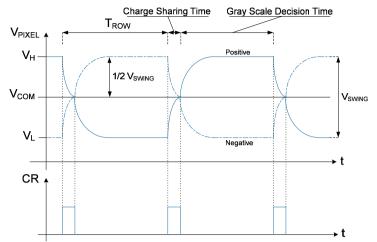

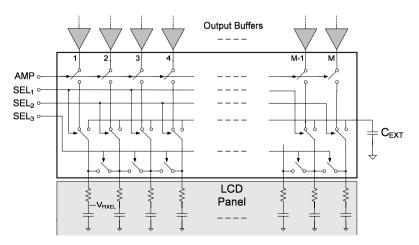

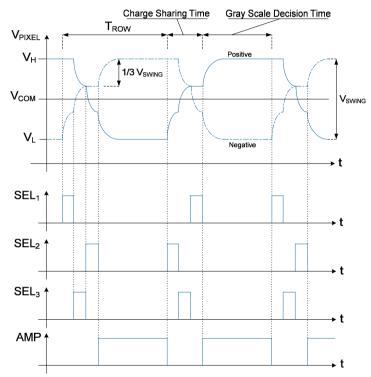

|    | 6.4               | 6.3.5 Charge Sharing                                         | 218 |

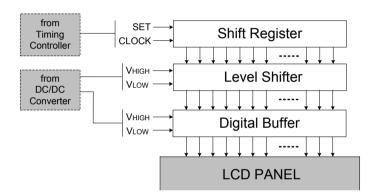

|    | 6.4               |                                                              | 222 |

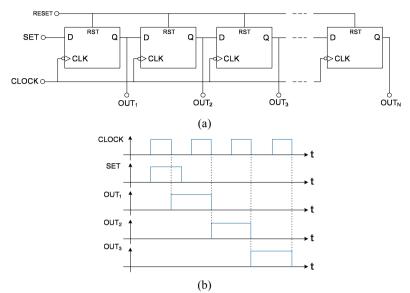

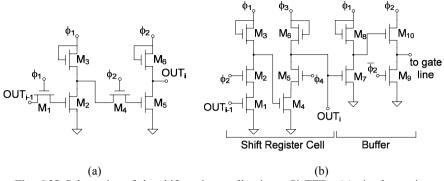

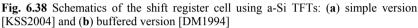

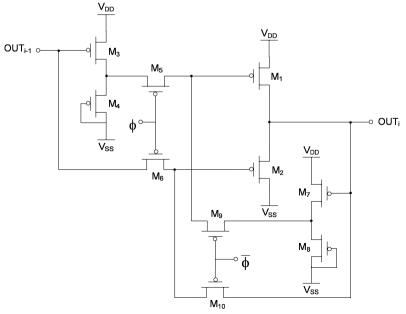

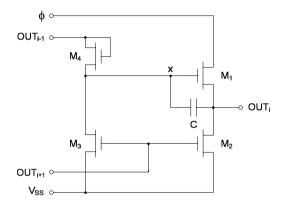

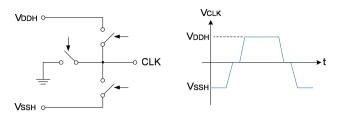

|    |                   | 6.4.1 Shift Registers                                        | 222 |

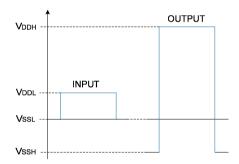

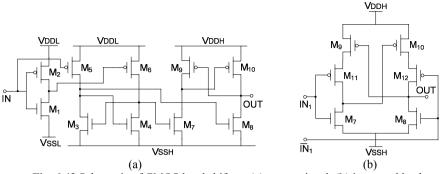

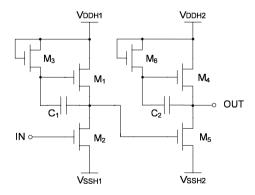

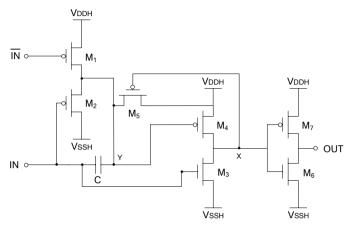

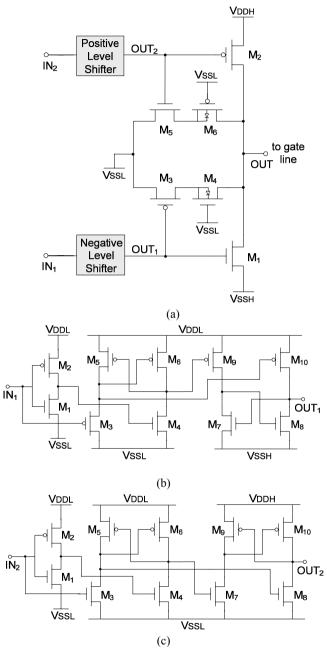

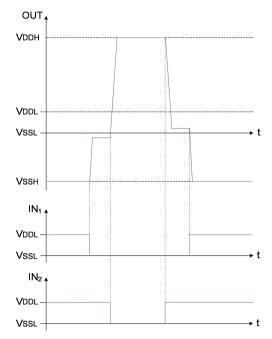

|         | <ul><li>6.4.2 Level Shifters</li><li>6.4.3 Digital Buffers</li></ul> | 226<br>228 |

|---------|----------------------------------------------------------------------|------------|

| Ref     | erences                                                              | 220        |

| 7. Char | ge Pumps for LCD Drivers                                             | 237        |

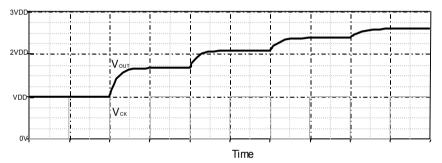

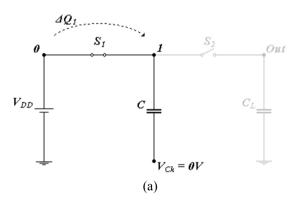

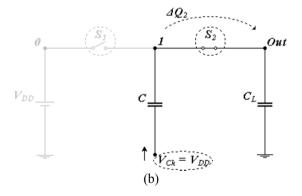

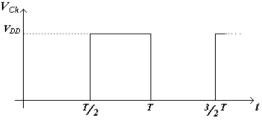

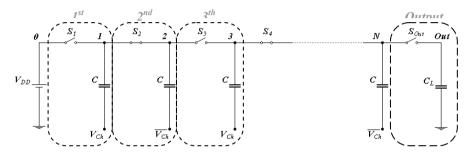

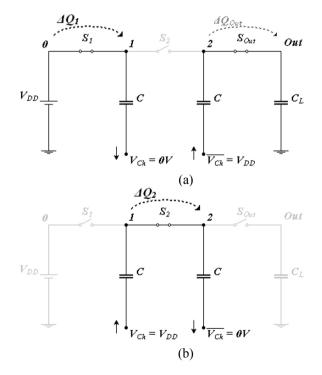

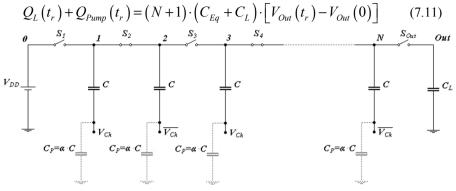

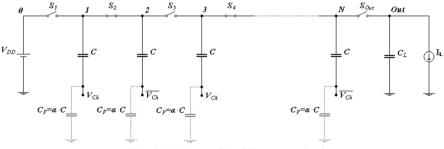

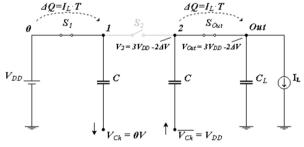

| 7.1     | Analysis of the Charge Pump with a Pure Capacitive Load              | 238        |

|         | 7.1.1 One-stage Charge Pump                                          | 238        |

|         | 7.1.2 N-stage Charge Pump                                            | 239        |

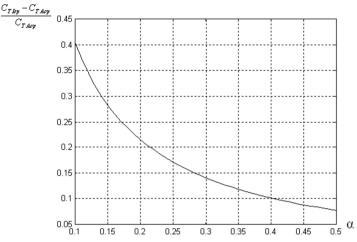

|         | 7.1.3 Charge Pump Parameters                                         | 241        |

| 7.2     | Optimized Design of the Charge Pump with a Pure                      | 243        |

|         | Capacitive Load                                                      |            |

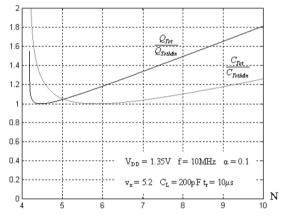

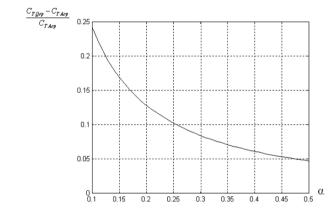

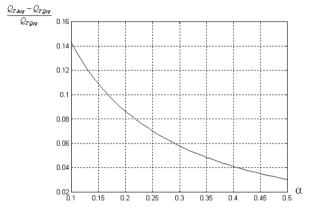

|         | 7.2.1 Minimizing Area Occupation and Rise Time                       | 244        |

|         | 7.2.2 Minimizing Charge Consumption                                  | 245        |

|         | 7.2.3 Comparison between the Optimized Design Strategies             | 246        |

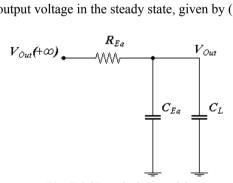

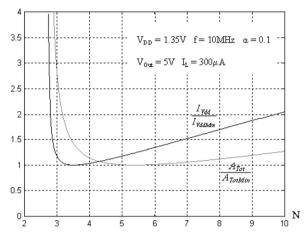

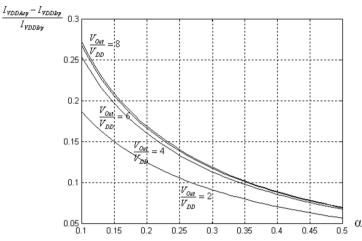

| 7.3     | Analysis of the Charge Pump with a Current Load                      | 248        |

| 7.4     | Optimized Design of the Charge Pump With a Current Load              | 251        |

|         | 7.4.1 Minimizing Area Occupation                                     | 252        |

|         | 7.4.2 Minimizing Current (Power) Consumption                         | 252        |

|         | 7.4.3 Comparison between the Optimized Design Strategies             | 253        |

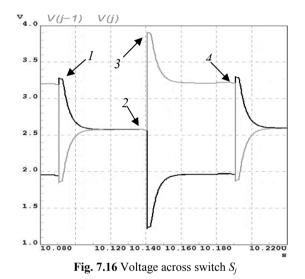

| 7.5     | Voltages In a CP with a Current Load                                 | 255        |

|         | 7.5.1 Evaluation of Voltages in the Inner Nodes                      | 255        |

|         | 7.5.2 Behavior of the Voltages Across the Switches                   | 256        |

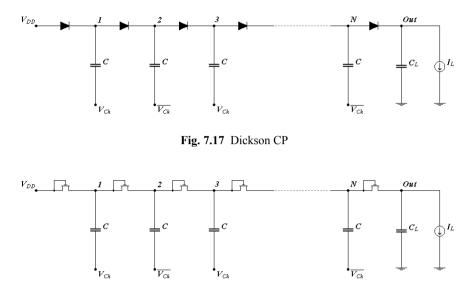

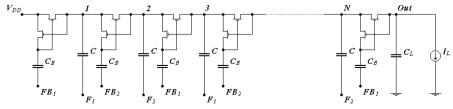

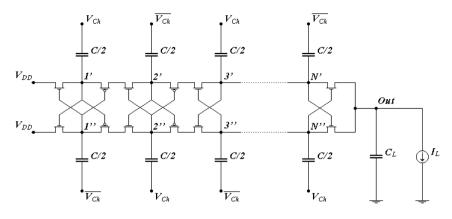

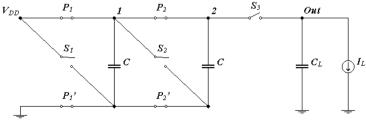

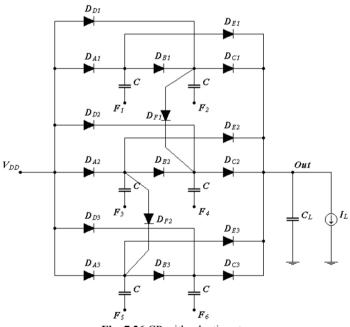

| 7.6     | Charge Pump Topologies                                               | 257        |

|         | 7.6.1 The Dickson Charge Pump                                        | 257        |

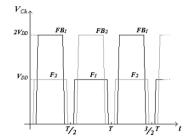

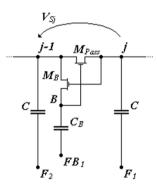

|         | 7.6.2 The Bootstrap Charge Pump                                      | 258        |

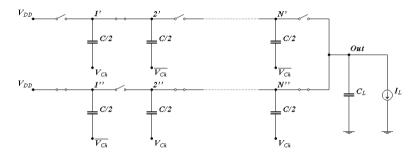

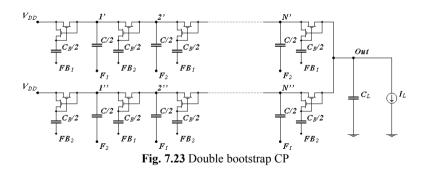

|         | 7.6.3 Double Charge Pumps                                            | 260        |

|         | 7.6.4 Series-Parallel Charge Pumps                                   | 261        |

|         | 7.6.5 Charge Pumps with Adaptive Number of Stages                    | 262        |

| 7.7     | Concluding Remarks                                                   | 263        |

| Ref     | erences                                                              | 264        |

| Append  | lix A – Flat Panel Displays                                          | 267        |

| Append  | lix B – Display Specifications                                       | 277        |

|         | lix C – Matrices for MLA                                             | 281        |

|         | lix D – Color Perception and Description                             | 285        |

| About   | the Authors                                                          | 289        |

| Index   |                                                                      | 291        |

### Forewords

The origins of this book can be found in the scientific collaboration (officially started in March 2003) between Francesco Pulvirenti and me. Besides its obvious technical aim, this collaboration has produced eighteen theses for second-level laurea degree in electronic engineering and fifteen theses for first level laurea degree in electronic engineering. It has given many students the possibility to work within a skilled and experienced design team in a friendly environment, while measuring their strengths against advanced and exciting microelectronic issues. Many of these students are now appreciated designers working all over the world. One of these graduate students was David Joseph Roger Cristaldi, who has just completed his Ph.D. course program.

This book has been written also to leave the marks of this hard work, commitment, respect, and friendship.

Salvatore Pennisi

The activity on Display Drivers started in 1999 when the former CEO of STMicroelectronics, Pasquale Pistorio, and the General Manager of TECDIS (a company of passive displays based in Chatillon, Italy), Ettore Morezzi, decided to create a joint-venture, called DORA, with the purpose to design display drivers. At the beginning this activity was managed by Roberto Gariboldi, today site manager of DORA design center, now based in Aosta (Italy) and by Giuseppe Collé, today quality assurance manager in EM Microelectronics based in Marin (Switzerland).

Starting from January 2001, Pietro Menniti, General Manager of the Industrial and Power Supply Division, now called Industrial and Power Conversion Division, involved me in the design activity. At the beginning I had a team of about 15 people, shared between the DORA design center, originally based in Chatillon, and the STMicroelectronics Catania (Italy) site.

This new challenging adventure started with the contribution and thrust of all the main actors: Roberto, Giuseppe and Pietro. A huge support to my activity came also from Maria Rosa Borghi, Design Director of the Industrial and Power Supply Division, based in Castelletto (Italy) and Mario Paparo, Director of the TPA (Telecommunication, Peripheral and Automotive) R&D team based in Catania. Today Maria Rosa is still covering the same position, while Mario is managing the Automotive R&D team in Shenzen (China).

My traveling from Catania to Agrate (Italy) and Chatillon became more and more frequent, and I used to spend at least one week a month in Chatillon. During my staying in Chatillon I felt very comfortable there thanks to Giuseppe support and his frequent invitations to dinner with his family. Even the members of the design team Alberto Iorio, Roberto Aletti, Mara Concolato, Riccardo Lavorerio, Ivo Pannizzo and Leonardo Sala became soon my friends sharing all efforts and satisfactions. We used to spend our evenings in a restaurant eating grilled steaks, smoking cigars and drinking some good whisky.

The first product developed under my responsibility was the STE2002, an 81row×128-column driver for monochrome displays designed in 0.5- $\mu$ m lithography. We sold several millions units for many years, but the best seller among the monochrome display drivers was the STE6596, a 65×96 driver for Nokia Mobile Phones, designed in the same lithography.

At that time, the business of those products was under the Industrial Business Unit, managed by Alberto De Marco, now director of the Health Care Business Unit in the MAHRS Division. The marketing responsible was Luca Rodeschini.

After the reorganization occurred in ST at the end of 2003, all the activity moved into the new Display Division, which grouped three main businesses: CRTs, large size and small size flat panel displays. The Division was managed by Philippe Berger, who was based in Grenoble with most of the divisional staff members. Luca Rodeschini became the responsible of the small size display Business Unit. He was based in Agrate together with the BU program managers and most of the marketing and application teams.

In this new context I had the responsibility of the design activity for small size display drivers. The design team suddenly grew to 45 people, based in Grenoble (France), Aosta and Catania; the Aosta team had moved from Chatillon.

The team in Grenoble was technically prepared and autonomous. Before my arrival it was managed by Olivier Le-Briz, who took the responsibility of the divisional R&D team continuing to guarantee a great support to the design activity. I was very lucky as I found skilled people with consolidated know-how in OLED design and application. Celine Mas had the leadership of most of the projects developed in Grenoble and the responsibility of the analog team. Olivier Scouarnec had the responsibility of the digital design and the related team. Christian Michon had the responsibility of the back-end activity and the related team.

In Catania, most of the team members had worked with me since before the beginning of the activity on display drivers, thus we were well tuned as a diapason. Gregorio Bontempo was my deputy and one of the first pioneer in the display driver design; he left the company in 2004 to be closer to his family and now he is a high school teacher of electronics. Salvo Pappalardo and Santo Ilardo became respectively the responsible of the Analog and Digital design teams. Tiziana Signorelli managed alternatively the Memory blocks for all devices and the Trocadero project. At the end of 2003 other colleagues joined my team: in particular, Bruno Cavallaro and Amedeo La Scala were respectively the project leaders of the Caravelle and Videophone projects. This is of course only a rough and limited description of the activity and role of each member of my design teams.

In the Display Division the design activity suddenly grew, leading to the development of drivers for OLED and Active Matrix LCD technologies. We developed several drivers for the above mentioned technologies, and two of them are today still in production: the STE2028, a  $162 \times 132$  RGB driver, 262k colors, for AMLCDs developed in 0.18-µm lithography, nicknamed Caravelle mounted in a display for Nokia 6070 model mobile phone, and the STE2102, a  $240 \times 320$  RGB

driver, 262k colors, for AMLCDs developed in 0.18-µm lithography, nicknamed Videophone.

Since the activity was spread in many sites, it was perceived as an additional incentive and motivation. Everybody intensified traveling in order to keep solid and fresh contacts with the other teams. I remember the past years as a wonderful period of my professional life. I had the opportunity to meet and work with important people in the display industry such as Marshall J. Bell, staff engineer of Flat Panel Display Group in National Semiconductor. Ken Foo, Manager of Platform Display Module and Driver ICs development in Motorola. Atsunari Tsuda, Manager of Platform Display Module development in Sanyo-Epson.

The design activity was strictly linked to the development of new technologies and the interaction with the technology department was intensified. Many skilled people worked for the purpose, among them the key leaders were: Enrico Laurin, responsible of the development of the HCMOS5 technology, in 0.5-µm lithography, and Giuseppe Croce, responsible of the development of the HVG6 and HVG8 technologies, respectively in 0.35-µm and 0.18-µm lithography.

Among the sale offices visited during my travels, the one in Japan remains for me an indelible experience for the human qualities of the people met there: Kamiya Akikatsu, responsible of the Photovoltaic team, Eric Benoit, marketing manager and Matsuo Takahiro, application manager. When the activity was slowing down Eric went back to Grenoble and, one year later, Matsuo left the company.

During these years I have had a friend and companion of adventure, who has supported me in all technical issues, with whom I have shared many moments of my private and professional life: prof. Pennisi, with whom, in conclusion of the activity on the display drivers, I accepted to write this book.

I am proud to have worked with all these persons. For the sake of conciseness, I have been obliged to shrink the wide list of people really involved and contacted during the intense activity on display drivers. However, I cannot omit to report my collaborators not mentioned yet, most of them still working with me: Michele Battista, Mirko Dondini, Sergio Fa', Laurent Ferchaud, Cinzia Ferrara, Salvatore Di Fazio, Basilio Filocamo, Angela Gambina, Marco Giuffrida, Corinne Ianigro, Rene Krawiec, Pascal Lelievre, Massimiliano Licciardello, Igor Lisciandra, Antonio Maimone, Rosario Murabito, Roberto Nicolosi, Nicola Nigido, Rosalba Pani, Maurizio Patane', Danika Perrin, Vincenzo Petitto, Salvatore Privitera, Salvatore Puglisi, Domenico Ragonese, Massimiliano Ragusa, Regis Rousset, Francesco Rua', Vincenzo Sambataro, Massimo Sorbera, Angelo Scuderi, Remi Tores.

I am too emotionally involved to tell my opinion on this story, but I leave the reader to judge the results. In less than seven years we developed 3 new technologies and more than 20 display drivers, most of them industrialized and produced with revenue of hundreds million dollars.

In June 2007 I joint back the Industrial and Power Conversion Division, with most of the design team based in Catania. Then Pietro Menniti gave me a new challenging adventure: developing new products for photovoltaic applications.

Few weeks before my moving back in the I&PC Division, the activity on display drivers was stopped for strategic reasons.

Francesco Pulvirenti

## Preface

Liquid Crystals (LCs) represent a paradigm studied and exploited in several different contexts. For example, the membrane of a biological cell is made up of *lyotropic* type LCs which are therefore broadly investigated in the fields of biochemistry, biophysics, and bionics. LCs are also studied in the area of pattern-forming mechanisms and in the bifurcation theory [C1991, BK1996, TMBC2001], to understand and describe nature structures: snowflakes, honeycomb, and animal coat markings are just some examples. They are preferred to standard isotropic fluids, because they provide more stable and larger regions with regular patterns, and are therefore more easily observable and controllable (by means of electric and magnetic fields). LCs are also used in the field of image processing and analysis. The diffusion of LCs is so wide all over the world that studies on their reuse, recycling, and recovery, as well as on their toxicity, have been performed. As a consequence, LC producers agreed to market no severely toxic, carcinogenic or mutagenic LC substances [MSB2004].

Nevertheless, LCs are certainly better known by most of us for their use in the realization of electronic displays. Flat Panel Displays (FPDs) of palm-top computers, notebook-PCs, Personal Digital Assistants (PDAs), mobile/smart phones, video games, desktop monitors, TV-sets, projectors, view finders for digital cameras/camcorders, CD/MP3/MP4 players, GPS navigation systems, airplane cockpits, e-Books, electronic labels (for supermarket shelves), photocopy and medical equipments, are the most noteworthy applications. FPDs are the principal medium actually linking people and information: they have enabled applications otherwise impossible<sup>1</sup> which are limited only by the designer fantasy.

The multi-billion-dollar Liquid Crystal Display (LCD) industry has been rapidly growing since 1971. Technological progress has enabled wide-ranging-size commercial products with diagonal size below 1 in. to 40 in. and more. This is nowadays the mainstream display technology playing an important role in the economy of many Asian countries. LCDs dominate the scene in portable electronic equipments and notebook computers. LCD monitors for desktop computers have almost completely replaced CRTs (cathode-ray-tubes). Furthermore, LCDs have recently surpassed CRTs even for television technology, outselling Plasma Displays by more than 7 to 1.

<sup>&</sup>lt;sup>1</sup>Not only compact hand-held equipments have taken advantage of FPDs, but also large screens. For instance, high definition TV (HDTV) has received widespread acceptance only with the availability of FPDs larger than 40 in. Indeed, large-screen CRT-based displays, both direct view and projection, are far too bulky for the average home.

This explosion is the consequence of concurrent and decisive research efforts in:

- 1. Materials (LC mixtures, polarizer films, and color pigments);

- 2. Processing technologies. The size of the glass substrates increased from  $320 \text{ mm} \times 400 \text{ mm}$  in 1989 (Generation 1) to 2160 mm  $\times$  2460 mm in 2006 (Generation 8). Corning Incorporated,<sup>2</sup> the world leader in specialty glass and ceramics, and the dominant supplier to the LCD industry, is going to begin the mass production of the Generation 10 glass substrates (2850 mm  $\times$  3050 mm) by 2010.

- 3. Micro-optics and precision machinery designs.

- 4. Electronic designs (driver ICs, ASIC ICs, image processing, color management);

While the above key elements are still continuously improving, other relevant research issues are emerging. Better electrical power utilization, better material utilization and environmental designs to save natural resources, are only some of the new topics. Besides, the LCD panels are migrating from *simple* output devices to *two-way* communication devices with many functions as human-machine interface (*integrated* touch panels are under development with signal-sensing pixels without an additional touch-pad attached on the LCD panel) [L2007].

Despite many alternative display technologies have been developed or may emerge in the near future, their chances of success are rather weak because of the huge investments in massive worldwide LCD business infrastructures made by the few dominating enterprises. OLED (Organic Light Emitting Diodes) is the only technology that can compete in picture quality, viewing angle issues and low power, but, to be competitive with LCDs, further reduction in cost, increase in throughput, increase in longevity, and scaling to larger sizes will be needed [V2008].

The sudden increase of interest in Liquid Crystals has been accompanied also by the publication of numerous books related to the topic. The reader may thus wonder why writing another one. The answer is that most of these books are focused on the LC materials and/or LCD technologies and many are written from the physics or chemistry point of view, or even from an historical perspective. This book, in contrast, deals with LCDs from the *electronic engineering* point of view and is specifically focused on those reliable techniques, architectures, and design solutions amenable to efficiently design driving circuits for such systems. To this aim the book, after providing an introduction to the physical-chemical properties of LC substances, their evolution and application to LCDs, converges to the examination and in-depth explanation of addressing techniques and suitable driving schemes for passive-matrix and active-matrix LCDs.

<sup>&</sup>lt;sup>2</sup>Since 2000, the Corning glass size has doubled about every 1.5 years by following Moore's law also for LCDs. A number of twelve 30-in. panels can be simultaneously derived from a single Generation-8 motherglass.

LCDs are intrinsically "passive" devices, they are simple light valves. The managing and control of the data to be displayed is relegated to one or more circuits commonly denoted as LCD drivers. The semiconductor market of LCD driver ICs is very competitive, similar to the DRAM aggressive market. Reduction of costs and area is vital, especially for small-size panels. Considering hand-held equipments for consumer electronics, the product life time is very short (1-3 years) and, due to the fast IC price erosion, the major revenues occur only in the first 6 months. These considerations mandate for very short development cycles, leaving no possibility of failure. Having a deep comprehension of the technology, the existing architectures and design techniques is fundamental for the implementation of next generation twoway display devices and to gain insight into the future of the industry.

In this rapidly evolving scenario, *Liquid Crystal Display Drivers* is focused on the presentation of practical approaches and circuit solutions regularly adopted for mass production, but also unconventional and emerging techniques are mentioned. Even if the attention is mainly paid on LCDs, the topics treated have more general validity and find application also in alternative display technologies (OLEDs, Electrophoretic Displays, etc.).

The book is not only a reference for engineers and system integrators who work in the field of displays with their future development, but it is written also for scientific researchers, educators and students. It is a valuable resource for advanced undergraduate and graduate students attending display systems courses, and it may prove interesting even for a non-expert in the field, as it is reasonably simply written without referring to unnecessary mathematics and by privileging the intuitive description. Besides, we have tried to put in evidence the men and the ideas behind the things they produced. To improve clarity and for the sake of completeness we also included 22 Photos, 20 Tables and more than 200 Figures and 400 bibliographic references.

Writing a book of this nature has also required extensive discussions with colleagues, designers and technologists. Our thanks to: Giuseppe Musumarra, Giuseppe Falci, Gino Sorbello, professors at the University of Catania. A special thank is due to Santo Ilardo and Amedeo La Scala at STMicroelectronics, to Giuseppe Collè at EM Microelectronics, and to Prof. Ingo Dierking for his photographs, as well as the people at Merck, Sharp and Corning, who have kindly and positively replied to our several requests. We are also indebted to professors Gaetano Palumbo and Domenico Pappalardo for their contributed chapter on charge pumps. Finally, we would gratefully acknowledge the financial support of STMicroelectronics.

> There are no limits to the creativity of the display developers or to the tools available for discovery and development. The challenge is to find the right combination of display performance and manufacturing cost to make FPDs attractive and affordable to billions of people, which in turn enrich their lives through technology [M2002].

> > Francesco Pulvirenti

Catania, Italy

Catania, Italy

Catania, Italy

David J.R. Cristaldi Salvatore Pennisi

#### References

- [BK1996] A. Buka and L. Kramer, *Pattern Formation in Liquid Crystals*, Springer, Berlin, 1996.

- [C1991] P.E. Cladis, *Pattern Formation in Complex Dissipative Systems*, World Scientific, Singapore, 1991.

- [L2007] C.T. Liu, "Revolution of the TFT LCD Technology," *IEEE Journal of Display Technology*, Vol. 3, No. 4, pp. 342–350, 2007.

- [M2002] D.E. Mentley, "State of Flat-Panel Display Technology and Future Trends," *Proceedings of the IEEE*, Vol. 90, No. 4, pp. 453–459, 2002.

- [MSB2004] R. Martin, B. Simon-Hettich, and W. Becker, "Safety of Liquid Crystals (LCs) and Recycling of Liquid Crystal Displays (LCDs) in Compliance with WEEE," *Merck Liquid Crystal Newsletter*, No. 19, pp. 27–30, 2004.

- [TBM2001] S.J. Tavener, G.I. Blake, T. Mullin, K.A. Cliffe, "A Numerical Bifurcation Study of Electrohydrodynamic Convection in Nematic Liquid Crystals," Phys. Rev. E, Vol. 63, No. 1, pp. 1-12, 2001.

- [V2008] R.J. Visser, "The Business of Displays: OLED Displays on the Verge of Commercial Breakthrough," *Journal of the SID*, Vol. 5, No. 4, p. 8, pp. 102–103, 2008.

# Chapter 1

# Liquid Crystals

#### Discovery, Classification, and Physics

This chapter begins with the early history of liquid crystals (LCs). Subsequently, a brief classification and introduction to the physics of LCs and their electro-optic properties is discussed, particularly, for those materials suitable for display applications.

It will emerge that the initial studies on LCs involve botanists, chemists, physicists (and even mineralogists and mathematicians) almost exclusively from Europe. The interested reader is referred to [SDS2004] for a thorough report concerning the history of LCs and for an excellent collection and translation in English of the fundamental documents in the field (most of which were originally written in German and French). Other important sources are, ordered by publication year, [K1973, H1984, K1988, KK1989, S1989, V1992, K2000, K2002, C2005].

Complete treatment of the physical LCs properties can be found in [GP1995] (a standard), another source is [DFL2001], a good review of basic properties is presented in [SS1974], optical and electro-optical properties are specifically discussed in [KW1993, BC1994, L2001].

#### 1.1 Early History

Solid, liquid and gaseous states were the only known states of matter before the discovery of LCs. A solid can be either crystalline or amorphous, being the former characterized by a three-dimensional lattice with both long-range positional and orientational atomic order and the latter having only short-range order. When a solid is heated above its melting point, it turns into an isotropic liquid having neither positional nor orientational order, which, after cooling, turns back into a solid.

In 1888,<sup>1</sup> a young Austrian botanist, **Friedrich Reinitzer**, was working at the University of Prague (Prague is now the capital of the Czech Republic, but was then the capital of the province of Bohemia in the Austro-Hungarian empire). In his

<sup>&</sup>lt;sup>1</sup>Nine years later, in 1897, the German scientist Karl F. Braun introduced the first cathode ray tube scanning device.

experiments he was extracting cholesterol from carrots in order to determine its exact chemical formula, and to find whether it was the same compound found in the cells of many animals. At this purpose he isolated from human gallstones two substances we now know as *cholesteryl benzoate*, and *cholesteryl acetate*. Both organic compounds are solid crystalline at room temperature, and he wanted to measure their melting point. When heating the compounds, he noticed the reflection colors of their melts, as had others before him for other cholesterol derivatives. However, he also noted two distinct melting points. The *cholesteryl benzoate* melted at 145.5°C, becoming cloudy and viscous, but rising the temperature to 178.5°C it became isotropic and clear, typical of the liquid state (for this reason this point was lately called **clearing point**; the **melting point**, in which a solid enters the liquid crystalline state, is sometimes called **freezing point**). The phenomenon was reversible. The other substance, the cholesteryl acetate, showed a melting point at 94.8°C and a clearing point at 114.3°C, in this case however, the appearance of colours was observed only once on cooling [SDS2004].

Reinitzer attributed the two-melting-point *anomaly* to the presence of impurities, but after several attempts and specimen refinements, he observed always the same behavior. Unable to explain the phenomenon, he communicated with **Otto Lehmann** a young German physicist.

Lehman studied physics at Strassburg University (contemporary Strasbourg is in France, but at that time, like the rest of the disputed provinces of Alsace and Lorraine, was in Germany). He was fascinated with microscopes and microscopy (his father, schoolmaster, had been an amateur microscopist before him), and to complement his research, Lehmann spent a large amount of time and energy developing and improving (in a series of implementations) his invention, the heating stage microscope, that he called the *crystallization microscope*, Fig. 1.1. This instrument is still standard equipment in liquid crystal research laboratories today.

Fig. 1.1 Lehmann's original hot-stage microscope and some Merck LC substances from 1904. Picture source: Merck KGaA, Corporate History

An epistolary communication between the two scientists produced the first actual investigation of liquid crystals, leading to a fundamental insight into the nature of this new phase of matter.

On 14 March 1888, Reinitzer wrote to Lehmann his, now famous, first 16-page-long letter describing the two melting points:

... just below the second melting temperature,  $178.5 \,^{\circ}$ C, ... violet and blue colors appear, which rapidly vanish as the sample becomes more milk-like turbid, but still fluid. On further cooling, the blue and violet colors reappear, to disappear again as the substance solidifies to form a white crystalline mass.

Along with the letter, Reinitzer sent samples of the two materials.

In 1888, Lehmann was 33. One year later he would become professor of physics at the Technical University of Karlsruhe, as the successor to Heinrich Hertz, who had lately demonstrated experimentally Maxwell's theory of electromagnetism.

Lehmann soon confirmed the observations of the Austrian botanist. At this purpose, the *crystallization microscope* revealed itself extremely useful to understand the behaviour of cholesteryl benzoate, because not only it allowed observations in polarized light, but also enabled *in situ* high temperature observations thanks to its hot stage.

In one of the many correspondences with Reinitzer, Lehmann wrote:

My results confirm your previous observations, which the substance consists of a crystal very soft ... It is completely homogenous and does not contain another liquid, unlike you suggested... It is truly of great interest for physicists that a crystal so soft that it can be called liquid exists.

Lehmann realized that he was dealing with a new state of the matter, between a solid crystal and an isotropic liquid, which appears fluid and turbid and that only certain materials exhibit. He also ascertained that this state shows a double refraction (typical of crystals, see Section 1.3.7). Because the shared properties of both liquids and solids, in a celebrated article of 1889 [L1889], he called these materials, *Fliessende Kristalle* (flowing crystals) or *Schleimig flussige Kristalle* (slimy liquid crystals). Lehmann found materials that even exhibited *three* melting points, he named this additional phase *Kristalline Flüssigkeit* (crystalline fluid) or *Tropfbar flüssige Kristalle* (liquid crystals which form drops). All this researches were organized in an enormous tome, simply entitled "Liquid Crystals" [L1904].

At first, many scientists underestimated the importance of the discovery while others were skeptic and thought that the newly-discovered state was just a mixture of solid and liquid components.

It is interesting to observe that Lehmann asked the support of the **E. Merck**<sup>2</sup> company in Darmstadt, Germany (see again Fig. 1.1), in order to obtain highly pure substances:

<sup>&</sup>lt;sup>2</sup>Since 1904, Merck produced and sold for experimental purposes chemical preparations exhibiting LC properties.

My work in the area of liquid crystals ... also among the experts in this field [remains] misunderstood and unknown. Nobody is able to procure the necessary materials and instruments.

Nevertheless, after the seminal works of Lehmann, new LC substances were continuously discovered. In 1890, Ludwig Gattermann (at that time 30-year-old Assistant Professor at the University of Heidelberg, and that later became Full Professor at the University of Freiburg and a famous organic chemist<sup>3</sup>) published the *first* report of the complete synthesis of one of these substances [GR1890]. The article describes the synthesis of **para-azoxyanisole** (PAA, a liquid crystal at temperature between 116°C to 134°C). The method of synthesis was well defined and relatively easy, and the temperature range was more accessible than in the case of cholesteryl benzoate. These favourable features caused this material to become that of choice for the successive studies in liquid crystal properties. In the subsequent years, the physical chemist Rudolf Schenck of Marburg, recorded new 24 LC compounds. Daniel Vorländer of the University of Halle and his students synthesized hundreds of LC compounds and the first *thermotropic smectic* compound. Even in 1908 he had enough material to be organized in a book [V1908].

In 1909, Lehmann (then 54 and with a recognized reputation) visited Geneva and Paris, giving seminars and experimental demonstrations. This stimulated the formation of a French school of LC science that became important up today. Among those influenced by Lehmann's visit were **George Friedel** and **Charles-Victor Mauguin**.

Friedel, was a crystallographer who formulated basic laws concerning the external morphology and internal structure of crystals. He clarified that LCs have three types of molecular organization: *smectic, nematic,* and *cholesteric* (that will be discussed in Section 1.2) leaving a mark on the science of LCs. Friedel gave Lehmann the responsibility of the initial skepticism of the scientific community, and to avoid misunderstanding he proposed to adopt the term **mesophase** to describe the LC state, or phase. After this work, we now use **mesomorphic** as the attribute related to both features and properties peculiar to this state of matter, and **mesogen** to designate an organic compound able to generate mesophases. Nevertheless, the term liquid crystal continued to be used.

In the introduction of his famous article published in 1922, Friedel wrote [F1922]:

I use the term mesomorphic to designate those states of matter observed by Lehmann in the years following 1889, and for which he conceived the terms liquid crystal and crystalline fluid. Lehmann had the great merit of drawing attention to these materials, but he erred greatly in naming them. The unfortunate names have been repeated again and again over the last 30 years. As a result many people suppose that these substances are merely crystalline materials, albeit rather more

<sup>&</sup>lt;sup>3</sup>Gattermann's textbook *Die Praxis des Organischen Chemikers* (The practice of Organic Chemist) was adopted by generations of students.

fluid than those hitherto known. The exact opposite is the case. Indeed, these materials are infinitely more interesting than they would be if they were simply crystals exhibiting some unexpected degree of fluidity.

On the other side, C. Mauguin, of the École Normale Supérieure, studied the behavior of LC thin layers (of thickness between 10 and 150  $\mu$ m) confined between plates. In his experiments he used also Gattermann's PAA. His achievements are fundamental for the subsequent evolution of the subject. In particular, he examined "birefringent liquid films with a helicoidal structure" and found that an incident linearly polarized beam exits the sample elliptically polarized. Moreover, under certain circumstances the polarization of incident light is twisted (this is the result of what we would now call a twisted nematic cell). He demonstrated that if the ratio of the twist pitch to the wavelength of light is large, the polarization follows the twisting birefringence [M1911a]. Even more significantly, Mauguin established that (magnetic) fields orient liquid crystals [M1911b].

Between 1922 and the World War II, **Carl W. Oseen**,<sup>4</sup> of the University of Uppsala, Sweden, and **Hans Zöcher** of the University of Prague developed a macroscopic mathematical model for the study of liquid crystals and introduced the *order parameter* (see Section 1.3.1) [O1933, Z1933]. Besides, the aligning properties of LCs due to magnetic fields was theoretically analyzed by **Vsevolod Freédericksz** and his group at the Physico-Technical Institute of Leningrad [FZ1929, FZ1933]. After these fundamental works, the scientific community gradually lost interest in LCs, as it was believed that all their relevant features had been discovered.

In the 1950s the works by **Glenn Brown**,<sup>5</sup> from the University of Cincinnati, **George W. Gray**,<sup>6</sup> from the University of Hull, and **Charles Frank**<sup>7</sup> from the University of Bristol led to a renewed interest in liquid crystals [F1958], while **Wilhelm Maier** and **Alfred Saupe**<sup>8</sup> formulated a molecular theory of LCs [MS1958]. It is also worth mentioning that in 1956, a young physicist named **James L. Fergason**, decided that LCs would be the lifetime subject of his research. He

<sup>&</sup>lt;sup>4</sup>C.W. Oseen was professor of mechanics and mathematical physics. He was also influential (and despotic) member of the committee for the Nobel Prize from 1921 to 1944, judging nominations for theoretical physics and in particular atomic physics. He awarded eminent personalities such as Albert Einstein, Niels Bohr, Werner Heisenberg, Erwin Schrödinger and Paul Dirac [F2002].

<sup>&</sup>lt;sup>5</sup>G. Brown learnt about LCs while looking for a research topic for his graduate students. Subsequently, he wrote a review of the existing literature in *Chemical Reviews* [BS1957]. The article was widely read and encouraged Brown to a lifetime study on the LC materials.

<sup>&</sup>lt;sup>6</sup>The work of G.W. Gray was fundamental for the successive development of new highperformance LC materials, see Section 2.3.

<sup>&</sup>lt;sup>7</sup>Sir C. Frank was a physicist interested in crystallography. He wrote only four papers on LCs, and one of them (the 1958 referenced paper) gave him long term recognition. Actually, he recapitulated in part the two previous works of Oseen and Zöcher (who can perhaps be regarded as the father of the Frank-Oseen theory [SDS2004], see Section 1.3.2).

<sup>&</sup>lt;sup>8</sup>A. Saupe was a German physicist who worked also at Kent State University. The Maier-Saupe theory is originated from his diploma thesis elaborated together with his advisor prof. W. Maier in Karlsruhe University.

would become one of the foremost pioneers in this field, and one of the American most prolific living inventors, as we will see in the next chapter.

From the 1960's the *commercial* interest in LCs started to grow, as reported in the next chapter, but the theoretical studies on LCs did not paused, culminating eventually in the 1991 Nobel Prize to **Pierre-Gilles de Gennes**, of College de France, Paris, with the following motivation:

... for discovering that methods developed for studying order phenomena in simple systems can be generalized to more complex forms of matter, in particular to liquid crystals and polymer.

In fact, de Gennes expanded the phase transitions theory of Lev D. Landau [LL1984] into liquid crystals, providing a phenomenological description of molecular order in the LC phases, as well as elastic and hydrodynamic properties. He showed that phase transitions in such seemingly widely-differing physical systems as magnets, liquid crystals, polymer solutions and superconductors can be described analytically in a general unified manner.

To close the section, we include in Fig. 1.2 the picture of some of the scientists involved in the history of LCs and mentioned before.

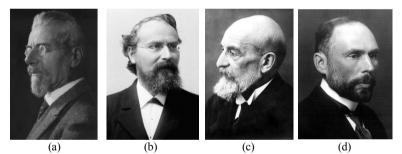

Fig. 1.2 (a) Friedrich Reinitzer (1857–1927), (b) Otto Lehmann (1855–1922), (c) Georges Friedel (1865–1933), (d) Carl W. Oseen (1878–1944), (e) Hans Zöcher (1893–1969), (f) George W. Gray (1926), (g) James L. Fergason (1934), (h) Pierre-Gilles de Gennes (1932–2007). [K1989, K2002]

#### 1.2 Classification

A vast variety of chemical compounds are now known to exhibit one or several liquid crystalline phases. These molecules show significant differences in chemical composition, but they share some common features in chemical and physical properties.

Many concepts discussed in the following are due to Friedel, who, as already mentioned, suggested the liquid crystal classification scheme which is used today.

#### 1.2.1 Cause of Formation

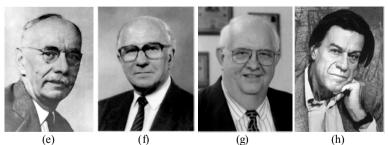

A first classification makes a distinction between **thermotropic** and **lyotropic** LCs, according to the mechanism that initiates the transition to the liquid crystal phase. Most known liquid crystals are produced by varying the temperature of various substances (in particular, by raising the temperature of certain solids or lowering the temperature of certain liquids) and are commonly termed thermotropic. Below the melting point temperature,  $T_{\rm mp}$ , thermotropic liquid crystals are solid, crystalline and anisotropic; as the temperature is raised above the clearing point  $T_{cD}>T_{mp}$ , they are a clear isotropic liquid. Between  $T_{\rm mp}$  and  $T_{\rm cp}$  they are in the liquid crystal mesophase,<sup>9</sup> as illustrated in Fig. 1.3. The process is usually reversible by lowering the temperature, though there may be a small temperature hysteresis (for example,  $T_{mn}$ ) when reducing temperature may be slightly less then  $T_{\rm mp}$  when increasing temperature). The liquid crystals Reinitzer and the early researchers discovered were all thermotropic. Among the thermotropic liquid crystals there are two fundamental classes of substances, those that are **enantiotropic**, which are able to enter the LC state both by cooling a liquid and heating a solid, and those that are **monotropic**, which can enter the LC state via one or the other of those methods, but not both.

Fig. 1.3 The temperature range of a thermotropic LC is comprised between the melting and clearing points

The other fundamental way to make a substance enter a liquid crystalline phase is by the action of a solvent, and the concentration of the solution is primarily responsible for the occurring phase. More specifically, concentration (and secondarily temperature) is the most important controllable parameter for the lyotropic phase, while temperature (and secondarily pressure) is the most important

<sup>&</sup>lt;sup>9</sup>An example of a typical phase sequence is Cr 20 N 60 I, meaning that the LC phase (in this case *nematic*) is located between 20°C and 60°C. Cr (or sometimes letter K) stands for the crystalline phase and I for the isotropic phase.

controllable parameter for the thermotropic phase. Lyotropic LCs are broadly present in nature. For instance, by adding water to soap (which is not a LC) above a minimum concentration, we cause the soap molecules to form lyotropic LCs. The term "lyo" comes from the Greek word *liein* which means "to dissolve" (just like soap does in the water). Steroids, glicolipids, phospholipids, liposomes, to cite some examples, all form lyotropic LCs. As a consequence, this type of LCs is primarily investigated in the fields of biochemistry, biophysics, and bionics.

#### 1.2.2 Shape and Molecular Structure

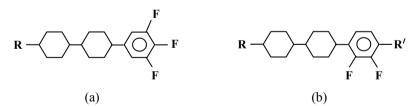

As far as the shape of LC molecules is concerned, we distinguish two main types (though there are less usual but more complex shapes): in the first the molecules appear like a rod (rod-like, cigar-like or **calamitic** LCs) as sketched in Fig. 1.4a, in the second the molecules are shaped like a disc (disc-like or **discotic**<sup>10</sup> LCs), as sketched in Fig. 1.4b.

Fig. 1.4 Shape of liquid crystal molecules: calamitic (a) and discotic (b)

We represented the molecules in Fig. 1.4 as made up of a rigid central part (core) plus some flexible ramifications (lateral, or side chains) whose chemical structures are generally different each other. Hereafter, the chains will not be plotted for the sake of simplicity, as they are not essential to the discussion. Moreover, since calamitic and thermotropic liquid crystals are the most important for display applications, we shall treat only these liquid crystals.

It is noteworthy that a careful balance between rigid and flexible parts is essential to produce the LC phase. The molecule must not be completely flexible, as it will not have orientational order, but if completely rigid it will directly pass from solid to liquid, with increasing temperature.

The characteristics of a calamitic LC are obtained by the interconnection of two (or more) rigid cyclic units, or rings, causing the elongated shape.

The planar conformation is ensured by the linking groups such as -(CH=N)-, -N=N-, -(CH=CH)<sub>n</sub>-, -CH=N-N=CH-, etc., that with their multiple bonds reduce the freedom of rotation. Some representative examples of these LC molecules and the

<sup>&</sup>lt;sup>10</sup>Discotic LCs were discovered by the group of **Sivaramakrishna Chandrasekhar** in Bangalore, India, only in 1977. The paper announcing the discovery was published in an Indian physics journal [CSS1977]. Discotic LCs found a limited application in electronic displays only in the late 1990s. They are used to make a sheet of film that expands the viewing angle of a twisted-nematic (TN) display [K2002]. Recently, other bizarre and more complex LC shapes have been added, like the banana, or boomerang, one [NSW1996].

temperature range in which they exhibit nematic mesophase are reported in Table 1.1.

| Acronym | Molecular structure and full name                                        | Nematic    |

|---------|--------------------------------------------------------------------------|------------|

|         |                                                                          | range (°C) |

|         |                                                                          |            |

| PAA     | $CH_{3}-O-\langle \rangle -N = N^{+}-\langle O \rangle -O-CH_{3}$        | 116–134    |

|         | o <sup>−</sup>                                                           |            |

|         | para-azoxyanisole                                                        |            |

|         |                                                                          |            |

| MBBA    | $CH_3 - O - O - CH = N - O - C_4 H_9$                                    | 22–47      |

|         | N-(4'-methoxybenzylidene)-4-butylaniline                                 |            |

|         |                                                                          |            |

| EBBA    | $C_2H_5-O-\langle \bigcirc \rangle-CH=N-\langle \bigcirc \rangle-C_4H_9$ | 35–77      |

|         | N-(4'-ethoxybenzylidene)-4-butylaniline                                  |            |

|         |                                                                          |            |

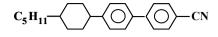

| 5CB     | $C_5H_{11} \longrightarrow CN$                                           | 22–35      |

|         | 4'-(n-pentyl)-4-cyanobiphenyl                                            |            |

|         |                                                                          |            |

| 6CB     | $C_6H_{13} \rightarrow O \rightarrow CN$                                 | 15–29      |

|         | 4'-(n-hexyl)-4-cyanobiphenyl                                             |            |

|         |                                                                          |            |

| РСН     | $C_5H_{11} \rightarrow O \rightarrow CN$                                 | 30–55      |

|         | 4'-(trans-4-n-pentylcyclohexyl) benzonitrile                             |            |

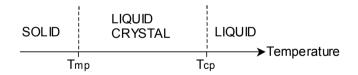

Table 1.1 Some Liquid Crystal compounds

All the structures in Table 1.1, except the last one, contain two benzene rings.<sup>11</sup> We recall from the organic chemistry that when the benzene ring is attached to some other group of atoms in a molecule it is called a *phenyl group* and is represented in several ways, as it is illustrated in Fig. 1.5a. Moreover, when two substituents of the hydrogen atoms are present, their relative positions are usually indicated by the prefixes *ortho, meta* and *para*, (or alternatively by 2, 3, and 4, respectively) as illustrated in Fig. 1.5b. In LC molecules, the linking groups are attached in the *para* positions, ensuring the most elongated shape (usually, in the range of a few nanometers). In general, a typical LC possesses a linear structure with a central core that contains several rings, a linkage and two terminal chains. It was seen that short chains helped the formation of the nematic state, as well as the combination of one

<sup>&</sup>lt;sup>11</sup>Benzene,  $C_6H_6$ , is conventionally and concisely depicted in several ways. We adopt the hexagon with a circle in the middle, to indicate that benzene is a resonance hybrid.

short alkyl chain on one ring and a polar substituent on the other to maximize the degree of anisotropic polarizability of electron density.

Fig. 1.5 (a) Symbols of the phenyl group. (b) Relative positions and nomenclature of substituents in a benzene ring

The first compound in Table 1.1 is the Gattermann's PAA which exhibits nematic state at temperatures greater than 116°C. The following entries, MBBA and EBBA, belong to a class of compounds called **Schiff's bases**, whose general formula is

$$R - O - O - CH = N - O - R'$$

where the symbols **R** and **R'** at the left and right represent the terminal groups. **R** is of the type  $C_nH_{2n+1}$ , with *n* integer. **R'** includes  $C_4H_9$ ,  $CH_3COO$ , and CN. They exhibit nematic state nearly at room temperature, thus making their use much easier for experimental purposes. Unfortunately they have poor chemical stability, as they are easily hydrolyzed by water. To avoid this problem, chemically stable substances, like for instance Cyanobiphenils (5CB and 6CB are two examples) and their derivatives were synthesized. They are characterized by two phenyl groups attached directly (**biphenyl**). The last entry in Table 1.1 shows PCH, as an example of a class of compounds in which one aromatic ring is substituted by a *cyclohexane* ( $C_6H_{12}$ ) ring. Further LC compounds and mixtures utilized for display applications will be discussed throughout the Chapter 2 of this book.

#### 1.2.3 Liquid Crystal Phases

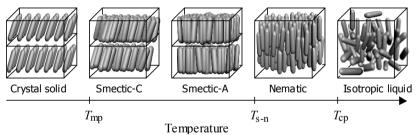

Unlike liquids, whose molecules possess no type of order and are free to move in all the three dimensions (Fig. 1.6), LCs possess a certain degree of orientational order and positional relationships between the molecules. Different **phases** for thermotropic LCs can be defined in a sequence given by increasing temperature (namely, the *smectic* and either *nematic* or *cholesteric* phases).

The first phase above  $T_m$  is the **smectic** phase, which is viscous and fluid. Smectic is derived from the Greek word for soap, *smectos*. The slipperiness of soap is indicative of the ease with which these layers shift about. The smectic liquid crystals are closer to solids because they exhibit both (two-dimensional) positional and orientational order. The molecules are arranged side by side in a series of layers and their movement is mainly limited inside the layers, which are free to slide over each other.

A unit vector **n**, known as the director, can be defined, parallel to the average direction of the long axis of the molecules in the immediate neighborhood. This vector is not constant throughout the whole medium, but is a function of space. To put in evidence this last aspect,  $\mathbf{n}(r)$  is often used to designate the director.<sup>12</sup>

Fig. 1.6 Molecular disorder in liquids

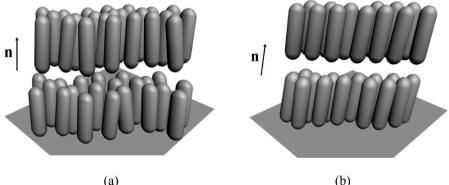

There are three main smectics sub-categories. The two best known of these are *smectic A*, in which the (calamitic) molecules align their long axes, with random deviations, perpendicularly to the layer planes, as shown in Fig. 1.7a, and *smectic C*, where the director is tilted from the layers normal by a fixed angle, as shown in Fig. 1.7b. The transition to smectic C occurs by cooling the smectic A phase.

Fig. 1.7 Molecular arrangement in (a) smectic A LCs and (b) smectic C LCs

<sup>&</sup>lt;sup>12</sup>Liquid crystals tend to form microdroplets. Within each droplet, molecules have the same orientation (director), but the director can be different for adjacent droplets. This explains the milky appearance of some LCs, as scattering of light occurs due to different director orientation. At the nematic-isotropic transition temperature (clearing point), the fluid no longer is made up of microdroplets and light scattering does not occur.

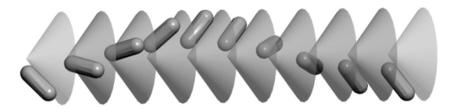

If materials which are intrinsically chiral or have added chiral components<sup>13</sup> are used, the smectic C phase changes into the *smectic*  $C^*$  (or *chiral smectic* C phase). This phase possess a layered smectic structure in which the parallel long axes of the molecules are rotated from layer to layer on the surface of a cone, resulting in a helix, as shown in Fig. 1.8. The helical structure, as discussed in the followings, is responsible for optical rotation, and other peculiar properties.

Fig. 1.8 The helix structure of the smectic C\* phase

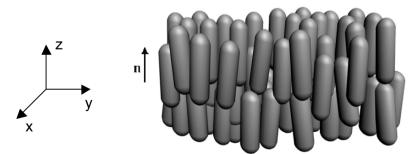

Next to the clearing point, increasing the temperature, the **nematic** phase appears. Nematic liquid crystals are the most widely used liquid crystals in display applications.

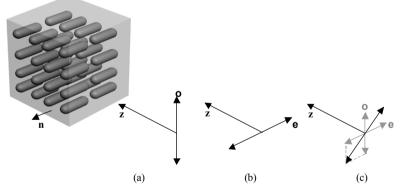

The name nematic is derived from a Greek word *nematos* meaning thread-like. In the nematic phase all molecules are aligned approximately parallel to each other, with only a one-dimensional (orientational) order and without a positional order. Molecules can translate in all the three directions and can rotate freely along the long molecular axes. An illustration of nematic phase is given in Fig. 1.9, along with an arbitrary system of coordinated axis included for reference. Some have compared the organization of the molecules in nematics to toothpicks in a box, which are free to translate in all directions and to rotate along the long (z) axis, but maintain their original orientation, since they are not allowed to rotate along the y and x axis by their neighbors.

Fig. 1.9 Molecular arrangement in *nematic* liquid crystals. Molecules are aligned approximately parallel to each other. The local average preferred direction is described by the unity vector  $\mathbf{n}$  (the director)

<sup>&</sup>lt;sup>13</sup>The term chiral is used to designate an object that cannot be superimposed to its mirror image. The classic example is constituted by the human hands. The left hand is a non-superimposable mirror image of the right hand.

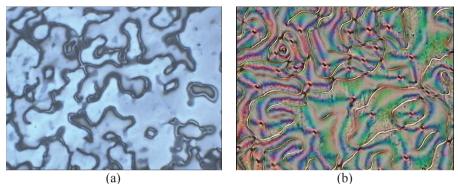

It should be noted that on optical inspection of a nematic, one rarely sees the idealized equilibrium configuration. Some very prominent structural perturbation appear as threads, as illustrated in the photographs in Fig. 1.10 [D2003], and from which nematics take their name.

Fig. 1.10 Thread-like textures of nematic materials. Photo courtesy of Ingo Dierking, Wiley-VCH and Taylor and Francis [D2003]

A schematic representation of the phase transitions with temperature described above is illustrated in Fig. 1.11.

Fig. 1.11 Schematization of phase transitions as a function of temperature for rod-like molecules.  $T_{mp}$ ,  $T_{s-n}$  and  $T_{cp}$  are respectively the temperatures at the melting point, smectic-to-nematic transition and clearing point

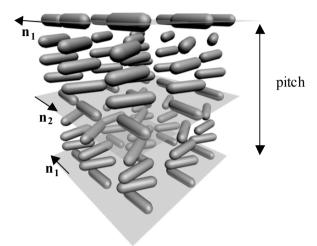

If chiral compounds such as cholesterol esters are added, the nematic phase changes into the **chiral-nematic** or **cholesteric** phase. The molecules in cholesteric liquid crystals are again arranged in layers (see Fig. 1.12). Layers are very thin and, within each layer, molecules are aligned in parallel with their long axes averagely parallel to the plane of the layers, similar to those in nematic liquid crystals. The main difference is that the director in each layer is displaced slightly from the corresponding director of the adjacent layers. The director is hence rotated (twisted) from layer to layer tracing out a helical path whose *pitch* is of the order of the wavelengths of visible light. Observe that the pitch is a function of temperature, and in particular it decreases as temperature increases.

Because of the helical structure, cholesteric LCs exhibit optical rotation, and selective reflection.<sup>14</sup> Moreover, cholesteric liquid crystals are also used as additives in the Twisted Nematic and Super Twisted Nematic technologies (that will be treated in the next chapter).

Fig. 1.12 Layers in cholesteric liquid crystals

#### 1.3 Physical Characteristics

In this section some fundamental physical properties of liquid crystals limited, for the purposes of this book, to the nematic liquid crystal phase will be discussed. It will be shown that nematic LCs, being not as rigid as solids, are easily reoriented, realigned, or deformed by applying mechanical stresses, electric and magnetic fields, and by the proximity actions with surfaces that have been properly prepared.

Because of their specific molecular shape and alignment, nematic LCs exhibit anisotropic physical characteristics. Their dielectric susceptibility, electrical conductivity, magnetic permeability, refractive index, and viscosity measured in the direction of the long axis are different from those measured in the plane normal to the long axis.

<sup>&</sup>lt;sup>14</sup>The phenomenon of selective reflection was exploited by J. L. Fergason in the first LC commercial application; well before liquid crystals were used for displays (see Sections 1.3.7 and 2.1.1).

#### 1.3.1 Molecular Order

In the nematic phase, the molecules alignment is described by two parameters:

(a) The already introduced director,  $\mathbf{n}$ . It describes the macroscopic preferred direction of molecules in a volume, which is small compared to the total LC system, but which is large compared to one LC molecule.

(b) The **order parameter**, S. It describes the distribution of molecules around the director direction within the volume. Defining as  $\vartheta$  the polar angle (i.e., the angle comprised between the director and the longitudinal axis of the molecule), S is expressed by

$$S = \frac{1}{2} \left\langle 3\cos^2 \vartheta - 1 \right\rangle \tag{1.1}$$

where the symbol  $\langle \cdot \rangle$  indicates an ensemble average. Observe that averaging this function, instead of just  $\vartheta$  alone, gives a value between 0 and 1 for the amount of orientational order. In a perfectly ordered state,  $\vartheta = 0$ , hence S = 1. A completely unordered phase has S = 0. In a typical nematic phase, S ranges between 0.4 and 0.7, indicating that the molecules have a certain degree of disorder [Z1933, O1933, F1958, L1999].

#### **1.3.2 Elastic Properties**

The lowest energy state for bulk nematic LCs corresponds to a single director orientation throughout the material. Boundaries, mechanical stress and external fields deform the LC molecular and director alignment; this induces reaction (elastic) forces. As a consequence of the orientational elasticity there exists always a local restoring torque (*elastic torque*) on the director which opposites to director variations.

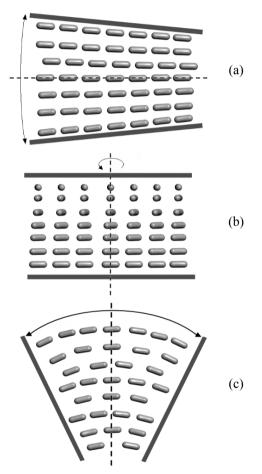

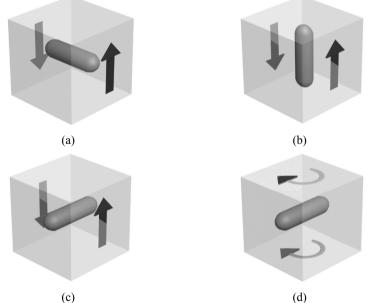

The deformation of nematic liquid crystals can be considered for three elementary cases, illustrated in Fig. 1.13.

The first is a "splay", where molecules are spread by external stress (Fig. 1.13a), the second is a "twist" where molecules are twisted by an external stress (Fig. 1.13b), and the third is a "bend" where molecules are bent by an external stress (Fig. 1.13c). General deformations are a combination of these three types.

The relationship between the deformation and the restoring torques opposing to the director deformation is expressed by the splay, twist and bend **elastic moduli** (also known as Frank elastic constants),  $k_{11}$ ,  $k_{22}$ ,  $k_{33}$ , whose dimension is *energy/length* and hence N in SI units.

The *elastic* increment of the volume *free energy* density (per cm<sup>3</sup>),  $f_k$ , due to splay, twist and bend is, according to the elastic theory for (non compressible) LCs, quadratic in the director gradients

$$f_{\mathbf{k}} = \frac{1}{2} \left[ k_{11} \left| \nabla \cdot \mathbf{n} \right|^2 + k_{22} \left| \mathbf{n} \cdot \nabla \times \mathbf{n} \right|^2 + k_{33} \left| \mathbf{n} \times \nabla \times \mathbf{n} \right|^2 \right]$$

(1.2)

This is the well-known Frank-Oseen elastic free energy density for nematics (and also cholesteric) LCs [F1958, C1992, GP1995].

The three elastic moduli are of the same order of magnitude  $(10^{-11} \text{ N})$ , with  $k_{22} < k_{11} < k_{33}$  for most nematics. The value of these moduli is much lower than that of ordinary elastic material; this facilitates alignment modification of liquid crystals by the application of external mechanical stress, electric field and magnetic field.

Fig. 1.13 Molecular alignments of nematic liquid crystals under external mechanical stress: (a) splay, (b) twist, (c) bend [F1958]

#### **1.3.3 Surface Aligning Properties**

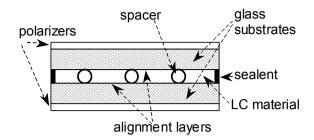

In most experiments and applications, a thin nematic layer (of  $2-10 \ \mu\text{m}$ , for display applications) is sandwiched between two substrates, usually glass plates. Near the substrate surface the LC molecules can exhibit aligning effects, that can be accentuated by special surface coatings (through certain organic or inorganic films)

and/or treatments to allow the director *alignment* to be controlled. The so called orienting (or alignment) layers force the director to a preferred orientation near their surface. Often, the interaction between the liquid crystal and the surface is strong enough not to allow a change of the director gradients within the boundaries (strong *anchoring*) even in presence of director gradients within the bulk. The surface treatments combined with the elastic torques originating from (1.2) ensure the initial homogeneous director alignment of liquid crystal cells (i.e., without spatial variations in the plane of the layer).

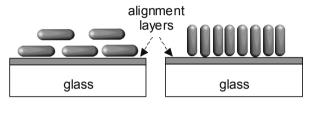

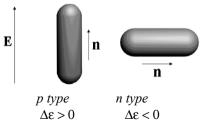

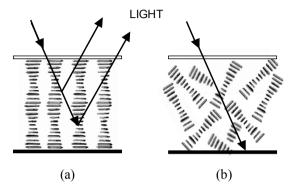

Two basic geometries exist: the **planar**<sup>15</sup> (or **homogeneous**) one, where **n** is parallel to the surface, and the **homeotropic** one, where **n** is normal to the surface, as shown in Fig. 1.14.

**Fig. 1.14** Alignment of nematic liquid near a solid plate (typically glass) trough suitable alignment layers. In the planar case the director is parallel to the substrate, whereas it is perpendicular in the homeotropic case

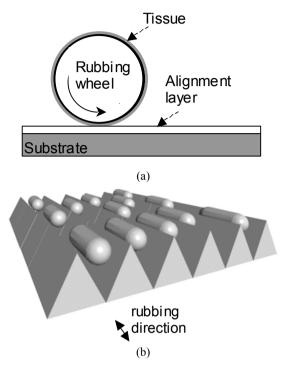

A simple and widely used process to achieve planar alignment is **rubbing**. A coating polymer layer (e.g. polyimide, nylon or polyvinylalcohol) is deposited on the glass surface and rubbed repeatedly in the same direction (about 100 times) with a soft tissue (cotton cloth) [C1941]. In this manner, microscopic grooves are created in the surface, which align the director of the near LC molecules parallel to the direction of rubbing,<sup>16</sup> as depicted in Fig 1.15.

This aligned LC monolayer induces long range alignment through the LC cell. The technique is related to an earlier method dated back at least to 1925 [Z1925, Z1932]. It is simple, but constitutes a source of yield loss causing non-uniform black areas in the LCD. New methods have been proposed to replace the rubbing approach

<sup>&</sup>lt;sup>15</sup>This case, important from the technology of LCDs, will be discussed also in the following chapter (see Section 2.4).

<sup>&</sup>lt;sup>16</sup>Actually, the underlying physical mechanism is not completely understood. It was originally supposed that *only* the morphology of the grooves were responsible of the alignment of LC molecules in the groove direction. However, observations made with the aid of an atomic force microscope, seem to indicate that this is not the case [LSU1992]. Indeed, the widths of the grooves (in the order of 600 Å) are much wider than the length of the long axis of nematic LCs (typically 30 Å). In other words, the LC molecules could align in any direction in the wide-pitch grooves. Therefore the alignment and anchoring effect are now attributed to the *stresses* in the surface.

such as oblique evaporation,<sup>17</sup> Langmuir-Blodgett formation, unidirectional stretching and groove formation by stamping, but without real success.

**Fig. 1.15 (a)** Roller used for rubbing. **(b)** In proximity of a surface where grooves are rubbed, LC molecules align along the direction of the grooves

It should be noted that rubbing gives a **pretilt** to the LC molecules that is, one end of the molecule is slightly lifted of some degrees. This speeds up and homogenizes the LC realignment under an electric field (avoiding the occurrence of reverse tilt and reverse twist creating different domains).

Some LCD modes, such as the Vertical Alignment discussed in Section 2.4.4 do not require rubbing (and this is considered an advantage).

In the homeotropic alignment the molecules are arranged perpendicular to the surface. This is coated with a surfactant like octadecyloxysilane (ODSE) that attaches to the surface with its long octadecyl chains projecting away in a direction approximately normal to the same surface.

<sup>&</sup>lt;sup>17</sup>An important problem of early LCDs was their limited life, caused by moisture as displays were not sealed hermetically. The development of techniques to align the crystals without rubbing and also allowing to seal displays hermetically was a major step toward the large-scale manufacture of LCDs. However, in 1977 new moisture resistant LCs were synthesized, so manufacturers abandoned hermetic sealing and went back to rubbing (or aligning the cells with epoxy stamped with tiny grooves).

#### 1.3.4 Viscosity

Viscosity has remarkable effects on the dynamic behavior of LCs. Indeed, the increase of viscosity at low temperatures reduces the possibility of molecules to move, and is one of the most limiting factors in the application of LCs.

Cinematic and dynamic viscosity can be defined, they are respectively referred to as  $\nu$  and  $\eta$ . The relationship that relates these two parameters is

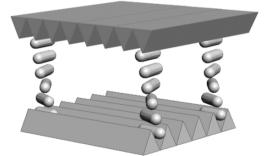

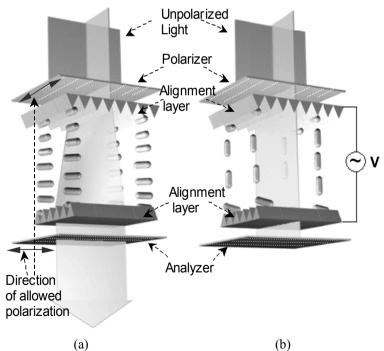

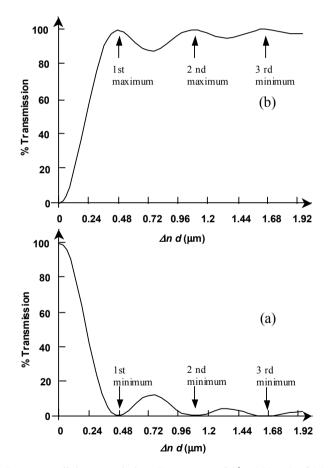

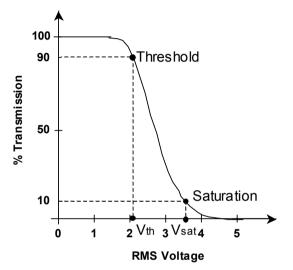

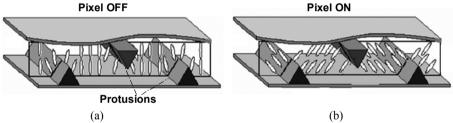

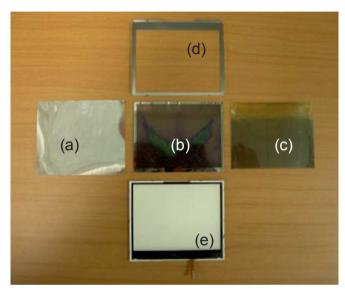

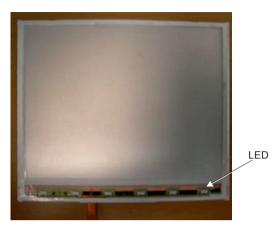

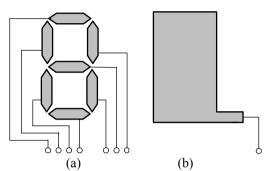

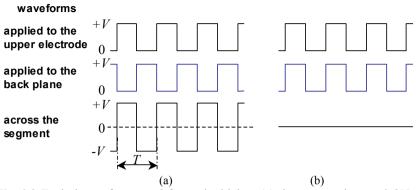

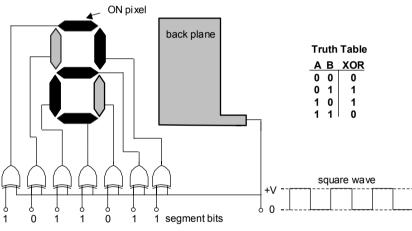

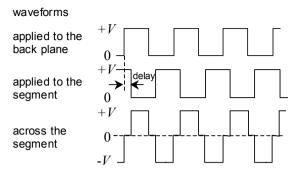

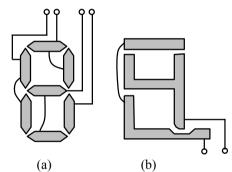

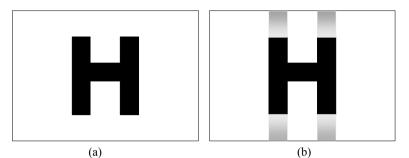

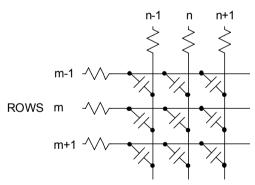

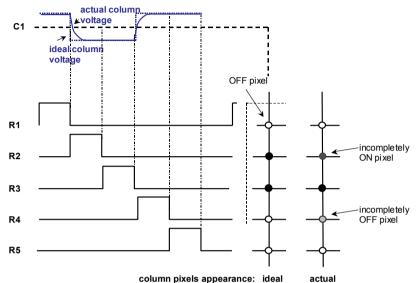

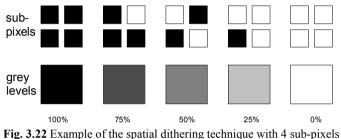

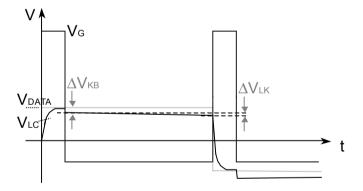

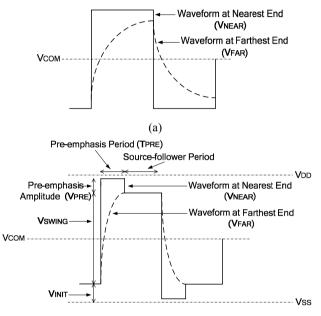

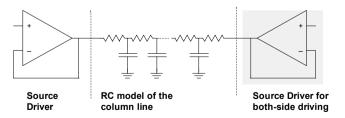

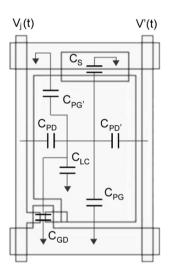

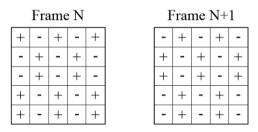

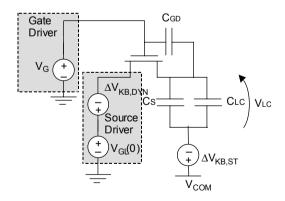

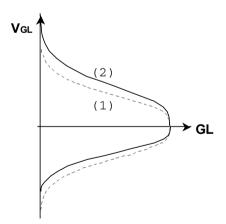

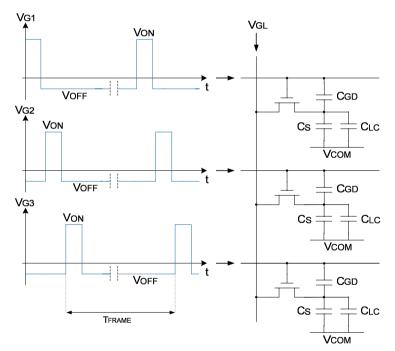

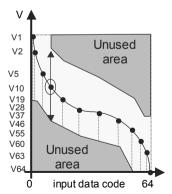

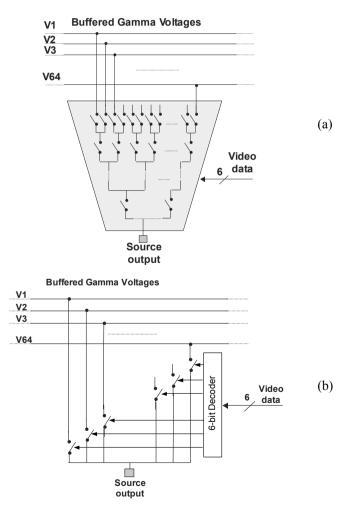

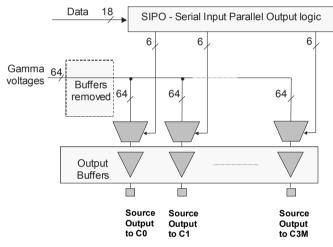

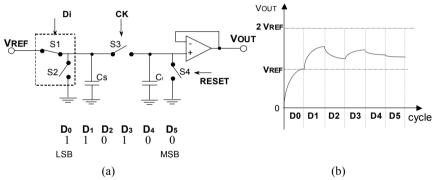

$$v = \frac{\eta}{\delta} \tag{1.3}$$