# VLSI Design and Test for Systems Dependability

VLSI Design and Test for Systems Dependability

A group picture of participants in the DVLSI Program: researchers from universities, national laboratories and industry, external program advisors and the staff members of JST are photographed. 13 March, 2013

Shojiro Asai Editor

# VLSI Design and Test for Systems Dependability

*Editor* Shojiro Asai Rigaku Corporation Tokyo Japan

ISBN 978-4-431-56592-5 ISBN 978-4-431-56594-9 (eBook) https://doi.org/10.1007/978-4-431-56594-9

Library of Congress Control Number: 2017963009

#### © Springer Japan KK, part of Springer Nature 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer Japan KK part of Springer Nature

The registered company address is: Shiroyama Trust Tower, 4-3-1 Toranomon, Minato-ku, Tokyo 105-6005, Japan

### Preface

The technological progress, with its tremendous economic impact, of electronic systems stands out among other industrial products of modern times and has produced various innovations over the last 50 years or so. It has had two major enablers, computer programs and the very-large-scale integration (VLSI) of semiconductor circuits. The concept of programed computing first materialized in computers that crunched alphanumeric data. The computer program has gone through a remarkable transformation since the introduction of high-level programing languages, close in form to human languages, describing how information is to be processed in the system; translating the program into machine-executable codes became a part of the job of computers. Electronic systems hardware has likewise shown progress in performance at an unprecedented pace starting out from the vacuum tube to the transistor to VLSI. High-performance computers, consisting of thousands of VLSI processors, each one containing billions of transistors, are being used for scientific calculations and big-data analysis. More remarkably, VLSI is used today in a far greater variety of electronic systems. Public infrastructures, such as transportation, utilities, public safety, and telecommunications, are large-scale electronic systems. Consumer items such as cell phones and automobiles are other examples of advanced electronic systems. All these electronic systems, in contrast to computers used for general computing, are customarily called computer-embedded systems. Progress in the development of these systems has been driven by the evolution of computer software (programing) and electronic hardware (VLSI among others), considered as twin engines working in harmony.

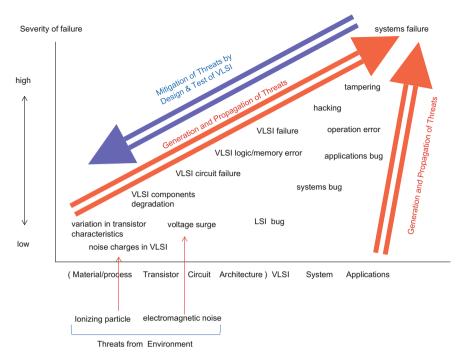

The three most important value metrics of an electronic system are performance, cost (price), and dependability. All three are carefully considered when a user is about to buy a system, or a manufacturer contemplates developing a system for sale. What is meant by performance and cost (price) is obvious and is talked about in terms of straightforward quantitative metrics. The concept of dependability, a term that has evolved from reliability, has expanded its attributes to range from a relatively simple quantity, such as mean time to failure (MTTF), a good statistical index of the availability of systems, to far harder to quantify metrics such as safety and tamper resistance. The bearings of dependability have become much more

important as humans increasingly rely on the convenience and benefit of electronic systems while the scale and severity of the detrimental effects of potential failures in such systems have become more devastating. The purpose of this book is to discuss how design and testing can help mitigate threats to the dependability of VLSI systems. Here the term VLSI system is meant to cover not only VLSI per se but also electronic systems that use VLSI (of semiconductor circuits) as a key component.

This book consists of three parts. Part I is a general introduction to the book and is made up of two chapters. It starts by describing in Chap. 1 the background and motivation that led to the undertaking of a government-funded research program entitled, "Fundamental technologies for dependable VLSI systems (called DVLSI hereafter)," funded by the Japan Science and Technology Agency (JST) under the Core Research of Evolutional Science and Technology (CREST) initiative. The program was started in April 2007 and lasted for about 8 years until March 2015, with 11 teams of researchers participating from universities, government laboratories, and industrial corporations. The rest of Chap. 1 describes the scope, activities, and management of the program. Detailed accounts are given as to how overarching issues of dependability were covered, how efforts were made to push expected deliverables toward applications, how exciting industry-academia collaborations were promoted during the term, and the final outcomes of the program. Chapter 2 begins with a quick overview of the principles and disciplines of design and verification/testing of electronic systems. Then, using this as a background, the implications of new technologies developed in the DVLSI program are discussed in light of other emerging trends in technology and the markets.

Part II of this book is entitled, "VLSI Issues in Systems Dependability." Chapters 3 through 12 discuss various threats to the dependability of VLSIs: ionizing radiation, electromagnetic interference, time-dependent degradation, variations in device characteristics, design errors, malicious tampering, etc., and what design and testing can do to manage these threats. Part III, which is entitled, "Design and Test of VLSI for Systems Dependability," consists of Chaps. 13 through 29, which describe technologies developed in the program as possible solutions for dependability in the design and testing of realistic systems such as robots and vehicles, data processing and storage in the cloud environment, wireless public telecommunications with improved connectivity, advanced electronic packaging with wireless interconnect, and so forth. Most chapters and sections of Part II and Part III are authored by the members of research teams in the DVLSI program, but some are contributed by "invited" authors, who, having participated in the various events of the program in one way or other, kindly agreed to express their thoughts in this book.

This book is intended to be a reference for engineers who work on the design and testing of electronic systems with particular attention on dependability. It can be used as an auxiliary textbook in undergraduate and graduate courses as well. It is also hoped that readers of this book with non-engineering backgrounds, such as mathematics and social economists, will gain insight into the problems of systems dependability, and may consider taking them on as innovative challenges. Preface

It was a real pleasure to be able to work with the members of the DVLSI program, and to witness industry-university collaborations from inception to fruition. I am thankful to numerous speakers from outside the program who gave stimulating talks and shared thoughts and discussions at program conferences. It was good to have been able to interact and exchange ideas with scholars and engineers from various parts of the world (the United States, China, Taiwan, India, and Germany) including active members of the United States program, "Failure-Resistant Systems (FRS)" sponsored by the National Science Foundation (NSF) and the Semiconductor Research Corporation (SRC), and the German program, "SPP1500 Dependable Embedded Systems," sponsored by the Deutsche Forschungsgemeinschaft (DFG). I only wish we had closer interactions between these programs—FRS (2013–present), SPP1500 (2012–2016), and DVLSI (2007–2015)—with more overlapping elements.

My heartfelt thanks go to the following gentlemen: Tohru Kikuno, Atsushi Hasegawa, Masatoshi Ishikawa, Yoshio Masubuchi, Naoki Nishi, Koki Noguchi, Tadayuki Takahashi, Koichiro Takayama, and Kazuo Yano, all of whom are advisory members of the DVLSI program. I would like to thank JST and all its management and staff members for their encouraging and patient support for this program: Kazunori Tsujimoto, Shinobu Masubuchi, Daichi Terashita, Toshiaki Ikoma, Michiharu Nakamura, and the late Koichi Kitazawa, to name but a few.

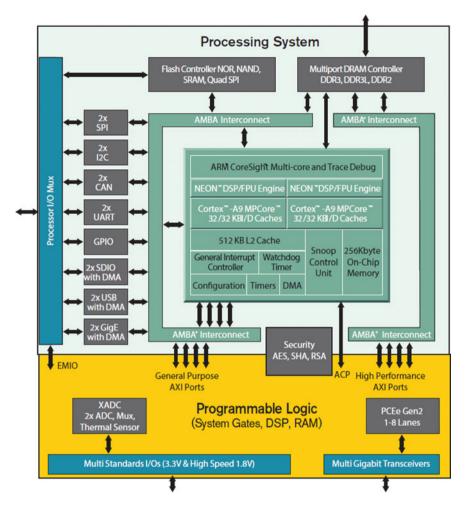

I would like to thank Toyota Motors Corporation for kindly providing a chart describing the power train of a hybrid vehicle to be used in this book as an illustration, and the Xilinx Company for kindly agreeing that the use of a chart showing an FPGA (Field Programmable Gate Array) coupled with an ARM (ARM is a company that provides an embedded processor architecture) processor, could be included in this book.

I am also thankful to Hikaru Shimura of the Rigaku Corporation who generously allowed me to spend some of my time on the job overseeing this program, and to his technical staff members, of which Kenji Wakasaya was one, who kindly shared their experience in systems design. I am thankful to Binu Thomas of Quest Global, a partner of Rigaku's in software development, for sharing his thoughts about verification and testing. I cannot thank my colleagues enough at Hitachi Ltd. for stimulating and helping me form ideas about what systems design is. Just to single out a person from the many I worked with, Masayoshih Tsutsumi was an engineer– philosopher who shared his great insight into how to guide thoughts in designing a product, which I have tried to reproduce, only to a very limited extent, in Chap. 2. My last thanks go to Shigeru Oho and Koki Noguchi for thoroughly reviewing the first two chapters and suggesting many important and necessary corrections.

Tokyo, Japan March 2017 Shojiro Asai

# Contents

#### Part I Introduction

| Cha  | llenges and Opportunities in VLSI for Systems               |        |

|------|-------------------------------------------------------------|--------|

| Dep  | endability                                                  | 2      |

| Shoj | iro Asai                                                    |        |

| 1.1  | VLSI in Electronic Systems and Their Dependability          | 2      |

| 1.2  | Background and Motivation for the Program                   | ,      |

| 1.3  | Threats and Opportunities for the VLSI Systems              | 12     |

| 1.4  | The DVLSI Program                                           | 1:     |

| 1.5  | A Summary of Results                                        | 2      |

| Refe | rences                                                      | 24     |

|      | iro Asai                                                    |        |

|      |                                                             |        |

| 2.1  | Core Considerations in Designing an Electronic System       |        |

|      | Product                                                     | 2      |

| 2.2  | Design and Development of an Electronic System Product      | 3      |

| 2.3  | Process and Management of Product Development               | 3.     |

| 2.4  | Risk Assessment and Refinement of Design Against Risks      | 4      |

| 2.5  | Conclusion and Future Work                                  | 4      |

| 2.6  | Appendix to Chapter 2: The Case of a Scientific Instrument  |        |

|      | inprendent to chapter 2. The case of a serentime instrument |        |

| DC   | System—An Example Electronic System                         | 48     |

| Refe |                                                             | 4<br>5 |

#### Part II VLSI Issues in Systems Dependability

| 3 | Radi       | ation-Induced Soft Errors                                | 57         |

|---|------------|----------------------------------------------------------|------------|

|   | Eishi      | H. Ibe, Shusuke Yoshimoto, Masahiko Yoshimoto,           |            |

|   | Hiros      | shi Kawaguchi, Kazutoshi Kobayashi, Jun Furuta,          |            |

|   | Yuki       | o Mitsuyama, Masanori Hashimoto, Takao Onoye,            |            |

|   | Hiro       | yuki Kanbara, Hiroyuki Ochi, Kazutoshi Wakabayashi,      |            |

|   | Hide       | toshi Onodera and Makoto Sugihara                        |            |

|   | 3.1        | Fundamentals and Highlights in Radiation-Induced         |            |

|   |            | Soft-Errors                                              | 58         |

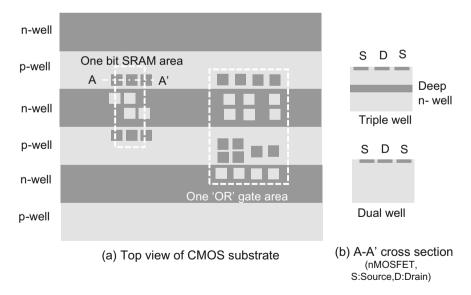

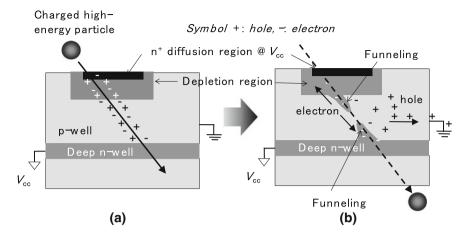

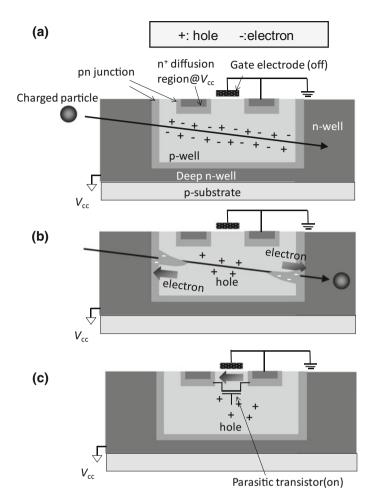

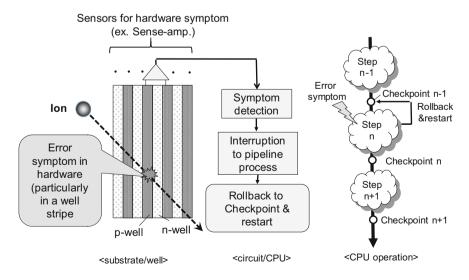

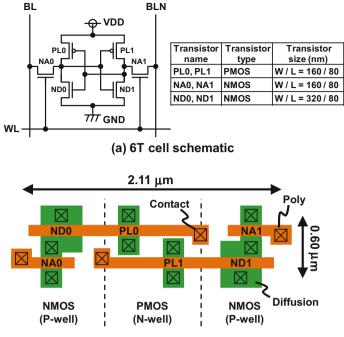

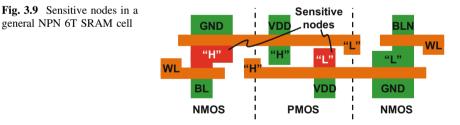

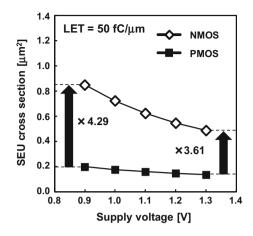

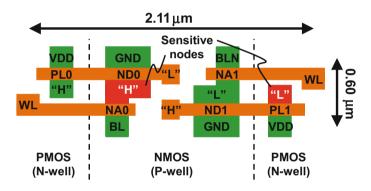

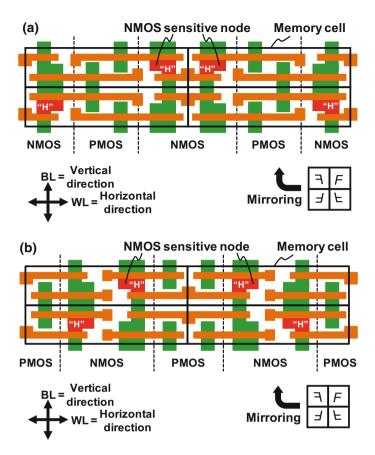

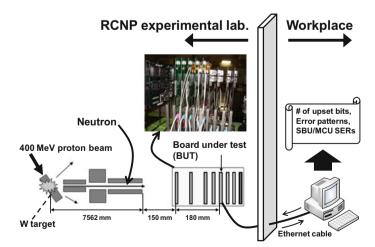

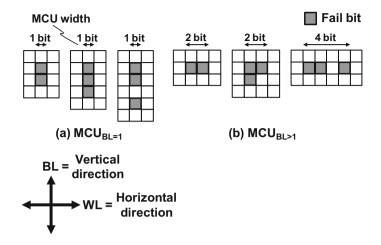

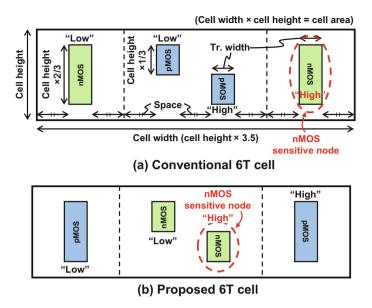

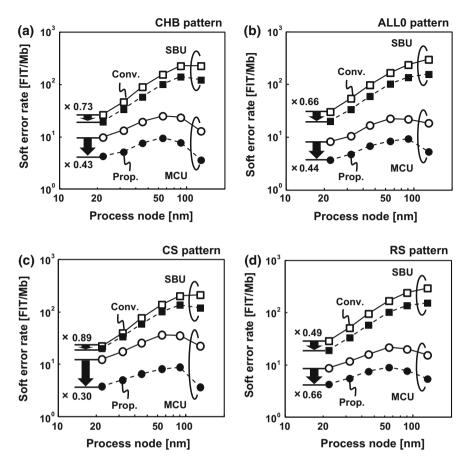

|   | 3.2        | Soft-Error Tolerant SRAM Cell Layout                     | 80         |

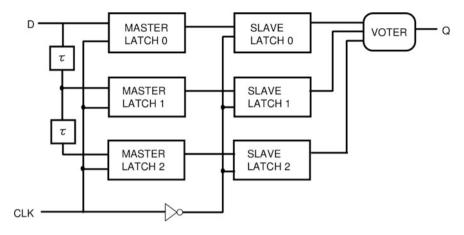

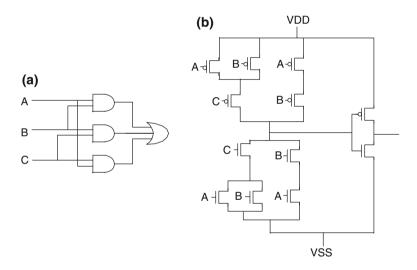

|   | 3.3        | Radiation-Hardened Flip-Flops                            | 91         |

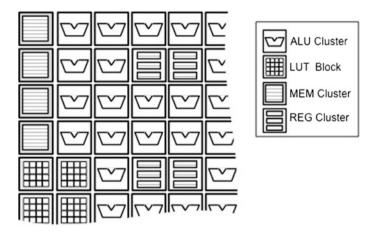

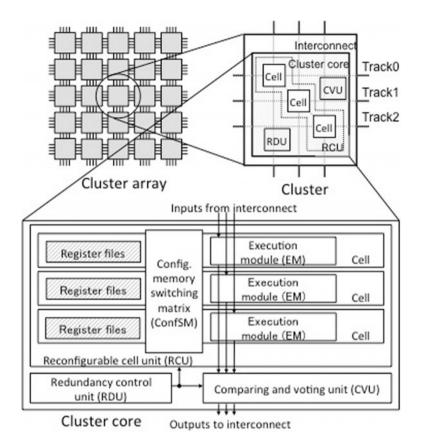

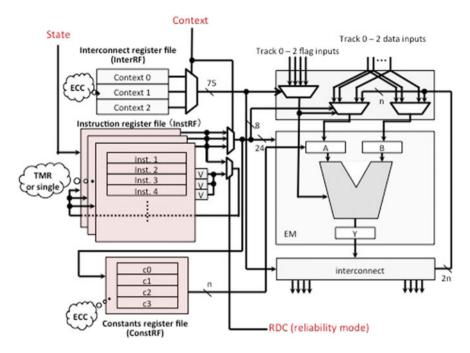

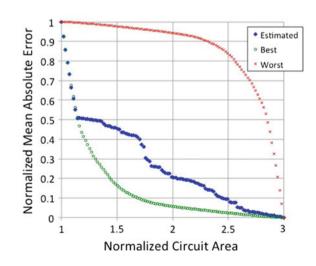

|   | 3.4        | Soft-Error-Tolerant Reconfigurable Architecture          | 101        |

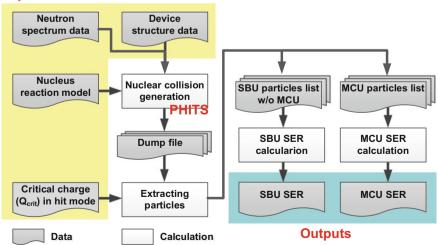

|   | 3.5        | Simulation and Design Techniques for Computer Systems    | 113        |

|   | Refe       | rences                                                   | 118        |

| 4 | Elect      | tromagnetic Noises                                       | 129        |

|   | Make       | oto Nagata, Nobuyuki Yamasaki, Yusuke Kumura,            |            |

|   | Shun       | na Hagiwara and Masayuki Inaba                           |            |

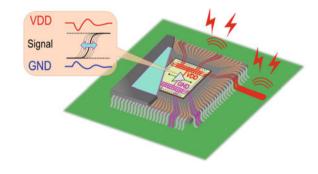

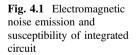

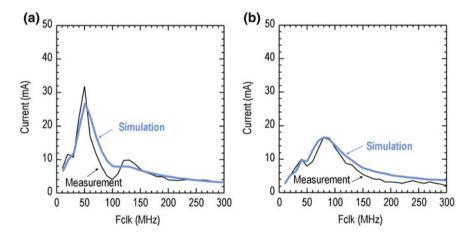

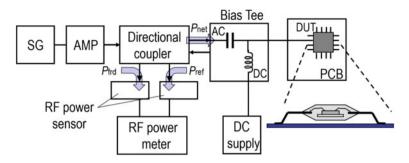

|   | 4.1        | Electromagnetic Compatibility of CMOS ICs                | 130        |

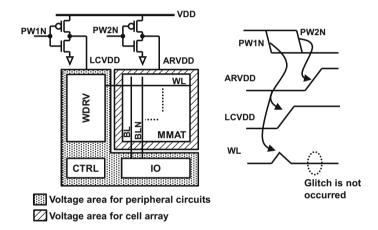

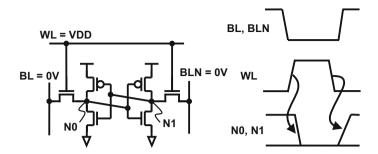

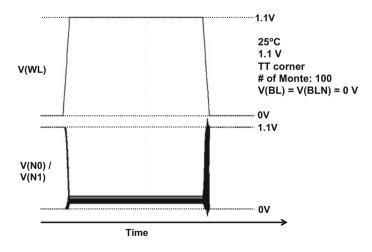

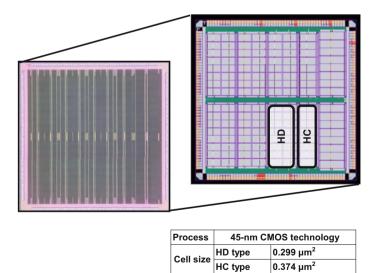

|   | 4.2        | Electromagnetic Noise Immunity in Memory Circuits        | 140        |

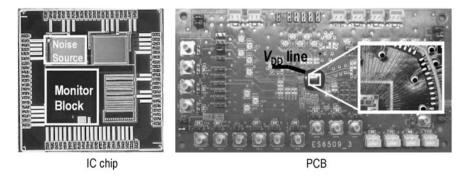

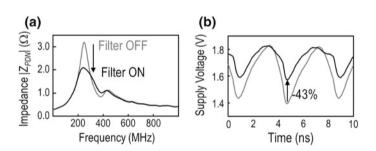

|   | 4.3        | Power Noise of IC Chips in Assembly                      |            |

|   |            | and Its Mitigations                                      | 145        |

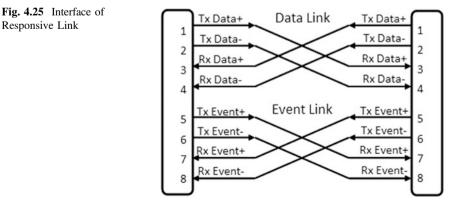

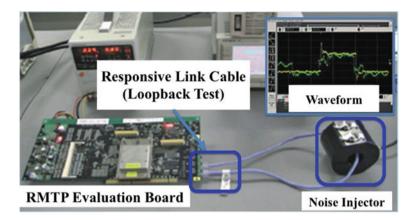

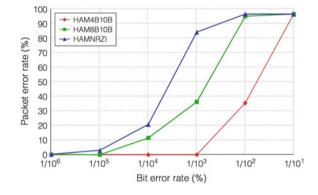

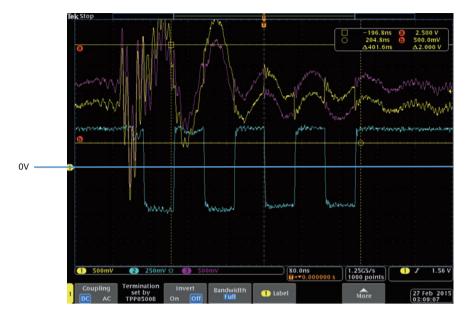

|   | 4.4        | Responsive Link for Noise-Tolerant Real-Time             |            |

|   |            | Communications                                           | 150        |

|   | Refe       | rences                                                   | 160        |

| 5 | Vari       | ations in Device Characteristics                         | 163        |

| 5 |            | toshi Onodera, Yukiya Miura, Yasuo Sato, Seiji Kajihara, | 105        |

|   |            | inori Sato, Ken Yano, Yuji Kunitake and Koji Nii         |            |

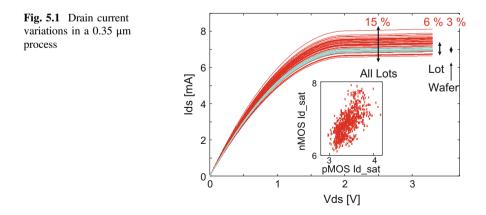

|   | 5.1        | Overview of Device Variations                            | 164        |

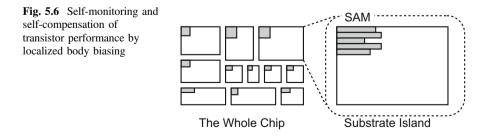

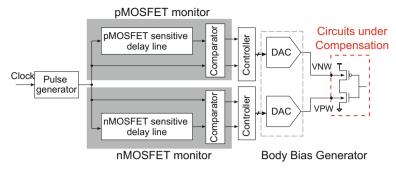

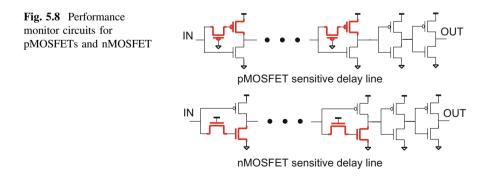

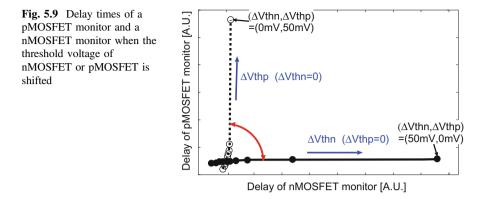

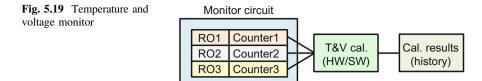

|   | 5.2        | Monitoring and Compensation for Variations in Device     | 104        |

|   | 5.2        | Characteristics                                          | 171        |

|   | 5.3        | Highly Accurate On-chip Measurement of Circuit Delay     | 1/1        |

|   | 5.5        | Time for Dependable VLSI Systems                         | 178        |

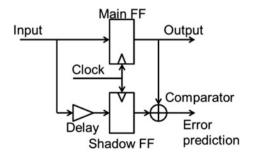

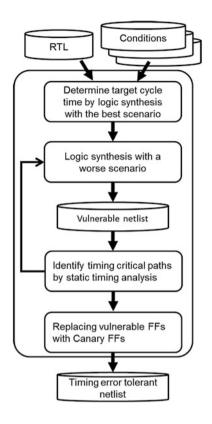

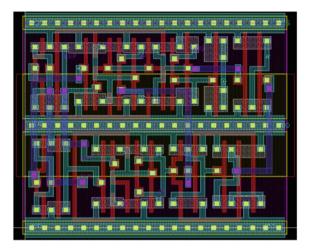

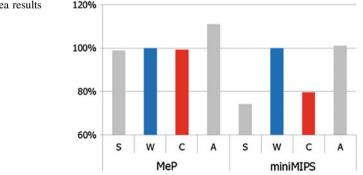

|   | 5.4        | Timing-Error-Sensitive Flip-Flop for Error Prediction    | 178        |

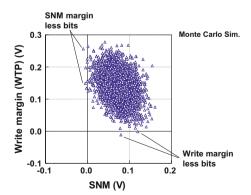

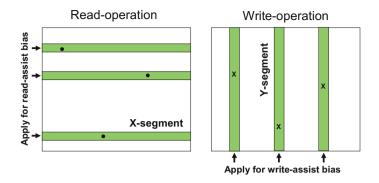

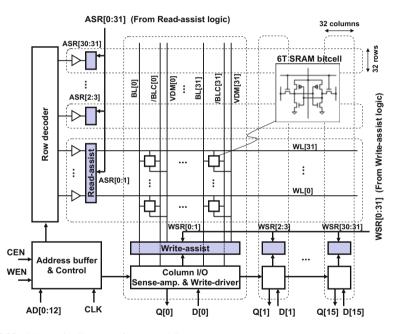

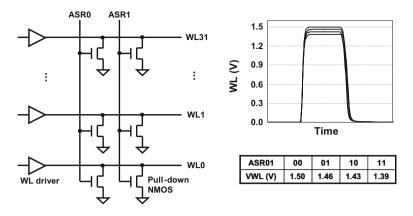

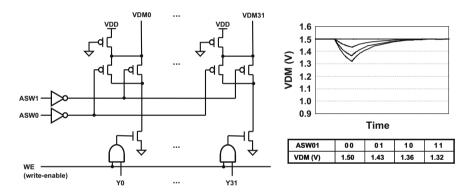

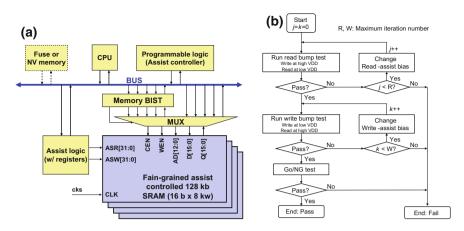

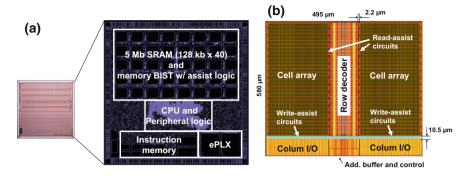

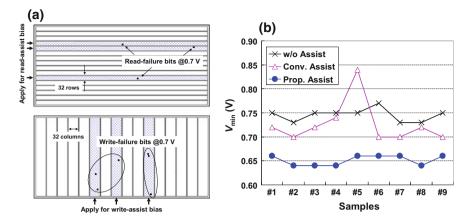

|   | 5.4<br>5.5 | Fine-Grain Assist Bias Control for Dependable SRAM       | 184<br>191 |

|   |            | *                                                        |            |

|   | Kefe       | rences                                                   | 199        |

| 6 | Time  | e-Dependent Degradation in Device Characteristics            |       |

|---|-------|--------------------------------------------------------------|-------|

|   | and   | Countermeasures by Design                                    | 203   |

|   | Taka  | shi Sato, Masanori Hashimoto, Shuhei Tanakamaru,             |       |

|   | Ken   | Takeuchi, Yasuo Sato, Seiji Kajihara, Masahiko Yoshimoto,    |       |

|   | Jinwo | ook Jung, Yuta Kimi, Hiroshi Kawaguchi, Hajime Shimada       |       |

|   | and J | lun Yao                                                      |       |

|   | 6.1   | Time-Dependent Device Degradation; Mechanisms                |       |

|   |       | and Mitigation Measures                                      | 204   |

|   | 6.2   | Degradation of Flash Memories and Signal Processing          |       |

|   |       | for Dependability                                            | 210   |

|   | 6.3   | In-Field Monitoring of Device Degradation for Predictive     |       |

|   |       | Maintenance                                                  | 216   |

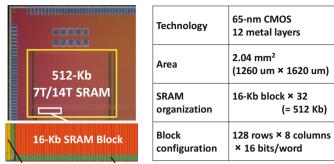

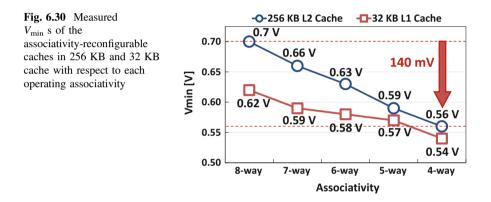

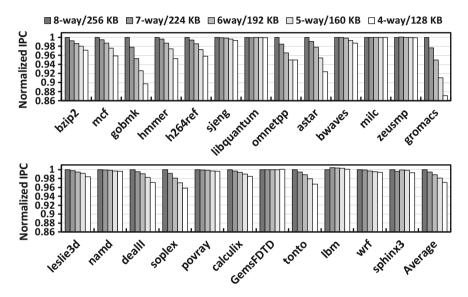

|   | 6.4   | A Reconfigurable SRAM Cache Design for Wide-Range            |       |

|   |       | Reliable Low-Voltage Operation                               | 225   |

|   | 6.5   | Runtime Self-reconstruction for Tolerating Software/Hardware |       |

|   |       | Faults Increment from Aging                                  | 233   |

|   | Refe  | rences                                                       | 239   |

| 7 | Com   | andinita in Window Talanamaniantiana                         | 245   |

| 7 |       | nectivity in Wireless Telecommunications                     | 245   |

|   |       | o Tsubouchi, Fumiyuki Adachi, Suguru Kameda,                 |       |

|   |       | ki Motoyoshi, Akinori Taira, Noriharu Suematsu,              |       |

|   |       | shi Takagi, Hiroshi Oguma, Minoru Fujishima, Ryuji Inagaki,  |       |

|   |       | nomi Tsuru, Eiji Taniguchi, Hiroshi Fukumoto,                |       |

|   |       | a Matsuzawa, Masaya Miyahara, Makoto Iwata,                  |       |

|   |       | hiro Yamagata and Noboru Izuka                               |       |

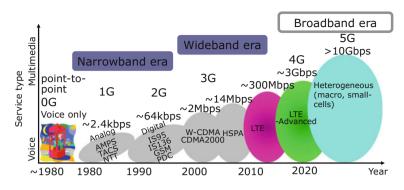

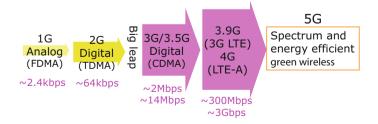

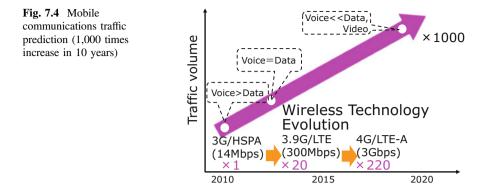

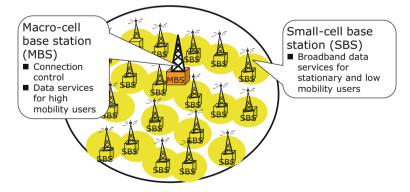

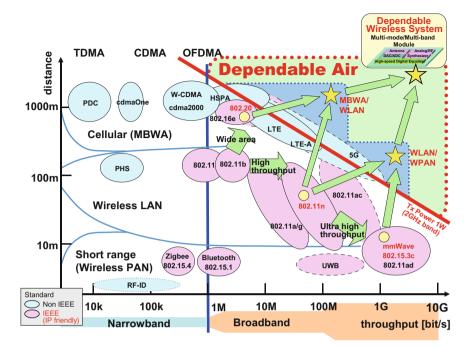

|   | 7.1   | Evolution of Public Wireless Networks                        | o / = |

|   |       | and Future Challenges.                                       | 247   |

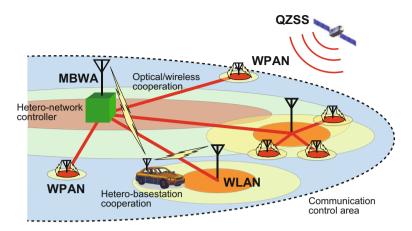

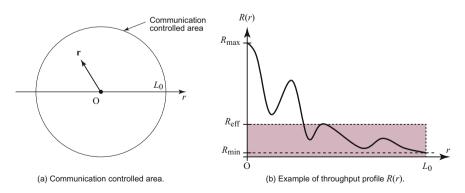

|   | 7.2   | Challenges for Dependable Wireless System.                   | 251   |

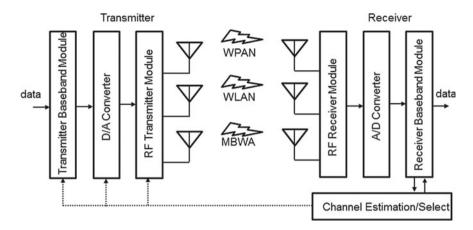

|   | 7.3   | Transceiver Technologies for Dependable Wireless System      | 260   |

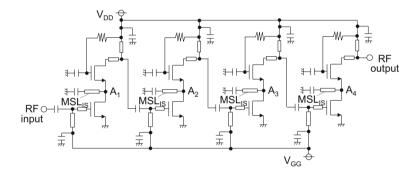

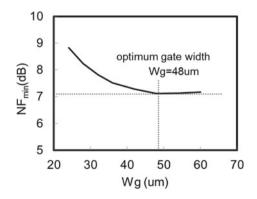

|   | 7.4   | Broadband RF Circuit for Versatile, Dependable Wireless      |       |

|   |       | Communications                                               | 274   |

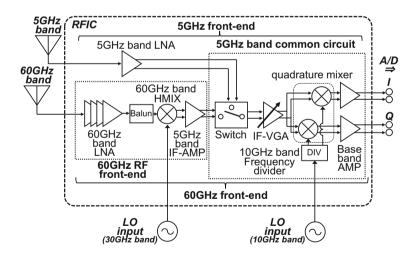

|   | 7.5   | All-Si-CMOS Front-End ICs for Multiband                      |       |

|   |       | Micro-/Millimeter-Wave Communications                        | 279   |

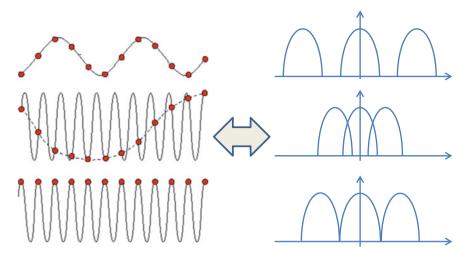

|   | 7.6   | Analog-to-Digital Converters for Versatile and Multiband     |       |

|   |       | Wireless Networks                                            | 292   |

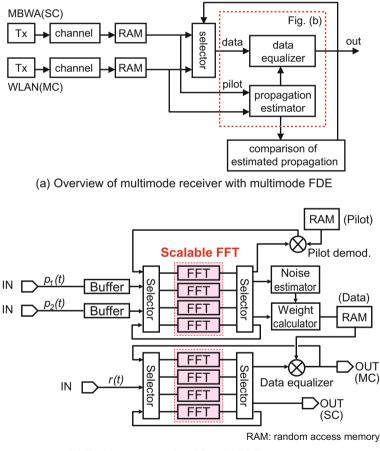

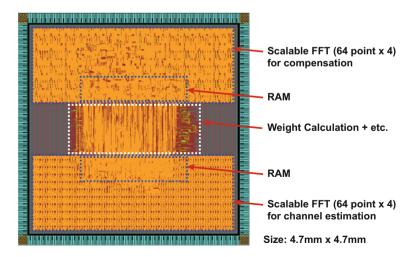

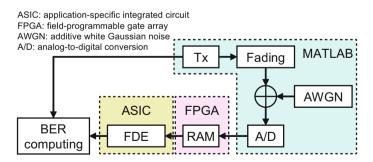

|   | 7.7   | Multimode Frequency Domain Equalizer for Heterogeneous       |       |

|   |       | Wireless Systems                                             | 299   |

|   | 7.8   | Network Technology for Heterogeneous Wireless Systems        | 309   |

|   | Refe  | rences                                                       | 321   |

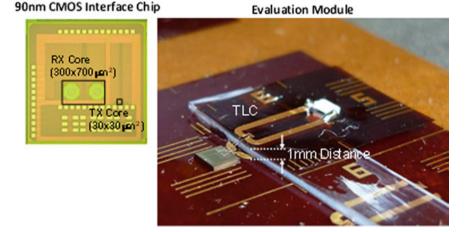

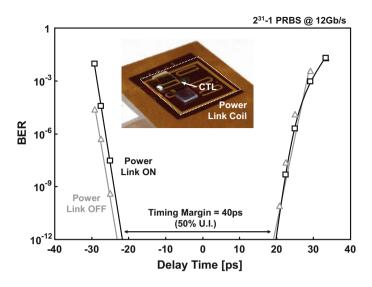

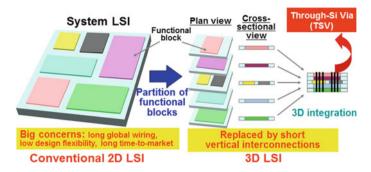

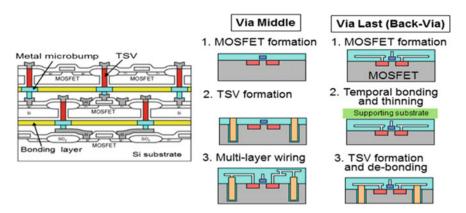

| 8  | Conn       | ectivity in Electronic Packaging                          | 325 |

|----|------------|-----------------------------------------------------------|-----|

|    | Hirok      | i Ishikuro, Tadahiro Kuroda, Atsutake Kosuge,             |     |

|    |            | masa Koyanagi, Kang Wook Lee, Hiroyuki Hashimoto          |     |

|    | and N      | Iakoto Motoyoshi                                          |     |

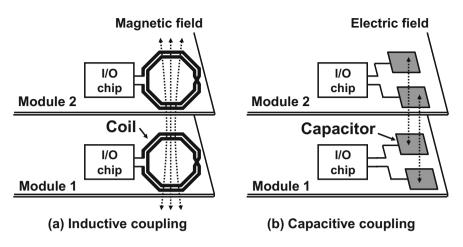

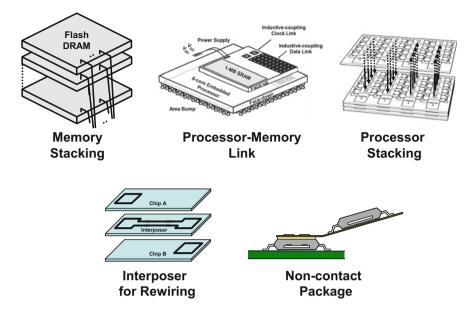

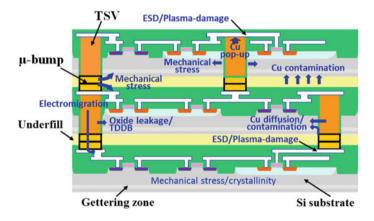

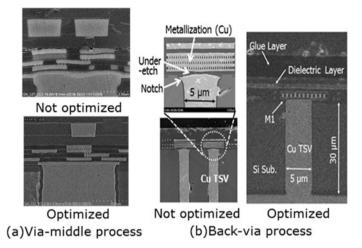

|    | 8.1        | Requirements for Dependable Electronic Packaging          | 326 |

|    | 8.2        | Wireless Interconnect for Dependable Electronic           |     |

|    |            | Packaging                                                 | 334 |

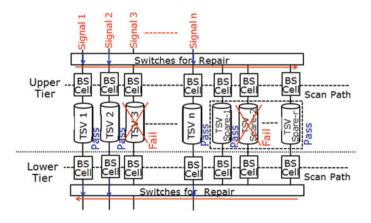

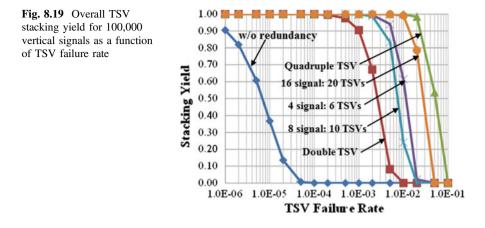

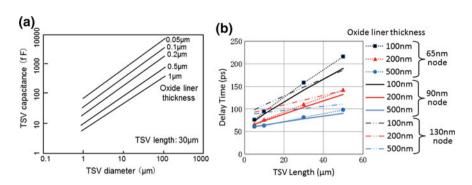

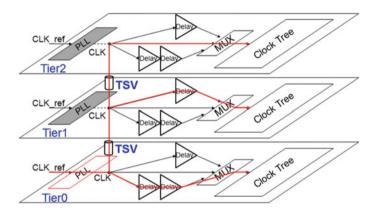

|    | 8.3        | Connectivity Issues in 3D Integration                     | 342 |

|    | Refer      | ences                                                     | 348 |

| 9  | Resn       | onsiveness and Timing                                     | 351 |

| ,  |            | bhiro Yoneda, Yoshihiro Nakabo, Nobuyuki Yamasaki,        | 551 |

|    |            | yoshi Takasu, Masashi Imai, Suguru Kameda, Hiroshi Oguma, |     |

|    |            | pri Taira, Noriharu Suematsu, Tadashi Takagi              |     |

|    |            | Kazuo Tsubouchi                                           |     |

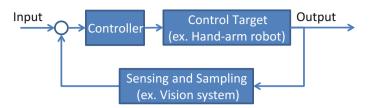

|    | 9.1        | Responsiveness for Hard Real-Time Control                 | 352 |

|    | 9.2        | Microprocessor Architecture for Real-Time Processing      | 358 |

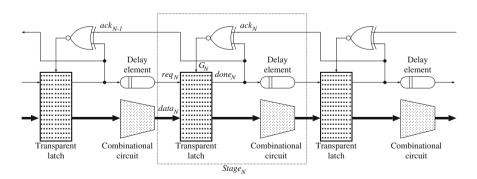

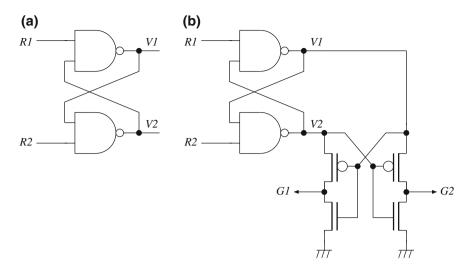

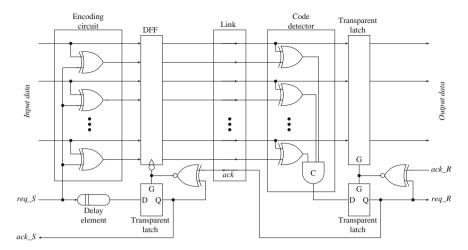

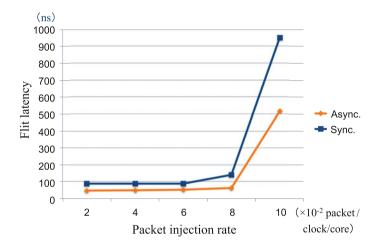

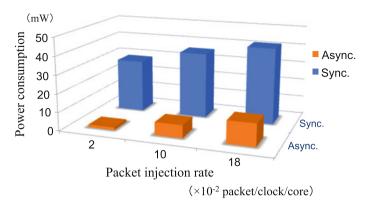

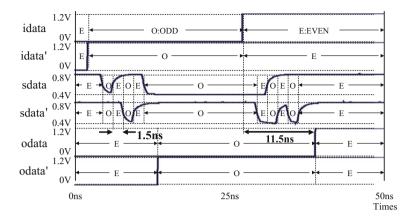

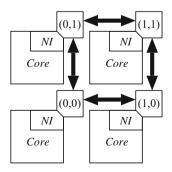

|    | 9.2<br>9.3 | Asynchronous Networks-on-Chip.                            | 366 |

|    | 9.5<br>9.4 | Timing and Synchronicity for Dependable Wireless          | 500 |

|    | 9.4        | Network                                                   | 378 |

|    | Pofor      | ences                                                     | 391 |

|    | Kelei      |                                                           | 591 |

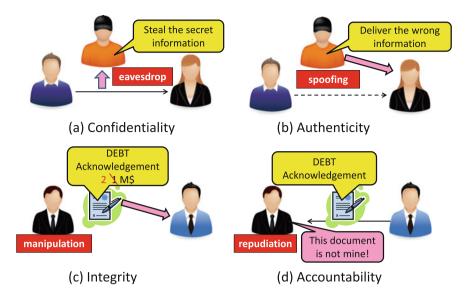

| 10 |            | cious Attacks on Electronic Systems                       |     |

|    |            | VLSIs for Security                                        | 395 |

|    |            | shi Fujino, Daisuke Suzuki, Yohei Hori, Mitsuru Shiozaki, |     |

|    | Masa       | ya Yoshikawa, Toshiya Asai and Masayoshi Yoshimura        |     |

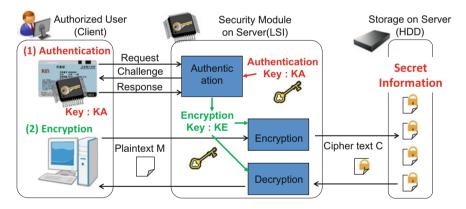

|    | 10.1       | The Role of Security LSI and the Example of Malicious     |     |

|    |            | Attacks                                                   | 396 |

|    | 10.2       | Methods for Tampering Cryptographic VLSIs                 | 403 |

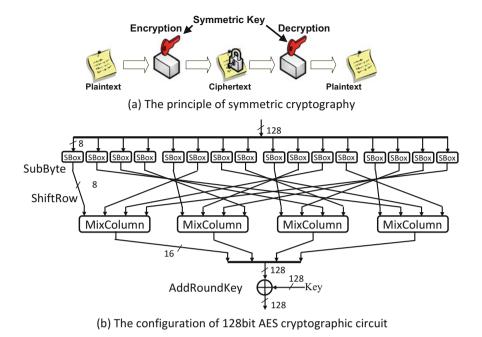

|    | 10.3       | Tamper-Resistant Symmetric-Key Cryptographic Circuits     | 410 |

|    | 10.4       | Verification Method for Tamper-Resistant VLSI Design      | 417 |

|    | 10.5       | A Method for Evaluating Vulnerability                     |     |

|    |            | to Scan-Based Attacks                                     | 423 |

|    | 10.6       | Evaluation of Tamper Resistance of VLSIs                  | 427 |

|    | Refer      | ences                                                     | 434 |

| 11 | Test       | Coverage                                                  | 439 |

|    |            | hiro Fujita, Koichiro Takayama, Takeshi Matsumoto,        |     |

|    |            | ke Oshima, Satoshi Jo, Michiko Inoue, Tomokazu Yoneda     |     |

|    |            | Yuta Yamato                                               |     |

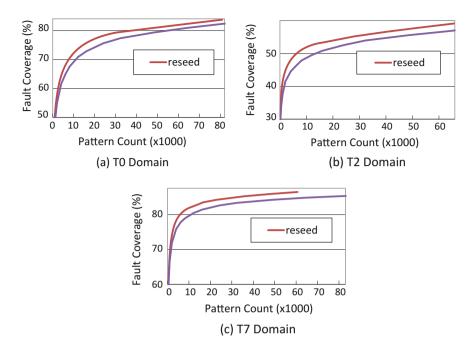

|    |            | Verification and Test Coverage                            | 440 |

|    | 11.2       | -                                                         | 444 |

|    |            | 6                                                         |     |

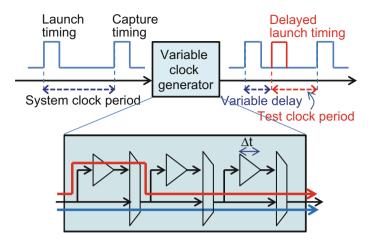

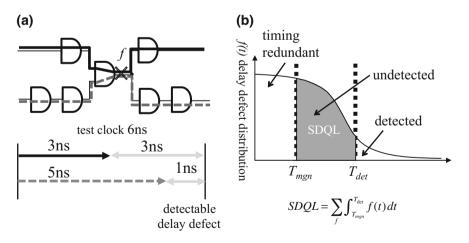

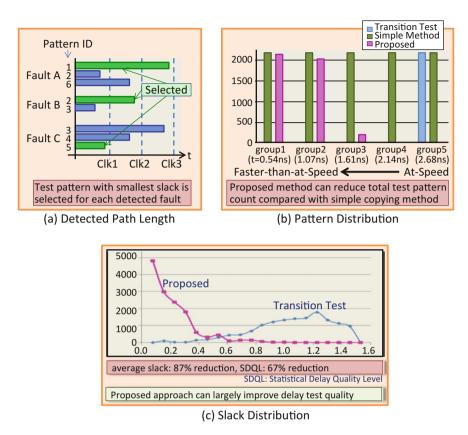

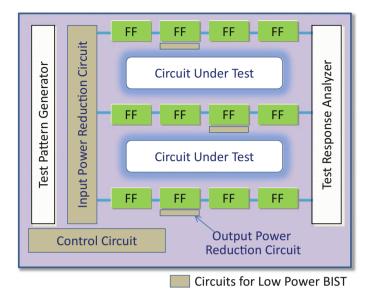

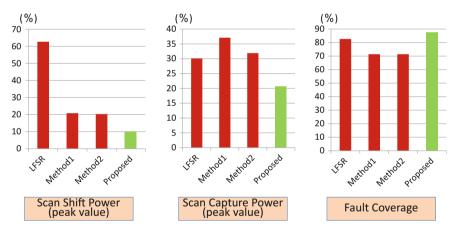

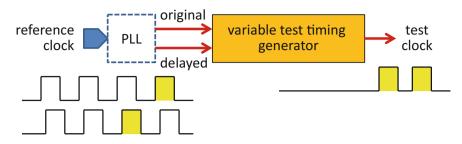

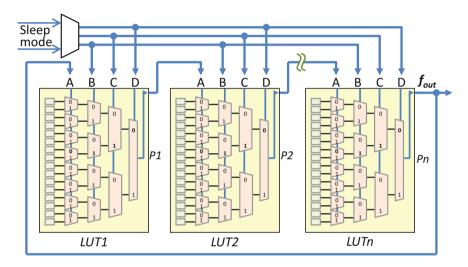

|     | 11.3<br>11.4                     | High-Quality Delay Testing for In-field Self-test                                                                                                                                                                                                       | 461<br>466 |

|-----|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | Refer                            | ences                                                                                                                                                                                                                                                   | 472        |

| 12  | Nobu<br>Takes<br>Satosl<br>Hiroy | wwn Threats and Provisions                                                                                                                                                                                                                              | 475        |

|     |                                  | Problems                                                                                                                                                                                                                                                | 477        |

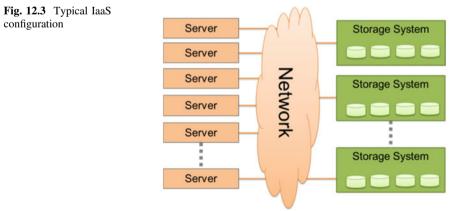

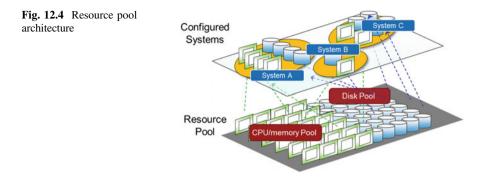

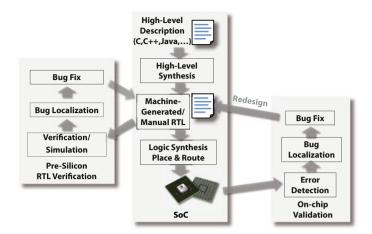

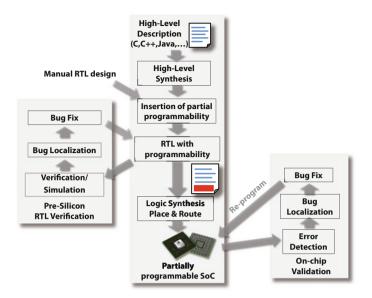

|     | 12.2<br>12.3                     | Challenges to Dependability at Data Centers<br>Post-silicon Validation and Patchable Hardware for                                                                                                                                                       | 480        |

|     | 12.4                             | Rectification<br>Logging and Using Field Test Data for Improved                                                                                                                                                                                         | 485        |

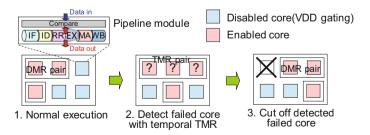

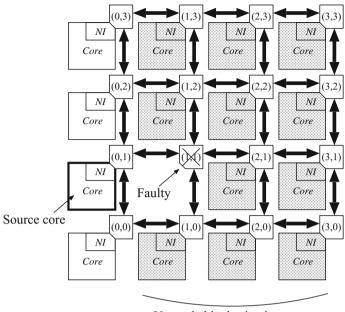

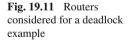

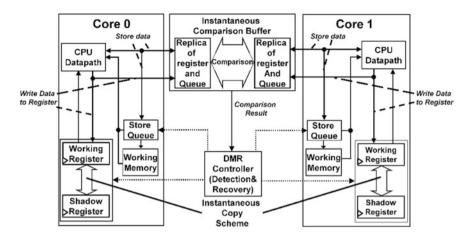

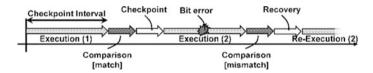

|     | 12.5                             | Dependability<br>Fault Detection and Reconfiguration in NoC-Coupled<br>Multiple-CPU Cores for Deadline-Specified Periodical                                                                                                                             | 495        |

|     | 12.6                             | Tasks    Checkpoint-Restart for Heterogeneous Multiple-Processor                                                                                                                                                                                        | 499        |

|     | Refer                            | Systems                                                                                                                                                                                                                                                 | 503<br>508 |

| Par | t III                            | Design and Test of VLSI for Systems Dependability                                                                                                                                                                                                       |            |

| 13  | _                                | n Automation for Reliability                                                                                                                                                                                                                            | 513        |

|     | 13.1                             | Design Automation Tools and Dependability                                                                                                                                                                                                               | 514        |

|     | 13.2                             | Analysis Tools for Soft Errors                                                                                                                                                                                                                          | 517        |

|     |                                  | ences                                                                                                                                                                                                                                                   | 518        |

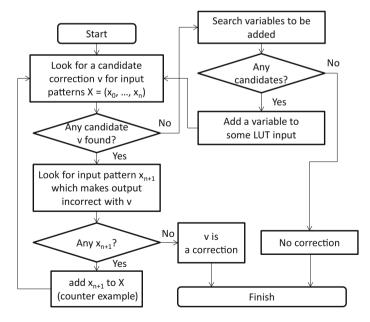

| 14  | for Sy<br>Masal<br>Kosul         | al Verification and Debugging of VLSI Logic Design<br>ystems Dependability: Experiments and Evaluation<br>hiro Fujita, Takeshi Matsumoto, Amir Masoud Gharehbaghi,<br>ke Oshima, Satoshi Jo, Hiroaki Yoshida, Takashi Takenaka<br>Kazutoshi Wakabayashi | 521        |

|     | 14.1                             | Goal of Logic Verification and Necessity                                                                                                                                                                                                                |            |

|     |                                  | of Formal Analysis                                                                                                                                                                                                                                      |            |

|     | 14.2                             | Formal Equivalence Checking Under C-Based Design                                                                                                                                                                                                        | 525        |

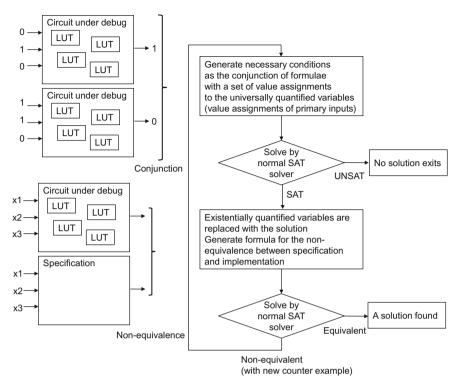

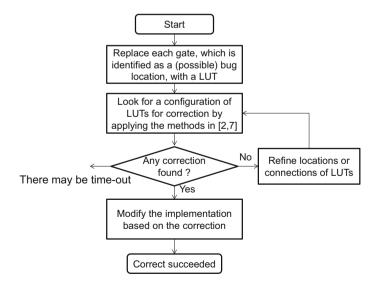

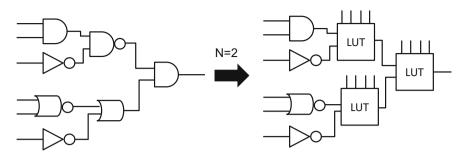

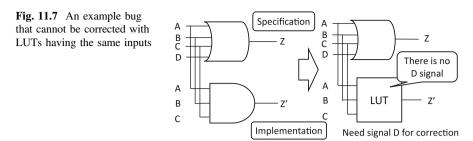

|     | 14.3                             | Logic Debugging with Formal Analysis                                                                                                                                                                                                                    | 532        |

|     | 14.4<br>Defer                    | Conclusion and Future Perspectives                                                                                                                                                                                                                      | 535        |

|     | Kefer                            | ences                                                                                                                                                                                                                                                   | 536        |

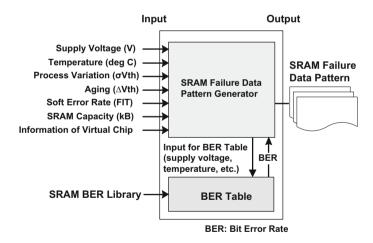

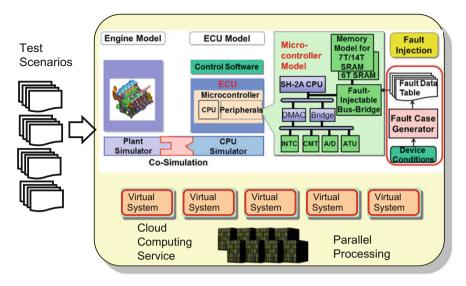

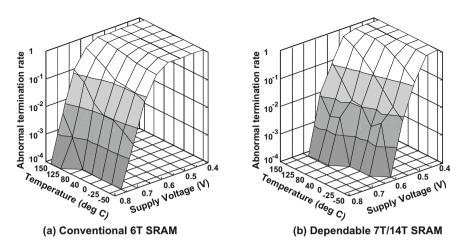

| 15 | Virtu | alization: System-Level Fault Simulation of SRAM            |      |

|----|-------|-------------------------------------------------------------|------|

|    | Error | s in Automotive Electronic Control Systems                  | 539  |

|    | Shige | ru Oho, Yasuhiro Ito, Yasuo Sugure, Yohei Nakata,           |      |

|    | Hiros | hi Kawaguchi and Masahiko Yoshimoto                         |      |

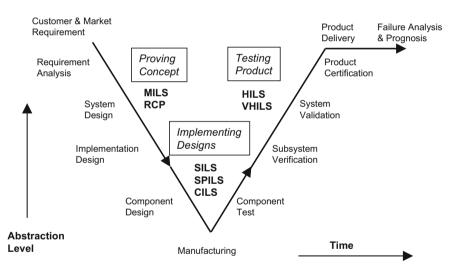

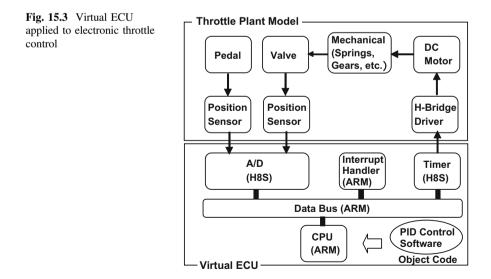

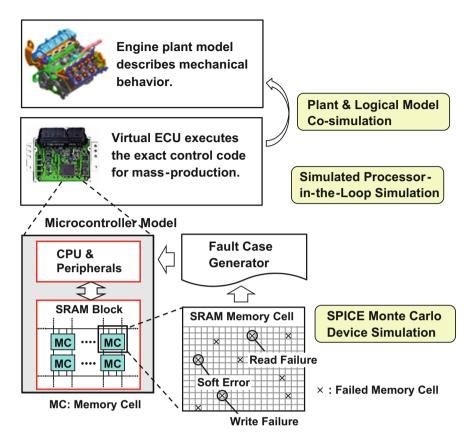

|    | 15.1  | Automotive Control Systems and Model-Based                  |      |

|    |       | Development                                                 | 540  |

|    | 15.2  | Virtual ECU and Its Applications                            | 542  |

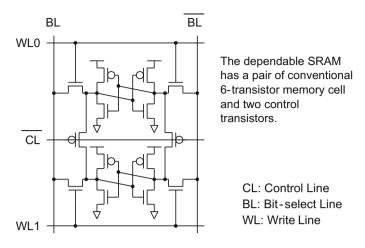

|    | 15.3  | Dependable SRAM                                             | 543  |

|    | 15.4  | Multilayer Modeling of Dependable SRAM and Automotive       |      |

|    |       | Control Systems                                             | 544  |

|    | 15.5  | Large-Scale Fault Injection Testing with Cloud Computing    | 547  |

|    | 15.6  | Future Directions                                           | 549  |

|    | Refer | ences                                                       | 550  |

|    |       |                                                             |      |

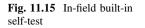

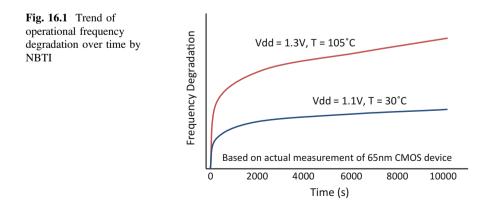

| 16 |       | T—A Concept of In-field Testing for Enhancing System        |      |

|    |       | ndability                                                   | 553  |

|    |       | ni Hatayama, Seiji Kajihara, Tomokazu Yoneda, Yuta Yamato,  |      |

|    |       | ko Inoue, Yasuo Sato, Yukiya Miura and Satoshi Ohtake       |      |

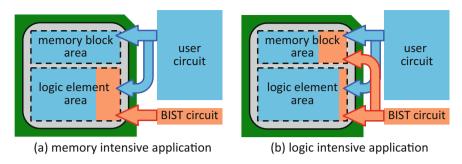

|    | 16.1  | Introduction                                                | 554  |

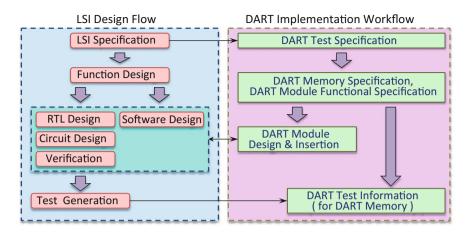

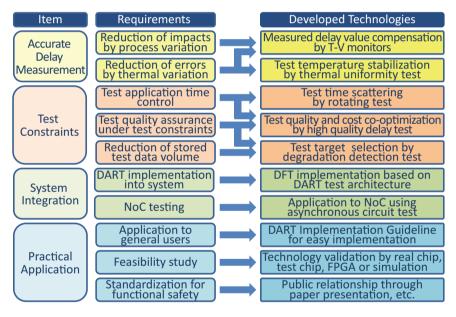

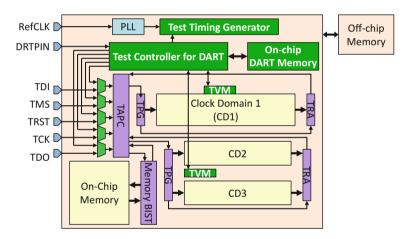

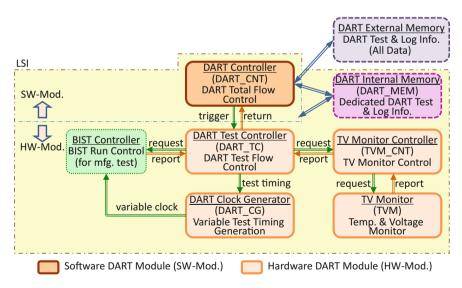

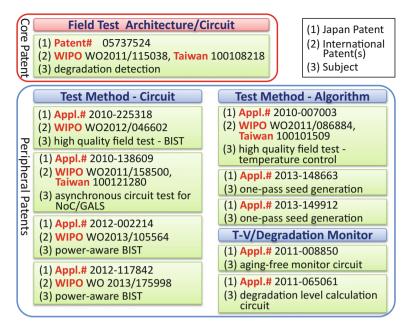

|    | 16.2  | Outline of DART Technology                                  | 556  |

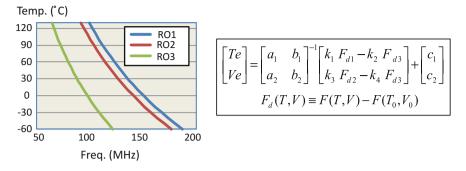

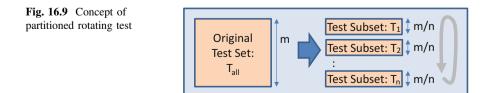

|    | 16.3  | Outlines of DART Elemental Technologies                     | 564  |

|    | 16.4  | Implementation of DART Technology                           | 567  |

|    | 16.5  | Other Activities                                            | 574  |

|    | 16.6  | Conclusion                                                  | 575  |

|    | Refer | ences                                                       | 576  |

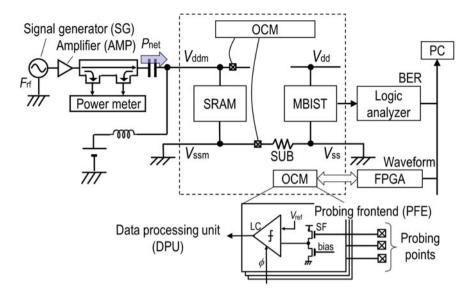

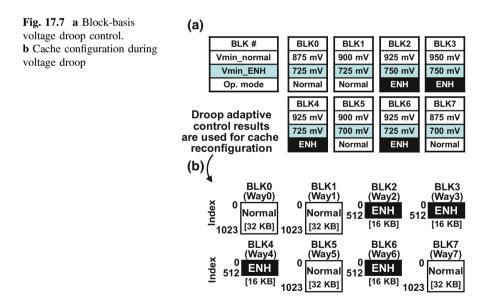

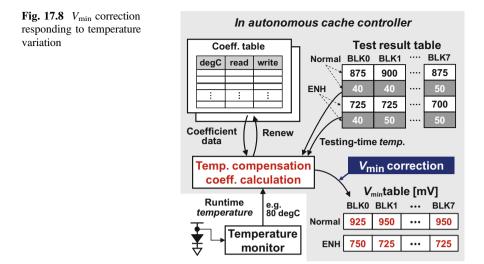

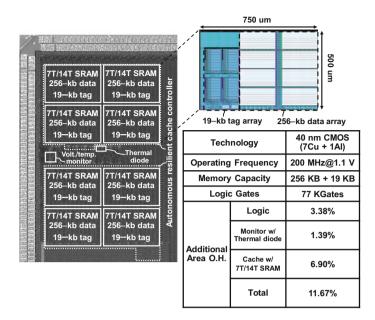

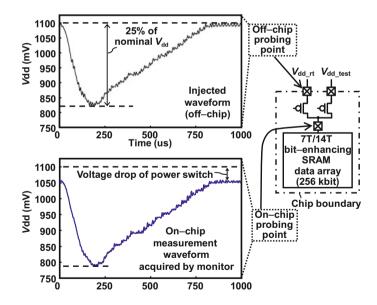

| 17 | Desig | n of SRAM Resilient Against Dynamic Voltage                 |      |

| 1, |       | tions                                                       | 579  |

|    |       | hiko Yoshimoto, Yohei Nakata, Yuta Kimi, Hiroshi Kawaguchi, | 0.12 |

|    |       | to Nagata and Koji Nii                                      |      |

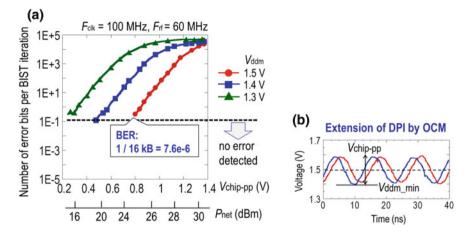

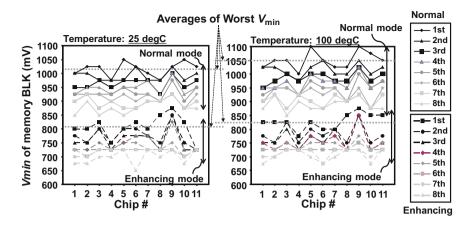

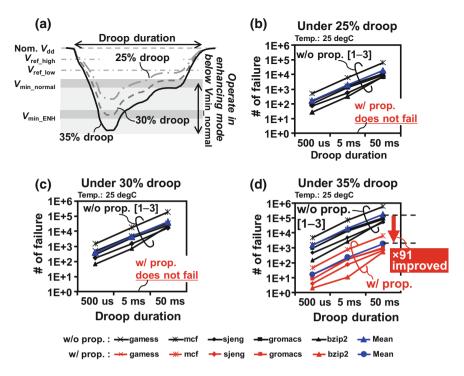

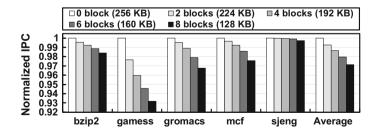

|    | 17.1  | Introduction                                                | 580  |

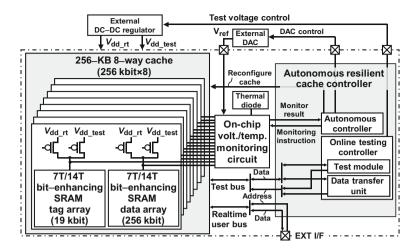

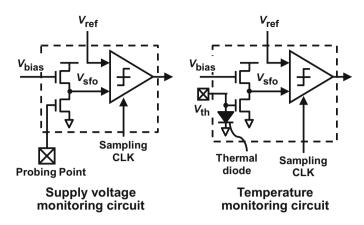

|    | 17.2  | Resilient Cache                                             | 580  |

|    | 17.3  | Measurement Results                                         | 586  |

|    | 17.4  | Conclusion                                                  | 590  |

|    | 17.1  | ences                                                       | 590  |

|    |       |                                                             | 570  |

| 18 | -     | n and Applications of Dependable Nonvolatile Memory         |      |

|    |       | ms                                                          | 593  |

|    | Shuhe | ei Tanakamaru and Ken Takeuchi                              |      |

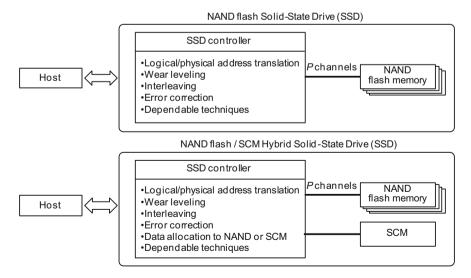

|    | 18.1  | Introduction                                                | 594  |

|    | 18.2  | Background                                                  | 594  |

|    | 18.3  | Reliability Improvement Techniques                          | 596  |

|    | 18.4  | Summary and Conclusion                                      | 604  |

|    | Refer | ences                                                       | 605  |

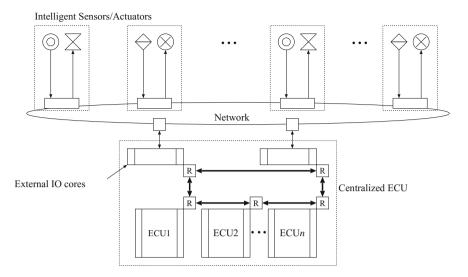

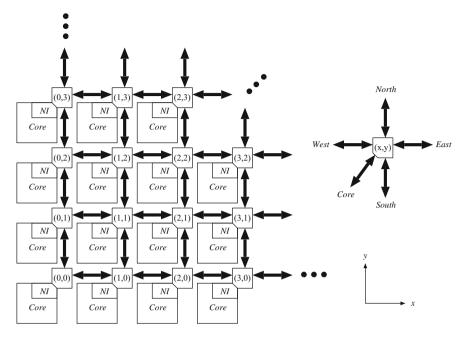

| 19         | Network-on-Chip Based Multiple-Core Centralized ECUs for<br>Safety-Critical Automotive Applications              |                                                                                                                                                                                                                                             |                                                                           |  |  |

|------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

|            |                                                                                                                  | hiro Yoneda, Masashi Imai, Hiroshi Saito, Akira Mochizuki,                                                                                                                                                                                  | 607                                                                       |  |  |

|            |                                                                                                                  | iro Hanyu, Kenji Kise and Yuichi Nakamura                                                                                                                                                                                                   |                                                                           |  |  |

|            | 19.1                                                                                                             | Introduction                                                                                                                                                                                                                                | 608                                                                       |  |  |

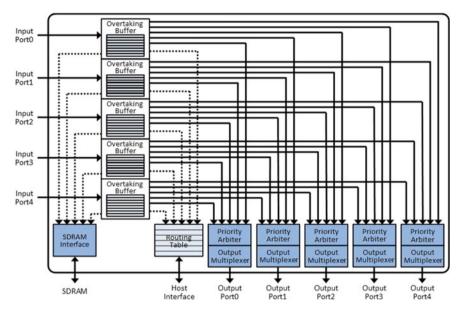

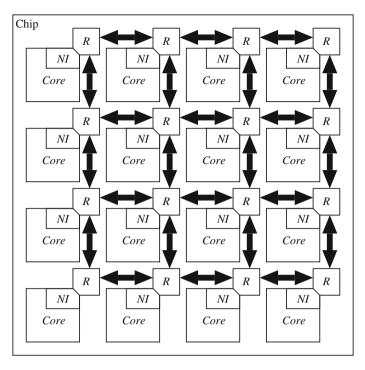

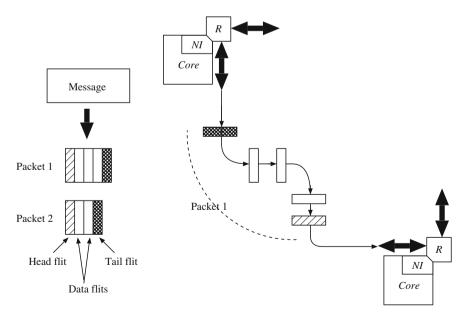

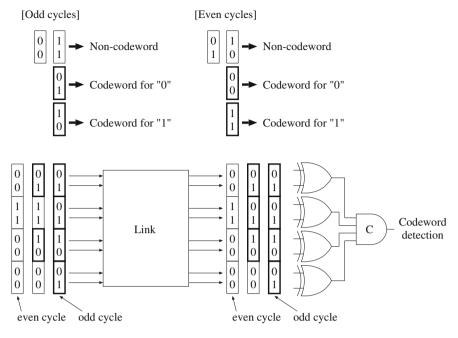

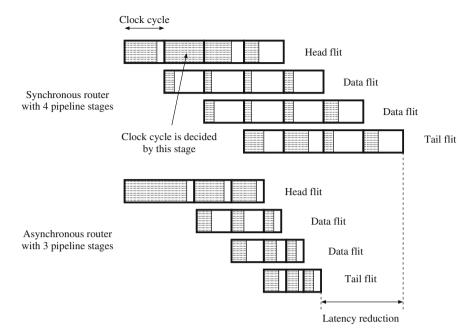

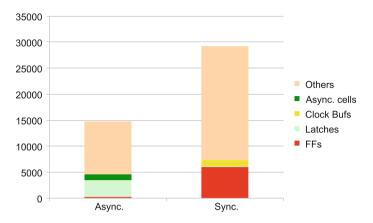

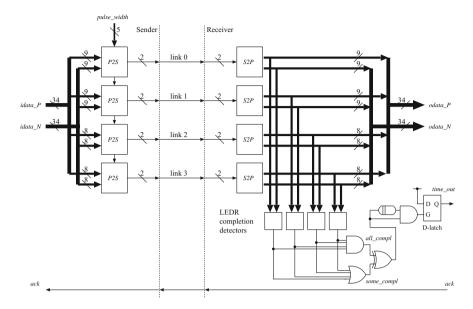

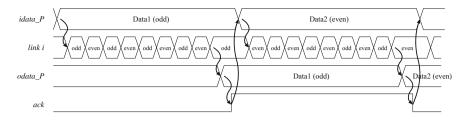

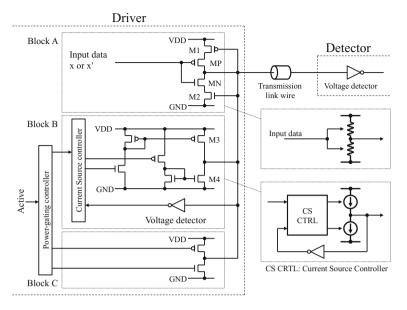

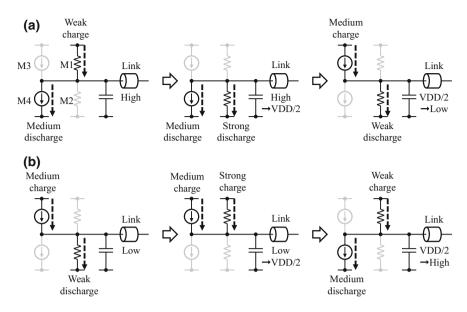

|            | 19.1                                                                                                             | Asynchronous On-chip and Inter-chip Network                                                                                                                                                                                                 | 610                                                                       |  |  |

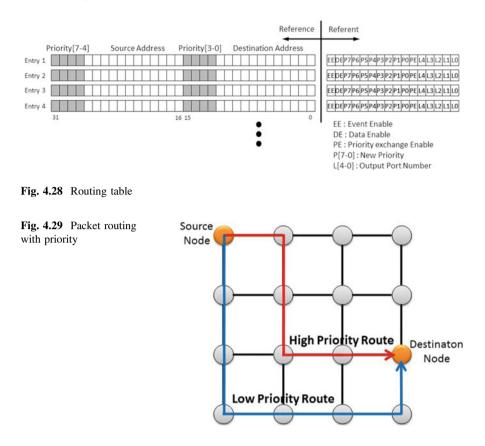

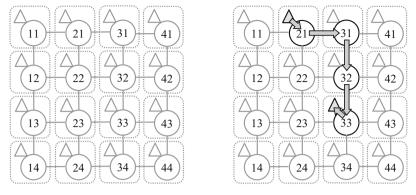

|            | 19.2                                                                                                             | Dependable Routing Algorithm                                                                                                                                                                                                                | 617                                                                       |  |  |

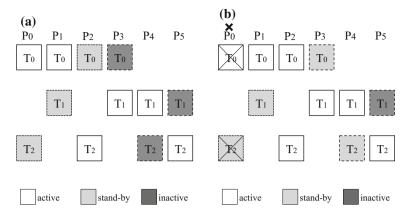

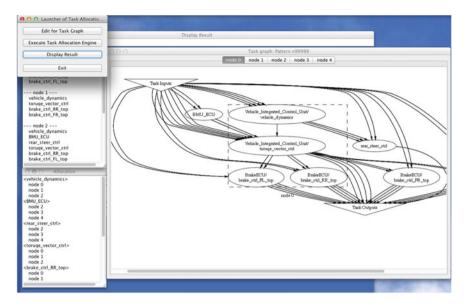

|            | 19.5                                                                                                             | Dependable Task Execution                                                                                                                                                                                                                   | 626                                                                       |  |  |

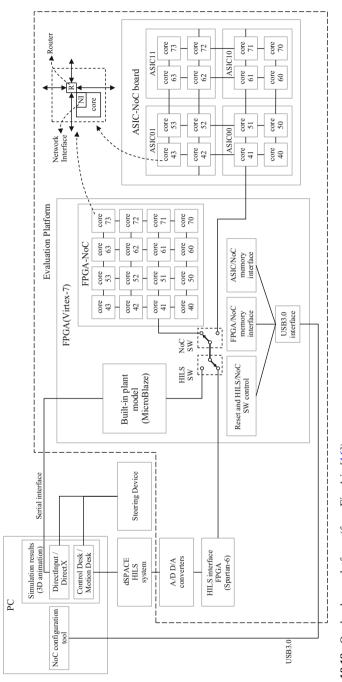

|            | 19.4                                                                                                             | Evaluation Kit                                                                                                                                                                                                                              | 629                                                                       |  |  |

|            | 19.5                                                                                                             | Conclusion                                                                                                                                                                                                                                  | 632                                                                       |  |  |

|            |                                                                                                                  | ences                                                                                                                                                                                                                                       | 632                                                                       |  |  |

|            | Kelei                                                                                                            |                                                                                                                                                                                                                                             | 052                                                                       |  |  |

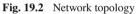

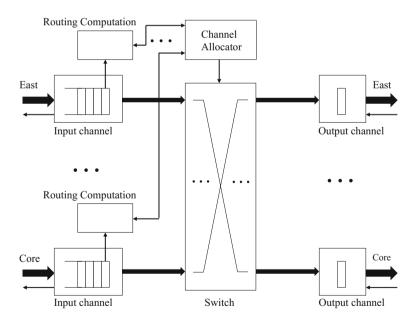

| 20         | An O                                                                                                             | n-chip Router Architecture for Dependable Multicore                                                                                                                                                                                         |                                                                           |  |  |

|            | Proce                                                                                                            | ssor                                                                                                                                                                                                                                        | 635                                                                       |  |  |

|            | Kenji                                                                                                            |                                                                                                                                                                                                                                             |                                                                           |  |  |

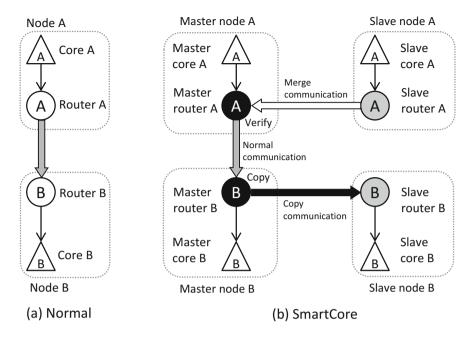

|            | 20.1                                                                                                             | Introduction                                                                                                                                                                                                                                | 635                                                                       |  |  |

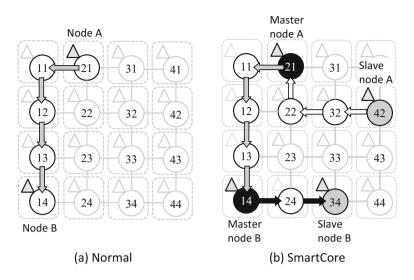

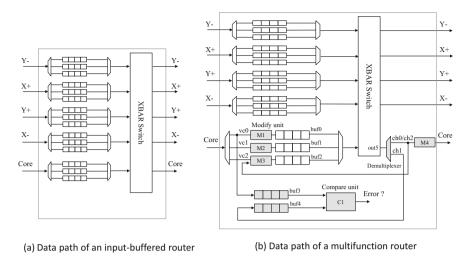

|            | 20.2                                                                                                             | SmartCore System                                                                                                                                                                                                                            | 636                                                                       |  |  |

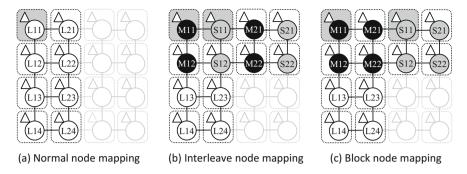

|            | 20.3                                                                                                             | NoC Multifunction Router for SmartCore System                                                                                                                                                                                               | 640                                                                       |  |  |

|            | 20.4                                                                                                             | Conclusion                                                                                                                                                                                                                                  | 642                                                                       |  |  |

|            | Refer                                                                                                            | ences                                                                                                                                                                                                                                       | 643                                                                       |  |  |

| <b>A</b> 1 | Wiro                                                                                                             | ess Interconnect in Electronic Systems                                                                                                                                                                                                      | 645                                                                       |  |  |

| 21         |                                                                                                                  |                                                                                                                                                                                                                                             | 043                                                                       |  |  |

| 21         | Tadał                                                                                                            | iro Kuroda and Atsutake Kosuge                                                                                                                                                                                                              |                                                                           |  |  |

| 21         | Tadał<br>21.1                                                                                                    | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646                                                                       |  |  |

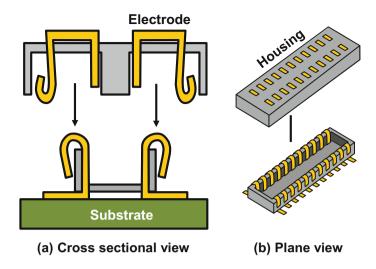

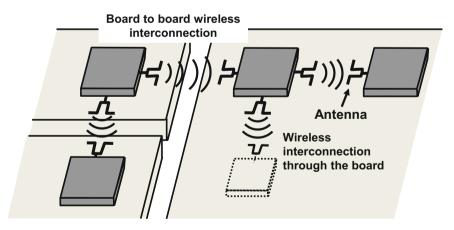

| 21         | Tadah<br>21.1<br>21.2                                                                                            | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646                                                                |  |  |

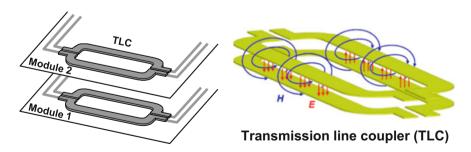

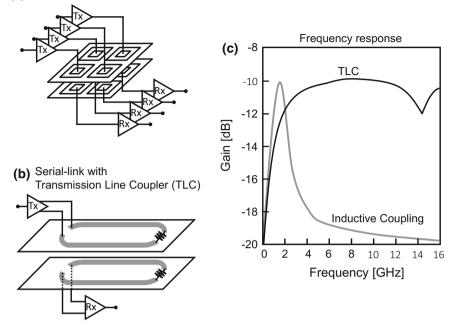

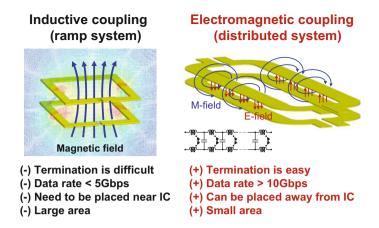

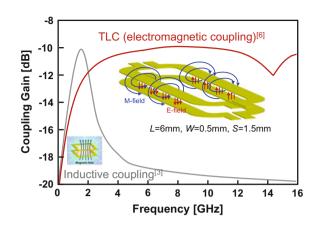

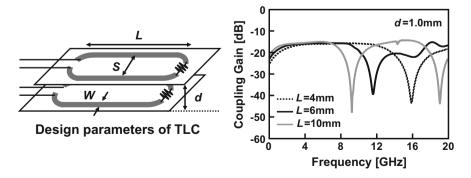

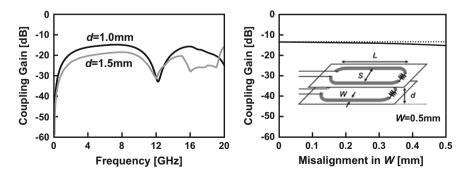

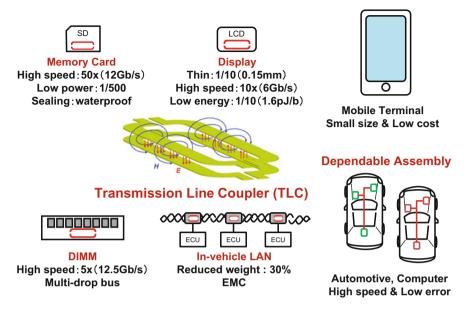

| 21         | Tadał<br>21.1<br>21.2<br>21.3                                                                                    | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648                                                         |  |  |

| 21         | Tadah<br>21.1<br>21.2<br>21.3<br>21.4                                                                            | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655                                                  |  |  |

| 21         | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer                                                                   | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656                                           |  |  |

| 21         | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer                                                                   | irro Kuroda and Atsutake Kosuge         Introduction         Wireless Interconnection         Transmission Line Couplers         Conclusion         ences         ences         ences         Delivery Resilient Against Loading Variations | 646<br>646<br>648<br>655                                                  |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok                                                 | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656                                           |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer                                                                   | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656<br>659                                    |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok                                                 | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656<br>659<br>660                             |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2                                 | iro Kuroda and Atsutake Kosuge          Introduction                                                                                                                                                                                        | 646<br>646<br>648<br>655<br>656<br>659                                    |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1                                         | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656<br>659<br>660                             |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2                                 | iro Kuroda and Atsutake Kosuge          Introduction                                                                                                                                                                                        | 646<br>648<br>655<br>656<br>659<br>660<br>662<br>663                      |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2                                 | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>648<br>655<br>656<br>659<br>660<br>662<br>663<br>664               |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2<br>22.3                         | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>648<br>655<br>656<br>659<br>660<br>662<br>663                      |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2<br>22.3<br>22.4<br>22.5<br>22.6 | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>648<br>655<br>656<br>659<br>660<br>662<br>663<br>664               |  |  |

|            | Tadah<br>21.1<br>21.2<br>21.3<br>21.4<br>Refer<br>Wirel<br>Hirok<br>22.1<br>22.2<br>22.3<br>22.4<br>22.5         | iro Kuroda and Atsutake Kosuge<br>Introduction                                                                                                                                                                                              | 646<br>646<br>648<br>655<br>656<br>659<br>660<br>662<br>663<br>664<br>667 |  |  |

| <b>Dependability of Public Wireless Communications</b>    |                                                                                                                                                                                                                       |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Noriharu Suematsu and Tadashi Takagi                      | а,                                                                                                                                                                                                                    |

| 6                                                         |                                                                                                                                                                                                                       |

| 22.1 25 Networks For Second Second Sec                    |                                                                                                                                                                                                                       |

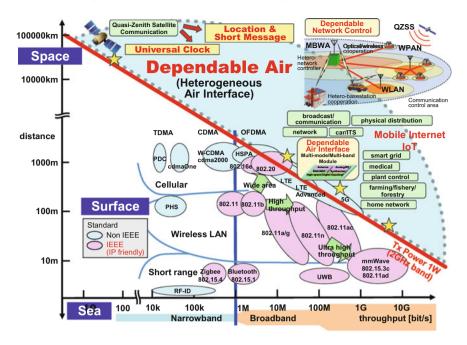

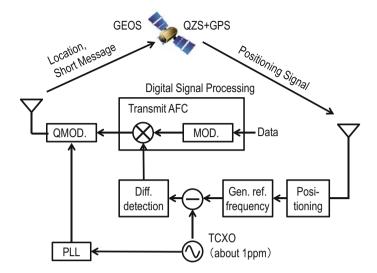

| 23.1 3S Network: For Space, Surface, and Sea              | 676                                                                                                                                                                                                                   |

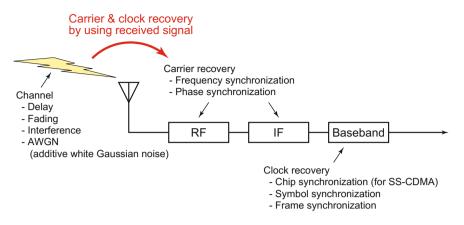

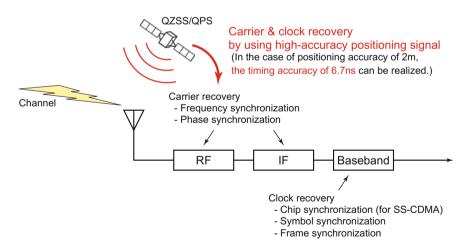

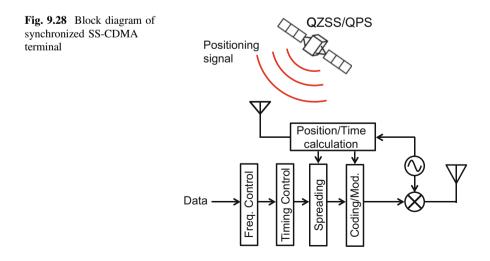

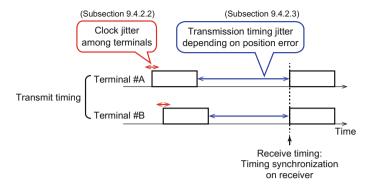

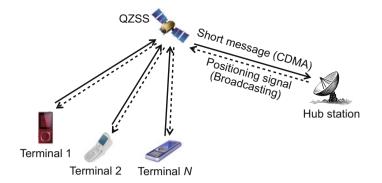

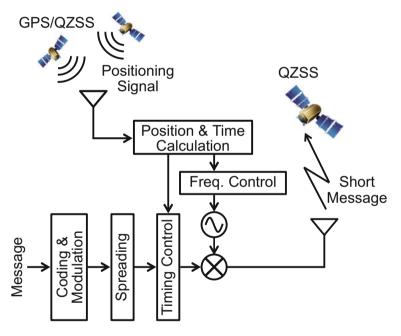

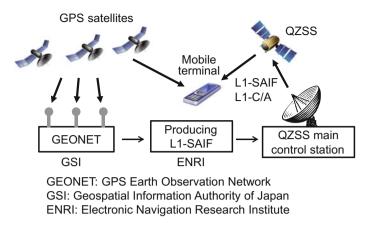

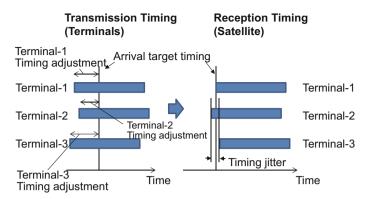

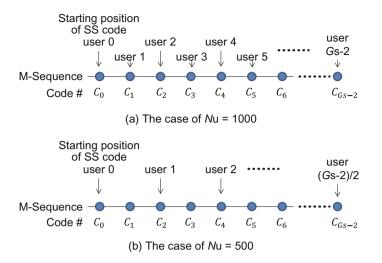

| 23.2 SS-CDMA: A Proposal for Disaster Message Exchange    | 678                                                                                                                                                                                                                   |

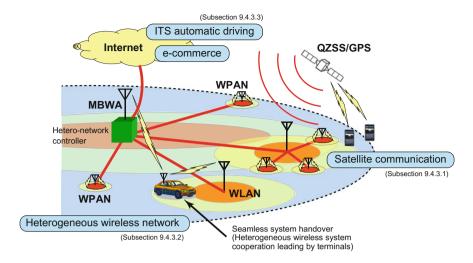

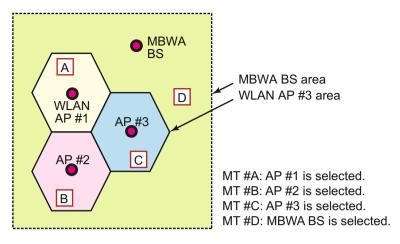

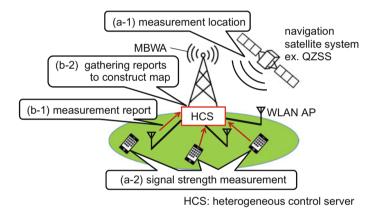

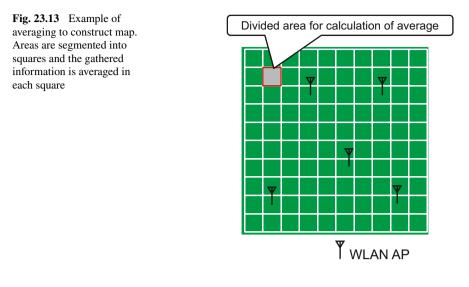

| 23.3 Heterogeneous Wireless System with Network Selection |                                                                                                                                                                                                                       |

| Scheme Using Positioning Information                      | 687                                                                                                                                                                                                                   |

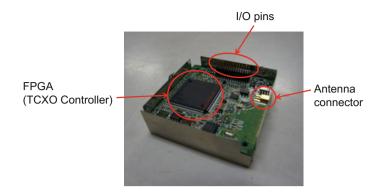

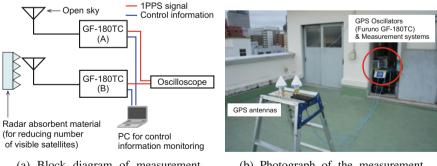

| 23.4 Readiness of Required Technologies                   | 690                                                                                                                                                                                                                   |

| References                                                | 691                                                                                                                                                                                                                   |

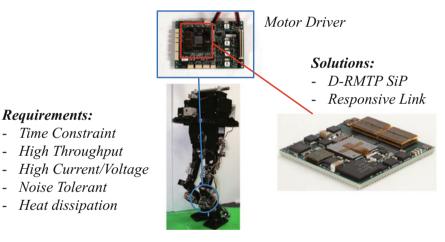

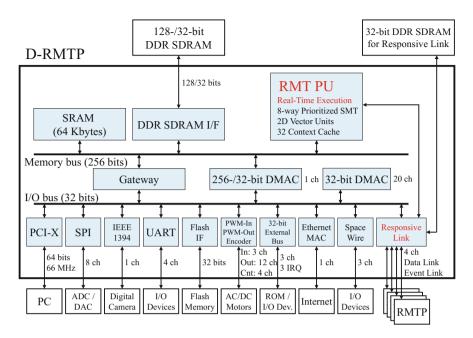

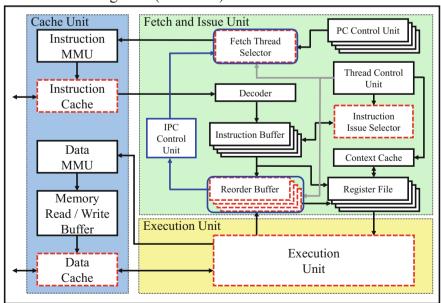

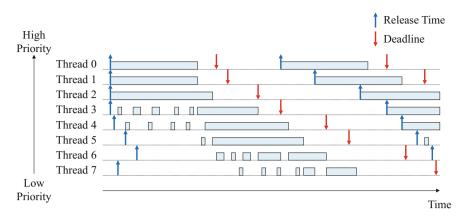

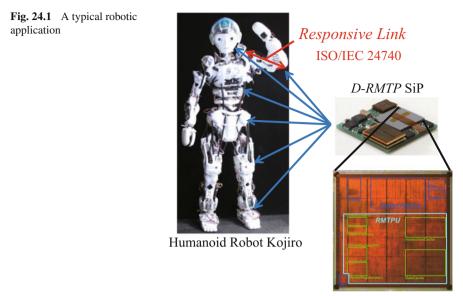

| 24 Responsive Multithreaded Processor for Hard Real-Time  |                                                                                                                                                                                                                       |

| Robotic Applications                                      | 693                                                                                                                                                                                                                   |

| Nobuyuki Yamasaki, Hiroyuki Chishiro, Keigo Mizotani      |                                                                                                                                                                                                                       |

| and Kikuo Wada                                            |                                                                                                                                                                                                                       |

| 24.1 Introduction                                         | 693                                                                                                                                                                                                                   |

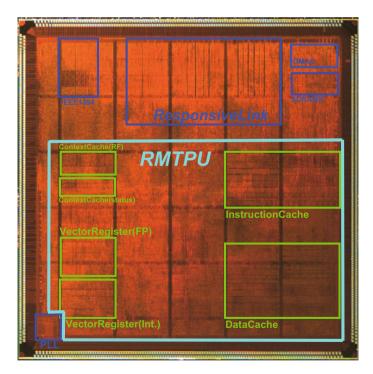

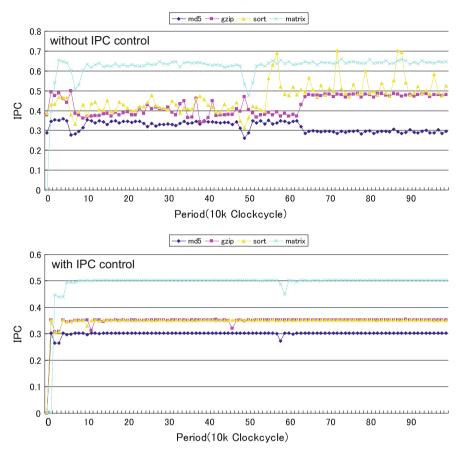

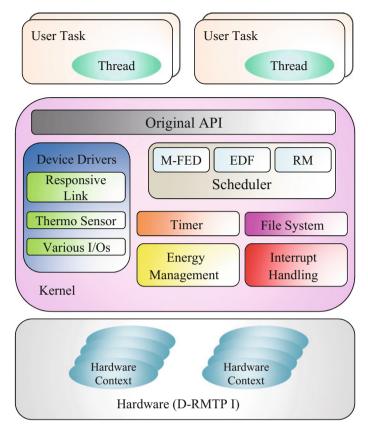

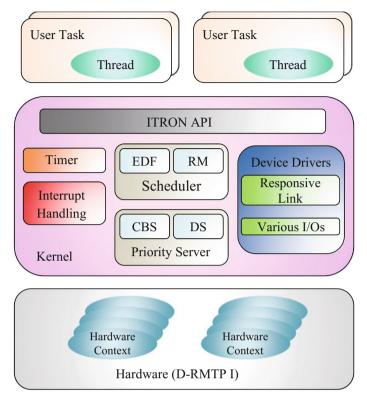

| 24.2 Responsive Multithreaded Processor (RMTP)            |                                                                                                                                                                                                                       |

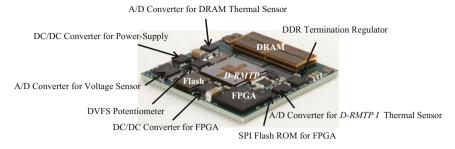

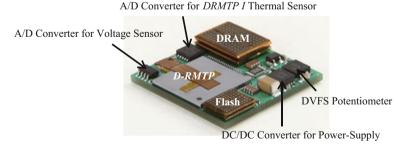

| 24.3 Co-design of SoC and SiP                             |                                                                                                                                                                                                                       |

| 24.4 Real-Time Operating Systems                          |                                                                                                                                                                                                                       |

|                                                           |                                                                                                                                                                                                                       |

| 24.5 Summary                                              |                                                                                                                                                                                                                       |

|                                                           | 705                                                                                                                                                                                                                   |

| 24.5 Summary                                              | 705                                                                                                                                                                                                                   |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706                                                                                                                                                                                                            |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706                                                                                                                                                                                                            |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706                                                                                                                                                                                                            |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709                                                                                                                                                                                                     |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709                                                                                                                                                                                              |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710                                                                                                                                                                                       |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710<br>713                                                                                                                                                                                |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710<br>713<br>715                                                                                                                                                                         |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710<br>713<br>715<br>717                                                                                                                                                                  |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710<br>713<br>715<br>717                                                                                                                                                                  |

| <ul> <li>24.5 Summary</li></ul>                           | 705<br>706<br>709<br>709<br>710<br>713<br>715<br>717<br>718                                                                                                                                                           |

| <ul> <li>24.5 Summary</li></ul>                           | 705            706            709            709            709            710            713            717            718            719                                                                            |

| <ul> <li>24.5 Summary</li></ul>                           | 705            706            709            709            709            710            713            717            718            719            720                                                             |

| <ul> <li>24.5 Summary</li></ul>                           | 705            706            709            709            709            710            713            717            718            719            720            723                                              |

| <ul> <li>24.5 Summary</li></ul>                           | 705            706            709            709            709            710            713            715            717            718            719            719            720            723            727 |

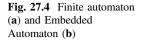

| 27  |       | ications of Reconfigurable Processors as Embedded                                                                 |     |

|-----|-------|-------------------------------------------------------------------------------------------------------------------|-----|

|     |       | matons in the IoT Sensor Networks in Space                                                                        | 735 |

|     |       | i Hihara, Akira Iwasaki, Masanori Hashimoto, Hiroyuki Ochi,                                                       |     |

|     |       | o Mitsuyama, Hidetoshi Onodera, Hiroyuki Kanbara,                                                                 |     |

|     |       | toshi Wakabayashi, Tadahiko Sugibayashi, Takashi Takenaka,                                                        |     |

|     | Hiron | nitsu Hada and Munehiro Tada                                                                                      |     |

|     | 27.1  | Introduction                                                                                                      | 736 |

|     | 27.2  | Intelligent Sensors for IoT Applications—Target                                                                   |     |

|     |       | Applications                                                                                                      | 737 |

|     | 27.3  | Choosing Proper Processor Architecture for                                                                        |     |

|     |       | IoT Applications                                                                                                  | 741 |

|     | 27.4  | The FRRA Implementation of Embedded Automatons                                                                    | 743 |

|     | 27.5  | An Example Implementation and Result                                                                              | 745 |

|     | 27.6  | Discussion                                                                                                        | 747 |

|     | Refer | ences                                                                                                             | 749 |

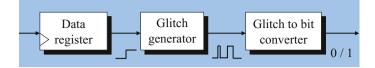

| 28  | Δn F  | PGA Implementation of Comprehensive Security Functions                                                            |     |

| 20  |       | ystems-Level Authentication                                                                                       | 751 |

|     |       | ike Suzuki, Koichi Shimizu and Takeshi Fujino                                                                     | 101 |

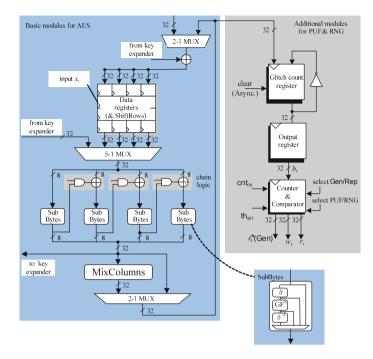

|     | 28.1  | Introduction                                                                                                      | 751 |

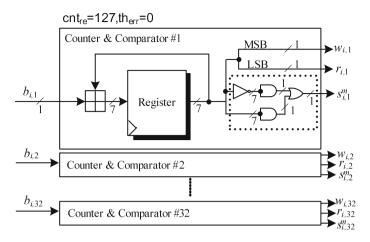

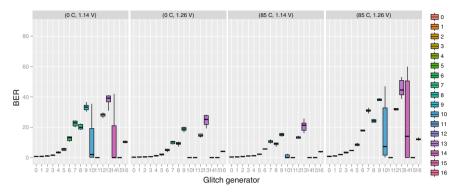

|     | 28.2  | Overview of Glitch PUFs                                                                                           | 752 |

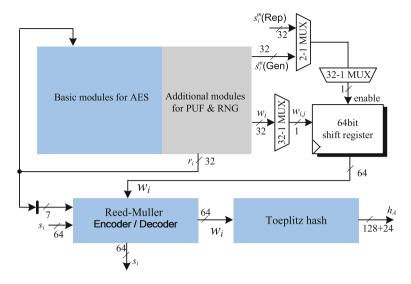

|     | 28.3  | Physical Random Number Generator                                                                                  | 753 |

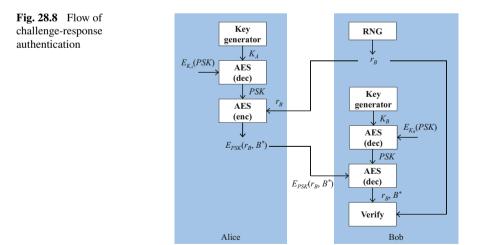

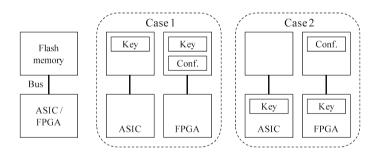

|     | 28.4  | Unified Security Coprocessor.                                                                                     | 756 |

|     | 28.5  | Performance Evaluation                                                                                            | 762 |

|     | 28.6  | Conclusions                                                                                                       | 771 |

|     |       | ences                                                                                                             | 772 |

| 29  |       |                                                                                                                   |     |

| 29  |       | M-Based Physical Unclonable Functions (PUFs) to Generate<br>ture Out of Silicon for Authentication and Encryption | 775 |

|     | Koji  |                                                                                                                   | 115 |

|     | 29.1  | Introduction                                                                                                      | 775 |

|     | 29.1  | A Unique Chip-ID Generation Scheme Using SRAM-Based                                                               | 115 |

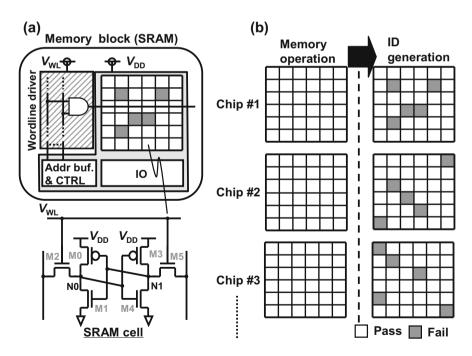

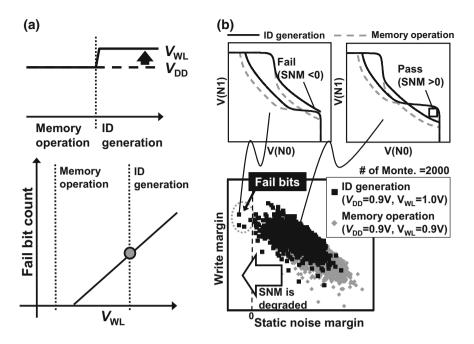

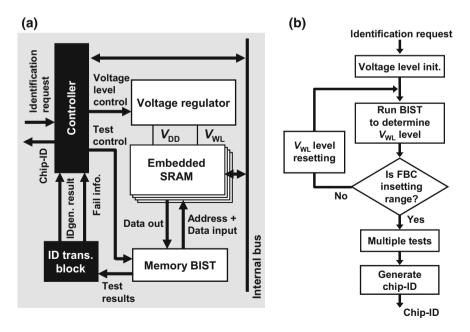

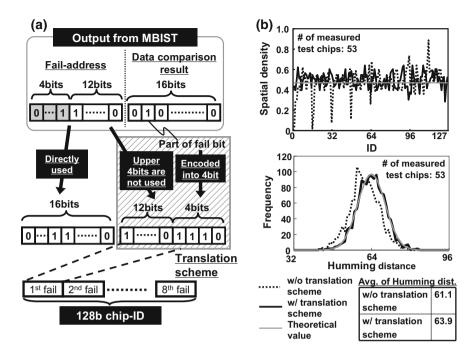

|     | 29.2  | PUF with Random Fail-Bit Addresses                                                                                | 777 |

|     | 29.3  | Assessing Uniqueness and Reliability of SRAM-Based PUFs                                                           | ,,, |

|     | 27.5  | from Silicon Measurements                                                                                         | 782 |

|     | 29.4  | Summary                                                                                                           | 791 |

|     |       | ences                                                                                                             | 791 |

| _   |       |                                                                                                                   |     |

| Ind | ex    |                                                                                                                   | 793 |

# Part I Introduction

## Chapter 1 Challenges and Opportunities in VLSI for Systems Dependability

Shojiro Asai

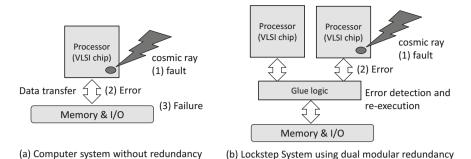

Abstract This chapter describes the scope, activities, and results of a research program entitled, "Fundamental Technologies for Dependable VLSI Systems (DVLSI for short henceforth)" which began in 2007 and ended in 2015. The program, funded by JST (Japan Science and Technology Agency) under the CREST (Core Research of Evolutional Science and Technology) initiative, consisted of 11 projects and addressed problems in dependability of electronic systems from various different angles. VLSI is a complex system in its own right and involves a number of potential hazards that arise internally from aging in elements or those that can be caused by external disturbances such as ionizing radiations. Coping with these phenomena has always been a challenge in semiconductor engineering and this program as well. Fabrics (physical structures) robust against threats, bit-error correction methods, and logic-level redundancies have been extensively studied. To go further, challenges of 3-D integration, chip-area (on-chip and across-chip) network, and wireless packaging have been taken on. Exploiting the potential of VLSI in solving problems in systems that call for hard real-time response and/or synchronicity as in robotics and wireless telecommunications has been addressed as new great opportunities for VLSIs. Advanced ways of verification and test for VLSIs have also been dealt with. We will begin this chapter by going over the background of VLSIs for electronic systems and reviewing the necessity of dependability. We will then describe how this multi-project program of CREST DVLSI was formed and conducted. The university-industry collaboration in goal-oriented management efforts is highlighted as essential. A summary of results obtained follows.

**Keywords** Dependable system • VLSI • CREST • University-industry collaboration • Goal-oriented management

Rigaku Corporation, Tokyo, Japan e-mail: asai@rigaku.co.jp

© Springer Japan KK, part of Springer Nature 2019

S. Asai (ed.), VLSI Design and Test for Systems Dependability, https://doi.org/10.1007/978-4-431-56594-9\_1

S. Asai (🖂)

#### **1.1 VLSI in Electronic Systems and Their Dependability**

#### 1.1.1 Pervasiveness of VLSI

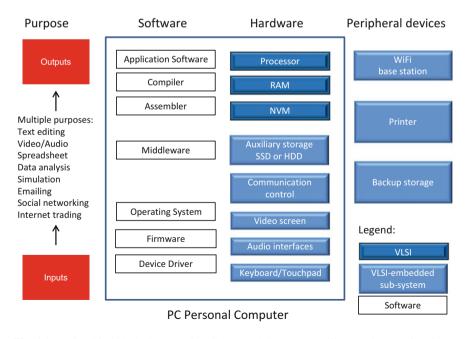

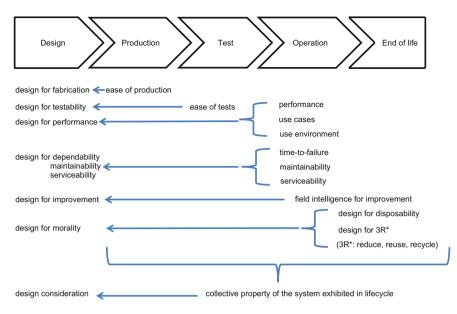

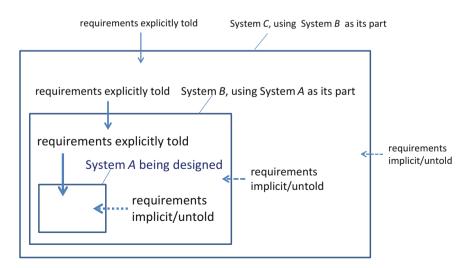

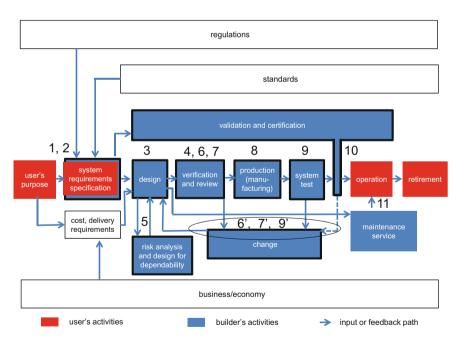

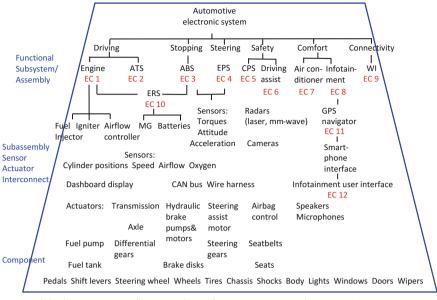

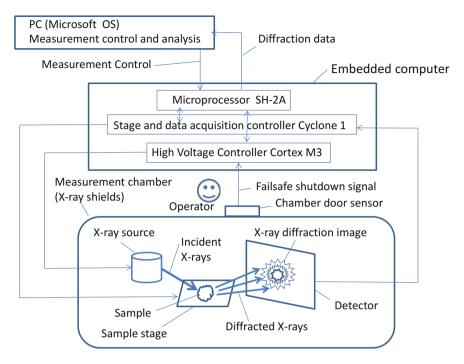

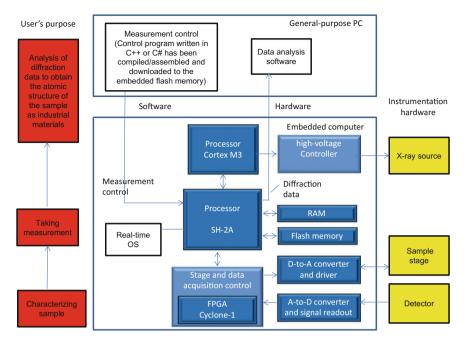

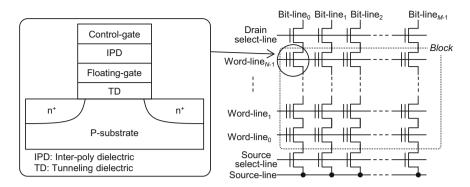

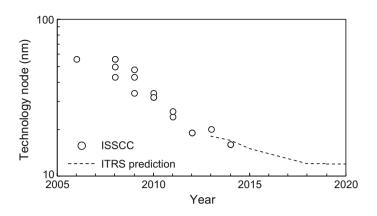

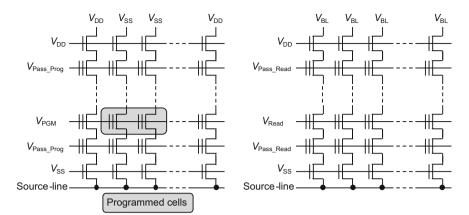

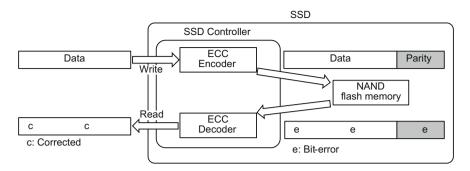

The VLSI (Very Large Scale Integration of semiconductor circuits) and software (computer program) are two great enablers of electronic systems, a synonym to modern-day convenience. Personal computers and cell phones, almost indispensable personal items these days, are good examples. Figure 1.1 shows a simplified block diagram of a personal computer. It is seen that VLSI chips such as a microprocessor [1–3], and semiconductor memories [4], e.g., RAM (Random Access Memory) and NVM (Nonvolatile Memory), are the most important parts among others. Important peripheral devices such as HDD (Hard Disk Drive), communications control, and monitoring display have built-in processors as well. The PC (Personal Computer) is a typical general-purpose computer where users run various different application programs. High-performance (Super-) computers are at the highest end of general-purpose computers.

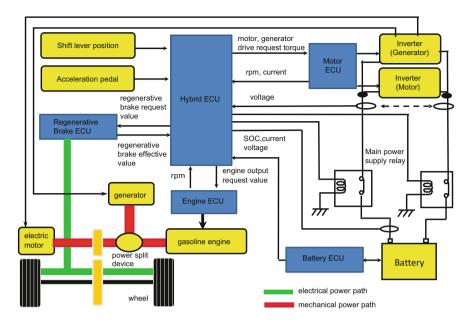

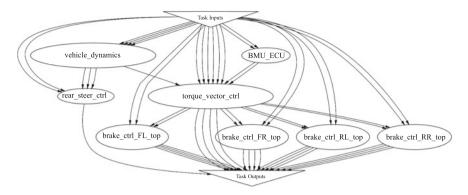

Figure 1.2 depicts the power train (power generation and transmission) in a hybrid electric-gasoline-engine vehicle which uses a number of ECUs (electronic control units). Each ECU has at least one microprocessor "embedded" and is thus an electronic system in its own right. The automobile these days is a typical embodiment of embedded computing [5]. A high-end car these days uses as many

Fig. 1.1 A simplified block diagram of a PC (Personal Computer) to illustrate the use of VLSIs as key components

Fig. 1.2 Electronic control units in the power train of a hybrid electric and gasoline-engine vehicle to illustrate use of VLSI-powered ECUs (Electronic Control Units). Courtesy, Toyota Motor Corporation

as 80 microprocessors for various subsystem and module-level control [6]. Actually, the VLSI has provided the biggest momentum to improve the quality and reduce the cost of products or services of electronic systems. This is true with most of complex systems products, which may be mechanical (stationary or mobile), aerodynamic, electrical, electromechanical, electromagnetic, optical, electro-optical, or chemical. Because these systems generally need control for precision and throughput, which is hard to achieve were it not for the VLSI and program control. Automobiles, aircrafts, rockets, robots, chemical plants, utilities, medical devices, ATMs (Automatic Teller Machines), data storages, and agricultural plants of today are good examples of computer-embedded systems. They would not have existed without the VLSI as their key components for smart control. It is almost funny that we are accustomed to call these computer-embedded electronic systems "dedicated systems." Although the purpose of the system is certainly "dedicated", for example, to automotive control, computers (microprocessors) have actually found far more general and voluminous applications in embedded control than in "general-purpose" computing by PCs and HPCs (High-Performance Computers).

The more the benefits are drawn out of these systems and the more extensive their uses become over the population, the more heavily the human life depends on them. It is necessary therefore to see to it that these systems are available whenever they are needed. Because the VLSI is at the core of these systems as the workhorse, it is necessary to understand what the VLSI does in electronic systems, what would happen if it fails to function as expected, what could be done to prevent serious failures from happening, and what we can innovate further in realizing more dependable systems technologies. Actually, these are the subjects discussed in this book. (Let us call the systems that use VLSIs as key components "electronic systems" hereafter. The term VLSI systems may be used interchangeably.)

#### 1.1.2 Necessity of Dependability

Dependability is never a single quality merit of a system. Central to the merit is rather the "performance" or "performance/cost," in other words, "better fulfillment of the primary purpose" it is intended for. Table 1.1 shows the factors that would affect the decision a user would make in the procurement of a product or service offered in the marketplace. During early stages of market introduction, cost and or performance may be the most influential factors, but as a product category and its market mature, increased attention is paid to dependability for increased social and economic implications, and this is true now with all kinds of electronic systems. These days, dependability of an electronic system is an interest shared among all those concerned: producers, users, and service providers alike.

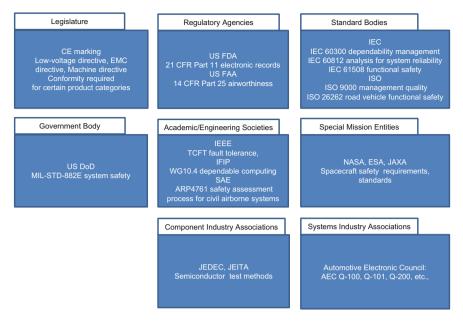

The requirements for dependability have been discussed in and among various government regulatory agencies, global/regional/national standards bodies, mission-oriented agencies, industrial associations, and academic societies. Figure 1.3 shows such organizations along with the documents they have published. It will be

| decisio       | n-affecting factors      | index                                                              |

|---------------|--------------------------|--------------------------------------------------------------------|

|               | cost of acquisition      | initial price (plus NRE when applies)                              |

|               |                          | cost of consumables                                                |

| cost (total   | operational cost         | cost of power, water, etc.                                         |

| cost of       |                          | maintenance/service cost                                           |

| ownership)    | cost of diposal          | disposal of consumables                                            |

|               | cost of diposal          | cost of retirement                                                 |

|               | speed (throughput)       | product units/hour, GBPS, MIPS, etc.                               |

| performance   |                          | accuracy/resolution (in units of time, length, etc.),              |

| penormanee    | accuracy, resolution     | measurement repeatability, etc.                                    |

|               | ease of use              | unquantifiable                                                     |

|               | availability             | MTTF, MTBF, regular maintenance/service time, network              |

|               | availability             | connentivity, etc.                                                 |

|               | maintainability          | MTTR                                                               |

| dependability | maintenance support      | unquantifiable (availability of service, parts, help desk, etc.)   |

|               | safety and security      | unquantifiable (functional safety, tamper resistance, availability |

|               | salety and security      | of encryption, etc.)                                               |

|               | integrity                | unquantifiable (tamper resistance, accountability, etc.)           |

| NRE: non-recu | rrent engineering, MIPS: | Million Instructions Per Second, GBPS: Giga Bits Per Second,       |

|               | <b>0</b>                 | Maan Tima Batuaan Failuraa, MTTD*, Maan Tima Ta Banair             |

Table 1.1 Factors affecting the decision-making for procurement of a product or service

NRE: non-recurrent engineering, MIPS: Million Instructions Per Second, GBPS: Giga Bits Per Second, MTTF\*: Mean Time To Failure, MTBF\*: Mean Time Between Failures, MTTR\*: Mean Time To Repair \*: Statistical quantities available only after operation for a certain length of time

Fig. 1.3 Organizations engaged in regulations, standards, and guidelines for dependability as part of product quality

relevant to refer in particular to IEC 60300 [7] for dependability management, IEC 61508 [8] for functional safety in industrial process measurement, control and automation, and ISO 26262 [9] for the functional safety for road vehicles, since these will be frequently cited throughout this book.

#### **1.2 Background and Motivation for the Program**

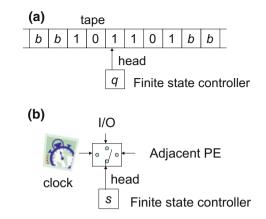

#### 1.2.1 What VLSI Has Brought About—A Historical Perspective

The VLSI has contributed to the progress in electronic systems in so many ways, which may be summarized as follows.

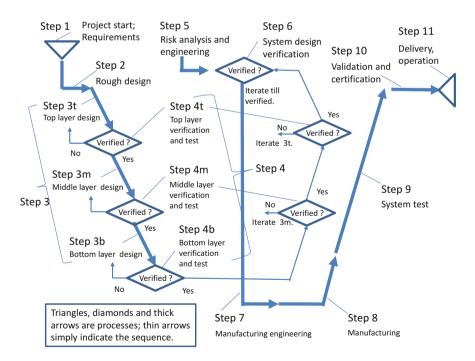

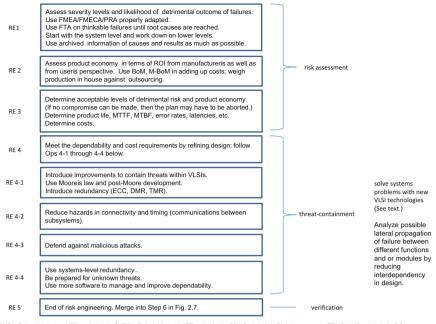

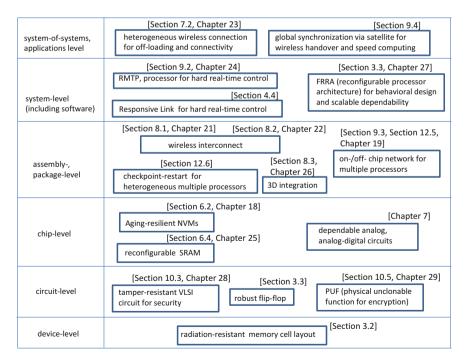

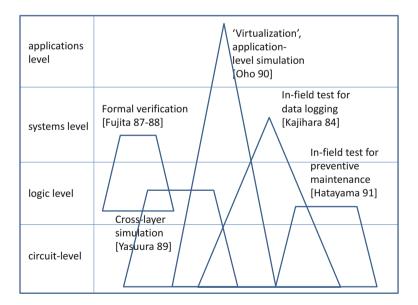

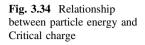

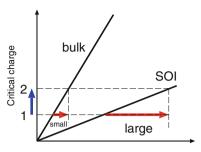

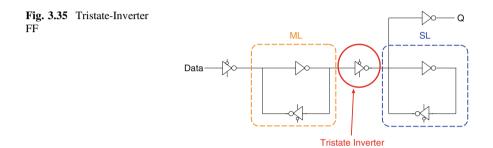

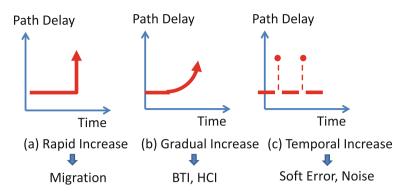

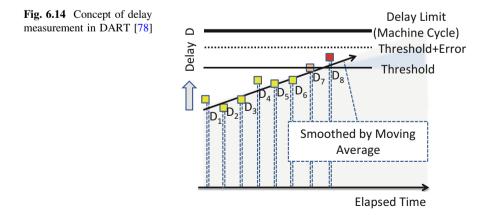

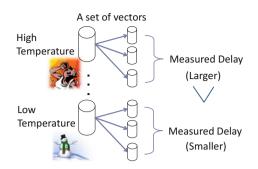

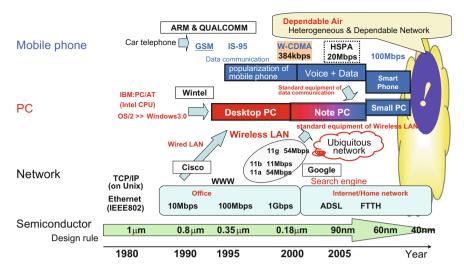

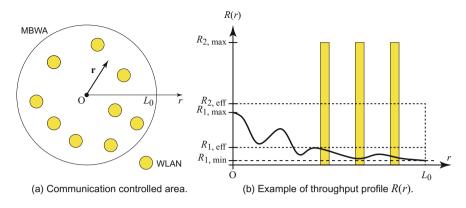

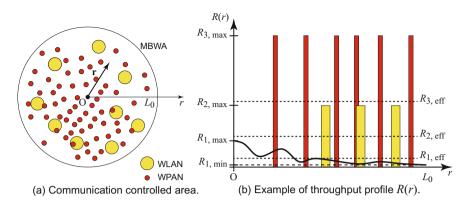

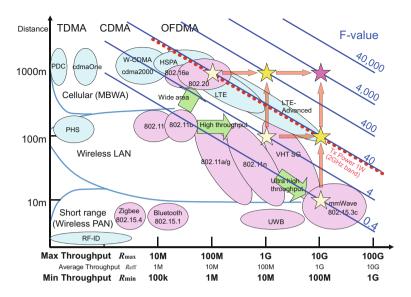

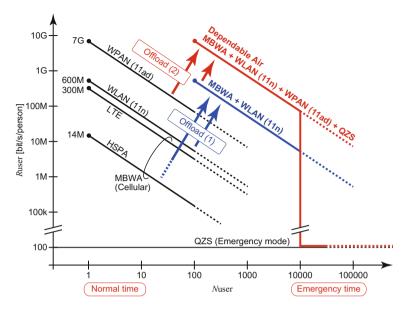

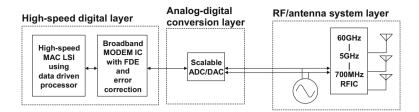

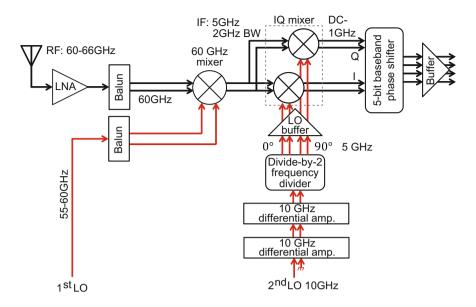

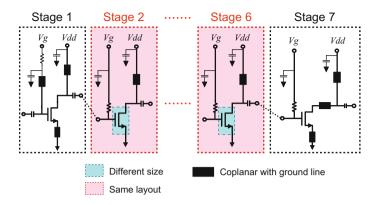

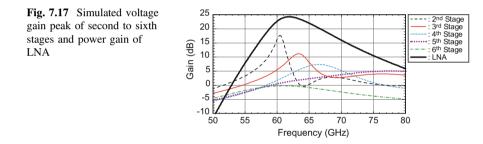

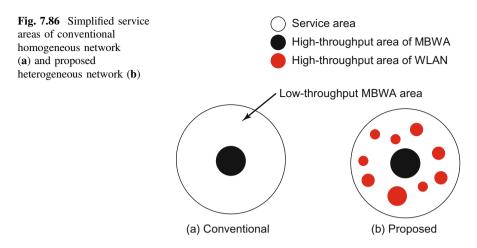

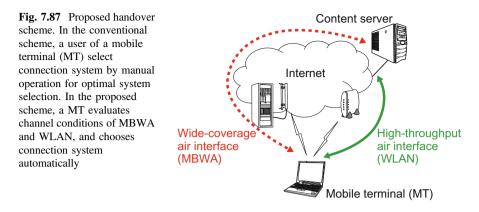

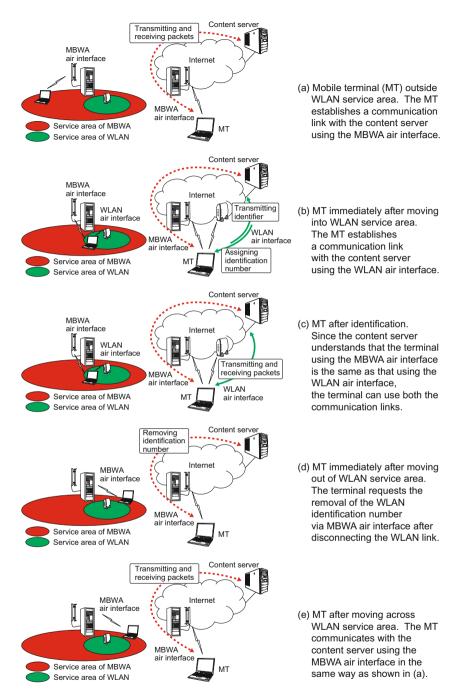

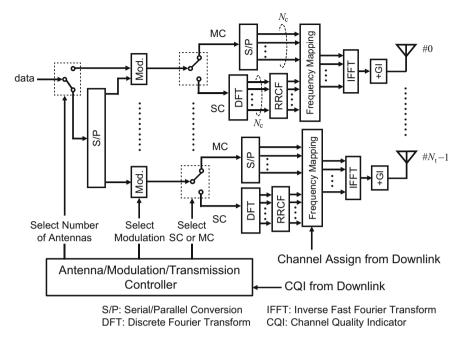

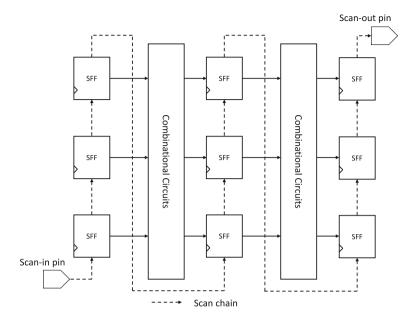

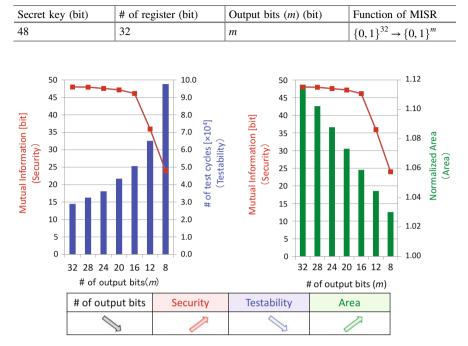

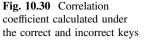

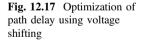

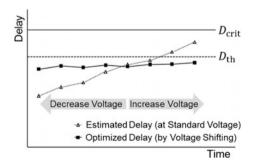

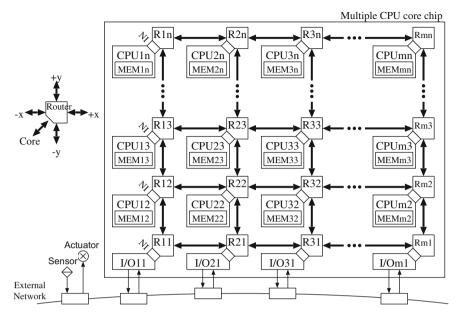

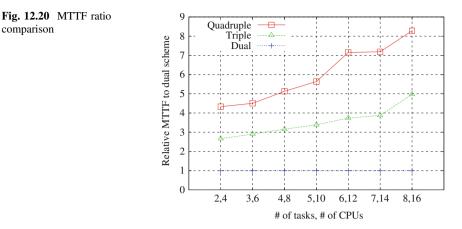

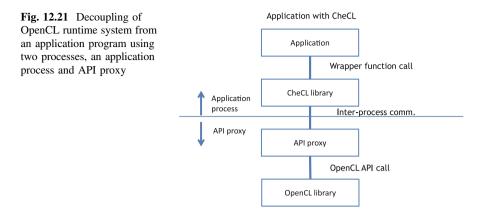

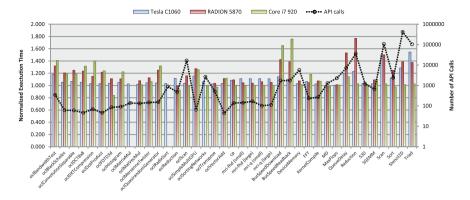

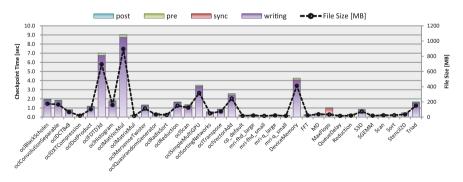

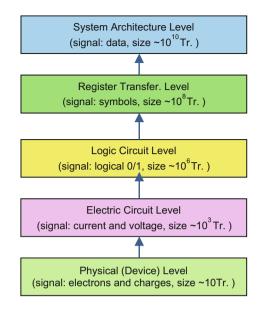

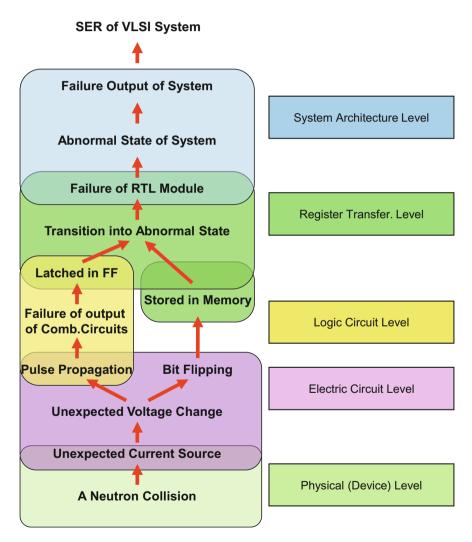

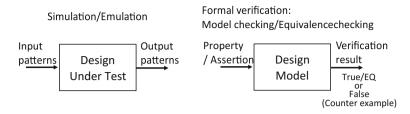

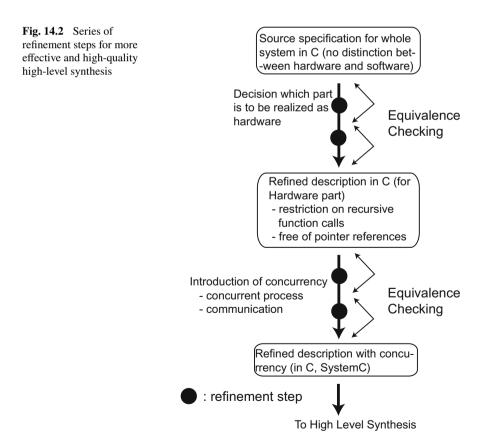

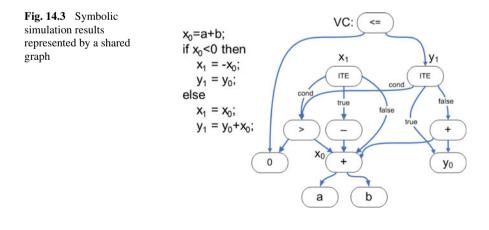

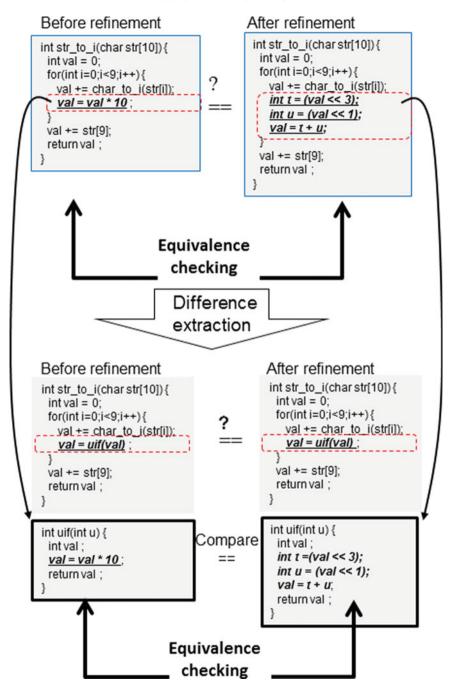

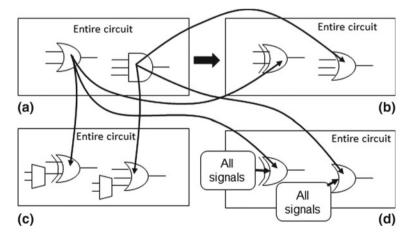

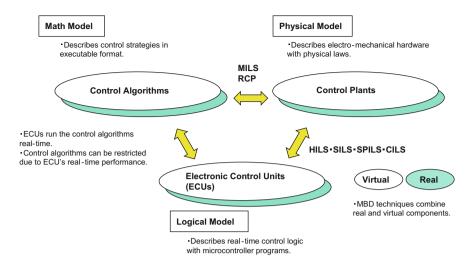

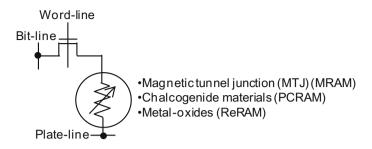

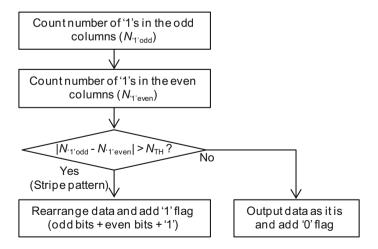

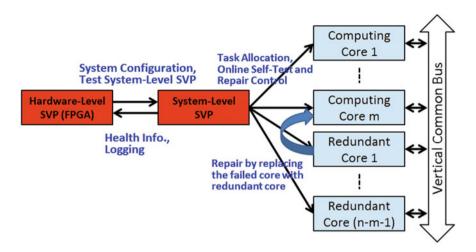

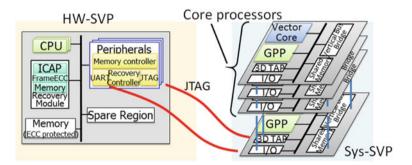

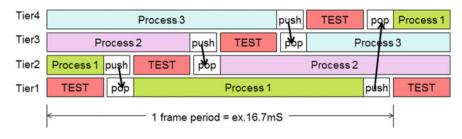

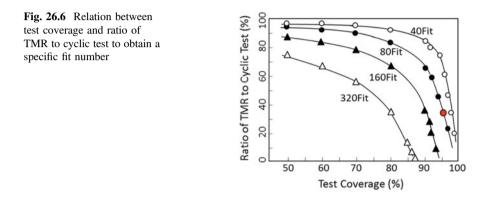

#1 Great number of devices integrated on a chip